Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                 |

|--------------------------------|------------------------------------------------------------------------|

| Number of LABs/CLBs            | 4224                                                                   |

| Number of Logic Elements/Cells | -                                                                      |

| Total RAM Bits                 | 55296                                                                  |

| Number of I/O                  | 138                                                                    |

| Number of Gates                | 250000                                                                 |

| Voltage - Supply               | 1.425V ~ 1.575V                                                        |

| Mounting Type                  | Surface Mount                                                          |

| Operating Temperature          | -55°C ~ 125°C (TA)                                                     |

| Package / Case                 | 256-LBGA                                                               |

| Supplier Device Package        | 256-FPBGA (17x17)                                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax250-fg256m |

|                                |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Axcelerator Family Device Status**

| Axcelerator <sup>®</sup> Devices | Status     |

|----------------------------------|------------|

| AX125                            | Production |

| AX250                            | Production |

| AX500                            | Production |

| AX1000                           | Production |

| AX2000                           | Production |

# **Temperature Grade Offerings**

| Package | AX125 | AX250   | AX500   | AX1000  | AX2000  |

|---------|-------|---------|---------|---------|---------|

| PQ208   | -     | C, I, M | C, I, M | _       | _       |

| CQ208   | -     | М       | М       | _       | _       |

| CQ256   | -     | _       | _       | _       | М       |

| FG256   | C, I  | C, I, M | -       | -       | -       |

| FG324   | C, I  | -       | -       | -       | -       |

| CQ352   | -     | М       | М       | М       | М       |

| FG484   | -     | C, I, M | C, I, M | C, I, M | -       |

| CG624   | -     | -       | -       | М       | М       |

| FG676   | -     | -       | C, I, M | C, I, M | -       |

| BG729   | -     | -       | -       | C, I, M | -       |

| FG896   | -     | -       | -       | C, I, M | C, I, M |

| FG1152  | -     | -       | -       | -       | C, I, M |

C = Commercial

l = Industrial

M = Military

# **Speed Grade and Temperature Grade Matrix**

| Temperature Grade | Std          | -1           | -2           |

|-------------------|--------------|--------------|--------------|

| С                 | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 1                 | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Μ                 | $\checkmark$ | $\checkmark$ | -            |

C = Commercial

l = Industrial

M = Military

Axcelerator Family FPGAs

# **Packaging Data**

Refer to the following documents located on the Microsemi SoC Products Group website for additional packaging information.

Package Mechanical Drawings

Package Thermal Characteristics and Weights

Hermatic Package Mechanical Information

Contact your local Microsemi representative for device availability.

# User I/Os<sup>2</sup>

## Introduction

The Axcelerator family features a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) with its bank-selectable I/Os. Table 2-8 on page 2-12 contains the I/O standards supported by the Axcelerator family, and Table 2-10 on page 2-12 compares the features of the different I/O standards.

Each I/O provides programmable slew rates, drive strengths, and weak pull-up and weak pull-down circuits. The slew rate setting is effective for both rising and falling edges.

I/O standards, except 3.3 V PCI and 3.3 V PCI-X, are capable of hot insertion. 3.3 V PCI and 3.3 V PCI-X are 5 V tolerant with the aid of an external resistor.

The input buffer has an optional user-configurable delay element. The element can reduce or eliminate the hold time requirement for input signals registered within the I/O cell. The value for the delay is set on a bank-wide basis. Note that the delay WILL be a function of process variations as well as temperature and voltage changes.

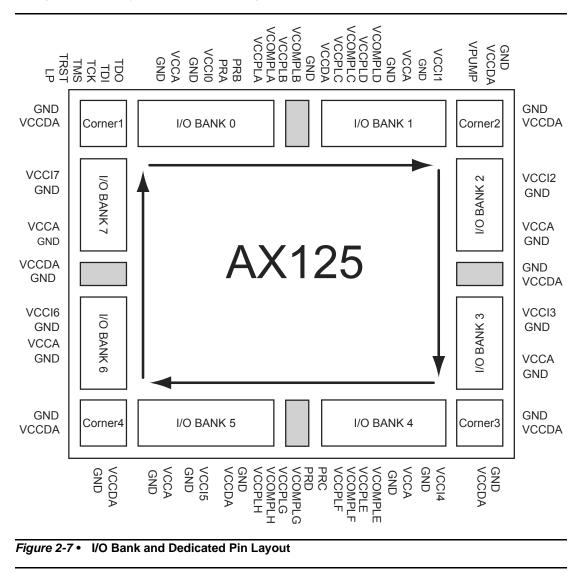

Each I/O includes three registers: an input (InReg), an output (OutReg), and an enable register (EnReg). I/Os are organized into banks, and there are eight banks per device—two per side (Figure 2-6 on page 2-18). Each I/O bank has a common VCCI, the supply voltage for its I/Os.

For voltage-referenced I/Os, each bank also has a common reference-voltage bus, VREF. While VREF must have a common voltage for an entire I/O bank, its location is user-selectable. In other words, any user I/O in the bank can be selected to be a VREF.

The location of the VREF pin should be selected according to the following rules:

- Any pin that is assigned as a VREF can control a maximum of eight user I/O pad locations in each direction (16 total maximum) within the same I/O bank.

- I/O pad locations listed as no connects are counted as part of the 16 maximum. In many cases, this leads to fewer than eight user I/O package pins in each direction being controlled by a VREF pin.

- Dedicated I/O pins such as GND and VCCI are counted as part of the 16.

- The two user I/O pads immediately adjacent on each side of the VREF pin (four in total) may only be used as inputs. The exception is when there is a VCCI/GND pair separating the VREF pin and the user I/O pad location.

- The user does not need to assign VREF pins for OUTBUF and TRIBUF. VREF pins are needed only for input and bidirectional I/Os.

The differential amplifier supply voltage VCCDA should be connected to 3.3 V.

A user can gain access to the various I/O standards in three ways:

- Instantiate specific library macros that represent the desired specific standard.

- Use generic I/O macros and then use Designer's PinEditor to specify the desired I/O standards (please note that this is not applicable to differential standards).

- A combination of the first two methods.

Refer to the I/O Features in Axcelerator Family Devices application note and the Antifuse Macro Library Guide for more details.

<sup>2.</sup> Do not use an external resister to pull the I/O above  $V_{CCI}$  for a higher logic "1" voltage level. The desired higher logic "1" voltage level will be degraded due to a small I/O current, which exists when the I/O is pulled up above  $V_{CCI}$ .

# 5 V Tolerance

There are two schemes to achieve 5 V tolerance:

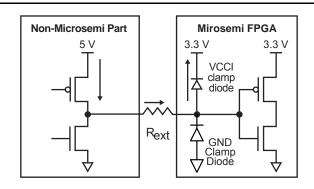

1. 3.3 V PCI and 3.3 V PCI-X are the only I/O standards that directly allow 5 V tolerance. To implement this, an internal clamp diode between the input pad and the VCCI pad is enabled so that the voltage at the input pin is clamped, as shown in EQ 3:

EQ 3

The internal VCCI clamp diode is only enabled while the device is powered on, so the voltage at the input will not be clamped if the VCCI or VCCA are powered off. An external series resistor (~100  $\Omega$ ) is required between the input pin and the 5 V signal source to limit the current to less than 20 mA (Figure 2-3). The 100  $\Omega$  resistor was chosen to meet the input Tr/Tf requirement (Table 2-19 on page 2-21). The GND clamp diode is available for all I/O standards and always enabled.

#### Figure 2-3 • Use of an External Resistor for 5 V Tolerance

5 V tolerance can also be achieved with 3.3 V I/O standards (3.3 V PCI, 3.3 V PCI-X, and LVTTL) using a bus-switch product (e.g. IDTQS32X2384). This will convert the 5 V signal to a 3.3 V signal with minimum delay (Figure 2-4).

#### Figure 2-4 • Bus Switch IDTQS32X2384

### Simultaneous Switching Outputs (SSO)

When multiple output drivers switch simultaneously, they induce a voltage drop in the chip/package power distribution. This simultaneous switching momentarily raises the ground voltage within the device relative to the system ground. This apparent shift in the ground potential to a non-zero value is known as simultaneous switching noise (SSN) or more commonly, ground bounce.

SSN becomes more of an issue in high pin count packages and when using high performance devices such as the Axcelerator family. Based upon testing, Microsemi recommends that users not exceed eight simultaneous switching outputs (SSO) per each VCCI/GND pair. To ease this potential burden on designers, Microsemi has designed all of the Axcelerator BGAs<sup>3</sup> to not exceed this limit with the exception of the CS180, which has an I/O to VCCI/GND pair ratio of nine to one.

Please refer to the *Simultaneous Switching Noise and Signal Integrity* application note for more information.

<sup>3.</sup> The user should note that in Bank 8 of both AX1000-FG484 and AX500-FG484, there are local violations of this 8:1 ratio.

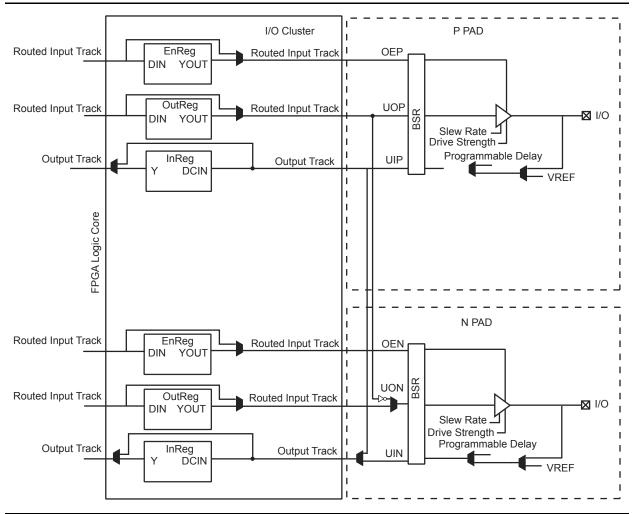

# I/O Clusters

Each I/O cluster incorporates two I/O modules, four RX modules, two TX modules, and a buffer module. In turn, each I/O module contains one Input Register (InReg), one Output Register (OutReg), and one Enable Register (EnReg) (Figure 2-5).

Figure 2-5 • I/O Cluster Interface

# Using an I/O Register

To access the I/O registers, registers must be instantiated in the netlist and then connected to the I/Os. Usage of each I/O register (register combining) is individually controlled and can be selected/deselected using the PinEditor tool in the Designer software. I/O register combining can also be controlled at the device level, affecting all I/Os. Please note, the I/O register option is deselected by default in any given design.<sup>4</sup>

In addition, Designer software provides a global option to enable/disable the usage of registers in the I/Os. This option is design-specific. The setting for each individual I/O overrides this global option. Furthermore, the *global set fuse* option in the Designer software, when checked, causes all I/O registers to output logic High at device power-up.

<sup>4.</sup> Please note that register combining for multi fanout nets is not supported.

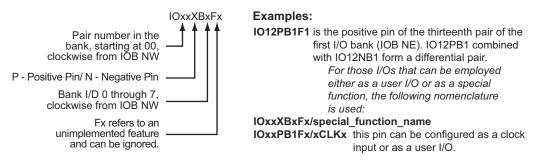

# **User I/O Naming Conventions**

Due to the complex and flexible nature of the Axcelerator family's user I/Os, a naming scheme is used to show the details of the I/O. The naming scheme explains to which bank an I/O belongs, as well as the pairing and pin polarity for differential I/Os (Figure 2-7).

Figure 2-8 • General Naming Schemes

# I/O Standard Electrical Specifications

#### Table 2-18 • Input Capacitance

| Symbol          | Parameter                              | Conditions           | Min. | Max. | Units |

|-----------------|----------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub> | Input Capacitance                      | VIN = 0, f = 1.0 MHz |      | 10   | pF    |

| CINCLK          | Input Capacitance on HCLK and RCLK Pin | VIN = 0, f = 1.0 MHz |      | 10   | pF    |

#### Table 2-19 • I/O Input Rise Time and Fall Time\*

| Input Buffer | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.) |

|--------------|-----------------------------|-----------------------------|

| LVTTL        | No Requirement              | 50 ns                       |

| LVCMOS 2.5V  | No Requirement              | 50 ns                       |

| LVCMOS 1.8V  | No Requirement              | 50 ns                       |

| LVCMOS 1.5V  | No Requirement              | 50 ns                       |

| PCI          | No Requirement              | 50 ns                       |

| PCIX         | No Requirement              | 50 ns                       |

| GTL+         | No Requirement              | 50 ns                       |

| HSTL         | No Requirement              | 50 ns                       |

| SSTL2        | No Requirement              | 50 ns                       |

| HSTL3        | No Requirement              | 50 ns                       |

| LVDS         | No Requirement              | 50 ns                       |

| LVPECL       | No Requirement              | 50 ns                       |

Note: \*Input Rise/Fall time applies to all inputs, be it clock or data. Inputs have to ramp up/down linearly, in a monotonic way. Glitches or a plateau may cause double clocking. They must be avoided. For output rise/fall time, refer to the IBIS models for extraction.

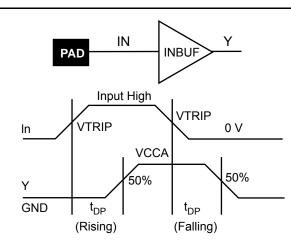

### Figure 2-9 • Input Buffer Delays

# Microsemi

**Detailed Specifications**

#### Table 2-22 • 3.3 V LVTTL I/O Module

### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C (continued)

|                     |                                                                           | –2 S | peed | –1 S | peed | Std S | Speed |       |

|---------------------|---------------------------------------------------------------------------|------|------|------|------|-------|-------|-------|

| Parameter           | Description                                                               | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| LVTTL Outp          | out Drive Strength =3 (16 mA) / High Slew Rate                            |      |      |      |      |       |       |       |

| t <sub>DP</sub>     | Input Buffer                                                              |      | 1.68 |      | 1.92 |       | 2.26  | ns    |

| t <sub>PY</sub>     | Output Buffer                                                             |      | 3.12 |      | 3.56 |       | 4.18  | ns    |

| t <sub>ENZL</sub>   | Enable to Pad Delay through the Output Buffer—Z to Low                    |      | 3.54 |      | 4.04 |       | 4.75  | ns    |

| t <sub>ENZH</sub>   | Enable to Pad Delay through the Output Buffer—Z to High                   |      | 2.78 |      | 3.17 |       | 3.72  | ns    |

| t <sub>ENLZ</sub>   | Enable to Pad Delay through the Output Buffer—Low to Z                    |      | 1.91 |      | 1.93 |       | 1.93  | ns    |

| t <sub>ENHZ</sub>   | Enable to Pad Delay through the Output Buffer—High to Z                   |      | 2.58 |      | 2.59 |       | 2.60  | ns    |

| t <sub>IOCLKQ</sub> | Sequential Clock-to-Q for the I/O Input Register                          |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>IOCLKY</sub> | Clock-to-output Y for the I/O Output Register and the I/O Enable Register |      | 0.67 |      | 0.77 |       | 0.90  | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                         |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                                       |      | 0.26 |      | 0.30 |       | 0.35  | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                           |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                         |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                             | 0.39 |      | 0.39 |      | 0.39  |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                                  | 0.37 |      | 0.37 |      | 0.37  |       | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                                |      | 0.13 |      | 0.15 |       | 0.17  | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                                 |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                                   |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                                  |      | 0.23 |      | 0.27 |       | 0.31  | ns    |

# **Routed Clocks**

The routed clock (CLK) is a low-skew network that can drive the clock inputs of all sequential modules in the device (logically equivalent to the HCLK), but has the added flexibility in that it can drive the S0 (Enable), S1, PSET, and CLR input of a register (R-cells and I/O registers) as well as any of the inputs of any C-cell in the device. This allows CLKs to be used not only as clocks, but also for other global signals or high fanout nets. All four CLKs are available everywhere on the chip.

# Timing Characteristics

#### Table 2-75 • AX125 Routed Array Clock Networks Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                    |                          | -2 S | peed | –1 S | peed | Std S | Speed |       |

|--------------------|--------------------------|------|------|------|------|-------|-------|-------|

| Parameter          | Description              | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| Routed Arra        | ay Clock Networks        |      |      |      |      |       |       |       |

| t <sub>RCKL</sub>  | Input Low to High        |      | 3.08 |      | 3.50 |       | 4.12  | ns    |

| t <sub>RCKH</sub>  | Input High to Low        |      | 3.13 |      | 3.56 |       | 4.19  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High | 0.57 |      | 0.64 |      | 0.75  |       | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low  | 0.52 |      | 0.59 |      | 0.69  |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew             |      | 0.35 |      | 0.39 |       | 0.46  | ns    |

| t <sub>RP</sub>    | Minimum Period           | 1.15 |      | 1.31 |      | 1.54  |       | ns    |

| t <sub>RMAX</sub>  | Maximum Frequency        |      | 870  |      | 763  |       | 649   | MHz   |

# Table 2-76 • AX250 Routed Array Clock Networks

#### Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}$ C

|                    |                          | -2 S | speed | –1 S | peed | Std S | Speed |       |

|--------------------|--------------------------|------|-------|------|------|-------|-------|-------|

| Parameter          | Description              | Min. | Max.  | Min. | Max. | Min.  | Max.  | Units |

| Routed Arra        | ay Clock Networks        |      |       |      |      |       |       |       |

| t <sub>RCKL</sub>  | Input Low to High        |      | 2.52  |      | 2.87 |       | 3.37  | ns    |

| t <sub>RCKH</sub>  | Input High to Low        |      | 2.59  |      | 2.95 |       | 3.47  | ns    |

| t <sub>RPWH</sub>  | Minimum Pulse Width High | 0.57 |       | 0.64 |      | 0.75  |       | ns    |

| t <sub>RPWL</sub>  | Minimum Pulse Width Low  | 0.52 |       | 0.59 |      | 0.69  |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew             |      | 0.35  |      | 0.39 |       | 0.46  | ns    |

| t <sub>RP</sub>    | Minimum Period           | 1.15 |       | 1.31 |      | 1.54  |       | ns    |

| t <sub>RMAX</sub>  | Maximum Frequency        |      | 870   |      | 763  |       | 649   | MHz   |

# **Embedded Memory**

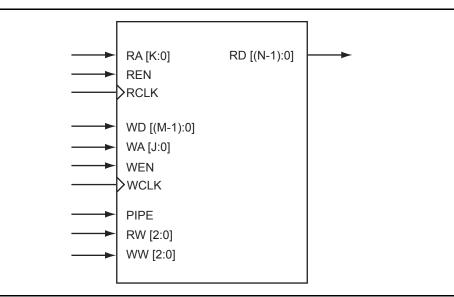

The AX architecture provides extensive, high-speed memory resources to the user. Each 4,608 bit block of RAM contains its own embedded FIFO controller, allowing the user to configure each block as either RAM or FIFO.

To meet the needs of high performance designs, the memory blocks operate in synchronous mode for both read and write operations. However, the read and write clocks are completely independent, and each may operate up to and above 500 MHz.

No additional core logic resources are required to cascade the address and data buses when cascading different RAM blocks. Dedicated routing runs along each column of RAM to facilitate cascading.

The AX memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY). Since read and write operations can occur asynchronously to one another, special control circuitry is included to prevent metastability, overflow, and underflow. A block diagram of the memory module is illustrated in Figure 2-57.

During RAM operation, read (RA) and write (WA) addresses are sourced by user logic and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes. Enables with programmable polarity are provided to create upper address bits for cascading up to 16 memory blocks. When cascading memory blocks, the bussed signals WA, WD, WEN, RA, RD, and REN are internally linked to eliminate external routing congestion.

Figure 2-57 • Axcelerator Memory Module

#### Table 2-89 • One RAM Block

# Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = $70^{\circ}\text{C}$

|                      |                               | -2 S | peed | -1 S | peed | Std S | Speed |       |

|----------------------|-------------------------------|------|------|------|------|-------|-------|-------|

| Parameter            | Description                   | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| Write Mode           |                               |      |      |      |      |       |       |       |

| t <sub>WDASU</sub>   | Write Data Setup vs. WCLK     |      | 1.08 |      | 1.23 |       | 1.45  | ns    |

| t <sub>WDAHD</sub>   | Write Data Hold vs. WCLK      |      | 0.22 |      | 0.25 |       | 0.30  | ns    |

| t <sub>WADSU</sub>   | Write Address Setup vs. WCLK  |      | 1.08 |      | 1.23 |       | 1.45  | ns    |

| t <sub>WADHD</sub>   | Write Address Hold vs. WCLK   |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>WENSU</sub>   | Write Enable Setup vs. WCLK   |      | 1.08 |      | 1.23 |       | 1.45  | ns    |

| t <sub>WENHD</sub>   | Write Enable Hold vs. WCLK    |      | 0.22 |      | 0.25 |       | 0.30  | ns    |

| t <sub>wcкн</sub>    | WCLK Minimum High Pulse Width | 0.75 |      | 0.75 |      | 0.75  |       | ns    |

| t <sub>WCLK</sub>    | WCLK Minimum Low Pulse Width  | 0.88 |      | 0.88 |      | 0.88  |       | ns    |

| t <sub>WCKP</sub>    | WCLK Minimum Period           | 1.63 |      | 1.63 |      | 1.63  |       | ns    |

| Read Mode            |                               |      |      |      |      |       |       |       |

| t <sub>RADSU</sub>   | Read Address Setup vs. RCLK   |      | 0.81 |      | 0.92 |       | 1.08  | ns    |

| t <sub>RADHD</sub>   | Read Address Hold vs. RCLK    |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>RENSU</sub>   | Read Enable Setup vs. RCLK    |      | 0.81 |      | 0.92 |       | 1.08  | ns    |

| t <sub>RENHD</sub>   | Read Enable Hold vs. RCLK     |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-to-OUT (Pipelined)       |      | 1.32 |      | 1.51 |       | 1.77  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-to-OUT (Non-Pipelined)   |      | 2.16 |      | 2.46 |       | 2.90  | ns    |

| t <sub>RCLKH</sub>   | RCLK Minimum High Pulse Width | 0.77 |      | 0.77 |      | 0.77  |       | ns    |

| t <sub>RCLKL</sub>   | RCLK Minimum Low Pulse Width  | 0.93 |      | 0.93 |      | 0.93  |       | ns    |

| t <sub>RCKP</sub>    | RCLK Minimum Period           | 1.70 |      | 1.70 |      | 1.70  |       | ns    |

Note: Timing data for this single block RAM has a depth of 4,096. For all other combinations, use Microsemi's timing software.

|                      |                               | –2 S | peed | –1 S | peed | Std S | Speed |       |

|----------------------|-------------------------------|------|------|------|------|-------|-------|-------|

| Parameter            | Description                   | Min. | Max. | Min. | Max. | Min.  | Max.  | Units |

| Write Mode           |                               |      |      |      |      |       |       |       |

| t <sub>WDASU</sub>   | Write Data Setup vs. WCLK     |      | 1.39 |      | 1.59 |       | 1.87  | ns    |

| t <sub>WDAHD</sub>   | Write Data Hold vs. WCLK      |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>WADSU</sub>   | Write Address Setup vs. WCLK  |      | 1.39 |      | 1.59 |       | 1.87  | ns    |

| t <sub>WADHD</sub>   | Write Address Hold vs. WCLK   |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>WENSU</sub>   | Write Enable Setup vs. WCLK   |      | 1.39 |      | 1.59 |       | 1.87  | ns    |

| t <sub>WENHD</sub>   | Write Enable Hold vs. WCLK    |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>WCKH</sub>    | WCLK Minimum High Pulse Width | 0.75 |      | 0.75 |      | 0.75  |       | ns    |

| t <sub>WCLK</sub>    | WCLK Minimum Low Pulse Width  | 1.76 |      | 1.76 |      | 1.76  |       | ns    |

| t <sub>WCKP</sub>    | WCLK Minimum Period           | 2.51 |      | 2.51 |      | 2.51  |       | ns    |

| Read Mode            |                               |      |      |      |      |       |       |       |

| t <sub>RADSU</sub>   | Read Address Setup vs. RCLK   |      | 1.71 |      | 1.94 |       | 2.28  | ns    |

| t <sub>RADHD</sub>   | Read Address Hold vs. RCLK    |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>RENSU</sub>   | Read Enable Setup vs. RCLK    |      | 1.71 |      | 1.94 |       | 2.28  | ns    |

| t <sub>RENHD</sub>   | Read Enable Hold vs. RCLK     |      | 0.00 |      | 0.00 |       | 0.00  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)       |      | 1.43 |      | 1.63 |       | 1.92  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Non-Pipelined)   |      | 2.26 |      | 2.58 |       | 3.03  | ns    |

| t <sub>RCLKH</sub>   | RCLK Minimum High Pulse Width | 0.73 |      | 0.73 |      | 0.73  |       | ns    |

| t <sub>RCLKL</sub>   | RCLK Minimum Low Pulse Width  | 1.89 |      | 1.89 |      | 1.89  |       | ns    |

| t <sub>RCKP</sub>    | RCLK Minimum Period           | 2.62 |      | 2.62 |      | 2.62  |       | ns    |

# Table 2-90 • Two RAM Blocks Cascaded

Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> =  $70^{\circ}$ C

Note: Timing data for these two cascaded RAM blocks uses a depth of 8,192. For all other combinations, use Microsemi's timing software.

# TDO

TDO is normally tristated, and it is active only when the TAP controller is in the "Shift\_DR" state or "Shift\_IR" state. The least significant bit of the selected register (i.e. IR or DR) is clocked out to TDO first by the falling edge of TCK.

### **TAP Controller**

The TAP Controller is compliant with the IEEE Standard 1149.1. It is a state machine of 16 states that controls the Instruction Register (IR) and the Data Registers (such as BSR, IDCODE, USRCODE, BYPASS, etc.). The TAP Controller steps into one of the states depending on the sequence of TMS at the rising edges of TCK.

### Instruction Register (IR)

The IR has five bits (IR4 to IR0). At the TRST state, IR is reset to IDCODE. Each time when IR is selected, it goes through "select IR-Scan," "Capture-IR," "Shift-IR," all the way through "Update-IR." When there is no test error, the first five data bits coming out of TDO during the "Shift-IR" will be "10111". If a test error occurs, the last three bits will contain one to three zeroes corresponding to negatively asserted signals: "TDO\_ERRORB," "PROBA\_ERRORB," and "PROBB\_ERRORB." The error(s) will be erased when the TAP is at the "Update-IR" or the TRST state. When in user mode start-up sequence, if the micro-probe has not been used, the "PROBA\_ERRORB" is used as a "Power-up done successfully" flag.

# Data Registers (DRs)

Data registers are distributed throughout the chip. They store testing/programming vectors. The MSB of a data register is connected to TDI, while the LSB is connected to TDO. There are different types of data registers. Descriptions of the main registers are as follow:

1. IDCODE:

The IDCODE is a 20-bit hard coded JTAG Silicon Signature. It is a hardwired device ID code, which contains the Microsemi identity, part number, and version number in a specific JTAG format.

2. USERCODE:

The USERCODE is a 33-bit programmable register. However, only 20 bits are allocated to use as JTAG Silicon Signature. It is a supplementary identity code for the user to program information to distinguish different programmed parts. USERCODE fuses will read out as "zeroes" when not programmed, so only the "1" bits need to be programmed.

3. Boundary-Scan Register (BSR):

Each I/O contains three Boundary-Scan Cells. Each cell has a shift register bit, a latch, and two MUXes. The boundary-scan cells are used for the Output-enable (E), Output (O), and Input (I) registers. The bit order of the boundary-scan cells for each of them is E-O-I. The boundary-scan cells are then chained serially to form the Boundary-Scan Register (BSR). The length of the BSR is the number of I/Os in the die multiplied by three.

4. Bypass Register (BYR):

This is the "1-bit" register. It is used to shorten the TDI-TDO serial chain in board-level testing to only one bit per device not being tested. It is also selected for all "reserved" or unused instructions.

### Probing

Internal activities of the JTAG interface can be observed via the Silicon Explorer II probes: "PRA," "PRB," "PRC," and "PRD."

# **Special Fuses**

#### Security

Microsemi antifuse FPGAs, with FuseLock technology, offer the highest level of design security available in a programmable logic device. Since antifuse FPGAs are live-at power-up, there is no bitstream that can be intercepted, and no bitstream or programming data is ever downloaded to the device during power-up, thus protecting against device cloning. In addition, special security fuses are hidden

| 1       | FG256         |                |  |  |  |  |

|---------|---------------|----------------|--|--|--|--|

| AX250 F | Pin<br>Number | AX250 Function |  |  |  |  |

| VCC     | L9            | VCCA           |  |  |  |  |

| VCC     | N3            | VCCA           |  |  |  |  |

| VCC     | P14           | VCCA           |  |  |  |  |

| VCC     | C7            | VCCPLA         |  |  |  |  |

| VCC     | D6            | VCCPLB         |  |  |  |  |

| VCC     | A10           | VCCPLC         |  |  |  |  |

| VCC     | D10           | VCCPLD         |  |  |  |  |

| VCC     | P10           | VCCPLE         |  |  |  |  |

| VCC     | N11           | VCCPLF         |  |  |  |  |

| VCC     | T7            | VCCPLG         |  |  |  |  |

| VCC     | N7            | VCCPLH         |  |  |  |  |

| VCON    | A11           | VCCDA          |  |  |  |  |

| VCON    | A2            | VCCDA          |  |  |  |  |

| VCON    | C13           | VCCDA          |  |  |  |  |

| VCON    | D9            | VCCDA          |  |  |  |  |

| VCON    | H1            | VCCDA          |  |  |  |  |

| VCON    | J15           | VCCDA          |  |  |  |  |

| VCON    | N14           | VCCDA          |  |  |  |  |

| VCON    | N8            | VCCDA          |  |  |  |  |

| VPU     | P4            | VCCDA          |  |  |  |  |

|         | R11           | VCCDA          |  |  |  |  |

|         | R5            | VCCDA          |  |  |  |  |

|         | E6            | VCCIB0         |  |  |  |  |

|         | E7            | VCCIB0         |  |  |  |  |

|         | E8            | VCCIB0         |  |  |  |  |

|         | E10           | VCCIB1         |  |  |  |  |

|         | E11           | VCCIB1         |  |  |  |  |

|         | E9            | VCCIB1         |  |  |  |  |

|         | F12           | VCCIB2         |  |  |  |  |

|         | G12           | VCCIB2         |  |  |  |  |

|         | H12           | VCCIB2         |  |  |  |  |

|         | J12           | VCCIB3         |  |  |  |  |

|         | K12           | VCCIB3         |  |  |  |  |

|         | L12           | VCCIB3         |  |  |  |  |

|         | M10           | VCCIB4         |  |  |  |  |

| AX250 Function | Pin<br>Number |

|----------------|---------------|

| VCCIB4         | M11           |

| VCCIB4         | M9            |

| VCCIB5         | M6            |

| VCCIB5         | M7            |

| VCCIB5         | M8            |

| VCCIB6         | J5            |

| VCCIB6         | K5            |

| VCCIB6         | L5            |

| VCCIB7         | F5            |

| VCCIB7         | G5            |

| VCCIB7         | H5            |

| VCOMPLA        | A7            |

| VCOMPLB        | D7            |

| VCOMPLC        | B9            |

| VCOMPLD        | D11           |

| VCOMPLE        | T10           |

| VCOMPLF        | N10           |

| VCOMPLG        | R8            |

| VCOMPLH        | N6            |

| VPUMP          | A14           |

FG256

Package Pin Assignments

| FG324          |               |  |  |

|----------------|---------------|--|--|

| AX125 Function | Pin<br>Number |  |  |

| VCCIB5         | N7            |  |  |

| VCCIB5         | N8            |  |  |

| VCCIB5         | N9            |  |  |

| VCCIB6         | K6            |  |  |

| VCCIB6         | L6            |  |  |

| VCCIB6         | M6            |  |  |

| VCCIB7         | G6            |  |  |

| VCCIB7         | H6            |  |  |

| VCCIB7         | J6            |  |  |

| VCOMPLA        | B8            |  |  |

| VCOMPLB        | E8            |  |  |

| VCOMPLC        | C10           |  |  |

| VCOMPLD        | E12           |  |  |

| VCOMPLE        | U11           |  |  |

| VCOMPLF        | P11           |  |  |

| VCOMPLG        | Т9            |  |  |

| VCOMPLH        | P7            |  |  |

| VPUMP          | B15           |  |  |

Package Pin Assignments

| FG484           |               | FG484            |               | FG484           |               |

|-----------------|---------------|------------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function  | Pin<br>Number | AX1000 Function | Pin<br>Number |

| Bank 0          | 1             | IO29NB0F2        | B12           | IO51PB1F4       | D22           |

| IO01NB0F0       | E3            | IO29PB0F2        | B11           | IO52NB1F4       | E16           |

| IO01PB0F0       | D3            | IO30NB0F2/HCLKAN | E11           | IO52PB1F4       | E15           |

| IO02NB0F0       | E7            | IO30PB0F2/HCLKAP | E10           | IO57NB1F5       | E21           |

| IO02PB0F0       | E6            | IO31NB0F2/HCLKBN | D12           | IO57PB1F5       | D21           |

| IO05NB0F0       | D2            | IO31PB0F2/HCLKBP | D11           | IO60NB1F5       | G16           |

| IO05PB0F0       | E2            | Bank 1           |               | IO60PB1F5       | G15           |

| IO06NB0F0       | C5            | IO32NB1F3/HCLKCN | F13           | IO61NB1F5       | D18           |

| IO06PB0F0       | C4            | IO32PB1F3/HCLKCP | F12           | IO61PB1F5       | E17           |

| IO12NB0F1       | D7            | IO33NB1F3/HCLKDN | E14           | IO63NB1F5       | E20           |

| IO12PB0F1       | D6            | IO33PB1F3/HCLKDP | E13           | IO63PB1F5       | D20           |

| IO13NB0F1       | B5            | IO34NB1F3        | C13           | Bank 2          |               |

| IO13PB0F1       | B4            | IO34PB1F3        | C12           | IO64NB2F6       | F18           |

| IO14NB0F1       | E9            | IO37NB1F3        | B14           | IO64PB2F6       | F17           |

| IO14PB0F1       | E8            | IO37PB1F3        | B13           | IO67NB2F6       | F19           |

| IO15NB0F1       | C7            | IO38NB1F3        | A16           | IO67PB2F6       | E19           |

| IO15PB0F1       | C6            | IO38PB1F3        | A15           | IO68NB2F6       | J16           |

| IO16NB0F1       | A5            | IO40NB1F3        | C15           | IO68PB2F6       | H16           |

| IO16PB0F1       | A4            | IO42NB1F4        | A18           | IO70NB2F6       | J17           |

| IO17NB0F1       | B7            | IO42PB1F4        | A17           | IO70PB2F6       | H17           |

| IO17PB0F1       | B6            | IO43NB1F4        | B16           | IO74NB2F7       | J18           |

| IO18NB0F1       | A7            | IO43PB1F4        | B15           | IO74PB2F7       | H18           |

| IO18PB0F1       | A6            | IO44NB1F4        | B18           | IO75NB2F7       | G20           |

| IO19NB0F1       | C9            | IO44PB1F4        | B17           | IO75PB2F7       | F20           |

| IO19PB0F1       | C8            | IO45NB1F4        | B19           | IO79NB2F7       | H19           |

| IO20NB0F1       | D9            | IO45PB1F4        | A19           | IO79PB2F7       | G19           |

| IO20PB0F1       | D8            | IO46NB1F4        | C19           | IO80NB2F7       | L16           |

| IO21NB0F1       | B9            | IO46PB1F4        | C18           | IO80PB2F7       | K16           |

| IO21PB0F1       | B8            | IO48NB1F4        | F15           | IO84NB2F7       | L17           |

| IO22NB0F2       | A9            | IO48PB1F4        | F14           | IO84PB2F7       | K17           |

| IO22PB0F2       | A8            | IO49NB1F4        | D16           | IO85NB2F8       | G21           |

| IO23NB0F2       | B10           | IO49PB1F4        | D15           | IO85PB2F8       | F21           |

| IO23PB0F2       | A10           | IO50NB1F4        | C17           | IO86NB2F8       | G22           |

| IO26NB0F2       | A14           | IO50PB1F4        | C16           | IO86PB2F8       | F22           |

| IO26PB0F2       | A13           | IO51NB1F4        | E22           | IO87NB2F8       | J20           |

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| IO51PB1F4       | J20           | IO69NB1F6       | C27           | IO86NB2F8       | J28           |

| IO52NB1F4       | B20           | IO69PB1F6       | C26           | IO86PB2F8       | J27           |

| IO52PB1F4       | A20           | IO70NB1F6       | H24           | IO87NB2F8       | M25           |

| IO53NB1F4       | F20           | IO70PB1F6       | G24           | IO87PB2F8       | L25           |

| IO53PB1F4       | E20           | IO71NB1F6       | H23           | IO88NB2F8       | L26           |

| IO54NB1F5       | B21           | IO71PB1F6       | G23           | IO88PB2F8       | K26           |

| IO54PB1F5       | A21           | IO72NB1F6       | B28           | IO89NB2F8       | G31           |

| IO55NB1F5       | K21           | IO72PB1F6       | A28           | IO89PB2F8       | F31           |

| IO55PB1F5       | J21           | IO73NB1F6       | E26           | IO90NB2F8       | H29           |

| IO56NB1F5       | D21           | IO73PB1F6       | E25           | IO90PB2F8       | G29           |

| IO56PB1F5       | C21           | IO74NB1F6       | F26           | IO91NB2F8       | K28           |

| IO57NB1F5       | G22           | IO74PB1F6       | F25           | IO91PB2F8       | K27           |

| IO57PB1F5       | G21           | IO75NB1F6       | K25           | IO92NB2F8       | J30           |

| IO58NB1F5       | E22           | IO75PB1F6       | K24           | IO92PB2F8       | H30           |

| IO58PB1F5       | E21           | IO76NB1F7       | D27           | IO93NB2F8       | L28           |

| IO59NB1F5       | D22           | IO76PB1F7       | D26           | IO93PB2F8       | L27           |

| IO59PB1F5       | C22           | IO77NB1F7       | B29           | IO94NB2F8       | K29           |

| IO60NB1F5       | B23           | IO77PB1F7       | A29           | IO94PB2F8       | J29           |

| IO60PB1F5       | A23           | IO78NB1F7       | D28           | IO95NB2F8       | K31           |

| IO61NB1F5       | H22           | IO78PB1F7       | C28           | IO95PB2F8       | J31           |

| IO61PB1F5       | H21           | IO79NB1F7       | H25           | IO96NB2F9       | J32           |

| IO62NB1F5       | C24           | IO79PB1F7       | G25           | IO96PB2F9       | H32           |

| IO62PB1F5       | C23           | IO80NB1F7       | F27           | IO97NB2F9       | M27           |

| IO63NB1F5       | F23           | IO80PB1F7       | E27           | IO97PB2F9       | M26           |

| IO63PB1F5       | F22           | IO81NB1F7       | J25           | IO98NB2F9       | L30           |

| IO64NB1F6       | B24           | IO81PB1F7       | J24           | IO98PB2F9       | K30           |

| IO64PB1F6       | A24           | IO82NB1F7       | D29           | IO99NB2F9       | N25           |

| IO65NB1F6       | J22           | IO82PB1F7       | C29           | IO99PB2F9       | N26           |

| IO65PB1F6       | K22           | IO83NB1F7       | H26           | IO100NB2F9      | M29           |

| IO66NB1F6       | B25           | IO83PB1F7       | G26           | IO100PB2F9      | L29           |

| IO66PB1F6       | A25           | IO84NB1F7       | F28           | IO101NB2F9      | L33           |

| IO67NB1F6       | K23           | IO84PB1F7       | E28           | IO101PB2F9      | L32           |

| IO67PB1F6       | J23           | IO85NB1F7       | H27           | IO102NB2F9      | K34           |

| IO68NB1F6       | F24           | IO85PB1F7       | G27           | IO102PB2F9      | K33           |

| IO68PB1F6       | E24           | Bank 2          |               | IO103NB2F9      | N28           |

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| IO155PB3F14     | AC29          | IO172PB4F16     | AH27          | IO190NB4F17     | AH22          |

| IO156NB3F14     | AE30          | IO173NB4F16     | AJ27          | IO190PB4F17     | AH23          |

| IO156PB3F14     | AD30          | IO173PB4F16     | AJ28          | IO191NB4F17     | AJ23          |

| IO157NB3F14     | AC26          | IO174NB4F16     | AL27          | IO191PB4F17     | AJ24          |

| IO157PB3F14     | AB26          | IO174PB4F16     | AL28          | IO192NB4F17     | AG21          |

| IO158NB3F14     | AH33          | IO175NB4F16     | AM28          | IO192PB4F17     | AG22          |

| IO158PB3F14     | AG33          | IO175PB4F16     | AM29          | IO193NB4F18     | AP23          |

| IO159NB3F14     | AD27          | IO176NB4F16     | AG25          | IO193PB4F18     | AP24          |

| IO159PB3F14     | AC27          | IO176PB4F16     | AG26          | IO194NB4F18     | AN22          |

| IO160NB3F14     | AG32          | IO177NB4F16     | AK26          | IO194PB4F18     | AN23          |

| IO160PB3F14     | AF32          | IO177PB4F16     | AK27          | IO195NB4F18     | AM23          |

| IO161NB3F15     | AG31          | IO178NB4F16     | AF25          | IO195PB4F18     | AL23          |

| IO161PB3F15     | AF31          | IO178PB4F16     | AE25          | IO196NB4F18     | AF21          |

| IO162NB3F15     | AF29          | IO179NB4F16     | AP28          | IO196PB4F18     | AF22          |

| IO162PB3F15     | AE29          | IO179PB4F16     | AN28          | IO197NB4F18     | AL22          |

| IO163NB3F15     | AE28          | IO180NB4F16     | AJ25          | IO197PB4F18     | AM22          |

| IO163PB3F15     | AD28          | IO180PB4F16     | AJ26          | IO198NB4F18     | AE21          |

| IO164NB3F15     | AG30          | IO181NB4F17     | AM26          | IO198PB4F18     | AE22          |

| IO164PB3F15     | AF30          | IO181PB4F17     | AM27          | IO199NB4F18     | AJ21          |

| IO165NB3F15     | AE26          | IO182NB4F17     | AF24          | IO199PB4F18     | AJ22          |

| IO165PB3F15     | AD26          | IO182PB4F17     | AE24          | IO200NB4F18     | AK21          |

| IO166NB3F15     | AJ30          | IO183NB4F17     | AH24          | IO200PB4F18     | AK22          |

| IO166PB3F15     | AH30          | IO183PB4F17     | AH25          | IO201NB4F18     | AM21          |

| IO167NB3F15     | AG28          | IO184NB4F17     | AG23          | IO201PB4F18     | AL21          |

| IO167PB3F15     | AF28          | IO184PB4F17     | AG24          | IO202NB4F18     | AE20          |

| IO168NB3F15     | AF27          | IO185NB4F17     | AL25          | IO202PB4F18     | AD20          |

| IO168PB3F15     | AE27          | IO185PB4F17     | AL26          | IO203NB4F19     | AN21          |

| IO169NB3F15     | AH29          | IO186NB4F17     | AP25          | IO203PB4F19     | AP21          |

| IO169PB3F15     | AG29          | IO186PB4F17     | AP26          | IO204NB4F19     | AP20          |

| IO170NB3F15     | AD25          | IO187NB4F17     | AK24          | IO204PB4F19     | AN20          |

| IO170PB3F15     | AC25          | IO187PB4F17     | AK25          | IO205NB4F19     | AN19          |

| Bank 4          | <u> </u>      | IO188NB4F17     | AF23          | IO205PB4F19     | AP19          |

| IO171NB4F16     | AP29          | IO188PB4F17     | AE23          | IO206NB4F19     | AG20          |

| IO171PB4F16     | AN29          | IO189NB4F17     | AN24          | IO206PB4F19     | AF20          |

| IO172NB4F16     | AH26          | IO189PB4F17     | AM24          | IO207NB4F19     | AL19          |

Package Pin Assignments

| AX500 Function Number<br>VCCDA 346<br>VCCIB0 321<br>VCCIB0 333 | er |

|----------------------------------------------------------------|----|

| VCCIB0 321                                                     |    |

|                                                                |    |

| VCCIB0 333                                                     |    |

|                                                                |    |

| VCCIB0 344                                                     |    |

| VCCIB1 273                                                     |    |

| VCCIB1 285                                                     |    |

| VCCIB1 297                                                     |    |

| VCCIB2 227                                                     |    |

| VCCIB2 239                                                     |    |

| VCCIB2 245                                                     |    |

| VCCIB2 257                                                     | ٦  |

| VCCIB3 185                                                     |    |

| VCCIB3 197                                                     |    |

| VCCIB3 203                                                     |    |

| VCCIB3 215                                                     |    |

| VCCIB4 144                                                     |    |

| VCCIB4 156                                                     |    |

| VCCIB4 168                                                     |    |

| VCCIB5 96                                                      |    |

| VCCIB5 108                                                     |    |

| VCCIB5 120                                                     |    |

| VCCIB6 50                                                      |    |

| VCCIB6 62                                                      |    |

| VCCIB6 68                                                      |    |

| VCCIB6 80                                                      |    |

| VCCIB7 8                                                       |    |

| VCCIB7 20                                                      |    |

| VCCIB7 26                                                      |    |

| VCCIB7 38                                                      |    |

| VCCPLA 317                                                     |    |

| VCCPLB 315                                                     |    |

| VCCPLC 303                                                     |    |

| VCCPLD 301                                                     |    |

| VCCPLE 140                                                     |    |

| VCCPLF 138                                                     |    |

| CQ352          |               |

|----------------|---------------|

| AX500 Function | Pin<br>Number |

| VCCPLG         | 126           |

| VCCPLH         | 124           |

| VCOMPLA        | 318           |

| VCOMPLB        | 316           |

| VCOMPLC        | 304           |

| VCOMPLD        | 302           |

| VCOMPLE        | 141           |

| VCOMPLF        | 139           |

| VCOMPLG        | 127           |

| VCOMPLH        | 125           |

| VPUMP          | 267           |

| CG624           | CG624         |                 |               | CG624           |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |

| IO194NB6F18     | Y3            | IO215PB6F20     | V4            | IO237NB7F22     | N8            |

| IO194PB6F18     | AA3           | IO216NB6F20     | P8            | IO237PB7F22     | N7            |

| IO195NB6F18     | V6            | IO216PB6F20     | R3            | IO238NB7F22     | M5            |

| IO195PB6F18     | W4            | IO217NB6F20     | P7            | IO239NB7F22     | L6            |

| IO197NB6F18     | R5            | IO217PB6F20     | R7            | IO239PB7F22     | L5            |

| IO197PB6F18     | U3            | IO219NB6F20     | R4            | IO240NB7F22     | M4            |

| IO198NB6F18     | P6            | IO219PB6F20     | T4            | IO241NB7F22     | L7            |

| IO199NB6F18     | Y5            | IO220NB6F20     | P2            | IO241PB7F22     | M7            |

| IO199PB6F18     | W5            | IO220PB6F20     | R2            | IO242NB7F22     | J3            |

| IO200NB6F18     | V3            | IO221NB6F20     | N4            | IO243NB7F22     | M9            |

| IO200PB6F18     | W3            | IO221PB6F20     | P4            | IO243PB7F22     | M8            |

| IO201NB6F18     | T7            | IO223NB6F20     | M2            | IO244NB7F22     | P9            |

| IO201PB6F18     | U7            | IO223PB6F20     | N2            | IO244PB7F22     | N6            |

| IO202NB6F18     | V2            | IO224NB6F20     | N3            | IO245NB7F22     | K8            |

| IO203NB6F19     | W2            | IO224PB6F20     | P3            | IO245PB7F22     | L8            |

| IO203PB6F19     | Y2            | Bank 7          | 1             | IO246NB7F22     | F3            |

| IO204NB6F19     | AA1           | IO225NB7F21     | J2            | IO246PB7F22     | E3            |

| IO204PB6F19     | AB1           | IO225PB7F21     | J1            | IO247NB7F23     | K7            |

| IO205NB6F19     | R6            | IO226PB7F21     | G2            | IO247PB7F23     | K6            |

| IO205PB6F19     | Т6            | IO227NB7F21     | H3            | IO248NB7F23     | D2            |

| IO206NB6F19     | W1            | IO227PB7F21     | H2            | IO249NB7F23     | G4            |

| IO206PB6F19     | Y1            | IO229NB7F21     | K2            | IO249PB7F23     | G3            |

| IO207NB6F19     | T2            | IO229PB7F21     | L2            | IO251NB7F23     | N10           |

| IO207PB6F19     | U2            | IO230NB7F21     | K1            | IO251PB7F23     | N9            |

| IO208NB6F19     | T1            | IO230PB7F21     | L1            | IO253NB7F23     | H4            |

| IO208PB6F19     | U1            | IO231NB7F21     | E2            | IO253PB7F23     | J4            |

| IO209NB6F19     | AA2           | IO231PB7F21     | F2            | IO255NB7F23     | J6            |

| IO209PB6F19     | AB2           | IO232NB7F21     | F1            | IO255PB7F23     | J5            |

| IO210NB6F19     | P5            | IO232PB7F21     | G1            | IO257NB7F23     | H5            |

| IO211NB6F19     | M1            | IO233NB7F21     | L3            | IO257PB7F23     | H6            |

| IO211PB6F19     | N1            | IO233PB7F21     | M3            | Dedicated I/O   |               |

| IO212NB6F19     | P1            | IO234NB7F21     | D1            | GND             | K5            |

| IO212PB6F19     | R1            | IO234PB7F21     | E1            | GND A1          |               |

| IO213NB6F19     | R8            | IO235NB7F21     | K4            | GND             | A2            |

| IO213PB6F19     | Т8            | IO235PB7F21     | L4            | GND             | A24           |

| IO215NB6F20     | U4            | IO236NB7F22     | M6            | GND             | A25           |