# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4224                                                        |

| Number of Logic Elements/Cells | -                                                           |

| Total RAM Bits                 | 55296                                                       |

| Number of I/O                  | 115                                                         |

| Number of Gates                | 250000                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/ax250-pqg208 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# User I/Os<sup>2</sup>

#### Introduction

The Axcelerator family features a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) with its bank-selectable I/Os. Table 2-8 on page 2-12 contains the I/O standards supported by the Axcelerator family, and Table 2-10 on page 2-12 compares the features of the different I/O standards.

Each I/O provides programmable slew rates, drive strengths, and weak pull-up and weak pull-down circuits. The slew rate setting is effective for both rising and falling edges.

I/O standards, except 3.3 V PCI and 3.3 V PCI-X, are capable of hot insertion. 3.3 V PCI and 3.3 V PCI-X are 5 V tolerant with the aid of an external resistor.

The input buffer has an optional user-configurable delay element. The element can reduce or eliminate the hold time requirement for input signals registered within the I/O cell. The value for the delay is set on a bank-wide basis. Note that the delay WILL be a function of process variations as well as temperature and voltage changes.

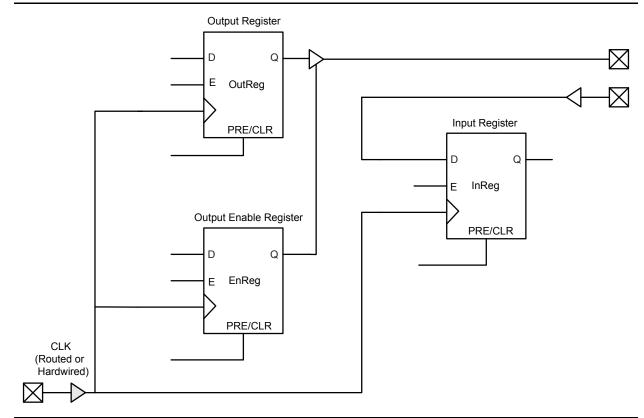

Each I/O includes three registers: an input (InReg), an output (OutReg), and an enable register (EnReg). I/Os are organized into banks, and there are eight banks per device—two per side (Figure 2-6 on page 2-18). Each I/O bank has a common VCCI, the supply voltage for its I/Os.

For voltage-referenced I/Os, each bank also has a common reference-voltage bus, VREF. While VREF must have a common voltage for an entire I/O bank, its location is user-selectable. In other words, any user I/O in the bank can be selected to be a VREF.

The location of the VREF pin should be selected according to the following rules:

- Any pin that is assigned as a VREF can control a maximum of eight user I/O pad locations in each direction (16 total maximum) within the same I/O bank.

- I/O pad locations listed as no connects are counted as part of the 16 maximum. In many cases, this leads to fewer than eight user I/O package pins in each direction being controlled by a VREF pin.

- Dedicated I/O pins such as GND and VCCI are counted as part of the 16.

- The two user I/O pads immediately adjacent on each side of the VREF pin (four in total) may only be used as inputs. The exception is when there is a VCCI/GND pair separating the VREF pin and the user I/O pad location.

- The user does not need to assign VREF pins for OUTBUF and TRIBUF. VREF pins are needed only for input and bidirectional I/Os.

The differential amplifier supply voltage VCCDA should be connected to 3.3 V.

A user can gain access to the various I/O standards in three ways:

- Instantiate specific library macros that represent the desired specific standard.

- Use generic I/O macros and then use Designer's PinEditor to specify the desired I/O standards (please note that this is not applicable to differential standards).

- A combination of the first two methods.

Refer to the I/O Features in Axcelerator Family Devices application note and the Antifuse Macro Library Guide for more details.

<sup>2.</sup> Do not use an external resister to pull the I/O above  $V_{CCI}$  for a higher logic "1" voltage level. The desired higher logic "1" voltage level will be degraded due to a small I/O current, which exists when the I/O is pulled up above  $V_{CCI}$ .

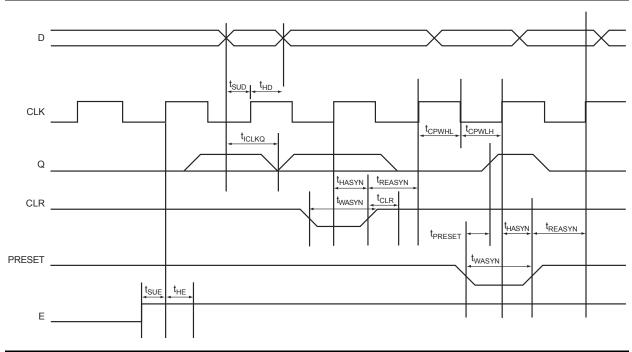

# **I/O Module Timing Characteristics**

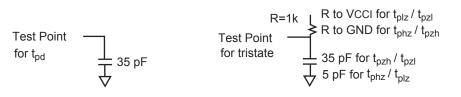

Figure 2-11 • Timing Model

**Detailed Specifications**

# 1.5 V LVCMOS (JESD8-11)

Low-Voltage Complementary Metal-Oxide Semiconductor for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.5 V applications. It uses a 3.3 V tolerant CMOS input buffer and a push-pull output buffer.

#### Table 2-29 • DC Input and Output Levels

|         | VIL       | VII       | H       | VOL     | VOH        | IOL  | IOH   |

|---------|-----------|-----------|---------|---------|------------|------|-------|

| Min., V | Max., V   | Min., V   | Max., V | Max., V | Min., V    | mA   | mA    |

| -0.3    | 0.35 VCCI | 0.65 VCCI | 3.6     | 0.4     | VCCI – 0.4 | 8 mA | –8 mA |

## AC Loadings

#### Table 2-30 • AC Test Loads

#### Table 2-31 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ) (V) | C <sub>load</sub> (pF) |

|---------------|----------------|----------------------|----------------|------------------------|

| 0             | 1.5            | 0.5V <sub>CCI</sub>  | N/A            | 35                     |

Note: \* Measuring Point = VTRIP

# **Timing Characteristics**

# *Table 2-61* • LVPECL I/O Module Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V, T<sub>J</sub> = 70°C

|                     |                                                                   | –2 S | peed | –1 S | peed | Std S | peed |       |

|---------------------|-------------------------------------------------------------------|------|------|------|------|-------|------|-------|

| Parameter           | Description                                                       | Min. | Max. | Min. | Max. | Min.  | Max. | Units |

| LVPECL Ou           | itput Module Timing                                               |      |      |      |      |       |      |       |

| t <sub>DP</sub>     | Input Buffer                                                      |      | 1.66 |      | 1.89 |       | 2.22 | ns    |

| t <sub>PY</sub>     | Output Buffer                                                     |      | 2.24 |      | 2.55 |       | 3.00 | ns    |

| t <sub>ICLKQ</sub>  | Clock-to-Q for the I/O input register                             |      | 0.67 |      | 0.77 |       | 0.90 | ns    |

| t <sub>oclkq</sub>  | Clock-to-Q for the IO output register and the I/O enable register |      | 0.67 |      | 0.77 |       | 0.90 | ns    |

| t <sub>SUD</sub>    | Data Input Set-Up                                                 |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

| t <sub>SUE</sub>    | Enable Input Set-Up                                               |      | 0.26 |      | 0.30 |       | 0.35 | ns    |

| t <sub>HD</sub>     | Data Input Hold                                                   |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>HE</sub>     | Enable Input Hold                                                 |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>CPWHL</sub>  | Clock Pulse Width High to Low                                     | 0.39 |      | 0.39 |      | 0.39  |      | ns    |

| t <sub>CPWLH</sub>  | Clock Pulse Width Low to High                                     | 0.39 |      | 0.39 |      | 0.39  |      | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                                          | 0.37 |      | 0.37 |      | 0.37  |      | ns    |

| t <sub>REASYN</sub> | Asynchronous Recovery Time                                        |      | 0.13 |      | 0.15 |       | 0.17 | ns    |

| t <sub>HASYN</sub>  | Asynchronous Removal Time                                         |      | 0.00 |      | 0.00 |       | 0.00 | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                                           |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                                          |      | 0.23 |      | 0.27 |       | 0.31 | ns    |

**Detailed Specifications**

# **Carry-Chain Logic**

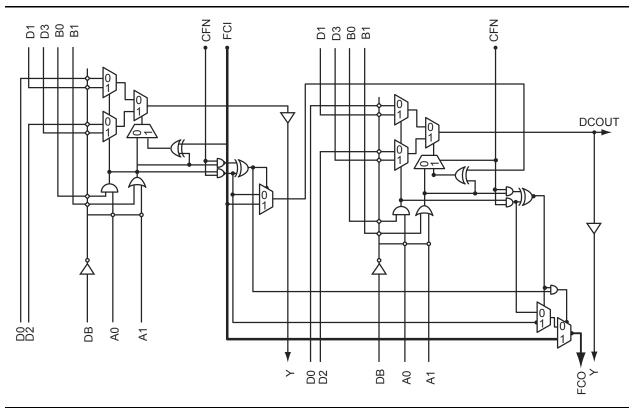

The Axcelerator dedicated carry-chain logic offers a very compact solution for implementing arithmetic functions without sacrificing performance.

To implement the carry-chain logic, two C-cells in a Cluster are connected together so the FCO (i.e. carry out) for the two bits is generated in a carry look-ahead scheme to achieve minimum propagation delay from the FCI (i.e. carry in) into the two-bit Cluster. The two-bit carry logic is shown in Figure 2-29.

The FCI of one C-cell pair is driven by the FCO of the C-cell pair immediately above it. Similarly, the FCO of one C-cell pair, drives the FCI input of the C-cell pair immediately below it (Figure 1-4 on page 1-3 and Figure 2-30 on page 2-57).

The carry-chain logic is selected via the CFN input. When carry logic is not required, this signal is deasserted to save power. Again, this configuration is handled automatically for the user through Microsemi's macro library.

The signal propagation delay between two C-cells in the carry-chain sequence is 0.1 ns.

# **Routing Specifications**

# **Routing Resources**

The routing structure found in Axcelerator devices enables any logic module to be connected to any other logic module while retaining high performance. There are multiple paths and routing resources that can be used to route one logic module to another, both within a SuperCluster and elsewhere on the chip.

There are four primary types of routing within the AX architecture: DirectConnect, CarryConnect, FastConnect, and Vertical and Horizontal Routing.

#### DirectConnect

DirectConnects provide a high-speed connection between an R-cell and its adjacent C-cell (Figure 2-35). This connection can be made from DCOUT of the C-cell to DCIN of the R-cell by configuring of the S1 line of the R-cell. This provides a connection that does not require an antifuse and has a delay of less than 0.1 ns.

#### Figure 2-35 • DirectConnect and CarryConnect

### CarryConnect

CarryConnects are used to build carry chains for arithmetic functions (Figure 2-35). The FCO output of the right C-cell of a two-C-cell Cluster drives the FCI input of the left C-cell in the two-C-cell Cluster immediately below it. This pattern continues down both sides of each SuperCluster column.

Similar to the DirectConnects, CarryConnects can be built without an antifuse connection. This connection has a delay of less than 0.1 ns from the FCO of one two-C-cell cluster to the FCI of the two-C-cell cluster immediately below it (see the "Carry-Chain Logic" section on page 2-56 for more information).

#### FastConnect

For high-speed routing of logic signals, FastConnects can be used to build a short distance connection using a single antifuse (Figure 2-36 on page 2-62). FastConnects provide a maximum delay of 0.3 ns. The outputs of each logic module connect directly to the Output Tracks within a SuperCluster. Signals on the Output Tracks can then be routed through a single antifuse connection to drive the inputs of logic modules either within one SuperCluster or in the SuperCluster immediately below it.

single-ended, or voltage-referenced standard. The [H]CLKxN pad can only be used as a differential pair with [H]CLKxP.

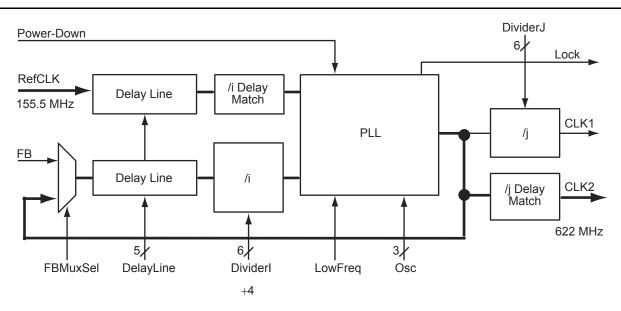

The block marked "/i Delay Match" is a fixed delay equal to that of the i divider. The "/j Delay Match" block has the same function as its j divider counterpart.

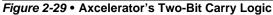

# **Functional Description**

Figure 2-48 on page 2-75 illustrates a block diagram of the PLL. The PLL contains two dividers, i and j, that allow frequency scaling of the clock signal:

- The i divider in the feedback path allows multiplication of the input clock by integer factors ranging from 1 to 64, and the resultant frequency is available at the output of the PLL block.

- The j divider divides the PLL output by integer factors ranging from 1 to 64, and the divided clock is available at CLK1.

- The two dividers together can implement any combination of multiplication and division up to a maximum frequency of 1 GHz on CLK1. Both the CLK1 and CLK2 outputs have a fixed 50/50 duty cycle.

- The output frequencies of the two clocks are given by the following formulas (f<sub>REF</sub> is the reference clock frequency):

$f_{CLK1} = f_{REF} * (DividerI) / (DividerJ)$

$f_{CLK2} = f_{REF} * (DividerI)$

FQ 5

EQ 4

CLK2 provides the PLL output directly—without division

The input and output frequency ranges are selected by LowFreq and Osc(2:0), respectively. These functions and their possible values are detailed in Table 2-80 on page 2-77.

The delay lines shown in Figure 2-48 on page 2-75 are programmable. The feedback clock path can be delayed (using the five DelayLine bits) relative to the reference clock (or vice versa) by up to 3.75 ns in increments of 250 ps. Table 2-80 on page 2-77 describes the usage of these bits. The delay increments are independent of frequency, so this results in phase changes that vary with frequency. The delay value is highly dependent on  $V_{CC}$  and the speed grade.

Figure 2-49 is a logical diagram of the various control signals to the PLL and shows how the PLL interfaces with the global and routing networks of the FPGA. Note that not all signals are user-accessible. These non-user-accessible signals are used by the place-and-route tool to control the configuration of the PLL. The user gains access to these control signals either based upon the connections built in the user's design or through the special macros (Table 2-84 on page 2-81) inserted into the design. For example, connecting the macro PLLOUT to CLK2 will control the OUTSEL signal.

Note: Not all signals are available to the user.

Figure 2-49 • PLL Logical Interface

| CLK1                       | CLK2                     |

|----------------------------|--------------------------|

| CLK1                       | Routed net               |

| CLK1                       | Unused                   |

| CLK2                       | CLK1                     |

| CLK2                       | Routed net               |

| CLK2                       | Both CLK1 and routed net |

| CLK2                       | Unused                   |

| Unused                     | CLK1                     |

| Unused                     | Routed net               |

| Unused                     | Both CLK1 and routed net |

| Unused                     | Unused                   |

| Routed net                 | CLK1                     |

| Routed net                 | Unused                   |

| Both CLK1 and CLK2         | Routed net               |

| Both CLK1 and CLK2         | Unused                   |

| Both CLK1 and routed net   | Unusable                 |

| Both CLK2 and routed net   | CLK1                     |

| Both CLK2 and routed net   | Unused                   |

| CLK1, CLK2, and routed net | Unusable                 |

#### Table 2-83 • South PLL Connections

Note: Designer software currently does not support all of these connections. Only exclusive connections where one output connects to a single net are supported at this time (e.g., CLK1 driving both CLK1 and CLK2 is not supported).

# **Sample Implementations**

## Frequency Synthesis

Figure 2-53 illustrates an example where the PLL is used to multiply a 155.5 MHz external clock up to 622 MHz. Note that the same PLL schematic could use an external 350 MHz clock, which is divided down to 155 MHz by the FPGA internal logic.

Figure 2-54 illustrates the PLL using both dividers to synthesize a 133 MHz output clock from a 155 MHz input reference clock. The input frequency of 155 MHz is multiplied by 6 and divided by 7, giving a CLK1 output frequency of 132.86 MHz. When dividers are used, a given ratio can be generated in multiple ways, allowing the user to stay within the operating frequency ranges of the PLL.

Figure 2-53 • Using the PLL 155.5 MHz In, 622 MHz Out

### Adjustable Clock Delay

Figure 2-55 illustrates using the PLL to delay the reference clock by employing one of the adjustable delay lines. In this case, the output clock is delayed relative to the reference clock. Delaying the reference clock relative to the output clock is accomplished by using the delay line in the feedback path.

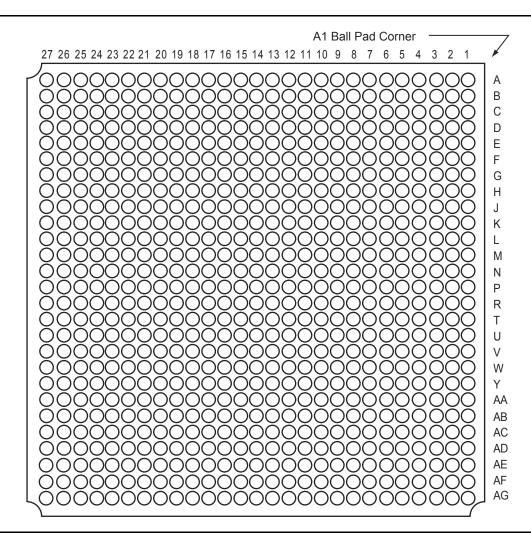

# BG729

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

# Microsemi

| BG729           |               | BG729           |               |  |

|-----------------|---------------|-----------------|---------------|--|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |  |

| VCCIB0          | B4            | VCCIB4          | W17           |  |

| VCCIB0          | C4            | VCCIB4          | W18           |  |

| VCCIB0          | J10           | VCCIB5          | AE4           |  |

| VCCIB0          | J11           | VCCIB5          | AF4           |  |

| VCCIB0          | J12           | VCCIB5          | AG4           |  |

| VCCIB0          | K12           | VCCIB5          | V12           |  |

| VCCIB0          | K13           | VCCIB5          | V13           |  |

| VCCIB1          | A24           | VCCIB5          | W10           |  |

| VCCIB1          | B24           | VCCIB5          | W11           |  |

| VCCIB1          | C24           | VCCIB5          | W12           |  |

| VCCIB1          | J16           | VCCIB6          | AD1           |  |

| VCCIB1          | J17           | VCCIB6          | AD2           |  |

| VCCIB1          | J18           | VCCIB6          | AD3           |  |

| VCCIB1          | K15           | VCCIB6          | R10           |  |

| VCCIB1          | K16           | VCCIB6          | T10           |  |

| VCCIB2          | D25           | VCCIB6          | Т9            |  |

| VCCIB2          | D26           | VCCIB6          | U9            |  |

| VCCIB2          | D27           | VCCIB6          | V9            |  |

| VCCIB2          | K19           | VCCIB7          | D1            |  |

| VCCIB2          | L19           | VCCIB7          | D2            |  |

| VCCIB2          | M18           | VCCIB7          | D3            |  |

| VCCIB2          | M19           | VCCIB7          | K9            |  |

| VCCIB2          | N18           | VCCIB7          | L9            |  |

| VCCIB3          | AD25          | VCCIB7          | M10           |  |

| VCCIB3          | AD26          | VCCIB7          | M9            |  |

| VCCIB3          | AD27          | VCCIB7          | N10           |  |

| VCCIB3          | R18           | VCOMPLA         | B13           |  |

| VCCIB3          | T18           | VCOMPLB         | A14           |  |

| VCCIB3          | T19           | VCOMPLC         | A15           |  |

| VCCIB3          | U19           | VCOMPLD         | J15           |  |

| VCCIB3          | V19           | VCOMPLE         | AG15          |  |

| VCCIB4          | AE24          | VCOMPLF         | W15           |  |

| VCCIB4          | AF24          | VCOMPLG         | AC14          |  |

| VCCIB4          | AG24          | VCOMPLH         | W13           |  |

| VCCIB4          | V15           | VPUMP           | D24           |  |

| VCCIB4          | V16           |                 |               |  |

| VCCIB4          | W16           |                 |               |  |

| FG256-Pin FBGA |               | FG256-Pin FI   | BGA           | FG256-Pin FI   | BGA           |

|----------------|---------------|----------------|---------------|----------------|---------------|

| AX125 Function | Pin<br>Number | AX125 Function | Pin<br>Number | AX125 Function | Pin<br>Number |

| Bank 6         |               | IO81NB7F7      | C2            | GND            | M12           |

| IO60NB6F6      | L4            | IO81PB7F7      | B1            | GND            | M5            |

| IO60PB6F6      | M4            | IO82NB7F7      | D2            | GND            | P13           |

| IO61NB6F6      | L3            | IO82PB7F7      | D3            | GND            | P3            |

| IO61PB6F6      | M3            | IO83NB7F7      | E3            | GND            | R15           |

| IO63NB6F6      | P2            | IO83PB7F7      | F3            | GND            | R2            |

| IO63PB6F6      | N2            | Dedicated I    | /0            | GND            | T1            |

| IO64NB6F6      | J4            | VCCDA          | E4            | GND            | T16           |

| IO64PB6F6      | K4            | GND            | A1            | GND/LP         | D4            |

| IO65NB6F6      | N1            | GND            | A16           | NC             | A11           |

| IO65PB6F6      | P1            | GND            | B15           | NC             | R11           |

| IO67NB6F6      | L2            | GND            | B2            | NC             | R5            |

| IO67PB6F6      | M2            | GND            | D15           | PRA            | D8            |

| IO69NB6F6      | L1            | GND            | E12           | PRB            | C8            |

| IO69PB6F6      | M1            | GND            | E5            | PRC            | N9            |

| IO70NB6F6      | J3            | GND            | F11           | PRD            | P9            |

| IO70PB6F6      | K3            | GND            | F6            | ТСК            | D5            |

| IO71NB6F6      | J2            | GND            | G10           | TDI            | C6            |

| IO71PB6F6      | K2            | GND            | G7            | TDO            | C4            |

| Bank 7         |               | GND            | G8            | TMS            | C3            |

| IO72NB7F7      | J1            | GND            | G9            | TRST           | C5            |

| IO72PB7F7      | K1            | GND            | H10           | VCCA           | D14           |

| IO73NB7F7      | G2            | GND            | H7            | VCCA           | F10           |

| IO73PB7F7      | H2            | GND            | H8            | VCCA           | F4            |

| IO74NB7F7      | G3            | GND            | H9            | VCCA           | F7            |

| IO74PB7F7      | H3            | GND            | J10           | VCCA           | F8            |

| IO75NB7F7      | E1            | GND            | J7            | VCCA           | F9            |

| IO75PB7F7      | F1            | GND            | J8            | VCCA           | G11           |

| IO76NB7F7      | G1            | GND            | J9            | VCCA           | G6            |

| IO77NB7F7      | E2            | GND            | K10           | VCCA           | H11           |

| IO77PB7F7      | F2            | GND            | K7            | VCCA           | H6            |

| IO78NB7F7      | G4            | GND            | K8            | VCCA           | J11           |

| IO78PB7F7      | H4            | GND            | К9            | VCCA           | J6            |

| IO79NB7F7      | C1            | GND            | L11           | VCCA           | K11           |

| IO79PB7F7      | D1            | GND            | L6            | VCCA           | K6            |

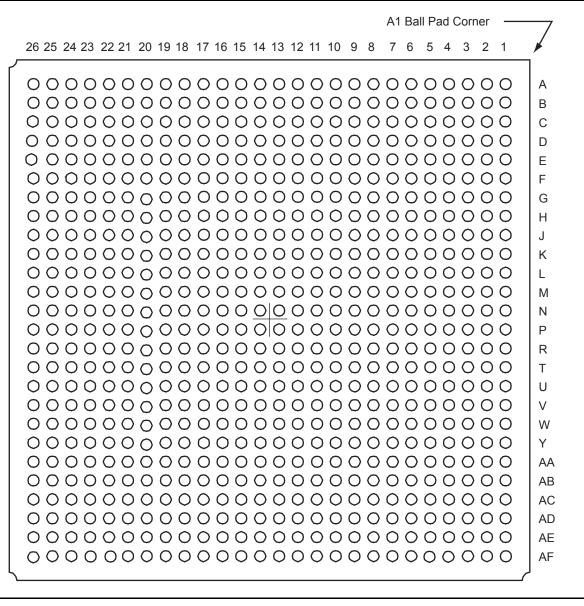

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

| FG676         |               | FG676          |               |

|---------------|---------------|----------------|---------------|

| X500 Function | Pin<br>Number | AX500 Function | Pin<br>Number |

| VCCIB3        | T19           | VCCIB7         | L8            |

| VCCIB3        | U19           | VCCIB7         | M8            |

| VCCIB3        | U20           | VCCIB7         | N8            |

| VCCIB3        | V19           | VCCPLA         | E12           |

| VCCIB3        | V20           | VCCPLB         | F13           |

| VCCIB3        | W20           | VCCPLC         | E15           |

| VCCIB4        | W14           | VCCPLD         | G14           |

| VCCIB4        | W15           | VCCPLE         | AF15          |

| VCCIB4        | W16           | VCCPLF         | AA14          |

| VCCIB4        | W17           | VCCPLG         | AF12          |

| VCCIB4        | W18           | VCCPLH         | AB13          |

| VCCIB4        | Y17           | VCOMPLA        | D12           |

| VCCIB4        | Y18           | VCOMPLB        | G13           |

| VCCIB4        | Y19           | VCOMPLC        | D15           |

| VCCIB5        | W10           | VCOMPLD        | F14           |

| VCCIB5        | W11           | VCOMPLE        | AD15          |

| VCCIB5        | W12           | VCOMPLF        | AB14          |

| VCCIB5        | W13           | VCOMPLG        | AD12          |

| VCCIB5        | W9            | VCOMPLH        | Y13           |

| VCCIB5        | Y10           | VPUMP          | E22           |

| VCCIB5        | Y8            |                |               |

| VCCIB5        | Y9            |                |               |

| VCCIB6        | P8            |                |               |

| VCCIB6        | R8            |                |               |

| VCCIB6        | Т8            |                |               |

| VCCIB6        | U7            |                |               |

| VCCIB6        | U8            |                |               |

| VCCIB6        | V7            |                |               |

| VCCIB6        | V8            |                |               |

| VCCIB6        | W7            |                |               |

| VCCIB7        | H7            |                |               |

| VCCIB7        | J7            |                |               |

| VCCIB7        | J8            |                |               |

| VCCIB7        | K7            |                |               |

| VCCIB7        | K8            |                |               |

| FG896           | FG896         |                 |               |

|-----------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |

| VCCIB2          | L22           | VCCIB5          | AK3           |

| VCCIB2          | M21           | VCCIB6          | AA9           |

| VCCIB2          | M22           | VCCIB6          | AH1           |

| VCCIB2          | N21           | VCCIB6          | AH2           |

| VCCIB2          | P21           | VCCIB6          | T10           |

| VCCIB2          | R21           | VCCIB6          | U10           |

| VCCIB3          | AA22          | VCCIB6          | V10           |

| VCCIB3          | AH29          | VCCIB6          | W10           |

| VCCIB3          | AH30          | VCCIB6          | W9            |

| VCCIB3          | T21           | VCCIB6          | Y10           |

| VCCIB3          | U21           | VCCIB6          | Y9            |

| VCCIB3          | V21           | VCCIB7          | C1            |

| VCCIB3          | W21           | VCCIB7          | C2            |

| VCCIB3          | W22           | VCCIB7          | K9            |

| VCCIB3          | Y21           | VCCIB7          | L10           |

| VCCIB3          | Y22           | VCCIB7          | L9            |

| VCCIB4          | AA16          | VCCIB7          | M10           |

| VCCIB4          | AA17          | VCCIB7          | M9            |

| VCCIB4          | AA18          | VCCIB7          | N10           |

| VCCIB4          | AA19          | VCCIB7          | P10           |

| VCCIB4          | AA20          | VCCIB7          | R10           |

| VCCIB4          | AB19          | VCOMPLA         | F14           |

| VCCIB4          | AB20          | VCOMPLB         | J15           |

| VCCIB4          | AB21          | VCOMPLC         | F17           |

| VCCIB4          | AJ28          | VCOMPLD         | H16           |

| VCCIB4          | AK28          | VCOMPLE         | AF17          |

| VCCIB5          | AA11          | VCOMPLF         | AD16          |

| VCCIB5          | AA12          | VCOMPLG         | AF14          |

| VCCIB5          | AA13          | VCOMPLH         | AB15          |

| VCCIB5          | AA14          | VPUMP           | G24           |

| VCCIB5          | AA15          |                 | •             |

| VCCIB5          | AB10          |                 |               |

| VCCIB5          | AB11          |                 |               |

| VCCIB5          | AB12          |                 |               |

| VCCIB5          | AJ3           |                 |               |

|                 | •             |                 |               |

| FG1152          |               | FG1152          |               | FG1152           |               |

|-----------------|---------------|-----------------|---------------|------------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function  | Pin<br>Number |

| Bank 0          |               | IO17NB0F1       | F12           | IO34PB0F3        | D14           |

| IO00NB0F0       | D6            | IO17PB0F1       | F11           | IO35NB0F3        | A15           |

| IO00PB0F0       | C6            | IO18NB0F1       | E11           | IO35PB0F3        | B15           |

| IO01NB0F0       | H10           | IO18PB0F1       | E10           | IO36NB0F3        | B16           |

| IO01PB0F0       | H9            | IO19NB0F1       | F13           | IO36PB0F3        | A16           |

| IO02NB0F0       | F8            | IO19PB0F1       | G13           | IO37NB0F3        | G16           |

| IO02PB0F0       | G8            | IO20NB0F1       | A10           | IO37PB0F3        | G15           |

| IO03NB0F0       | A6            | IO20PB0F1       | A9            | IO38NB0F3        | D16           |

| IO03PB0F0       | B6            | IO21NB0F1       | K14           | IO38PB0F3        | C16           |

| IO04NB0F0       | C7            | IO21PB0F1       | K13           | IO39NB0F3        | K16           |

| IO04PB0F0       | D7            | IO22NB0F2       | B11           | IO39PB0F3        | L16           |

| IO05NB0F0       | K10           | IO22PB0F2       | B10           | IO40NB0F3        | D17           |

| IO05PB0F0       | J10           | IO23NB0F2       | C12           | IO40PB0F3        | C17           |

| IO06NB0F0       | F9            | IO23PB0F2       | C11           | IO41NB0F3/HCLKAN | E16           |

| IO06PB0F0       | G9            | IO24NB0F2       | A12           | IO41PB0F3/HCLKAP | F16           |

| IO07NB0F0       | F10           | IO24PB0F2       | A11           | IO42NB0F3/HCLKBN | G17           |

| IO07PB0F0       | G10           | IO25NB0F2       | H14           | IO42PB0F3/HCLKBP | F17           |

| IO08NB0F0       | E9            | IO25PB0F2       | J14           | Bank 1           |               |

| IO08PB0F0       | E8            | IO26NB0F2       | D13           | IO43NB1F4/HCLKCN | G19           |

| IO09NB0F0       | J11           | IO26PB0F2       | D12           | IO43PB1F4/HCLKCP | G18           |

| IO09PB0F0       | K11           | IO27NB0F2       | F14           | IO44NB1F4/HCLKDN | E19           |

| IO10NB0F0       | C8            | IO27PB0F2       | G14           | IO44PB1F4/HCLKDP | F19           |

| IO10PB0F0       | D8            | IO28NB0F2       | E14           | IO45NB1F4        | C18           |

| IO11NB0F0       | K12           | IO28PB0F2       | E13           | IO45PB1F4        | D18           |

| IO11PB0F0       | J12           | IO29NB0F2       | B13           | IO46NB1F4        | A18           |

| IO12NB0F1       | G11           | IO29PB0F2       | B12           | IO46PB1F4        | B18           |

| IO12PB0F1       | H11           | IO30NB0F2       | C14           | IO47NB1F4        | K19           |

| IO13NB0F1       | G12           | IO30PB0F2       | C13           | IO47PB1F4        | L19           |

| IO13PB0F1       | H12           | IO31NB0F2       | H15           | IO48NB1F4        | C19           |

| IO14NB0F1       | A7            | IO31PB0F2       | J15           | IO48PB1F4        | D19           |

| IO14PB0F1       | B7            | IO32NB0F2       | A14           | IO49NB1F4        | K20           |

| IO15NB0F1       | H13           | IO32PB0F2       | B14           | IO49PB1F4        | L20           |

| IO15PB0F1       | J13           | IO33NB0F2       | K15           | IO50NB1F4        | A19           |

| IO16NB0F1       | C9            | IO33PB0F2       | L15           | IO50PB1F4        | B19           |

| IO16PB0F1       | D9            | IO34NB0F3       | D15           | IO51NB1F4        | H20           |

| CQ352          |               |  |  |  |

|----------------|---------------|--|--|--|

| AX250 Function | Pin<br>Number |  |  |  |

| VCCDA          | 346           |  |  |  |

| VCCIB0         | 321           |  |  |  |

| VCCIB0         | 333           |  |  |  |

| VCCIB0         | 344           |  |  |  |

| VCCIB1         | 273           |  |  |  |

| VCCIB1         | 285           |  |  |  |

| VCCIB1         | 297           |  |  |  |

| VCCIB2         | 227           |  |  |  |

| VCCIB2         | 239           |  |  |  |

| VCCIB2         | 245           |  |  |  |

| VCCIB2         | 257           |  |  |  |

| VCCIB3         | 185           |  |  |  |

| VCCIB3         | 197           |  |  |  |

| VCCIB3         | 203           |  |  |  |

| VCCIB3         | 215           |  |  |  |

| VCCIB4         | 144           |  |  |  |

| VCCIB4         | 156           |  |  |  |

| VCCIB4         | 168           |  |  |  |

| VCCIB5         | 96            |  |  |  |

| VCCIB5         | 108           |  |  |  |

| VCCIB5         | 120           |  |  |  |

| VCCIB6         | 50            |  |  |  |

| VCCIB6         | 62            |  |  |  |

| VCCIB6         | 68            |  |  |  |

| VCCIB6         | 80            |  |  |  |

| VCCIB7         | 8             |  |  |  |

| VCCIB7         | 20            |  |  |  |

| VCCIB7         | 26            |  |  |  |

| VCCIB7         | 38            |  |  |  |

| VCCPLA         | 317           |  |  |  |

| VCCPLB         | 315           |  |  |  |

| VCCPLC         | 303           |  |  |  |

| VCCPLD         | 301           |  |  |  |

| VCCPLE         | 140           |  |  |  |

| VCCPLF         | 138           |  |  |  |

| CQ352          |               |  |  |  |  |

|----------------|---------------|--|--|--|--|

| AX250 Function | Pin<br>Number |  |  |  |  |

| VCCPLG         | 126           |  |  |  |  |

| VCCPLH         | 124           |  |  |  |  |

| VCOMPLA        | 318           |  |  |  |  |

| VCOMPLB        | 316           |  |  |  |  |

| VCOMPLC        | 304           |  |  |  |  |

| VCOMPLD        | 302           |  |  |  |  |

| VCOMPLE        | 141           |  |  |  |  |

| VCOMPLF        | 139           |  |  |  |  |

| VCOMPLG        | 127           |  |  |  |  |

| VCOMPLH        | 125           |  |  |  |  |

| VPUMP          | 267           |  |  |  |  |

3-102

| CG624           |               | CG624            |               | CG624           |               |

|-----------------|---------------|------------------|---------------|-----------------|---------------|

| AX1000 Function | Pin<br>Number | AX1000 Function  | Pin<br>Number | AX1000 Function | Pin<br>Number |

| Bank 0          |               | IO23NB0F2        | E11           | IO42NB1F4       | G21           |

| IO00NB0F0       | F8            | IO23PB0F2        | F11           | IO42PB1F4       | G20           |

| IO00PB0F0       | F7            | IO24NB0F2        | D7            | IO43NB1F4       | A16           |

| IO02NB0F0       | G7            | IO24PB0F2        | E7            | IO43PB1F4       | A15           |

| IO02PB0F0       | G6            | IO25PB0F2        | B12           | IO44NB1F4       | A20           |

| IO04NB0F0       | E9            | IO26NB0F2        | H11           | IO44PB1F4       | A19           |

| IO04PB0F0       | D8            | IO26PB0F2        | G11           | IO45NB1F4       | B17           |

| IO06NB0F0       | G9            | IO27NB0F2        | C11           | IO45PB1F4       | B16           |

| IO06PB0F0       | G8            | IO27PB0F2        | B8            | IO46NB1F4       | G17           |

| IO07PB0F0       | B6            | IO28NB0F2        | J13           | IO46PB1F4       | H17           |

| IO08NB0F0       | F10           | IO28PB0F2        | K13           | IO47NB1F4       | A17           |

| IO08PB0F0       | F9            | IO29NB0F2        | J8            | IO48NB1F4       | C19           |

| IO09PB0F0       | C7            | IO29PB0F2        | J7            | IO48PB1F4       | C18           |

| IO10NB0F0       | H8            | IO30NB0F2/HCLKAN | G13           | IO49NB1F4       | B20           |

| IO10PB0F0       | H7            | IO30PB0F2/HCLKAP | G12           | IO49PB1F4       | B19           |

| IO11NB0F0       | D10           | IO31NB0F2/HCLKBN | C13           | IO50NB1F4       | H20           |

| IO11PB0F0       | D9            | IO31PB0F2/HCLKBP | C12           | IO50PB1F4       | H19           |

| IO12NB0F1       | B5            | Bank 1           |               | IO51NB1F4       | A22           |

| IO12PB0F1       | B4            | IO32NB1F3/HCLKCN | G15           | IO51PB1F4       | A21           |

| IO13NB0F1       | A7            | IO32PB1F3/HCLKCP | G14           | IO52NB1F4       | C21           |

| IO13PB0F1       | A6            | IO33NB1F3/HCLKDN | B14           | IO52PB1F4       | C20           |

| IO14NB0F1       | C9            | IO33PB1F3/HCLKDP | B13           | IO53NB1F4       | B22           |

| IO14PB0F1       | C8            | IO34NB1F3        | G16           | IO53PB1F4       | B21           |

| IO15PB0F1       | B7            | IO34PB1F3        | H16           | IO54NB1F5       | J18           |

| IO16NB0F1       | A5            | IO35NB1F3        | C17           | IO54PB1F5       | J19           |

| IO16PB0F1       | A4            | IO35PB1F3        | B18           | IO55NB1F5       | D18           |

| IO17NB0F1       | A9            | IO36NB1F3        | H18           | IO55PB1F5       | D17           |

| IO17PB0F1       | B9            | IO36PB1F3        | H15           | IO56NB1F5       | F20           |

| IO18NB0F1       | D12           | IO37NB1F3        | H13           | IO56PB1F5       | F19           |

| IO18PB0F1       | D11           | IO38NB1F3        | E15           | IO58NB1F5       | E17           |

| IO20NB0F1       | B11           | IO38PB1F3        | F15           | IO58PB1F5       | F17           |

| IO20PB0F1       | B10           | IO39NB1F3        | D14           | IO60NB1F5       | D20           |

| IO21NB0F1       | A11           | IO39PB1F3        | C14           | IO60PB1F5       | D19           |

| IO21PB0F1       | A10           | IO40NB1F3        | D16           | IO62NB1F5       | E18           |

| IO22NB0F2       | H10           | IO40PB1F3        | D15           | IO62PB1F5       | F18           |

| IO22PB0F2       | H9            | IO41NB1F4        | F16           | IO63NB1F5       | G19           |

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                           | Page                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Revision 8<br>(continued)    | The following changes were made in the "FG676"(AX500) section:   AE2, AE25 Change from NC to GND.   AF2, AF25 Changed from GND to NC   AB4, AF24, C1, C26 Changed from V <sub>CCDA</sub> to V <sub>CCA</sub> AD15 Change from V <sub>CCDA</sub> to V <sub>COMPLE</sub> AD17 Changed from V <sub>COMPLE</sub> to V <sub>CCDA</sub> | 3-37                                     |

|                              | In the "FG896" (AX2000) section, the AK28 changed from VCCIB5 to VCCIB4.                                                                                                                                                                                                                                                          | 3-52                                     |

|                              | The "CQ352" and "CG624" sections are new.                                                                                                                                                                                                                                                                                         | 3-98, 3-115                              |

| Revision 7<br>(Advance v1.6) | All I/O FIFO capability was removed.                                                                                                                                                                                                                                                                                              | n/a                                      |

|                              | Table 1 was updated.                                                                                                                                                                                                                                                                                                              | i                                        |

|                              | Figure 1-9 was updated.                                                                                                                                                                                                                                                                                                           | 1-7                                      |

|                              | Figure 2-5 was updated.                                                                                                                                                                                                                                                                                                           | 2-16                                     |

|                              | The "Using an I/O Register" section was updated.                                                                                                                                                                                                                                                                                  | 2-16                                     |

|                              | The AX250 and AX1000 descriptions were added to the "FG484"section.                                                                                                                                                                                                                                                               | 3-21                                     |

| Revision 6<br>(Advance v1.5) | Table 2-3 was updated.                                                                                                                                                                                                                                                                                                            | 2-2                                      |

|                              | Figure 2-1 was updated.                                                                                                                                                                                                                                                                                                           | 2-8                                      |

|                              | Figure 2-48 was updated.                                                                                                                                                                                                                                                                                                          | 2-75                                     |

|                              | Figure 2-52 was updated.                                                                                                                                                                                                                                                                                                          | 2-82                                     |

| Revision 5<br>(Advance v1.4) | In the "PQ208" table, pin 196 was missing, but it has been added in this version with a function of GND.                                                                                                                                                                                                                          | 3-84                                     |

|                              | The following pins in the "FG484" table for AX500 were changed:<br>Pin G7 is GND/LP<br>Pins AB8, C10, C11, C14, AB16 are NC.                                                                                                                                                                                                      | 3-21                                     |

|                              | The "FG676" table was updated.                                                                                                                                                                                                                                                                                                    | 3-37                                     |

| Revision 4                   | The "Device Resources" section was updated for the CS180.                                                                                                                                                                                                                                                                         | ii                                       |

| (Advance v1.3)               | The "Programmable Interconnect Element" and Figure 1-2 are new.                                                                                                                                                                                                                                                                   | "<br>1-1 and 1-2                         |

|                              | The "CS180" table is new.                                                                                                                                                                                                                                                                                                         | 3-1                                      |

|                              | The "PQ208" tables for the AX500 were updated. The following pins were not<br>defined in the previous version:<br>GND 21<br>IO106PB5F10/CLKHP 71<br>GND 136                                                                                                                                                                       | 3-84                                     |

| Revision 3<br>(Advance v1.2) | Table 1, "Ordering Information", "Device Resources", and the Product Plan table were updated.                                                                                                                                                                                                                                     | i, ii                                    |

|                              | The following figures and tables were updated:<br>Figure 1-3<br>Figure 1-8 (new)<br>Table 2-3<br>Figure 2-2<br>Table 2-8<br>Figure 2-11                                                                                                                                                                                           | 1-2<br>1-6<br>2-2<br>2-9<br>2-12<br>2-23 |

|                              | The "Design Environment" section was updated.                                                                                                                                                                                                                                                                                     | 1-7                                      |

|                              | The "Package Thermal Characteristics" was updated.                                                                                                                                                                                                                                                                                | 2-6                                      |