Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                |

| Number of LABs/CLBs            | 8064                                                                    |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 73728                                                                   |

| Number of I/O                  | 115                                                                     |

| Number of Gates                | 500000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -55°C ~ 125°C (TA)                                                      |

| Package / Case                 | 208-BFQFP                                                               |

| Supplier Device Package        | 208-PQFP (28x28)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/ax500-1pq208m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5 V Tolerance

There are two schemes to achieve 5 V tolerance:

1. 3.3 V PCI and 3.3 V PCI-X are the only I/O standards that directly allow 5 V tolerance. To implement this, an internal clamp diode between the input pad and the VCCI pad is enabled so that the voltage at the input pin is clamped, as shown in EQ 3:

Vinput = VCCI + Vdiode = 3.3 V + 0.7 V = 4.0 V

EQ3

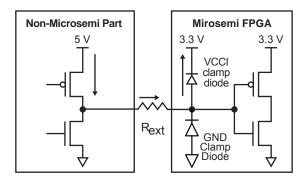

The internal VCCI clamp diode is only enabled while the device is powered on, so the voltage at the input will not be clamped if the VCCI or VCCA are powered off. An external series resistor ( $\sim$ 100  $\Omega$ ) is required between the input pin and the 5 V signal source to limit the current to less than 20 mA (Figure 2-3). The 100  $\Omega$  resistor was chosen to meet the input Tr/Tf requirement (Table 2-19 on page 2-21). The GND clamp diode is available for all I/O standards and always enabled.

Figure 2-3 • Use of an External Resistor for 5 V Tolerance

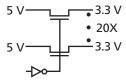

5 V tolerance can also be achieved with 3.3 V I/O standards (3.3 V PCI, 3.3 V PCI-X, and LVTTL) using a bus-switch product (e.g. IDTQS32X2384). This will convert the 5 V signal to a 3.3 V signal with minimum delay (Figure 2-4).

Figure 2-4 • Bus Switch IDTQS32X2384

### Simultaneous Switching Outputs (SSO)

When multiple output drivers switch simultaneously, they induce a voltage drop in the chip/package power distribution. This simultaneous switching momentarily raises the ground voltage within the device relative to the system ground. This apparent shift in the ground potential to a non-zero value is known as simultaneous switching noise (SSN) or more commonly, ground bounce.

SSN becomes more of an issue in high pin count packages and when using high performance devices such as the Axcelerator family. Based upon testing, Microsemi recommends that users not exceed eight simultaneous switching outputs (SSO) per each VCCI/GND pair. To ease this potential burden on designers, Microsemi has designed all of the Axcelerator BGAs<sup>3</sup> to not exceed this limit with the exception of the CS180, which has an I/O to VCCI/GND pair ratio of nine to one.

Please refer to the Simultaneous Switching Noise and Signal Integrity application note for more information.

<sup>3.</sup> The user should note that in Bank 8 of both AX1000-FG484 and AX500-FG484, there are local violations of this 8:1 ratio.

Table 2-13 summarizes the different combinations of voltages and I/O standards that can be used together in the same I/O bank.

Table 2-13 • Legal I/O Usage Matrix

| I/O Standard                           | LVTTL 3.3 V  | LVCMOS 2.5 V | LVCMOS1.8 V | LVCMOS1.5 V (JESD8-11) | 3.3V PCI/PCI-X | GTL + (3.3 V) | GTL + (2.5 V) | HSTL Class I (1. 5V) | SSTL2 Class I & II (2.5 V) | SSTL3 Class I & II (3.3 V) | LVDS (2.5 V) | LVPECL (3.3 V) |

|----------------------------------------|--------------|--------------|-------------|------------------------|----------------|---------------|---------------|----------------------|----------------------------|----------------------------|--------------|----------------|

| LVTTL 3.3 V (VREF=1.0 V)               | ✓            | -            | -           | -                      | ✓              | ✓             | -             | -                    | -                          | -                          | -            | ✓              |

| LVTTL 3.3 V(VREF=1.5 V)                | $\checkmark$ | ı            | -           | ı                      | ✓              | _             | -             | -                    | -                          | ✓                          | -            | ✓              |

| LVCMOS 2.5 V (VREF=1.0 V)              | ı            | ✓            | 1           | -                      | -              | ı             | ✓             | ı                    | ı                          | ı                          | ✓            | _              |

| LVCMOS 2.5 V (VREF=1.25V)              | 1            | ✓            | -           | 1                      | -              | -             | -             | -                    | ✓                          | -                          | ✓            | _              |

| LVCMOS1.8 V                            | -            | -            | <b>√</b>    | -                      | -              | -             | _             | -                    | -                          | -                          | -            | _              |

| LVCMOS1.5 V (VREF = 1.75 V) (JESD8-11) | ı            | 1            | -           | <b>√</b>               | -              | -             | -             | ✓                    | -                          | -                          | -            | _              |

| 3.3 V PCI/PCI-X (VREF = 1.0 V)         | <b>√</b>     | -            | -           | 1                      | <b>√</b>       | <b>√</b>      | -             | -                    | -                          | -                          | -            | ✓              |

| 3.3 V PCI/PCI-X (VREF= 1.5 V)          | <b>√</b>     | -            | -           | 1                      | <b>√</b>       | -             | -             | _                    | -                          | ✓                          | -            | ✓              |

| GTL + (3.3 V)                          | <b>√</b>     | -            | -           | 1                      | <b>√</b>       | <b>√</b>      | -             | -                    | -                          | -                          | -            | ✓              |

| GTL + (2.5 V)                          | -            | ✓            | -           | -                      | -              | -             | ✓             | -                    | -                          | -                          | -            | _              |

| HSTL Class I                           | 1            | -            | -           | <b>√</b>               | -              | -             | -             | ✓                    | -                          | -                          | -            | _              |

| SSTL2 Class I & II                     | -            | ✓            | -           | -                      | -              | -             | -             | -                    | ✓                          | -                          | ✓            | _              |

| SSTL3 Class I & II                     | <b>√</b>     | _            | -           | -                      | <b>√</b>       | -             | -             | -                    | -                          | ✓                          | -            | ✓              |

| LVDS (VREF = 1.0 V)                    | 1            | ✓            | -           | 1                      | -              | -             | ✓             | -                    | -                          | -                          | ✓            | -              |

| LVDS (VREF = 1.25 V)                   | -            | ✓            | -           | -                      | -              | _             | -             | -                    | ✓                          | -                          | ✓            | _              |

| LVPECL (VREF = 1.0 V)                  | <b>✓</b>     | _            | -           | -                      | <b>✓</b>       | <b>√</b>      | -             | -                    | -                          | -                          | -            | ✓              |

| LVPECL (VREF = 1.5 V)                  | ✓            | _            | -           | _                      | ✓              | _             | -             | _                    | -                          | ✓                          | -            | <b>√</b>       |

#### Notes:

- 1. Note that GTL+ 2.5 V is not supported across the full military temperature range.

- 2. A "\" indicates whether standards can be used within a bank at the same time. Examples:

- a) LVTTL can be used with 3.3V PCI and GTL+ (3.3V), when  $V_{REF} = 1.0V$  (GTL+ requirement). b) LVTTL can be used with 3.3V PCI and SSTL3 Class I and II, when  $V_{REF} = 1.5V$  (SSTL3 requirement).

Note that two I/O standards are compatible if:

- Their VCCI values are identical.

- Their VREF standards are identical (if applicable).

For example, if LVTTL 3.3 V (VREF= 1.0 V) is used, then the other available (i.e. compatible) I/O standards in the same bank are LVTTL 3.3 V PCI/PCI-X, GTL+, and LVPECL.

Also note that when multiple I/O standards are used within a bank, the voltage tolerance will be limited to the minimum tolerance of all I/O standards used in the bank.

### **3.3 V LVTTL**

Low-Voltage Transistor-Transistor Logic is a general purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

Table 2-20 • DC Input and Output Levels

| ,       | VIL     | VIH     |         | VOL     | VOH     | IOL | ЮН  |

|---------|---------|---------|---------|---------|---------|-----|-----|

| Min., V | Max., V | Min., V | Max., V | Max., V | Min., V | mA  | mA  |

| -0.3    | 0.8     | 2.0     | 3.6     | 0.4     | 2.4     | 24  | -24 |

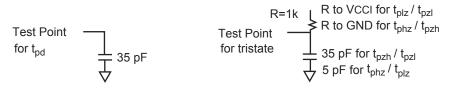

## **AC Loadings**

Figure 2-15 • AC Test Loads

Table 2-21 • AC Waveforms, Measuring Points, and Capacitive Load

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ) (V) | C <sub>load</sub> (pF) |

|---------------|----------------|----------------------|----------------|------------------------|

| 0             | 3.0            | 1.40                 | N/A            | 35                     |

Note: \* Measuring Point = VTRIP

**Detailed Specifications**

### 1.8 V LVCMOS

Low-Voltage Complementary Metal-Oxide Semiconductor for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 3.3 V tolerant CMOS input buffer and a push-pull output buffer.

Table 2-26 • DC Input and Output Levels

| ,       | VIL      | VIH      |         | VOL     | VOH        | IOL  | ЮН    |

|---------|----------|----------|---------|---------|------------|------|-------|

| Min., V | Max., V  | Min., V  | Max., V | Max., V | Min., V    | mA   | mA    |

| -0.3    | 0.2 VCCI | 0.7 VCCI | 3.6     | 0.2     | VCCI - 0.2 | 8 mA | –8 mA |

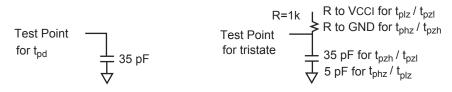

## AC Loadings

Figure 2-17 • AC Test Loads

Table 2-27 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ) (V) | C <sub>load</sub> (pF) |

|---------------|----------------|----------------------|----------------|------------------------|

| 0             | 1.8            | 0.5 VCCI             | N/A            | 35                     |

Note: \* Measuring Point = VTRIP

2-36 Revision 18

## **Routing Specifications**

### **Routing Resources**

The routing structure found in Axcelerator devices enables any logic module to be connected to any other logic module while retaining high performance. There are multiple paths and routing resources that can be used to route one logic module to another, both within a SuperCluster and elsewhere on the chip.

There are four primary types of routing within the AX architecture: DirectConnect, CarryConnect, FastConnect, and Vertical and Horizontal Routing.

### **DirectConnect**

DirectConnects provide a high-speed connection between an R-cell and its adjacent C-cell (Figure 2-35). This connection can be made from DCOUT of the C-cell to DCIN of the R-cell by configuring of the S1 line of the R-cell. This provides a connection that does not require an antifuse and has a delay of less than 0.1 ns.

Figure 2-35 • DirectConnect and CarryConnect

### **CarryConnect**

CarryConnects are used to build carry chains for arithmetic functions (Figure 2-35). The FCO output of the right C-cell of a two-C-cell Cluster drives the FCI input of the left C-cell in the two-C-cell Cluster immediately below it. This pattern continues down both sides of each SuperCluster column.

Similar to the DirectConnects, CarryConnects can be built without an antifuse connection. This connection has a delay of less than 0.1 ns from the FCO of one two-C-cell cluster to the FCI of the two-C-cell cluster immediately below it (see the "Carry-Chain Logic" section on page 2-56 for more information).

### **FastConnect**

For high-speed routing of logic signals, FastConnects can be used to build a short distance connection using a single antifuse (Figure 2-36 on page 2-62). FastConnects provide a maximum delay of 0.3 ns. The outputs of each logic module connect directly to the Output Tracks within a SuperCluster. Signals on the Output Tracks can then be routed through a single antifuse connection to drive the inputs of logic modules either within one SuperCluster or in the SuperCluster immediately below it.

### **CLK1 and CLK2**

Both PLL outputs, CLK1 and CLK2, can be used to drive a global resource, an adjacent PLL RefCLK input, or a net in the FPGA core. Not all drive combinations are possible (Table 2-81).

Table 2-81 • PLL General Connections Rules

| CLK1              | CLK2              |

|-------------------|-------------------|

| HCLK              | HCLK              |

| CLK               | CLK               |

| HCLK              | Routed net output |

| Routed net output | HCLK              |

| HCLK              | NONE              |

| NONE              | HCLK              |

| CLK               | NONE              |

| NONE              | CLK               |

Note: The PLL outputs remain Low when REFCLK is constant (either Low or High).

### Restrictions on CLK1 and CLK2

- When both are driving global resources, they must be driving the same *type* of global resource (i.e. either HCLK or CLK).

- Only one can drive a routed net at any given time.

Table 2-82 and Table 2-83 specify all the possible CLK1 and CLK2 connections for the north and south PLLs. HCLK1 and HCLK2 are used to denote the different HCLK networks when two are being driven at the same time by a single PLL (Note that HCLK1 is the primary clock resource associated with the PLL, and HCLK2 is the clock resource associated with the adjacent PLL). Likewise, CLK1 and CLK2 are used to denote the different CLK networks when two are being driven at the same time by a single PLL (Figure 2-48 on page 2-75).

Table 2-82 • North PLL Connections

| CLK1                         | CLK2                      |

|------------------------------|---------------------------|

| HCLK1                        | Routed net                |

| HCLK1                        | Unused                    |

| HCLK2                        | HCLK1                     |

| HCLK2                        | Routed net                |

| HCLK2                        | Both HCLK1 and routed net |

| HCLK2                        | Unused                    |

| Unused                       | HCLK1                     |

| Unused                       | Routed net                |

| Unused                       | Both HCLK1 and routed net |

| Unused                       | Unused                    |

| Routed net                   | HCLK1                     |

| Routed net                   | Unused                    |

| Both HCLK1 and HCLK2         | Routed net                |

| Both HCLK1 and HCLK2         | Unused                    |

| Both HCLK1 and routed net    | Unusable                  |

| Both HCLK2 and routed net    | HCLK1                     |

| Both HCLK2 and routed net    | Unused                    |

| HCLK1, HCLK2, and routed net | Unusable                  |

Note: Designer software currently does not support all of these connections. Only exclusive connections where one output connects to a single net are supported at this time (e.g.CLK1 driving HCLK1, and HCLK2 is not supported).

**Detailed Specifications**

Table 2-83 • South PLL Connections

| CLK1                       | CLK2                     |

|----------------------------|--------------------------|

| CLK1                       | Routed net               |

| CLK1                       | Unused                   |

| CLK2                       | CLK1                     |

| CLK2                       | Routed net               |

| CLK2                       | Both CLK1 and routed net |

| CLK2                       | Unused                   |

| Unused                     | CLK1                     |

| Unused                     | Routed net               |

| Unused                     | Both CLK1 and routed net |

| Unused                     | Unused                   |

| Routed net                 | CLK1                     |

| Routed net                 | Unused                   |

| Both CLK1 and CLK2         | Routed net               |

| Both CLK1 and CLK2         | Unused                   |

| Both CLK1 and routed net   | Unusable                 |

| Both CLK2 and routed net   | CLK1                     |

| Both CLK2 and routed net   | Unused                   |

| CLK1, CLK2, and routed net | Unusable                 |

Note: Designer software currently does not support all of these connections. Only exclusive connections where one output connects to a single net are supported at this time (e.g., CLK1 driving both CLK1 and CLK2 is not supported).

2-80 Revision 18

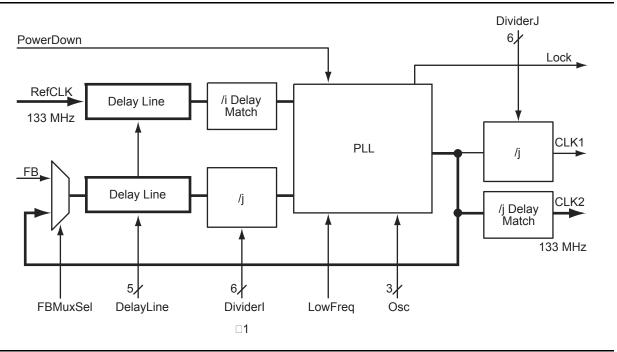

**FBMuxSel**

LowFreq

Osc

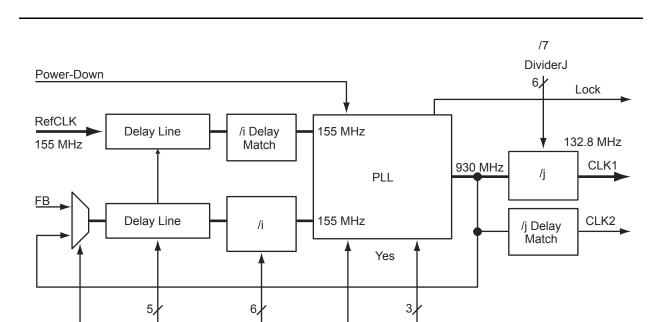

Figure 2-54 • Using the PLL 155 MHz In, 133 MHz Out

DividerI

+6

DelayLine

Figure 2-55 • Using the PLL Delaying the Reference Clock

2-84 Revision 18

## **Timing Characteristics**

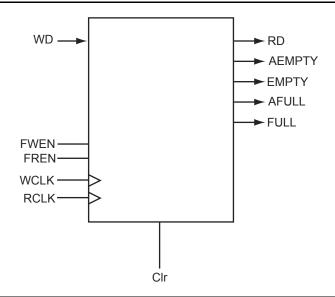

Figure 2-66 • FIFO Model

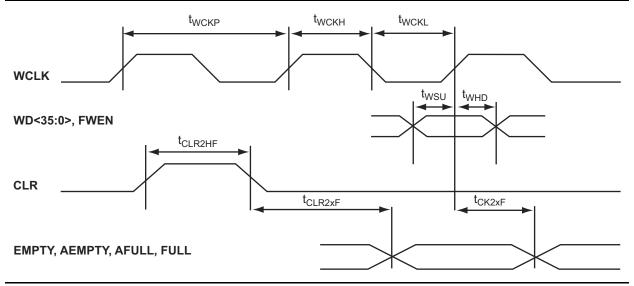

Figure 2-67 • FIFO Write Timing

Table 2-101 • Eight FIFO Blocks Cascaded Worst-Case Commercial Conditions VCCA = 1.425 V, VCCI = 3.0 V,  $T_J$  = 70°C

|                      |                              | -2 S | peed  | -1 S | peed  | Std S | Speed |       |

|----------------------|------------------------------|------|-------|------|-------|-------|-------|-------|

| Parameter            | Description                  | Min. | Max.  | Min. | Max.  | Min.  | Max.  | Units |

| FIFO Module          | Timing                       |      |       |      |       |       |       |       |

| t <sub>WSU</sub>     | Write Setup                  |      | 15.46 |      | 17.61 |       | 20.70 | ns    |

| $t_{WHD}$            | Write Hold                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>WCKH</sub>    | WCLK High                    |      | 0.75  |      | 0.75  |       | 0.75  | ns    |

| $t_{WCKL}$           | WCLK Low                     |      | 5.13  |      | 5.13  |       | 5.13  | ns    |

| t <sub>WCKP</sub>    | Minimum WCLK Period          | 5.88 |       | 5.88 |       | 5.88  |       | ns    |

| t <sub>RSU</sub>     | Read Setup                   |      | 16.22 |      | 18.47 |       | 21.72 | ns    |

| t <sub>RHD</sub>     | Read Hold                    |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>RCKH</sub>    | RCLK High                    |      | 0.73  |      | 0.73  |       | 0.73  | ns    |

| t <sub>RCKL</sub>    | RCLK Low                     |      | 5.77  |      | 5.77  |       | 5.77  | ns    |

| t <sub>RCKP</sub>    | Minimum RCLK period          | 6.50 |       | 6.50 |       | 6.50  |       | ns    |

| t <sub>CLRHF</sub>   | Clear High                   |      | 0.00  |      | 0.00  |       | 0.00  | ns    |

| t <sub>CLR2FF</sub>  | Clear-to-flag (EMPTY/FULL)   |      | 1.92  |      | 2.18  |       | 2.57  | ns    |

| t <sub>CLR2AF</sub>  | Clear-to-flag (AEMPTY/AFULL) |      | 4.39  |      | 5.00  |       | 5.88  | ns    |

| t <sub>CK2FF</sub>   | Clock-to-flag (EMPTY/FULL)   |      | 2.13  |      | 2.42  |       | 2.85  | ns    |

| t <sub>CK2AF</sub>   | Clock-to-flag (AEMPTY/AFULL) |      | 5.04  |      | 5.75  |       | 6.75  | ns    |

| t <sub>RCK2RD1</sub> | RCLK-To-OUT (Pipelined)      |      | 3.39  |      | 3.86  |       | 4.54  | ns    |

| t <sub>RCK2RD2</sub> | RCLK-To-OUT (Nonpipelined)   |      | 4.93  |      | 5.62  |       | 6.61  | ns    |

Note: Timing data for these eight cascaded FIFO blocks uses a depth of 32,768. For all other combinations, use Microsemi's timing software.

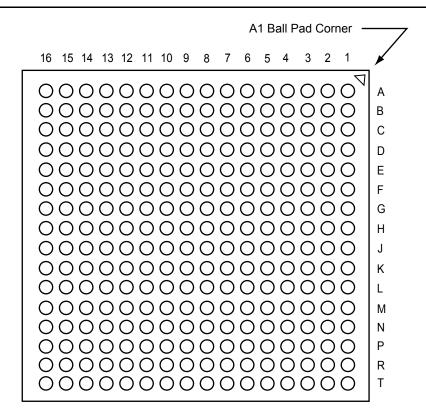

## **FG256**

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Package Pin Assignments

| FG256-Pin FBGA   |        | FG256-Pin F    | BGA    | FG256-Pin FBGA  |        |  |

|------------------|--------|----------------|--------|-----------------|--------|--|

|                  | Pin    |                | Pin    |                 | Pin    |  |

| AX125 Function   | Number | AX125 Function | Number | AX125 Function  | Number |  |

| Bank 0           |        | IO20NB2F2      | F15    | IO41PB3F3       | L14    |  |

| IO01NB0F0        | B4     | IO20PB2F2      | E15    | Bank 4          |        |  |

| IO01PB0F0        | В3     | IO21NB2F2      | C16    | IO42NB4F4       | N12    |  |

| IO03NB0F0        | A4     | IO21PB2F2      | B16    | IO42PB4F4       | N13    |  |

| IO03PB0F0        | A3     | IO22NB2F2      | H13    | IO43NB4F4       | T14    |  |

| IO04NB0F0        | В6     | IO22PB2F2      | G13    | IO43PB4F4       | R14    |  |

| IO04PB0F0        | B5     | IO23NB2F2      | E16    | IO44PB4F4       | T15    |  |

| IO06NB0F0        | A6     | IO23PB2F2      | D16    | IO45NB4F4       | R12    |  |

| IO06PB0F0        | A5     | IO25NB2F2      | H15    | IO45PB4F4       | R13    |  |

| IO07NB0F0/HCLKAN | B8     | IO25PB2F2      | G15    | IO46NB4F4       | P11    |  |

| IO07PB0F0/HCLKAP | В7     | IO26NB2F2      | H14    | IO46PB4F4       | P12    |  |

| IO08NB0F0/HCLKBN | A9     | IO26PB2F2      | G14    | IO47PB4F4       | T11    |  |

| IO08PB0F0/HCLKBP | A8     | IO27NB2F2      | G16    | IO48NB4F4       | T12    |  |

| Bank 1           |        | IO27PB2F2      | F16    | IO48PB4F4       | T13    |  |

| IO09NB1F1/HCLKCN | C10    | IO28NB2F2      | K15    | IO49NB4F4/CLKEN | R9     |  |

| IO09PB1F1/HCLKCP | C9     | IO28PB2F2      | K16    | IO49PB4F4/CLKEP | R10    |  |

| IO10NB1F1/HCLKDN | B11    | IO29NB2F2      | J16    | IO50NB4F4/CLKFN | Т8     |  |

| IO10PB1F1/HCLKDP | B10    | IO29PB2F2      | H16    | IO50PB4F4/CLKFP | Т9     |  |

| IO12NB1F1        | A13    | Bank 3         |        | Bank 5          |        |  |

| IO12PB1F1        | A12    | IO30NB3F3      | K13    | IO51NB5F5/CLKGN | P7     |  |

| IO13NB1F1        | B13    | IO30PB3F3      | J13    | IO51PB5F5/CLKGP | P8     |  |

| IO13PB1F1        | B12    | IO31NB3F3      | K14    | IO52NB5F5/CLKHN | R6     |  |

| IO14NB1F1        | C12    | IO31PB3F3      | J14    | IO52PB5F5/CLKHP | R7     |  |

| IO14PB1F1        | C11    | IO33NB3F3      | L15    | IO54NB5F5       | T5     |  |

| IO15NB1F1        | A15    | IO33PB3F3      | L16    | IO54PB5F5       | Т6     |  |

| IO15PB1F1        | B14    | IO35NB3F3      | P16    | IO55NB5F5       | P5     |  |

| IO16NB1F1        | C15    | IO35PB3F3      | N16    | IO55PB5F5       | P6     |  |

| IO16PB1F1        | C14    | IO36PB3F3      | M16    | IO56NB5F5       | Т3     |  |

| IO17NB1F1        | D13    | IO37NB3F3      | P15    | IO56PB5F5       | T4     |  |

| IO17PB1F1        | D12    | IO37PB3F3      | R16    | IO57NB5F5       | R3     |  |

| Bank 2           |        | IO39NB3F3      | N15    | IO57PB5F5       | R4     |  |

| IO18NB2F2        | F13    | IO39PB3F3      | M15    | IO58NB5F5       | R1     |  |

| IO18PB2F2        | E13    | IO40NB3F3      | M13    | IO58PB5F5       | T2     |  |

| IO19NB2F2        | F14    | IO40PB3F3      | L13    | IO59NB5F5       | N4     |  |

| IO19PB2F2        | E14    | IO41NB3F3      | M14    | IO59PB5F5       | N5     |  |

3-10 Revision 18

## Package Pin Assignments

| _                 |               |  |  |  |  |

|-------------------|---------------|--|--|--|--|

| FG256-Pin FBGA    |               |  |  |  |  |

| AX125 Function    | Pin<br>Number |  |  |  |  |

| VCCA              | L10           |  |  |  |  |

| VCCA              | L7            |  |  |  |  |

| VCCA              | L8            |  |  |  |  |

| VCCA              | L9            |  |  |  |  |

| VCCA              | N3            |  |  |  |  |

| VCCA              | P14           |  |  |  |  |

| VCCPLA            | C7            |  |  |  |  |

| VCCPLB            | D6            |  |  |  |  |

| VCCPLC            | A10           |  |  |  |  |

| VCCPLD            | D10           |  |  |  |  |

| VCCPLE            | P10           |  |  |  |  |

| VCCPLF            | N11           |  |  |  |  |

| VCCPLG            | T7            |  |  |  |  |

| VCCPLH            | N7            |  |  |  |  |

| VCCDA             | A2            |  |  |  |  |

| VCCDA             | C13           |  |  |  |  |

| VCCDA             | D9            |  |  |  |  |

| V <sub>CCDA</sub> | H1            |  |  |  |  |

| VCCDA             | J15           |  |  |  |  |

| VCCDA             | N14           |  |  |  |  |

| VCCDA             | N8            |  |  |  |  |

| VCCDA             | P4            |  |  |  |  |

| VCCIB0            | E6            |  |  |  |  |

| VCCIB0            | E7            |  |  |  |  |

| VCCIB0            | E8            |  |  |  |  |

| VCCIB1            | E10           |  |  |  |  |

| VCCIB1            | E11           |  |  |  |  |

| VCCIB1            | E9            |  |  |  |  |

| VCCIB2            | F12           |  |  |  |  |

| VCCIB2            | G12           |  |  |  |  |

| VCCIB2            | H12           |  |  |  |  |

| VCCIB3            | J12           |  |  |  |  |

| VCCIB3            | K12           |  |  |  |  |

| VCCIB3            | L12           |  |  |  |  |

| VCCIB4            | M10           |  |  |  |  |

| FG256-Pin FBGA |               |  |  |  |

|----------------|---------------|--|--|--|

| AX125 Function | Pin<br>Number |  |  |  |

| VCCIB4         | M11           |  |  |  |

| VCCIB4         | M9            |  |  |  |

| VCCIB5         | M6            |  |  |  |

| VCCIB5         | M7            |  |  |  |

| VCCIB5         | M8            |  |  |  |

| VCCIB6         | J5            |  |  |  |

| VCCIB6         | K5            |  |  |  |

| VCCIB6         | L5            |  |  |  |

| VCCIB7         | F5            |  |  |  |

| VCCIB7         | G5            |  |  |  |

| VCCIB7         | H5            |  |  |  |

| VCOMPLA        | A7            |  |  |  |

| VCOMPLB        | D7            |  |  |  |

| VCOMPLC        | В9            |  |  |  |

| VCOMPLD        | D11           |  |  |  |

| VCOMPLE        | T10           |  |  |  |

| VCOMPLF        | N10           |  |  |  |

| VCOMPLG        | R8            |  |  |  |

| VCOMPLH        | N6            |  |  |  |

| VPUMP          | A14           |  |  |  |

3-12 Revision 18

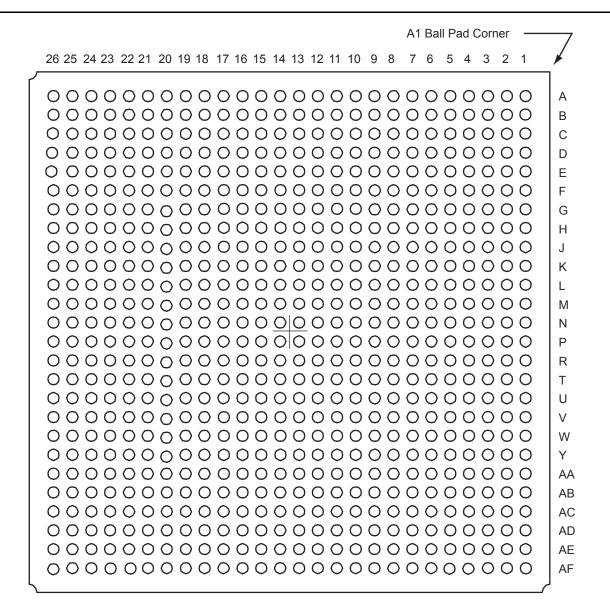

## **FG484**

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

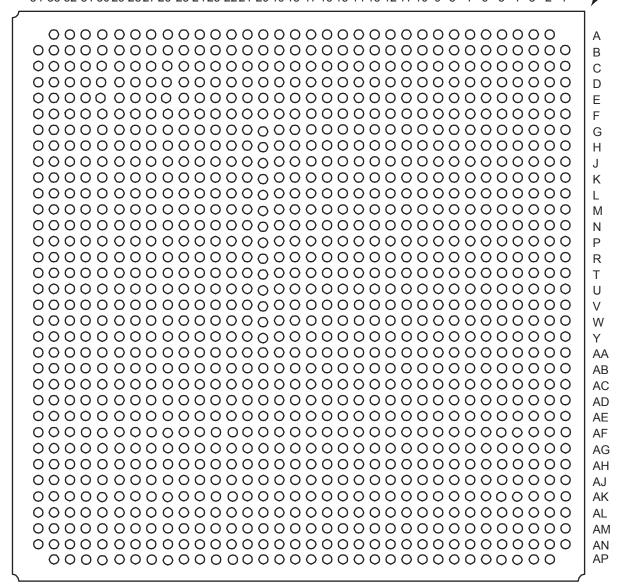

## **FG676**

#### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Package Pin Assignments

### **FG896**

30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 Α В С D Ε F G Н J Κ L M Ν Ρ R Τ U V W Υ AA AB AC ΑD ΑE AF AG AΗ ΑJ ΑK

A1 Ball Pad Corner

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

3-52 Revision 18

## FG1152

A1 Ball Pad Corner

34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

### Note

For Package Manufacturing and Environmental information, visit Resource center at http://www.microsemi.com/soc/products/rescenter/package/index.html.

Package Pin Assignments

| FG1152          |               | FG1152          |               | FG1152          |               |

|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number | AX2000 Function | Pin<br>Number |

| VCCIB0          | C5            | VCCIB3          | AA24          | VCCIB6          | AA11          |

| VCCIB0          | D5            | VCCIB3          | AB23          | VCCIB6          | AA12          |

| VCCIB0          | L12           | VCCIB3          | AB24          | VCCIB6          | AB11          |

| VCCIB0          | L13           | VCCIB3          | AC24          | VCCIB6          | AB12          |

| VCCIB0          | L14           | VCCIB3          | AK31          | VCCIB6          | AC11          |

| VCCIB0          | M13           | VCCIB3          | AK32          | VCCIB6          | AK1           |

| VCCIB0          | M14           | VCCIB3          | AK33          | VCCIB6          | AK2           |

| VCCIB0          | M15           | VCCIB3          | AK34          | VCCIB6          | AK3           |

| VCCIB0          | M16           | VCCIB3          | V23           | VCCIB6          | AK4           |

| VCCIB0          | M17           | VCCIB3          | W23           | VCCIB6          | V12           |

| VCCIB1          | A30           | VCCIB3          | Y23           | VCCIB6          | W12           |

| VCCIB1          | B30           | VCCIB4          | AC18          | VCCIB6          | Y12           |

| VCCIB1          | C30           | VCCIB4          | AC19          | VCCIB7          | E1            |

| VCCIB1          | D30           | VCCIB4          | AC20          | VCCIB7          | E2            |

| VCCIB1          | L21           | VCCIB4          | AC21          | VCCIB7          | E3            |

| VCCIB1          | L22           | VCCIB4          | AC22          | VCCIB7          | E4            |

| VCCIB1          | L23           | VCCIB4          | AD21          | VCCIB7          | M11           |

| VCCIB1          | M18           | VCCIB4          | AD22          | VCCIB7          | N11           |

| VCCIB1          | M19           | VCCIB4          | AD23          | VCCIB7          | N12           |

| VCCIB1          | M20           | VCCIB4          | AL30          | VCCIB7          | P11           |

| VCCIB1          | M21           | VCCIB4          | AM30          | VCCIB7          | P12           |

| VCCIB1          | M22           | VCCIB4          | AN30          | VCCIB7          | R12           |

| VCCIB2          | E31           | VCCIB4          | AP30          | VCCIB7          | T12           |

| VCCIB2          | E32           | VCCIB5          | AC13          | VCCIB7          | U12           |

| VCCIB2          | E33           | VCCIB5          | AC14          | VCCPLA          | J16           |

| VCCIB2          | E34           | VCCIB5          | AC15          | VCCPLB          | K17           |

| VCCIB2          | M24           | VCCIB5          | AC16          | VCCPLC          | J19           |

| VCCIB2          | N23           | VCCIB5          | AC17          | VCCPLD          | L18           |

| VCCIB2          | N24           | VCCIB5          | AD12          | VCCPLE          | AK19          |

| VCCIB2          | P23           | VCCIB5          | AD13          | VCCPLF          | AE18          |

| VCCIB2          | P24           | VCCIB5          | AD14          | VCCPLG          | AK16          |

| VCCIB2          | R23           | VCCIB5          | AL5           | VCCPLH          | AF17          |

| VCCIB2          | T23           | VCCIB5          | AM5           | VCOMPLA         | H16           |

| VCCIB2          | U23           | VCCIB5          | AN5           | VCOMPLB         | L17           |

| VCCIB3          | AA23          | VCCIB5          | AP5           | VCOMPLC         | H19           |

3-82 Revision 18

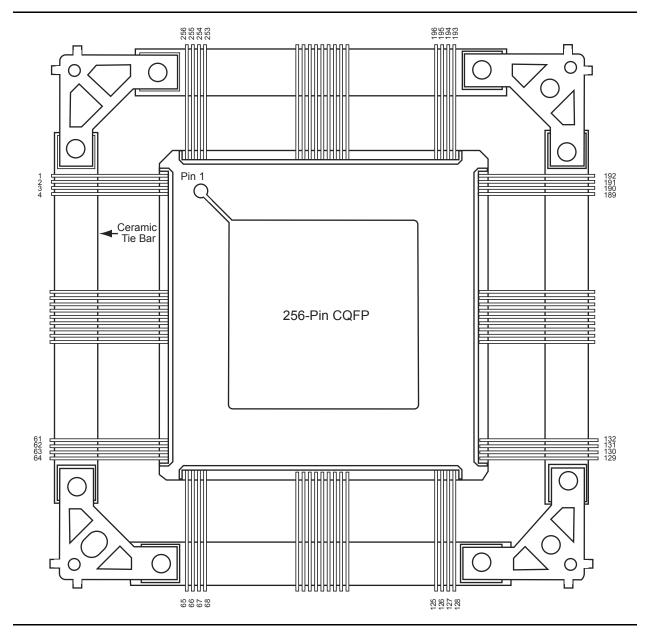

# **CQ256**

### Note

For Package Manufacturing and Environmental information, visit the Resource center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

3-94 Revision 18

| CQ352            |               | CQ352           |               | CQ352           |               |

|------------------|---------------|-----------------|---------------|-----------------|---------------|

| AX1000 Function  | Pin<br>Number | AX1000 Function | Pin<br>Number | AX1000 Function | Pin<br>Number |

| Bank 0           |               | IO60NB1F5       | 275           | Bank 3          |               |

| IO02NB0F0        | 341           | IO60PB1F5       | 276           | IO96NB3F9       | 217           |

| IO02PB0F0        | 342           | IO61NB1F5       | 271           | IO96PB3F9       | 218           |

| IO03PB0F0        | 343           | IO61PB1F5       | 272           | IO97NB3F9       | 219           |

| IO04NB0F0        | 337           | IO63NB1F5       | 269           | IO97PB3F9       | 220           |

| IO04PB0F0        | 338           | IO63PB1F5       | 270           | IO99NB3F9       | 213           |

| IO08NB0F0        | 331           | Bank 2          |               | IO99PB3F9       | 214           |

| IO08PB0F0        | 332           | IO64NB2F6       | 259           | IO108NB3F10     | 211           |

| IO09NB0F0        | 335           | IO64PB2F6       | 260           | IO108PB3F10     | 212           |

| IO09PB0F0        | 336           | IO67NB2F6       | 261           | IO109NB3F10     | 207           |

| IO24NB0F2        | 325           | IO67PB2F6       | 262           | IO109PB3F10     | 208           |

| IO24PB0F2        | 326           | IO68NB2F6       | 255           | IO111NB3F10     | 205           |

| IO25NB0F2        | 323           | IO68PB2F6       | 256           | IO111PB3F10     | 206           |

| IO25PB0F2        | 324           | IO69NB2F6       | 253           | IO112NB3F10     | 199           |

| IO30NB0F2/HCLKAN | 319           | IO69PB2F6       | 254           | IO112PB3F10     | 200           |

| IO30PB0F2/HCLKAP | 320           | IO74NB2F7       | 249           | IO113NB3F10     | 201           |

| IO31NB0F2/HCLKBN | 313           | IO74PB2F7       | 250           | IO113PB3F10     | 202           |

| IO31PB0F2/HCLKBP | 314           | IO75NB2F7       | 247           | IO115NB3F10     | 195           |

| Bank 1           | Bank 1        |                 | 248           | IO115PB3F10     | 196           |

| IO32NB1F3/HCLKCN | 305           | IO76NB2F7       | 243           | IO116NB3F10     | 193           |

| IO32PB1F3/HCLKCP | 306           | IO76PB2F7       | 244           | IO116PB3F10     | 194           |

| IO33NB1F3/HCLKDN | 299           | IO77NB2F7       | 241           | IO117NB3F10     | 189           |

| IO33PB1F3/HCLKDP | 300           | IO77PB2F7       | 242           | IO117PB3F10     | 190           |

| IO38NB1F3        | 295           | IO78NB2F7       | 237           | IO124NB3F11     | 183           |

| IO38PB1F3        | 296           | IO78PB2F7       | 238           | IO124PB3F11     | 184           |

| IO54NB1F5        | 287           | IO79NB2F7       | 235           | IO125NB3F11     | 187           |

| IO54PB1F5        | 288           | IO79PB2F7       | 236           | IO125PB3F11     | 188           |

| IO55NB1F5        | 289           | IO82NB2F7       | 231           | IO127NB3F11     | 181           |

| IO55PB1F5        | 290           | IO82PB2F7       | 232           | IO127PB3F11     | 182           |

| IO56NB1F5        | 281           | IO83NB2F7       | 229           | IO128NB3F11     | 179           |

| IO56PB1F5        | 282           | IO83PB2F7       | 230           | IO128PB3F11     | 180           |

| IO57NB1F5        | 283           | IO94NB2F8       | 225           | Bank 4          |               |

| IO57PB1F5        | 284           | IO94PB2F8       | 226           | IO130NB4F12     | 172           |

| IO59NB1F5        | 277           | IO95NB2F8       | 223           | IO130PB4F12     | 173           |

| IO59PB1F5        | 278           | IO95PB2F8       | 224           | IO131NB4F12     | 170           |