Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Active                                                                    |

| Туре                    | Dual Core                                                                 |

| Interface               | CAN, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 400MHz                                                                    |

| Non-Volatile Memory     | ROM (64kB)                                                                |

| On-Chip RAM             | 552kB                                                                     |

| Voltage - I/O           | 1.8V, 3.3V                                                                |

| Voltage - Core          | 1.25V                                                                     |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                             |

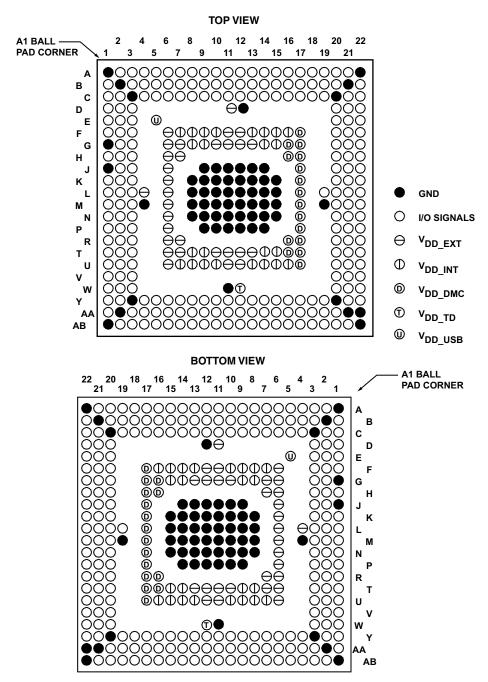

| Package / Case          | 349-LFBGA, CSPBGA                                                         |

| Supplier Device Package | 349-CSPBGA (19x19)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf606wcbcz402       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Event Handling**

The processor provides event handling that supports both nesting and prioritization. Nesting allows multiple event service routines to be active simultaneously. Prioritization ensures that servicing of a higher-priority event takes precedence over servicing of a lower-priority event. The processor provides support for five different types of events:

- Emulation An emulation event causes the processor to enter emulation mode, allowing command and control of the processor via the JTAG interface.

- Reset This event resets the processor.

- Nonmaskable Interrupt (NMI) The NMI event can be generated either by the software watchdog timer, by the NMI input signal to the processor, or by software. The NMI event is frequently used as a power-down indicator to initiate an orderly shutdown of the system.

- Exceptions Events that occur synchronously to program flow (in other words, the exception is taken before the instruction is allowed to complete). Conditions such as data alignment violations and undefined instructions cause exceptions.

- Interrupts Events that occur asynchronously to program flow. They are caused by input signals, timers, and other peripherals, as well as by an explicit software instruction.

### **Core Event Controller (CEC)**

The CEC supports nine general-purpose interrupts (IVG15–7), in addition to the dedicated interrupt and exception events. Of these general-purpose interrupts, the two lowest-priority interrupts (IVG15–14) are recommended to be reserved for software interrupt handlers. For more information, see the *ADSP-BF60x Processor Programmer's Reference*.

### System Event Controller (SEC)

The SEC manages the enabling, prioritization, and routing of events from each system interrupt or fault source. Additionally, it provides notification and identification of the highest priority active system interrupt request to each core and routes system fault sources to its integrated fault management unit.

### Trigger Routing Unit (TRU)

The TRU provides system-level sequence control without core intervention. The TRU maps trigger masters (generators of triggers) to trigger slaves (receivers of triggers). Slave endpoints can be configured to respond to triggers in various ways. Common applications enabled by the TRU include:

- Automatically triggering the start of a DMA sequence after a sequence from another DMA channel completes

- Software triggering

- Synchronization of concurrent activities

### Pin Interrupts

Every port pin on the processor can request interrupts in either an edge-sensitive or a level-sensitive manner with programmable polarity. Interrupt functionality is decoupled from GPIO operation. Six system-level interrupt channels (PINT0–5) are reserved for this purpose. Each of these interrupt channels can manage up to 32 interrupt pins. The assignment from pin to interrupt is not performed on a pin-by-pin basis. Rather, groups of eight pins (half ports) can be flexibly assigned to interrupt channels.

Every pin interrupt channel features a special set of 32-bit memory-mapped registers that enable half-port assignment and interrupt management. This includes masking, identification, and clearing of requests. These registers also enable access to the respective pin states and use of the interrupt latches, regardless of whether the interrupt is masked or not. Most control registers feature multiple MMR address entries to write-one-to-set or write-one-to-clear them individually.

### General-Purpose I/O (GPIO)

Each general-purpose port pin can be individually controlled by manipulation of the port control, status, and interrupt registers:

- GPIO direction control register Specifies the direction of each individual GPIO pin as input or output.

- GPIO control and status registers A "write one to modify" mechanism allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins.

- GPIO interrupt mask registers Allow each individual GPIO pin to function as an interrupt to the processor.

GPIO pins defined as inputs can be configured to generate hardware interrupts, while output pins can be triggered by software interrupts.

- GPIO interrupt sensitivity registers Specify whether individual pins are level- or edge-sensitive and specify—if edge-sensitive—whether just the rising edge or both the rising and falling edges of the signal are significant.

### Pin Multiplexing

The processor supports a flexible multiplexing scheme that multiplexes the GPIO pins with various peripherals. A maximum of 4 peripherals plus GPIO functionality is shared by each GPIO pin. All GPIO pins have a bypass path feature – that is, when the output enable and the input enable of a GPIO pin are both active, the data signal before the pad driver is looped back to the receive path for the same GPIO pin. For more information, see GP I/O Multiplexing for 349-Ball CSP\_BGA on Page 33.

### **MEMORY ARCHITECTURE**

The processor views memory as a single unified 4G byte address space, using 32-bit addresses. All resources, including internal memory, external memory, and I/O control registers, occupy separate sections of this common address space. The memory portions of this address space are arranged in a hierarchical structure to provide a good cost/performance balance of some very fast, low-latency core-accessible memory as cache or SRAM, and larger, lower-cost and performance interface-accessible memory systems. See Figure 3 and Figure 4.

### **Memory Protection**

The Blackfin cores feature a memory protection concept, which grants data and/or instruction accesses from enabled memory regions only. A supervisor mode vs. user mode programming model supports dynamically varying access rights. Increased flexibility in memory page size options supports a simple method of static memory partitioning.

### **System Protection**

All system resources and L2 memory banks can be controlled by either the processor cores, memory-to-memory DMA, or the system debug unit (SDU). A system protection unit (SPU) enables write accesses to specific resources that are locked to any of four masters: Core 0, Core 1, Memory DMA, and the System Debug Unit. System protection is enabled in greater granularity for some modules (L2, SEC and GPIO controllers) through a *global lock* concept.

### **Watchpoint Protection**

The primary purpose of watchpoints and hardware breakpoints is to serve emulator needs. When enabled, they signal an emulator event whenever user-defined system resources are accessed or a core executes from user-defined addresses. Watchpoint events can be configured such that they signal the events to the other Blackfin core or to the fault management unit.

### **Dual Watchdog**

The two on-chip watchdog timers each may supervise one Blackfin core.

### **Bandwidth Monitor**

All DMA channels that operate in memory-to-memory mode (Memory DMA, PVP Memory Pipe DMA, PIXC DMA) are equipped with a bandwidth monitor mechanism. They can signal a system event or fault when transactions tend to starve because system buses are fully loaded with higher-priority traffic.

### Signal Watchdogs

The eight general-purpose timers feature two new modes to monitor off-chip signals. The Watchdog Period mode monitors whether external signals toggle with a period within an expected range. The Watchdog Width mode monitors whether the pulse widths of external signals are in an expected range. Both modes help to detect incorrect undesired toggling (or lack thereof) of system-level signals.

### **Up/Down Count Mismatch Detection**

The up/down counter can monitor external signal pairs, such as request/grant strobes. If the edge count mismatch exceeds the expected range, the up/down counter can flag this to the processor or to the fault management unit.

### **Fault Management**

The fault management unit is part of the system event controller (SEC). Any system event, whether a dual-bit uncorrectable ECC error, or any peripheral status interrupt, can be defined as being

a "fault". Additionally, the system events can be defined as an interrupt to the cores. If defined as such, the SEC forwards the event to the fault management unit which may automatically reset the entire device for reboot, or simply toggle the SYS\_FAULT output pins to signal off-chip hardware. Optionally, the fault management unit can delay the action taken via a keyed sequence, to provide a final chance for the Blackfin cores to resolve the crisis and to prevent the fault action from being taken.

### ADDITIONAL PROCESSOR PERIPHERALS

The processor contains a rich set of peripherals connected to the core via several high-bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the block diagram on Page 1). The processors contain high-speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

The following sections describe additional peripherals that were not described in the previous sections.

#### Timers

The processor includes several timers which are described in the following sections.

### **General-Purpose Timers**

There is one GP timer unit and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TMRx pins, an external clock TMRCLK input pin, or to the internal SCLKO.

The timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals via the TRU (for instance, to signal a fault).

### **Core Timers**

Each processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

### **Watchdog Timers**

Each core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, via generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before

CrossCore Embedded Studio or VisualDSP++ installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

#### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called Board Support Packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

### Middleware Packages

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules".

### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the *EE-68: Analog Devices JTAG Emulation Technical Reference* on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

### ADDITIONAL INFORMATION

The following publications that describe the ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609 processors (and related processors) can be ordered from any Analog Devices sales office or accessed electronically on our website:

- Getting Started With Blackfin Processors

- ADSP-BF60x Blackfin Processor Hardware Reference

- Blackfin Processor Programming Reference

- ADSP-BF60x Blackfin Processor Anomaly List

### **RELATED SIGNAL CHAINS**

A *signal chain* is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. For more information about this term and related topics, see the "signal chain" entry in the Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The Application Signal Chains page in the Circuits from the Lab™ site (http:\\www.analog.com\circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

Table 6. Detailed Signal Descriptions (Continued)

| Signal Name | Direction | Description                                                                                                                                                                                       |

|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPT_BD1     | I/O       | <b>Channel B Data 1</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                              |

| SPT_BFS     | I/O       | <b>Channel B Frame Sync</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                     |

| SPT_BTDV    | Output    | <b>Channel B Transmit Data Valid</b> This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots.                        |

| SYS_BMODEn  | Input     | <b>Boot Mode Control n</b> Selects the boot mode of the processor.                                                                                                                                |

| SYS_CLKIN   | Input     | Clock/Crystal Input Connect to an external clock source or crystal.                                                                                                                               |

| SYS_CLKOUT  | Output    | <b>Processor Clock Output</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter in the processor hardware reference for more details.                                      |

| SYS_EXTWAKE | Output    | <b>External Wake Control</b> Drives low during hibernate and high all other times. Typically connected to the enable input of the voltage regulator controlling the $V_{DD\ INT}$ supply.         |

| SYS_FAULT   | I/O       | Complementary Fault Complement of SYS_FAULT.                                                                                                                                                      |

| SYS_FAULT   | I/O       | Fault Indicates internal faults or senses external faults depending on the operating mode.                                                                                                        |

| SYS_HWRST   | Input     | Processor Hardware Reset Control Resets the device when asserted.                                                                                                                                 |

| SYS_IDLEn   | Output    | Core n Idle Indicator When low indicates that core n is in idle mode or being held in reset.                                                                                                      |

| SYS_NMI     | Input     | <b>Non-maskable Interrupt</b> Priority depends on the core that receives the interrupt. See the processor hardware and programming references for more details.                                   |

| SYS_PWRGD   | Input     | <b>Power Good Indicator</b> When high it indicates to the processor that the V <sub>DD_INT</sub> level is within specifications such that it is safe to begin booting upon return from hibernate. |

| SYS_RESOUT  | Output    | Reset Output Indicates that the device is in the reset state.                                                                                                                                     |

| SYS_SLEEP   | Output    | <b>Processor Sleep Indicator</b> When low indicates that the processor is in the deep sleep power saving mode.                                                                                    |

| SYS_TDA     | Input     | <b>Thermal Diode Anode</b> May be used by an external temperature sensor to measure the die temperature.                                                                                          |

| SYS_TDK     | Input     | <b>Thermal Diode Cathode</b> May be used by an external temperature sensor to measure the die temperature.                                                                                        |

| SYS_XTAL    | Output    | Crystal Output Drives an external crystal. Must be left unconnected if an external clock is driving CLKIN.                                                                                        |

| TMR_ACIn    | Input     | Alternate Capture Input n Provides an additional input for WIDCAP, WATCHDOG, and PININT modes.                                                                                                    |

| TMR_ACLKn   | Input     | Alternate Clock n Provides an additional time base for use by an individual timer.                                                                                                                |

| TMR_CLK     | Input     | <b>Clock</b> Provides an additional global time base for use by all the GP timers.                                                                                                                |

| TMR_TMRn    | I/O       | Timer n The main input/output signal for each timer.                                                                                                                                              |

| TWI_SCL     | I/O       | Serial Clock Clock output when master, clock input when slave.                                                                                                                                    |

| TWI_SDA     | I/O       | Serial Data Receives or transmits data.                                                                                                                                                           |

| UART_CTS    | Input     | Clear to Send Flow control signal.                                                                                                                                                                |

| UART_RTS    | Output    | Request to Send Flow control signal.                                                                                                                                                              |

| UART_RX     | Input     | <b>Receive</b> Receive input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                                   |

| UART_TX     | Output    | <b>Transmit</b> Transmit output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                                |

| USB_CLKIN   | Input     | Clock/Crystal Input This clock input is multiplied by a PLL to form the USB clock. See Universal Serial Bus (USB) On-The-Go—Receive and Transmit Timing for frequency/tolerance information.      |

| USB_DM      | I/O       | Data – Bidirectional differential data line.                                                                                                                                                      |

| USB_DP      | I/O       | Data + Bidirectional differential data line.                                                                                                                                                      |

| USB_ID      | Input     | OTG ID Senses whether the controller is a host or device. This signal is pulled low when an A-type plug                                                                                           |

|             |           | is sensed (signifying that the USB controller is the A device), but the input is high when a B-type plug is                                                                                       |

|             |           | sensed (signifying that the USB controller is the B device).                                                                                                                                      |

| USB_VBC     | Output    | <b>VBUS Control</b> Controls an external voltage source to supply VBUS when in host mode. May be configured as open drain. Polarity is configurable as well.                                      |

| USB_VBUS    | I/O       | Bus Voltage Connects to bus voltage in host and device modes.                                                                                                                                     |

Table 7. ADSP-BF60x 349-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name          | Description                        | Port      | Pin Name       |

|----------------------|------------------------------------|-----------|----------------|

| PWM1_AH              | PWM1 Channel A High Side           | G         | PG_03          |

| PWM1_AL              | PWM1 Channel A Low Side            | G         | PG_02          |

| PWM1_BH              | PWM1 Channel B High Side           | G         | PG_00          |

| PWM1_BL              | PWM1 Channel B Low Side            | E         | PE_15          |

| PWM1_CH              | PWM1 Channel C High Side           | E         | PE_13          |

| PWM1_CL              | PWM1 Channel C Low Side            | E         | PE_12          |

| PWM1_DH              | PWM1 Channel D High Side           | E         | PE_11          |

| PWM1_DL              | PWM1 Channel D Low Side            | E         | PE_10          |

| PWM1_SYNC            | PWM1 Sync                          | G         | PG_05          |

| PWM1_TRIP0           | PWM1 Shutdown Input 0              | G         | PG_06          |

| PWM1_TRIP1           | PWM1 Shutdown Input 1              | G         | PG_08          |

| RSIO_CLK             | RSI0 Clock                         | G         | PG_06          |

| RSIO_CMD             | RSI0 Command                       | G         | PG_05          |

| RSIO_D0              | RSI0 Data 0                        | G         | PG_03          |

| RSIO_D1              | RSI0 Data 1                        | G         | PG_02          |

| RSI0_D2              | RSI0 Data 2                        | G         | PG_00          |

| RSI0_D3              | RSI0 Data 3                        | E         | PE_15          |

| RSI0_D4              | RSIO Data 4                        | E         | PE_13          |

| RSI0_D5              | RSIO Data 5                        | E         | PE_12          |

| RSI0_D6              | RSIO Data 6                        | E         | PE_10          |

| RSI0_D7              | RSI0 Data 7                        | E         | PE_11          |

| SMC0_A01             | SMC0 Address 1                     | Not Muxed | SMC0_A01       |

| SMC0_A01             | SMC0 Address 2                     | Not Muxed | SMC0_A01       |

| SMC0_A02             | SMC0 Address 3                     |           | PA_00          |

| SMC0_A03             | SMC0 Address 4                     | A         | PA_00          |

|                      | SMC0 Address 5                     | A         | PA_01          |

| SMC0_A05<br>SMC0_A06 | SMC0 Address 6                     | A         | PA_03          |

|                      | SMC0 Address 7                     |           | PA_03<br>PA_04 |

| SMC0_A07             | SMC0 Address 8                     | A         |                |

| SMC0_A08             | SMC0 Address 9                     | A         | PA_05          |

| SMC0_A09             | SMC0 Address 10                    | A         | PA_06          |

| SMC0_A10             | SMC0 Address 10                    | A         | PA_07          |

| SMC0_A11             |                                    | A         | PA_08          |

| SMC0_A12             | SMC0 Address 12<br>SMC0 Address 13 | A         | PA_09          |

| SMC0_A13             | SMC0 Address 13 SMC0 Address 14    | В         | PB_02          |

| SMC0_A14             |                                    | A         | PA_10          |

| SMC0_A15             | SMC0 Address 15                    | A         | PA_11          |

| SMC0_A16             | SMC0 Address 16                    | В         | PB_03          |

| SMC0_A17             | SMC0 Address 17                    | A         | PA_12          |

| SMC0_A18             | SMC0 Address 18                    | A         | PA_13          |

| SMC0_A19             | SMC0 Address 19                    | A         | PA_14          |

| SMC0_A20             | SMC0 Address 20                    | A         | PA_15          |

| SMC0_A21             | SMC0 Address 21                    | В         | PB_06          |

| SMC0_A22             | SMC0 Address 22                    | В         | PB_07          |

| SMC0_A23             | SMC0 Address 23                    | В         | PB_08          |

| SMC0_A24             | SMC0 Address 24                    | В         | PB_10          |

| SMC0_A25             | SMC0 Address 25                    | В         | PB_11          |

Table 7. ADSP-BF60x 349-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name | Description                      | Port      | Pin Name       |

|-------------|----------------------------------|-----------|----------------|

| SYS_BMODE2  | Boot Mode Control 2              | Not Muxed | SYS_BMODE2     |

| SYS_CLKIN   | Clock/Crystal Input              | Not Muxed | SYS_CLKIN      |

| SYS_CLKOUT  | Processor Clock Output           | Not Muxed | SYS_CLKOUT     |

| SYS_EXTWAKE | External Wake Control            | Not Muxed | SYS_EXTWAKE    |

| SYS_FAULT   | Fault Output                     | Not Muxed | SYS_FAULT      |

| SYS_FAULT   | Complementary Fault Output       | Not Muxed | SYS_FAULT      |

| SYS_HWRST   | Processor Hardware Reset Control | Not Muxed | SYS_HWRST      |

| SYS_IDLE0   | Core 0 Idle Indicator            | G         | PG_15          |

| SYS_IDLE1   | Core 1 Idle Indicator            | G         | PG_14          |

| SYS_NMI     | Non-maskable Interrupt           | Not Muxed | SYS_NMI_RESOUT |

| SYS_PWRGD   | Power Good Indicator             | Not Muxed | SYS_PWRGD      |

| SYS_RESOUT  | Reset Output                     | Not Muxed | SYS_NMI_RESOUT |

| SYS_SLEEP   | Processor Sleep Indicator        | G         | PG_15          |

| SYS_TDA     | Thermal Diode Anode              | Not Muxed | SYS_TDA        |

| SYS_TDK     | Thermal Diode Cathode            | Not Muxed | SYS_TDK        |

| SYS_XTAL    | Crystal Output                   | Not Muxed | SYS_XTAL       |

| TM0_ACI0    | TIMERO Alternate Capture Input 0 | D         | PD_08          |

| TM0_ACI1    | TIMERO Alternate Capture Input 1 | G         | PG_14          |

| TM0_ACI2    | TIMERO Alternate Capture Input 2 | G         | PG_04          |

| TM0_ACI3    | TIMERO Alternate Capture Input 3 | D         | PD_07          |

| TM0_ACI4    | TIMERO Alternate Capture Input 4 | G         | PG_15          |

| TM0_ACI5    | TIMERO Alternate Capture Input 5 | D         | PD_06          |

| TM0_ACI6    | TIMERO Alternate Capture Input 6 | В         | PB_13          |

| TM0_ACLK0   | TIMERO Alternate Clock 0         | В         | PB_10          |

| TM0_ACLK1   | TIMERO Alternate Clock 1         | В         | PB_12          |

| TM0_ACLK2   | TIMERO Alternate Clock 2         | В         | PB_09          |

| TM0_ACLK3   | TIMERO Alternate Clock 3         | В         | PB_11          |

| TM0_ACLK4   | TIMERO Alternate Clock 4         | В         | PB_06          |

| TM0_ACLK5   | TIMERO Alternate Clock 5         | D         | PD_13          |

| TM0_ACLK6   | TIMERO Alternate Clock 6         | D         | PD_14          |

| TM0_ACLK7   | TIMERO Alternate Clock 7         | D         | PD_05          |

| TM0_CLK     | TIMERO Clock                     | G         | PG_13          |

| TM0_TMR0    | TIMER0 Timer 0                   | E         | PE_14          |

| TM0_TMR1    | TIMER0 Timer 1                   | G         | PG_04          |

| TM0_TMR2    | TIMER0 Timer 2                   | G         | PG_01          |

| TM0_TMR3    | TIMER0 Timer 3                   | G         | PG_08          |

| TM0_TMR4    | TIMER0 Timer 4                   | G         | PG_09          |

| TM0_TMR5    | TIMER0 Timer 5                   | G         | PG_07          |

| TM0_TMR6    | TIMER0 Timer 6                   | G         | PG_11          |

| TM0_TMR7    | TIMER0 Timer 7                   | G         | PG_12          |

| TWI0_SCL    | TWI0 Serial Clock                | Not Muxed | TWI0_SCL       |

| TWI0_SDA    | TWI0 Serial Data                 | Not Muxed | TWI0_SDA       |

| TWI1_SCL    | TWI1 Serial Clock                | Not Muxed | TWI1_SCL       |

| TWI1_SDA    | TWI1 Serial Data                 | Not Muxed | TWI1_SDA       |

| UARTO_CTS   | UARTO Clear to Send              | D         | PD_10          |

| UARTO_RTS   | UARTO Request to Send            | D         | PD_09          |

# GP I/O MULTIPLEXING FOR 349-BALL CSP\_BGA

Table 8 through Table 14 identifies the pin functions that are multiplexed on the general-purpose I/O pins of the 349-ball CSP\_BGA package.

Table 8. Signal Multiplexing for Port A

| Signal Name | Multiplexed Function 0 | Multiplexed Function 1 | Multiplexed Function 2 | Multiplexed Function<br>Input Tap |

|-------------|------------------------|------------------------|------------------------|-----------------------------------|

| PA_00       | SMC0_A03               | PPI2_D00               | LP0_D0                 |                                   |

| PA_01       | SMC0_A04               | PPI2_D01               | LP0_D1                 |                                   |

| PA_02       | SMC0_A05               | PPI2_D02               | LP0_D2                 |                                   |

| PA_03       | SMC0_A06               | PPI2_D03               | LP0_D3                 |                                   |

| PA_04       | SMC0_A07               | PPI2_D04               | LP0_D4                 |                                   |

| PA_05       | SMC0_A08               | PPI2_D05               | LP0_D5                 |                                   |

| PA_06       | SMC0_A09               | PPI2_D06               | LP0_D6                 |                                   |

| PA_07       | SMC0_A10               | PPI2_D07               | LP0_D7                 |                                   |

| PA_08       | SMC0_A11               | PPI2_D08               | LP1_D0                 |                                   |

| PA_09       | SMC0_A12               | PPI2_D09               | LP1_D1                 |                                   |

| PA_10       | SMC0_A14               | PPI2_D10               | LP1_D2                 |                                   |

| PA_11       | SMC0_A15               | PPI2_D11               | LP1_D3                 |                                   |

| PA_12       | SMC0_A17               | PPI2_D12               | LP1_D4                 |                                   |

| PA_13       | SMC0_A18               | PPI2_D13               | LP1_D5                 |                                   |

| PA_14       | SMC0_A19               | PPI2_D14               | LP1_D6                 |                                   |

| PA_15       | SMC0_A20               | PPI2_D15               | LP1_D7                 |                                   |

Table 9. Signal Multiplexing for Port B

| Signal Name | Multiplexed Function 0 | Multiplexed Function 1 | Multiplexed Function 2 | Multiplexed Function Input Tap |

|-------------|------------------------|------------------------|------------------------|--------------------------------|

| PB_00       | SMC0_NORCLK            | PPI2_CLK               | LPO_CLK                |                                |

| PB_01       | SMC0_AMS1              | PPI2_FS1               | LP0_ACK                |                                |

| PB_02       | SMC0_A13               | PPI2_FS2               | LP1_ACK                |                                |

| PB_03       | SMC0_A16               | PPI2_FS3               | LP1_CLK                |                                |

| PB_04       | SMC0_AMS2              | SMC0_ABE0              | SPT0_AFS               |                                |

| PB_05       | SMC0_AMS3              | SMC0_ABE1              | SPT0_ACLK              |                                |

| PB_06       | SMC0_A21               | SPT0_ATDV              |                        | TM0_ACLK4                      |

| PB_07       | SMC0_A22               | PPI2_D16               | SPT0_BFS               |                                |

| PB_08       | SMC0_A23               | PPI2_D17               | SPT0_BCLK              |                                |

| PB_09       | SMC0_BGH               |                        | SPT0_AD0               | TM0_ACLK2                      |

| PB_10       | SMC0_A24               |                        | SPT0_BD1               | TM0_ACLK0                      |

| PB_11       | SMC0_A25               |                        | SPT0_BD0               | TM0_ACLK3                      |

| PB_12       | SMC0_BG                | SPT0_BTDV              | SPT0_AD1               | TM0_ACLK1                      |

| PB_13       | ETHO_TXEN              | PPI1_FS1               |                        | TM0_ACI6                       |

| PB_14       | ETH0_REFCLK            | PPI1_CLK               |                        |                                |

| PB_15       | ETH0_PTPPPS            | PPI1_FS3               |                        |                                |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| Signal Name | Type | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                                                                                                                               |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_00       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 0   SMC0 Address 3   EPPI2 Data 0   LP0 Data 0. Notes: No notes.                                                                                  |

| PA_01       | I/O  | А              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 1   SMC0 Address 4   EPPI2 Data 1   LP0 Data 1.                                                                                                   |

| PA_02       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 2   SMC0 Address 5   EPPI2 Data 2   LP0 Data 2.  Notes: No notes.                                                               |

| PA_03       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 3   SMC0 Address 6   EPPI2 Data 3   LP0 Data 3. Notes: No notes.                                                                                  |

| PA_04       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 4   SMC0 Address 7   EPPI2 Data 4   LP0 Data 4. Notes: No notes.                                                                                  |

| PA_05       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 5   SMC0 Address 8  <br>EPPI2 Data 5   LP0 Data 5.                                                                                                |

| PA_06       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 6   SMC0 Address 9   EPPI2 Data 6   LP0 Data 6.  Notes: No notes.                                                               |

| PA_07       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 7   SMC0 Address 10   EPPI2 Data 7   LP0 Data 7. Notes: No notes.                                                                                 |

| PA_08       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PA Position 8   SMC0 Address 11  <br>EPPI2 Data 8   LP1 Data 0.                                                                                               |

| PA_09       | I/O  | А              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 9   SMC0 Address 12   EPPI2 Data 9   LP1 Data 1.                                                                                |

| PA_10       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 10   SMC0 Address 14   EPPI2 Data 10   LP1 Data 2.                                                                              |

| PA_11       | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 11   SMC0 Address 15   EPPI2 Data 11   LP1 Data 3.                                                                              |

| PA_12       | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 12   SMC0 Address 17   EPPI2 Data 12   LP1 Data 4.                                                                              |

| PA_13       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 13   SMC0 Address 18   EPPI2 Data 13   LP1 Data 5.                                                                              |

| PA_14       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 14   SMC0 Address 19   EPPI2 Data 14   LP1 Data 6.                                                                              |

| PA_15       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PA Position 15   SMC0 Address 20   EPPI2 Data 15   LP1 Data 7.  Notes: May be used to wake the processor from hibernate or deep sleep mode. |

### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                     |                                                              | Test Conditions                                                                                                    | Min                        | Typical     | Max   | Unit  |

|---------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|-------|-------|

| V <sub>OH</sub> <sup>1</sup>                                  | High Level Output Voltage                                    | $V_{DD\_EXT} = 1.7 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                           | V <sub>DD_EXT</sub> - 0.40 |             |       | V     |

| V <sub>OH</sub> <sup>1</sup>                                  | High Level Output Voltage                                    | $V_{DD\_EXT} = 3.13 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                          | V <sub>DD_EXT</sub> - 0.40 |             |       | V     |

| V <sub>OH_DDR2</sub> <sup>2</sup>                             | High Level Output Voltage, ds = 00                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -13.4 \text{ mA}$                                                        | 1.388                      |             |       | V     |

| V <sub>OH_DDR2</sub> <sup>3</sup>                             | High Level Output Voltage, ds = 10                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -6.70 \text{ mA}$                                                        | 1.311                      |             |       | V     |

| V <sub>OH_LPDDR</sub> <sup>4</sup>                            | High Level Output Voltage, ds = 00                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -11.2 \text{ mA}$                                                        | 1.300                      |             |       | V     |

| V <sub>OH_LPDDR</sub> <sup>5</sup>                            | High Level Output Voltage, ds = 01                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -7.85 \text{ mA}$                                                        | 1.300                      |             |       | V     |

| V <sub>OH_LPDDR</sub> <sup>6</sup>                            | High Level Output Voltage, ds = 10                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -5.10 \text{ mA}$                                                        | 1.300                      |             |       | V     |

| V <sub>OH_LPDDR</sub> <sup>7</sup>                            | High Level Output Voltage, ds = 11                           | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OH} = -2.55 \text{ mA}$                                                        | 1.300                      |             |       | V     |

| V <sub>OL</sub> <sup>8</sup>                                  | Low Level Output Voltage                                     | $V_{DD\_EXT} = 1.7 \text{ V, } I_{OL} = 2.0 \text{ mA}$                                                            |                            |             | 0.400 | V     |

| V <sub>OL</sub> <sup>8</sup>                                  | Low Level Output Voltage                                     | $V_{DD\_EXT} = 3.13 \text{ V}, I_{OL} = 2.0 \text{ mA}$                                                            |                            |             | 0.400 | V     |

| $V_{OL\_DDR2}^{2}$                                            | Low Level Output Voltage, ds = 00                            | $V_{DD_{-}DMC} = 1.70 \text{ V, } I_{OL}13.4 \text{ mA}$                                                           |                            |             | 0.312 | V     |

| V <sub>OL_DDR2</sub> <sup>3</sup>                             | Low Level Output Voltage, ds = 10                            | $V_{DD_{-}DMC} = 1.70 \text{ V, } I_{OL} = 6.70 \text{ mA}$                                                        |                            |             | 0.390 | V     |

| V <sub>OL_LPDDR</sub> <sup>4</sup>                            | Low Level Output Voltage, ds = 00                            | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OL} = 11.2 \text{ mA}$                                                         |                            |             | 0.400 | V     |

| V <sub>OL_LPDDR</sub> <sup>5</sup>                            | Low Level Output Voltage, ds = 01                            | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OL} = 7.85 \text{ mA}$                                                         |                            |             | 0.400 | V     |

| V <sub>OL_LPDDR</sub> <sup>6</sup>                            | Low Level Output Voltage, ds = 10                            | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OL} = 5.10 \text{ mA}$                                                         |                            |             | 0.400 | V     |

| V <sub>OL_LPDDR</sub> <sup>7</sup>                            | Low Level Output Voltage, ds = 11                            | $V_{DD_{-}DMC} = 1.70 \text{ V}, I_{OL} = 2.55 \text{ mA}$                                                         |                            |             | 0.400 | V     |

| I <sub>IH</sub> <sup>9</sup>                                  | High Level Input Current                                     | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 10    | μΑ    |

|                                                               |                                                              | $V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                            |                            |             |       |       |

| I <sub>IH_PD</sub> <sup>10</sup>                              | High Level Input Current with Pull-                          | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 110   | μΑ    |

| 44                                                            | down Resistor                                                | $V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                            |                            |             |       |       |

| I <sub>IL</sub> <sup>11</sup>                                 | Low Level Input Current                                      | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 10    | μΑ    |

| . 12                                                          |                                                              | $V_{DD\_USB} = 3.47 \text{ V, } V_{IN} = 0 \text{ V}$                                                              |                            |             | 100   |       |

| $I_{IL\_PU}^{12}$                                             | Low Level Input Current with Pull-up<br>Resistor             | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V}, V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$    |                            |             | 100   | μΑ    |

| I <sub>IH_USB0</sub> <sup>13</sup>                            | High Level Input Current                                     |                                                                                                                    |                            |             | 240   | μΑ    |

| 'IH_USB0                                                      | riigii Levei iiiput Current                                  | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V}, V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$ |                            |             | 240   | μΛ    |

| I <sub>IL_USB0</sub> 13                                       | Low Level Input Current                                      | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                         |                            |             | 100   | μΑ    |

| -IL_03B0                                                      | 2011 2010 mp at Can ont                                      | $V_{DD\_USB} = 3.47 \text{ V, } V_{IN} = 0 \text{ V}$                                                              |                            |             |       | Fax 1 |

| I <sub>OZH</sub> <sup>14</sup>                                | Three-State Leakage Current                                  | $V_{DD EXT} = 3.47 \text{ V}, V_{DD DMC} = 1.9 \text{ V},$                                                         |                            |             | 10    | μΑ    |

|                                                               | -                                                            | $V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 3.47 \text{ V}$                                                            |                            |             |       | ľ     |

| I <sub>OZH</sub> <sup>15</sup>                                | Three-State Leakage Current                                  | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 10    | μΑ    |

|                                                               |                                                              | $V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 1.9 \text{ V}$                                                             |                            |             |       |       |

| I <sub>OZL</sub> <sup>16</sup>                                | Three-State Leakage Current                                  | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 10    | μΑ    |

| . 17                                                          |                                                              | $V_{DD\_USB} = 3.47 \text{ V, } V_{IN} = 0 \text{ V}$                                                              |                            |             |       |       |

| I <sub>OZL_PU</sub> 17                                        | Three-State Leakage Current with                             | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V},$                                                       |                            |             | 100   | μΑ    |

| 18                                                            | Pull-up Resistor                                             | $V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 0 \text{ V}$                                                               |                            |             | 10    |       |

| I <sub>OZH_TWI</sub> 18                                       | Three-State Leakage Current                                  | $V_{DD\_EXT} = 3.47 \text{ V}, V_{DD\_DMC} = 1.9 \text{ V}, V_{DD\_USB} = 3.47 \text{ V}, V_{IN} = 5.5 \text{ V}$  |                            |             | 10    | μΑ    |

| C <sub>IN</sub> <sup>19, 20</sup>                             | Input Capacitance                                            | $T_{\text{AMBIENT}} = 25^{\circ}\text{C}$                                                                          |                            | 4.9         | 6.7   | pF    |

| C <sub>IN_TWI</sub> <sup>18, 20</sup>                         | Input Capacitance                                            | $T_{AMBIENT} = 25^{\circ}C$                                                                                        |                            | 8.9         | 9.9   | pF    |

| C <sub>IN_DDR</sub> 20, 21                                    | Input Capacitance                                            | $T_{AMBIENT} = 25^{\circ}C$                                                                                        |                            | 5.8         | 6.6   | pF    |

|                                                               | V <sub>DD TD</sub> Current                                   | $V_{DD\_TD} = 3.3 \text{ V}$                                                                                       |                            | 5.0         | 1     | μΑ    |

| I <sub>DD_TD</sub> I <sub>DD_DEEPSLEEP</sub> <sup>22, 2</sup> | <sup>23</sup> V <sub>DD_INT</sub> Current in Deep Sleep Mode | $f_{CCLK} = 0 \text{ MHz}$                                                                                         |                            | Table 21 on |       | mΑ    |

| 'DD_DEEPSLEEP                                                 | V DD_INT CUITETIT III Deep Sieep Mode                        | $f_{SCLK0/1} = 0 \text{ MHz}$                                                                                      |                            | Page 58     |       | IIIA  |

| Parameter                                 |                                                      | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                    | Min | Typical | Max                                            | Unit |

|-------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------------------------------------------------|------|

| I <sub>DD_IDLE</sub> <sup>23</sup>        | V <sub>DD_INT</sub> Current in Idle                  | $\begin{split} f_{\text{CCLK}} &= 500 \text{ MHz} \\ \text{ASFC0} &= 0.14 \text{ (Idle)} \\ \text{ASFC1} &= 0 \text{ (Disabled)} \\ f_{\text{SYSCLK}} &= 250 \text{ MHz, } f_{\text{SCLK0/1}} = 125 \text{ MHz} \\ f_{\text{DCLK}} &= 0 \text{ MHz (DDR Disabled)} \\ f_{\text{USBCLK}} &= 0 \text{ MHz (USB Disabled)} \\ \text{No PVP or DMA activity} \\ T_J &= 25^{\circ}\text{C} \end{split}$ |     | 137     |                                                | mA   |

| I <sub>DD_TYP</sub> <sup>23</sup>         | V <sub>DD_INT</sub> Current                          | $f_{CCLK} = 500 \text{ MHz}$ $ASFC0 = 1.0 \text{ (Full-on Typical)}$ $ASFC1 = 0.86 \text{ (App)}$ $f_{SYSCLK} = 250 \text{ MHz, } f_{SCLK0/1} = 125 \text{ MHz}$ $f_{DCLK} = 250 \text{ MHz} \text{ (USB Disabled)}$ $DMA Data Rate = 124 \text{ MB/s}$ $Medium PVP Activity$ $T_J = 25^{\circ}C$                                                                                                  |     | 357     |                                                | mA   |

| I <sub>DD_HIBERNATE</sub> <sup>22</sup> , | <sup>24</sup> Hibernate State Current                | $V_{DD\_INT} = 0 \text{ V},$<br>$V_{DD\_EXT} = V_{DD\_TD} = V_{DD\_USB} = 3.3 \text{ V},$<br>$V_{DD\_DMC} = 1.8 \text{ V}, V_{REF\_DMC} = 0.9 \text{ V},$<br>$T_J = 25^{\circ}\text{C}, f_{CLKIN} = 0 \text{ MHz}$                                                                                                                                                                                 |     | 40      |                                                | μΑ   |

| I <sub>DD_HIBERNATE</sub> <sup>22</sup> , | <sup>24</sup> Hibernate State Current<br>Without USB | $\begin{split} &V_{DD\_INT}=0~V,\\ &V_{DD\_EXT}=V_{DD\_TD}=V_{DD\_USB}=3.3~V,\\ &V_{DD\_DMC}=1.8~V,V_{REF\_DMC}=0.9~V,\\ &T_{J}=25^{\circ}C,\\ &f_{CLKIN}=0~MHz,USB~protection\\ &disabled~(USB0\_PHY\_CTL.DIS=1) \end{split}$                                                                                                                                                                     |     | 10      |                                                | μΑ   |

| I <sub>DD_INT</sub> <sup>23</sup>         | V <sub>DD_INT</sub> Current                          | $f_{CCLK} > 0 \text{ MHz}$<br>$f_{SCLK0/1} \ge 0 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                      |     |         | See I <sub>DDINT_TOT</sub> equation on Page 57 | mA   |

<sup>&</sup>lt;sup>1</sup> Applies to all output and bidirectional signals except DMC0 signals, TWI signals and USB0 signals.

<sup>&</sup>lt;sup>2</sup> Applies to all DMC0 output and bidirectional signals in DDR2 full drive strength mode.

<sup>&</sup>lt;sup>3</sup> Applies to all DMC0 output and bidirectional signals in DDR2 half drive strength mode.

<sup>&</sup>lt;sup>4</sup> Applies to all DMC0 output and bidirectional signals in LPDDR full drive strength mode.

<sup>&</sup>lt;sup>5</sup> Applies to all DMC0 output and bidirectional signals in LPDDR three-quarter drive strength mode.

<sup>&</sup>lt;sup>6</sup> Applies to all DMC0 output and bidirectional signals in LPDDR half drive strength mode.

<sup>&</sup>lt;sup>7</sup> Applies to all DMC0 output and bidirectional signals in LPDDR one-quarter drive strength mode.

<sup>&</sup>lt;sup>8</sup> Applies to all output and bidirectional signals except DMC0 signals and USB0 signals.

<sup>9</sup> Applies to signals SMC0\_ARDY, SMC0\_BR, SYS\_BMODE0-2, SYS\_CLKIN, SYS\_HWRST, SYS\_PWRGD, JTG\_TDI, and JTG\_TMS.

<sup>&</sup>lt;sup>10</sup>Applies to signals JTG\_TCK and JTG\_TRST.

<sup>&</sup>lt;sup>11</sup>Applies to signals SMC0\_ARDY, SMC0\_BR, SYS\_BMODE0-2, SYS\_CLKIN, SYS\_HWRST, SYS\_PWRGD, JTG\_TCK, and JTG\_TRST.

<sup>&</sup>lt;sup>12</sup>Applies to signals JTG\_TDI, JTG\_TMS.

<sup>&</sup>lt;sup>13</sup>Applies to signal USB0\_CLKIN.

<sup>14</sup> Applies to signals PA0-15, PB0-15, PC0-15, PD0-15, PE0-15, PF0-15, PG0-15, SMC0\_AMS0, SMC0\_ARE, SMC0\_AWE, SMC0\_A0E, SMC0\_A01-02, SMC0\_D00-15, SYS\_FAULT, SYS\_FAULT, JTG\_EMU, JTG\_TDO, USB0\_DM, USB0\_DP, USB0\_ID, USB0\_VBC, USB0\_VBUS.

<sup>15</sup> Applies to DMC0\_A[00:13], DMC0\_BA[0:2], DMC0\_CAS, DMC0\_CS0, DMC0\_DQ[00:15], DMC0\_LQDS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_UDQS DMC0\_UDM, DMC0\_ODT, DMC0\_RAS, and DMC0\_WE.

<sup>16</sup> Applies to signals PA0-15, PB0-15, PC0-15, PD0-15, PE0-15, PF0-15, PG0-15, \overline{SMC0\_A0E}, SMC0\_A01-02, SMC0\_D00-15, SYS\_FAULT, \overline{SYS\_FAULT}, \overline{JTG\_EMU}, JTG\_TDO, USB0\_DM, USB0\_DP, USB0\_ID, USB0\_VBC, USB0\_VBUS, DMC0\_A00-13, DMC0\_BA0-2, \overline{DMC0\_CAS}, \overline{DMC0\_CS0}, DMC0\_DQ00-15, DMC0\_LQDS, DMC0\_LDQS, DMC0\_UDQS, DMC0\_UDQS, DMC0\_LDM, DMC0\_UDM, DMC0\_ODT, DMC0\_RAS, DMC0\_WE, and TWI signals.

<sup>&</sup>lt;sup>17</sup>Applies to signals SMC0\_AMS0, SMC0\_ARE, SMC0\_AWE, and when RSI pull-up resistors are enabled, PE10-13, 15 and PG00, 02, 03, 05.

<sup>&</sup>lt;sup>18</sup>Applies to all TWI signals.

<sup>&</sup>lt;sup>19</sup>Applies to all signals, except DMC0 and TWI signals.

<sup>&</sup>lt;sup>20</sup>Guaranteed, but not tested.

<sup>&</sup>lt;sup>21</sup>Applies to all DMC0 signals.

<sup>&</sup>lt;sup>22</sup>See the ADSP-BF60x Blackfin Processor Hardware Reference Manual for definition of deep sleep and hibernate operating modes.

<sup>&</sup>lt;sup>23</sup>Additional information can be found at Total Internal Power Dissipation on Page 57.

<sup>&</sup>lt;sup>24</sup>Applies to V<sub>DD EXT</sub>, V<sub>DD DMC</sub>, V<sub>DD USB</sub> and V<sub>DD TD</sub> supply signals only. Clock inputs are tied high or low.

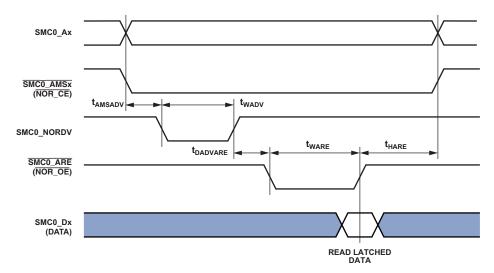

### Asynchronous Flash Read

Table 29. Asynchronous Flash Read

|                       |                                                                          | V <sub>DD_EXT</sub> 1.8 V/3.3 V Nominal |     |      |

|-----------------------|--------------------------------------------------------------------------|-----------------------------------------|-----|------|

| Parameter             |                                                                          | Min                                     | Max | Unit |

| Switching C           | haracteristics                                                           |                                         |     |      |

| t <sub>AMSADV</sub>   | SMC0_Ax (Address)/SMC0_AMSx Assertion Before SMC0_NORDV Low <sup>1</sup> | $PREST \times t_{SCLK0} - 2$            |     | ns   |

| t <sub>WADV</sub>     | SMC0_NORDV Active Low Width <sup>2</sup>                                 | $RST \times t_{SCLK0} - 2$              |     | ns   |

| t <sub>DADVARE</sub>  | SMC0_ARE Low Delay From SMC0_NORDV High <sup>3</sup>                     | $PREAT \times t_{SCLK0} - 2$            |     | ns   |

| t <sub>HARE</sub>     | Output <sup>4</sup> Hold After SMC0_ARE High <sup>5</sup>                | $RHT \times t_{SCLK0} - 2$              |     | ns   |

| $t_{\text{WARE}}^{}}$ | SMC0_ARE Active Low Width <sup>7</sup>                                   | $RAT \times t_{SCLK0} - 2$              |     | ns   |

$<sup>^{\</sup>rm 1}\,{\rm PREST}$  value set using the SMC\_BxETIM.PREST bits.

$<sup>^7\,\</sup>mathrm{RAT}$  value set using the SMC\_BxTIM.RAT bits.

Figure 13. Asynchronous Flash Read

<sup>&</sup>lt;sup>2</sup>RST value set using the SMC\_BxTIM.RST bits.

<sup>&</sup>lt;sup>3</sup> PREAT value set using the SMC\_BxETIM.PREAT bits.

$<sup>^4</sup>$  Output signals are SMC0\_Ax,  $\overline{SMC0\_AMS}, \overline{SMC0\_AOE}.$

$<sup>^{5}\,\</sup>mathrm{RHT}$  value set using the SMC\_BxTIM.RHT bits.

<sup>&</sup>lt;sup>6</sup> SMC0\_BxCTL.ARDYEN bit = 0.

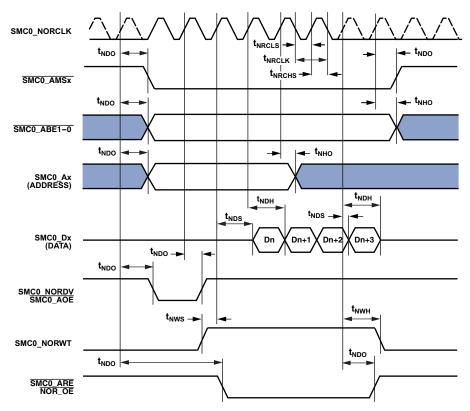

NOTE: SMC0\_NORCLK dotted line represents a free running version of SMC0\_NORCLK that is not visible on the SMC0\_NORCLK pin.

Figure 15. Synchronous Burst AC Interface Timing

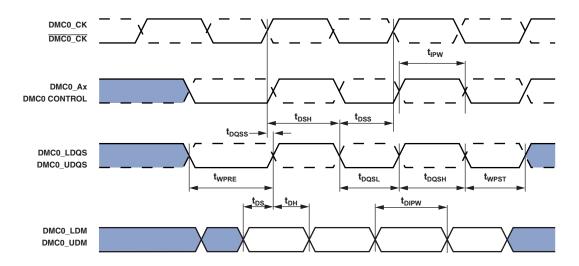

### DDR2 SDRAM Write Cycle Timing

Table 38. DDR2 SDRAM Write Cycle Timing,  $V_{DD\_DMC}$  Nominal 1.8 V

|                                |                                                                |       | 250 MHz <sup>1</sup> |                 |

|--------------------------------|----------------------------------------------------------------|-------|----------------------|-----------------|

| Parameter                      |                                                                | Min   | Max                  | Unit            |

| Switching Chard                | acteristics                                                    |       |                      |                 |

| t <sub>DQSS</sub> <sup>2</sup> | DMC0_DQS Latching Rising Transitions to Associated Clock Edges | -0.15 | 0.15                 | t <sub>CK</sub> |

| $t_{DS}$                       | Last Data Valid to DMC0_DQS Delay                              | 0.15  |                      | ns              |

| t <sub>DH</sub>                | DMC0_DQS to First Data Invalid Delay                           | 0.3   |                      | ns              |

| t <sub>DSS</sub>               | DMC0_DQS Falling Edge to Clock Setup Time                      | 0.25  |                      | t <sub>CK</sub> |

| t <sub>DSH</sub>               | DMC0_DQS Falling Edge Hold Time From DMC0_CK                   | 0.25  |                      | t <sub>CK</sub> |

| t <sub>DQSH</sub>              | DMC0_DQS Input High Pulse Width                                | 0.35  |                      | t <sub>CK</sub> |

| t <sub>DQSL</sub>              | DMC0_DQS Input Low Pulse Width                                 | 0.35  |                      | t <sub>CK</sub> |

| t <sub>WPRE</sub>              | Write Preamble                                                 | 0.35  |                      | t <sub>CK</sub> |

| t <sub>WPST</sub>              | Write Postamble                                                | 0.4   |                      | t <sub>CK</sub> |

| t <sub>IPW</sub>               | Address and Control Output Pulse Width                         | 0.6   |                      | t <sub>CK</sub> |

| $t_{DIPW}$                     | DMC0_DQ and DMC0_DM Output Pulse Width                         | 0.35  |                      | t <sub>CK</sub> |

<sup>&</sup>lt;sup>1</sup> In order to ensure proper operation of the DDR2, all the DDR2 guidelines have to be strictly followed.

<sup>&</sup>lt;sup>2</sup> Write command to first DMC0\_DQS delay = WL ×  $t_{CK}$  +  $t_{DQSS}$ .

Figure 21. DDR2 SDRAM Controller Output AC Timing

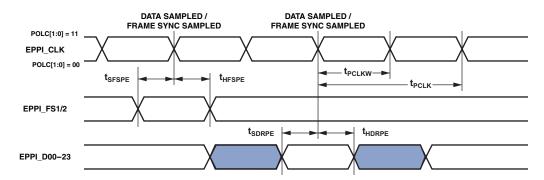

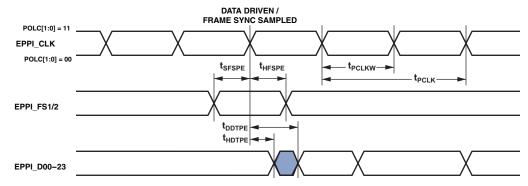

Figure 32. PPI External Clock GP Receive Mode with External Frame Sync Timing

Figure 33. PPI External Clock GP Transmit Mode with External Frame Sync Timing

### **Link Ports**

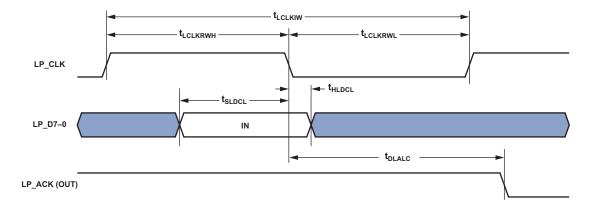

In link port receive mode the link port clock is supplied externally and is called  $f_{\text{LCLKREXT}}$ :

$$t_{LCLKREXT} = \frac{1}{f_{LCLKREXT}}$$

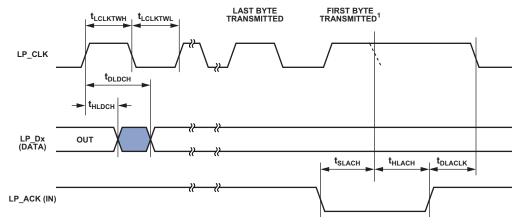

In link port transmit mode the programmed link port clock ( $f_{\rm LCLKTPROG}$ ) frequency in MHz is set by the following equation where VALUE is a field in the LP\_DIV register that can be set from 1 to 255:

$$f_{LCLKTPROG} = \frac{f_{SCLK0}}{(VALUE \times 2)}$$

Table 44. Link Ports—Receive

In the case where VALUE = 0,  $f_{LCLKTPROG} = f_{SCLK0}$ . For all settings of VALUE the following equation also holds:

$$t_{LCLKTPROG} = \frac{1}{f_{LCLKTPROG}}$$

Calculation of link receiver data setup and hold relative to link clock is required to determine the maximum allowable skew that can be introduced in the transmission path length difference between LP\_Dx (data) and LP\_CLK. Setup skew is the maximum delay that can be introduced in LP\_Dx relative to LP\_CLK:

(setup skew =  $t_{LCLKTWH}$  min –  $t_{DLDCH}$  –  $t_{SLDCL}$ ). Hold skew is the maximum delay that can be introduced in LP\_CLK relative to LP\_Dx: (hold skew =  $t_{LCLKTWL}$  min –  $t_{HLDCH}$  –  $t_{HLDCL}$ ).

|                      |                                                | V <sub>DD_EXT</sub> 1.8 V Nominal/3.3 V Nominal                        |                             |      |  |

|----------------------|------------------------------------------------|------------------------------------------------------------------------|-----------------------------|------|--|

| Parameter            |                                                | Min                                                                    | Max                         | Unit |  |

| Timing Requirements  |                                                |                                                                        |                             |      |  |

| $t_{SLDCL}$          | Data Setup Before LP_CLK Low                   | 2                                                                      |                             | ns   |  |

| t <sub>HLDCL</sub>   | Data Hold After LP_CLK Low                     | 3                                                                      |                             | ns   |  |

| t <sub>LCLKIW</sub>  | LP_CLK Period <sup>1</sup>                     | t <sub>LCLKREXT</sub> – 1.5                                            |                             | ns   |  |

| t <sub>LCLKRWL</sub> | LP_CLK Width Low <sup>1</sup>                  | $(0.5 \times t_{LCLKREXT}) - 1.5$                                      |                             | ns   |  |

| t <sub>LCLKRWH</sub> | LP_CLK Width High <sup>1</sup>                 | $(0.5 \times t_{LCLKREXT}) - 1.5$<br>$(0.5 \times t_{LCLKREXT}) - 1.5$ |                             | ns   |  |

| Switching Ch         | aracteristic                                   |                                                                        |                             |      |  |

| tolaic               | LP ACK Low Delay After LP CLK Low <sup>2</sup> | $1.5 \times t_{SCLK0} + 4$                                             | $2.5 \times t_{SCLK0} + 12$ | ns   |  |

<sup>&</sup>lt;sup>1</sup>This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external LP\_CLK. For the external LP\_CLK ideal maximum frequency see the f<sub>LCLKTEXT</sub> specification in Table 17 on Page 53 in Clock Related Operating Conditions.

<sup>&</sup>lt;sup>2</sup> LP\_ACK goes low with t<sub>DLALC</sub> relative to rise of LP\_CLK after first byte, but does not go low if the receiver's link buffer is not about to fill.

Figure 34. Link Ports—Receive

Table 45. Link Ports—Transmit

|                                   |                                       |                              | / <sub>DD_EXT</sub><br>/ Nominal       | V <sub>DD_EXT</sub><br>3.3 V Nominal |                                        |      |

|-----------------------------------|---------------------------------------|------------------------------|----------------------------------------|--------------------------------------|----------------------------------------|------|

| Parameter                         |                                       | Min                          | Max                                    | Min                                  | Max                                    | Unit |

| Timing Red                        | quirements                            |                              |                                        |                                      |                                        |      |

| t <sub>SLACH</sub>                | LP_ACK Setup Before LP_CLK Low        | $2 \times t_{SCLK0} + 17.5$  |                                        | $2 \times t_{SCLK0} + 13.5$          |                                        | ns   |

| $t_{HLACH}$                       | LP_ACK Hold After LP_CLK Low          | 0                            |                                        | 0                                    |                                        | ns   |

| Switching Characteristics         |                                       |                              |                                        |                                      |                                        |      |

| $t_{DLDCH}$                       | Data Delay After LP_CLK High          |                              | 2.5                                    |                                      | 2.5                                    | ns   |

| $t_{\text{HLDCH}}$                | Data Hold After LP_CLK High           | -1.5                         |                                        | -1.5                                 |                                        | ns   |

| t <sub>LCLKTWL</sub> <sup>1</sup> | LP_CLK Width Low                      | $0.4 \times t_{LCLKTPROG}$   | $0.6 \times t_{LCLKTPROG}$             | $0.4 \times t_{LCLKTPROG}$           | $0.6 \times t_{LCLKTPROG}$             | ns   |

| t <sub>LCLKTWH</sub> 1            | LP_CLK Width High                     | $0.4 \times t_{LCLKTPROG}$   | $0.6 \times t_{LCLKTPROG}$             | $0.4 \times t_{LCLKTPROG}$           | $0.6 \times t_{LCLKTPROG}$             | ns   |