Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Active                                                                    |

| Туре                    | Dual Core                                                                 |

| Interface               | CAN, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 500MHz                                                                    |

| Non-Volatile Memory     | ROM (64kB)                                                                |

| On-Chip RAM             | 808K x 8                                                                  |

| Voltage - I/O           | 1.8V, 3.3V                                                                |

| Voltage - Core          | 1.25V                                                                     |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 349-LFBGA, CSPBGA                                                         |

| Supplier Device Package | 349-CSPBGA (19x19)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adbf608wcbcz502rl     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

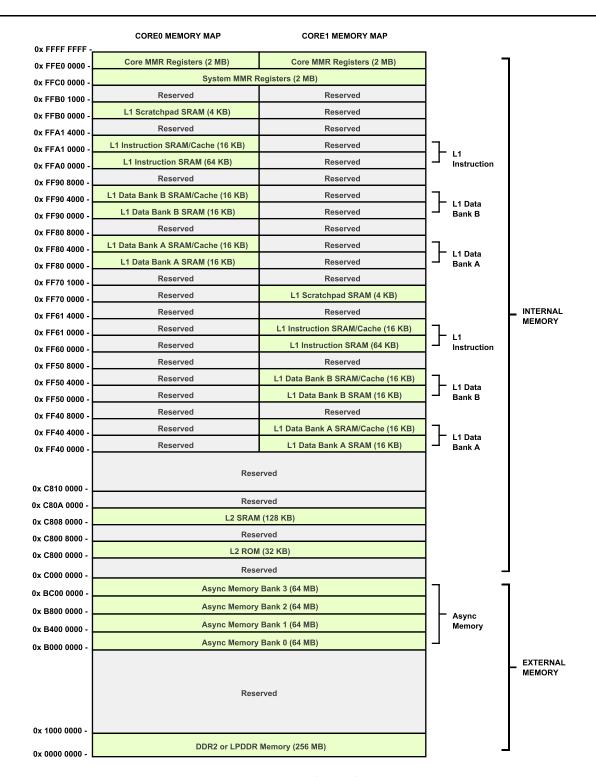

Figure 3. ADSP-BF606 Internal/External Memory Map

- A 32-bit threshold block with 16 thresholds, a histogram, and run-length encoding

- Two 32-bit integral blocks that support regular and diagonal integrals

- An up- and down-scaling unit with independent scaling ratios for horizontal and vertical components

- Input and output formatters for compatibility with many data formats, including Bayer input format

The PVP can form a pipe of all the constituent algorithmic modules and is dynamically reconfigurable to form different pipeline structures.

The PVP supports the simultaneous processing of up to four data streams. The memory pipe stream operates on data received by DMA from any L1, L2, or L3 memory. The three camera pipe streams operate on a common input received directly from any of the three PPI inputs. Optionally, the PIXC can convert color data received by the PPI and forward luma values to the PVP's monochrome engine. Each stream has a dedicated DMA output. This preprocessing concept ensures careful use of available power and bandwidth budgets and frees up the processor cores for other tasks.

The PVP provides for direct core MMR access to all control/status registers. Two hardware interrupts interface to the system event controller. For optimal performance, the PVP allows register programming through its control DMA interface, as well as outputting selected status registers through the status DMA interface. This mechanism enables the PVP to automatically process job lists completely independent of the Blackfin cores.

#### **Pixel Compositor (PIXC)**

The pixel compositor (PIXC) provides image overlays with transparent-color support, alpha blending, and color space conversion capabilities for output to TFT LCDs and NTSC/PAL video encoders. It provides all of the control to allow two data streams from two separate data buffers to be combined, blended, and converted into appropriate forms for both LCD panels and digital video outputs. The main image buffer provides the basic background image, which is presented in the data stream. The overlay image buffer allows the user to add multiple foreground text, graphics, or video objects on top of the main image or video data stream.

#### Parallel Peripheral Interface (PPI)

The processor provides up to three parallel peripheral interfaces (PPIs), supporting data widths up to 24 bits. The PPI supports direct connection to TFT LCD panels, parallel analog-to-digital and digital-to-analog converters, video encoders and decoders, image sensor modules and other general-purpose peripherals.

The following features are supported in the PPI module:

- Programmable data length: 8 bits, 10 bits, 12 bits, 14 bits, 16 bits, 18 bits, and 24 bits per clock.

- Various framed, non-framed, and general-purpose operating modes. Frame syncs can be generated internally or can be supplied by an external device.

- ITU-656 status word error detection and correction for ITU-656 receive modes and ITU-656 preamble and status word decode.

- Optional packing and unpacking of data to/from 32 bits from/to 8 bits, 16 bits and 24 bits. If packing/unpacking is enabled, endianness can be configured to change the order of packing/unpacking of bytes/words.

- RGB888 can be converted to RGB666 or RGB565 for transmit modes.

- Various de-interleaving/interleaving modes for receiving/transmitting 4:2:2 YCrCb data.

- Configurable LCD data enable (DEN) output available on Frame Sync 3.

#### **PROCESSOR SAFETY FEATURES**

The ADSP-BF60x processor has been designed for functional safety applications. While the level of safety is mainly dominated by the system concept, the following primitives are provided by the devices to build a robust safety concept.

#### **Dual Core Supervision**

The processor has been implemented as dual-core devices to separate critical tasks to large independency. Software models support mutual supervision of the cores in symmetrical fashion.

#### Multi-Parity-Bit-Protected L1 Memories

In the processor's L1 memory space, whether SRAM or cache, each word is protected by multiple parity bits to detect the single event upsets that occur in all RAMs. This applies both to L1 instruction and data memory spaces.

#### **ECC-Protected L2 Memories**

Error correcting codes (ECC) are used to correct single event upsets. The L2 memory is protected with a Single Error Correct-Double Error Detect (SEC-DED) code. By default ECC is enabled, but it can be disabled on a per-bank basis. Single-bit errors are transparently corrected. Dual-bit errors can issue a system event or fault if enabled. ECC protection is fully transparent to the user, even if L2 memory is read or written by 8-bit or 16-bit entities.

#### **CRC-Protected Memories**

While parity bit and ECC protection mainly protect against random soft errors in L1 and L2 memory cells, the CRC engines can be used to protect against systematic errors (pointer errors) and static content (instruction code) of L1, L2 and even L3 memories (DDR2, LPDDR). The processors feature two CRC engines which are embedded in the memory-to-memory DMA controllers. CRC check sums can be calculated or compared on the fly during memory transfers, or one or multiple memory regions can be continuously scrubbed by single DMA work unit as per DMA descriptor chain instructions. The CRC engine also protects data loaded during the boot process.

#### **Memory Protection**

The Blackfin cores feature a memory protection concept, which grants data and/or instruction accesses from enabled memory regions only. A supervisor mode vs. user mode programming model supports dynamically varying access rights. Increased flexibility in memory page size options supports a simple method of static memory partitioning.

#### **System Protection**

All system resources and L2 memory banks can be controlled by either the processor cores, memory-to-memory DMA, or the system debug unit (SDU). A system protection unit (SPU) enables write accesses to specific resources that are locked to any of four masters: Core 0, Core 1, Memory DMA, and the System Debug Unit. System protection is enabled in greater granularity for some modules (L2, SEC and GPIO controllers) through a *global lock* concept.

#### **Watchpoint Protection**

The primary purpose of watchpoints and hardware breakpoints is to serve emulator needs. When enabled, they signal an emulator event whenever user-defined system resources are accessed or a core executes from user-defined addresses. Watchpoint events can be configured such that they signal the events to the other Blackfin core or to the fault management unit.

#### **Dual Watchdog**

The two on-chip watchdog timers each may supervise one Blackfin core.

#### **Bandwidth Monitor**

All DMA channels that operate in memory-to-memory mode (Memory DMA, PVP Memory Pipe DMA, PIXC DMA) are equipped with a bandwidth monitor mechanism. They can signal a system event or fault when transactions tend to starve because system buses are fully loaded with higher-priority traffic.

#### Signal Watchdogs

The eight general-purpose timers feature two new modes to monitor off-chip signals. The Watchdog Period mode monitors whether external signals toggle with a period within an expected range. The Watchdog Width mode monitors whether the pulse widths of external signals are in an expected range. Both modes help to detect incorrect undesired toggling (or lack thereof) of system-level signals.

#### **Up/Down Count Mismatch Detection**

The up/down counter can monitor external signal pairs, such as request/grant strobes. If the edge count mismatch exceeds the expected range, the up/down counter can flag this to the processor or to the fault management unit.

#### **Fault Management**

The fault management unit is part of the system event controller (SEC). Any system event, whether a dual-bit uncorrectable ECC error, or any peripheral status interrupt, can be defined as being

a "fault". Additionally, the system events can be defined as an interrupt to the cores. If defined as such, the SEC forwards the event to the fault management unit which may automatically reset the entire device for reboot, or simply toggle the SYS\_FAULT output pins to signal off-chip hardware. Optionally, the fault management unit can delay the action taken via a keyed sequence, to provide a final chance for the Blackfin cores to resolve the crisis and to prevent the fault action from being taken.

#### ADDITIONAL PROCESSOR PERIPHERALS

The processor contains a rich set of peripherals connected to the core via several high-bandwidth buses, providing flexibility in system configuration as well as excellent overall system performance (see the block diagram on Page 1). The processors contain high-speed serial and parallel ports, an interrupt controller for flexible management of interrupts from the on-chip peripherals or external sources, and power management control functions to tailor the performance and power characteristics of the processor and system to many application scenarios.

The following sections describe additional peripherals that were not described in the previous sections.

#### Timers

The processor includes several timers which are described in the following sections.

#### **General-Purpose Timers**

There is one GP timer unit and it provides eight general-purpose programmable timers. Each timer has an external pin that can be configured either as a pulse width modulator (PWM) or timer output, as an input to clock the timer, or as a mechanism for measuring pulse widths and periods of external events. These timers can be synchronized to an external clock input on the TMRx pins, an external clock TMRCLK input pin, or to the internal SCLKO.

The timer units can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The timers can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals via the TRU (for instance, to signal a fault).

#### **Core Timers**

Each processor core also has its own dedicated timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### **Watchdog Timers**

Each core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, via generation of a hardware reset, nonmaskable interrupt (NMI), or general-purpose interrupt, if the timer expires before

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumb wheels. All three pins have a programmable debouncing circuit.

Internal signals forwarded to each general-purpose timer enable these timers to measure the intervals between count events. Boundary registers enable auto-zero operation or simple system warning by interrupts when programmable count values are exceeded.

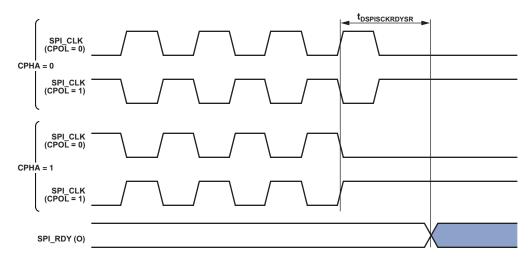

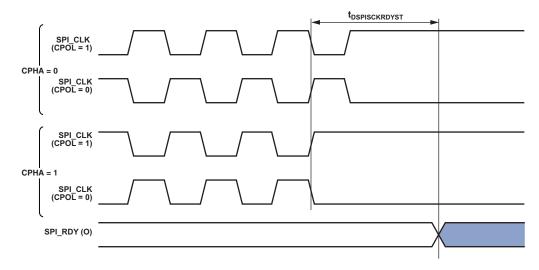

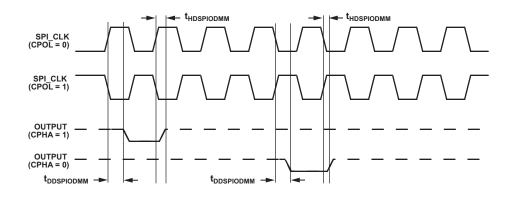

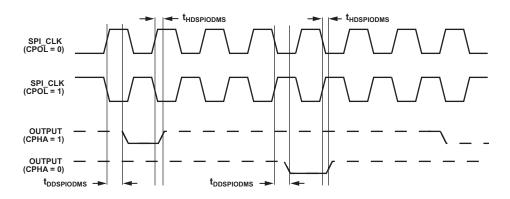

#### Serial Peripheral Interface (SPI) Ports

The processors have two SPI-compatible ports that allow the processor to communicate with multiple SPI-compatible devices.

In its simplest mode, the SPI interface uses three pins for transferring data: two data pins (Master Output-Slave Input, MOSI, and Master Input-Slave Output, MISO) and a clock pin (serial clock, SPI\_CLK). A SPI chip select input pin (SPI\_SS) lets other SPI devices select the processor, and seven SPI chip select output pins (SPI\_SEL7-1) let the processor select other SPI devices. The SPI select pins are reconfigured general-purpose I/O pins. Using these pins, the SPI port provides a full-duplex, synchronous serial interface, which supports both master/slave modes and multimaster environments.

In a multi-master or multi-slave SPI system, the MOSI and MISO data output pins can be configured to behave as open drain outputs (using the ODM bit) to prevent contention and possible damage to pin drivers. An external pull-up resistor is required on both the MOSI and MISO pins when this option is selected.

When ODM is set and the SPI is configured as a master, the MOSI pin is three-stated when the data driven out on MOSI is a logic-high. The MOSI pin is not three-stated when the driven data is a logic-low. Similarly, when ODM is set and the SPI is configured as a slave, the MISO pin is three-stated if the data driven out on MISO is a logic-high.

The SPI port's baud rate and clock phase/polarities are programmable, and it has integrated DMA channels for both transmit and receive data streams.

#### **UART Ports**

The processors provide two full-duplex universal asynchronous receiver/transmitter (UART) ports, which are fully compatible with PC-standard UARTs. Each UART port provides a simplified UART interface to other peripherals or hosts, supporting full-duplex, DMA-supported, asynchronous transfers of serial data. A UART port includes support for five to eight data bits, and none, even, or odd parity. Optionally, an additional address bit can be transferred to interrupt only addressed nodes in multi-drop bus (MDB) systems. A frame is terminates by one, one and a half, two or two and a half stop bits.

The UART ports support automatic hardware flow control through the Clear To Send (CTS) input and Request To Send (RTS) output with programmable assertion FIFO levels.

To help support the Local Interconnect Network (LIN) protocols, a special command causes the transmitter to queue a break command of programmable bit length into the transmit buffer. Similarly, the number of stop bits can be extended by a programmable inter-frame space.

The capabilities of the UARTs are further extended with support for the Infrared Data Association (IrDA\*) serial infrared physical layer link specification (SIR) protocol.

#### TWI Controller Interface

The processors include a 2-wire interface (TWI) module for providing a simple exchange method of control data between multiple devices. The TWI module is compatible with the widely used I<sup>2</sup>C bus standard. The TWI module offers the capabilities of simultaneous master and slave operation and support for both 7-bit addressing and multimedia data arbitration. The TWI interface utilizes two pins for transferring clock (TWI\_SCL) and data (TWI\_SDA) and supports the protocol at speeds up to 400k bits/sec. The TWI interface pins are compatible with 5 V logic levels.

Additionally, the TWI module is fully compatible with serial camera control bus (SCCB) functionality for easier control of various CMOS camera sensor devices.

#### Removable Storage Interface (RSI)

The removable storage interface (RSI) controller acts as the host interface for multimedia cards (MMC), secure digital memory cards (SD), secure digital input/output cards (SDIO). The following list describes the main features of the RSI controller.

- Support for a single MMC, SD memory, SDIO card

- Support for 1-bit and 4-bit SD modes

- Support for 1-bit, 4-bit, and 8-bit MMC modes

- Support for eMMC 4.3 embedded NAND flash devices

- A ten-signal external interface with clock, command, and up to eight data lines

- Card interface clock generation from SCLK0

- · SDIO interrupt and read wait features

#### Controller Area Network (CAN)

A CAN controller implements the CAN 2.0B (active) protocol. This protocol is an asynchronous communications protocol used in both industrial and automotive control systems. The CAN protocol is well suited for control applications due to its capability to communicate reliably over a network. This is because the protocol incorporates CRC checking, message error tracking, and fault node confinement.

The CAN controller offers the following features:

- 32 mailboxes (8 receive only, 8 transmit only, 16 configurable for receive or transmit).

- Dedicated acceptance masks for each mailbox.

- Additional data filtering on first two bytes.

- Support for both the standard (11-bit) and extended (29-bit) identifier (ID) message formats.

From a system perspective reset is defined by both the reset target and the reset source as described below.

#### Target defined:

- Hardware Reset All functional units are set to their default states without exception. History is lost.

- System Reset All functional units except the RCU are set to their default states.

- Core-n only Reset Affects Core-n only. The system software should guarantee that the core in reset state is not accessed by any bus master.

#### Source defined:

- Hardware Reset The SYS\_HWRST input signal is asserted active (pulled down).

- System Reset May be triggered by software (writing to the RCU\_CTL register) or by another functional unit such as the dynamic power management (DPM) unit (Hibernate) or any of the system event controller (SEC), trigger routing unit (TRU), or emulator inputs.

- Core-n-only reset Triggered by software.

- Trigger request (peripheral).

#### **Voltage Regulation**

The processor requires an external voltage regulator to power the  $V_{\text{DD\_INT}}$  pins. To reduce standby power consumption, the external voltage regulator can be signaled through SYS\_ EXTWAKE to remove power from the processor core. This signal is high-true for power-up and may be connected directly to the low-true shut-down input of many common regulators.

While in the hibernate state, all external supply pins ( $V_{DD\_EXT}$ ,  $V_{DD\_USB}$ ,  $V_{DD\_DMC}$ ) can still be powered, eliminating the need for external buffers. The external voltage regulator can be activated from this power down state by asserting the  $\overline{SYS\_HWRST}$  pin, which then initiates a boot sequence.  $SYS\_EXTWAKE$  indicates a wakeup to the external voltage regulator.

#### **SYSTEM DEBUG**

The processor includes various features that allow for easy system debug. These are described in the following sections.

#### System Watchpoint Unit

The System Watchpoint Unit (SWU) is a single module which connects to a single system bus and provides for transaction monitoring. One SWU is attached to the bus going to each system slave. The SWU provides ports for all system bus address channel signals. Each SWU contains four match groups of registers with associated hardware. These four SWU match groups operate independently, but share common event (interrupt, trigger and others) outputs.

#### System Debug Unit

The System Debug Unit (SDU) provides IEEE-1149.1 support through its JTAG interface. In addition to traditional JTAG features, present in legacy Blackfin products, the SDU adds more features for debugging the chip without halting the core processors.

#### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (which include CrossCore® Embedded Studio and/or VisualDSP++®), evaluation products, emulators, and a wide variety of software add-ins.

#### **Integrated Development Environments (IDEs)**

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers two IDEs.

The newest IDE, CrossCore Embedded Studio, is based on the Eclipse™ framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information visit www.analog.com/cces.

The other Analog Devices IDE, VisualDSP++, supports processor families introduced prior to the release of CrossCore Embedded Studio. This IDE includes the Analog Devices VDK real time operating system and an open source TCP/IP stack. For more information visit www.analog.com/visualdsp. Note that VisualDSP++ will not support future Analog Devices processors.

#### **EZ-KIT Lite Evaluation Board**

For processor evaluation, Analog Devices provides wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information visit www.analog.com and search on "ezkit" or "ezextender".

#### **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of

Table 6. Detailed Signal Descriptions (Continued)

| Signal Name | Direction | Description                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSI_CLK     | Output    | Clock The clock signal applied to the connected device from the RSI.                                                                                                                                                                                                                                                                                            |

| RSI_CMD     | I/O       | <b>Command</b> Used to send commands to and receive responses from the connected device.                                                                                                                                                                                                                                                                        |

| RSI_Dn      | I/O       | Data n Bidirectional data bus.                                                                                                                                                                                                                                                                                                                                  |

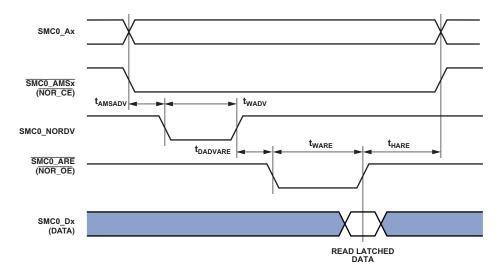

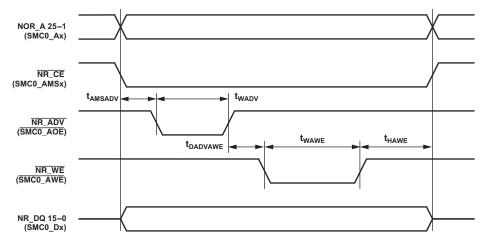

| SMC_ABEn    | Output    | Byte Enable n Indicate whether the lower or upper byte of a memory is being accessed. When an asynchronous write is made to the upper byte of a 16-bit memory, $\overline{SMC\_ABE1} = 0$ and $\overline{SMC\_ABE0} = 1$ . When an asynchronous write is made to the lower byte of a 16-bit memory, $\overline{SMC\_ABE1} = 1$ and $\overline{SMC\_ABE0} = 0$ . |

| SMC_AMSn    | Output    | Memory Select n Typically connects to the chip select of a memory device.                                                                                                                                                                                                                                                                                       |

| SMC_Ann     | Output    | Address n Address bus.                                                                                                                                                                                                                                                                                                                                          |

| SMC_AOE     | Output    | Output Enable Asserts at the beginning of the setup period of a read access.                                                                                                                                                                                                                                                                                    |

| SMC_ARDY    | Input     | <b>Asynchronous Ready</b> Flow control signal used by memory devices to indicate to the SMC when further transactions may proceed.                                                                                                                                                                                                                              |

| SMC_ARE     | Output    | <b>Read Enable</b> Asserts at the beginning of a read access.                                                                                                                                                                                                                                                                                                   |

| SMC_AWE     | Output    | Write Enable Asserts for the duration of a write access period.                                                                                                                                                                                                                                                                                                 |

| SMC_BG      | Output    | <b>Bus Grant</b> Output used to indicate to an external device that it has been granted control of the SMC buses.                                                                                                                                                                                                                                               |

| SMC_BGH     | Output    | <b>Bus Grant Hang</b> Output used to indicate that the SMC has a pending transaction which requires control of the bus to be restored before it can be completed.                                                                                                                                                                                               |

| SMC_BR      | Input     | <b>Bus Request</b> Input used by an external device to indicate that it is requesting control of the SMC buses.                                                                                                                                                                                                                                                 |

| SMC_Dnn     | I/O       | Data n Bidirectional data bus.                                                                                                                                                                                                                                                                                                                                  |

| SMC_NORCLK  | Output    | NOR Clock Clock for synchronous burst mode.                                                                                                                                                                                                                                                                                                                     |

| SMC_NORDV   | Output    | NOR Data Valid Asserts for the duration of a synchronous burst mode read setup period.                                                                                                                                                                                                                                                                          |

| SMC_NORWT   | Input     | <b>NOR Wait</b> Flow control signal used by memory devices in synchronous burst mode to indicate to the SMC when further transactions may proceed.                                                                                                                                                                                                              |

| SPI_CLK     | I/O       | Clock Input in slave mode, output in master mode.                                                                                                                                                                                                                                                                                                               |

| SPI_D2      | I/O       | Data 2 Used to transfer serial data in quad mode. Open drain in ODM mode.                                                                                                                                                                                                                                                                                       |

| SPI_D3      | I/O       | Data 3 Used to transfer serial data in quad mode. Open drain in ODM mode.                                                                                                                                                                                                                                                                                       |

| SPI_MISO    | I/O       | <b>Master In, Slave Out</b> Used to transfer serial data. Operates in the same direction as SPI_MOSI in dual and quad modes. Open drain in ODM mode.                                                                                                                                                                                                            |

| SPI_MOSI    | I/O       | <b>Master Out, Slave In</b> Used to transfer serial data. Operates in the same direction as SPI_MISO in dual and quad modes. Open drain in ODM mode.                                                                                                                                                                                                            |

| SPI_RDY     | I/O       | <b>Ready</b> Optional flow signal. Output in slave mode, input in master mode.                                                                                                                                                                                                                                                                                  |

| SPI_SELn    | Output    | Slave Select Output n Used in master mode to enable the desired slave.                                                                                                                                                                                                                                                                                          |

| SPI_SS      | Input     | <b>Slave Select Input</b> Slave mode: acts as the slave select input. Master mode: optionally serves as an error detection input for the SPI when there are multiple masters.                                                                                                                                                                                   |

| SPT_ACLK    | I/O       | <b>Channel A Clock</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                                                                                                                         |

| SPT_AD0     | I/O       | <b>Channel A Data 0</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                                                                              |

| SPT_AD1     | I/O       | <b>Channel A Data 1</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                                                                            |

| SPT_AFS     | I/O       | <b>Channel A Frame Sync</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                                                                                                                                                                                   |

| SPT_ATDV    | Output    | <b>Channel A Transmit Data Valid</b> This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots.                                                                                                                                                                                      |

| SPT_BCLK    | I/O       | <b>Channel B Clock</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                                                                                                                         |

| SPT_BD0     | I/O       | <b>Channel B Data 0</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data.                                                                                                                                                                                              |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| Signal Name   | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain    | Description and Notes                                |

|---------------|------|----------------|-------------|---------------|----------------|---------------|----------------|--------------------|------------------------------------------------------|

| DMC0_A11      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Address 11.                               |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_A12      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Address 12.                               |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_A13      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Address 13.                               |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_BA0      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Bank Address Input 0.                     |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_BA1      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Bank Address Input 1.<br>Notes: No notes. |

| DMC0_BA2      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Bank Address Input 2.                     |

|               |      |                |             |               |                |               |                |                    | Notes: For LPDDR, leave unconnected                  |

| DMC0_CAS      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Column Address Strobe.                    |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

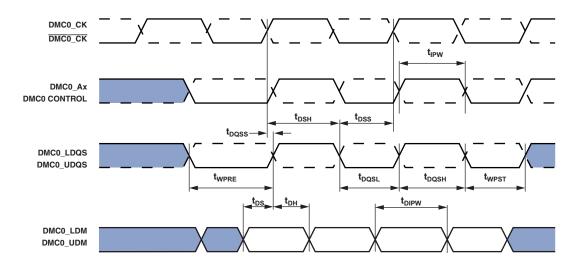

| DMC0_CK       | I/O  | C              | none        | none          | L              | none          | L              | VDD_DMC            | Desc: DMC0 Clock.                                    |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_CK       | I/O  | C              | none        | none          | L              | none          | L              | VDD_DMC            | Desc: DMC0 Clock (complement).                       |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_CKE      | I/O  | В              | none        | none          | L              | none          | L              | VDD_DMC            | Desc: DMC0 Clock enable.                             |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_CS0      | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Chip Select 0.                            |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ00     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 0.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ01     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 1.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ02     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 2.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ03     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 3.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ04     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 4.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ05     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 5.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ06     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 6.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ07     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 7.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ08     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 8.                                   |

|               |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ09     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 9.                                   |

| D1466 D T : - |      |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ10     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 10.                                  |

| D1460 D043    |      |                |             |               |                |               |                | \(\(\mathbb{C}\)\) | Notes: No notes.                                     |

| DMC0_DQ11     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 11.                                  |

|               | .,.  |                |             |               |                |               |                |                    | Notes: No notes.                                     |

| DMC0_DQ12     | I/O  | В              | none        | none          | none           | none          | none           | VDD_DMC            | Desc: DMC0 Data 12.                                  |

|               |      |                |             |               | 1              |               | 1              |                    | Notes: No notes.                                     |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| -           |      | Driver | Int  | Reset | Reset | Hiber | Hiber | Power   | Description                                                                                               |

|-------------|------|--------|------|-------|-------|-------|-------|---------|-----------------------------------------------------------------------------------------------------------|

| Signal Name | Туре | Type   | Term | Term  | Drive | Term  | Drive | Domain  | and Notes                                                                                                 |

| DMC0_DQ13   | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data 13.                                                                                       |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| DMC0_DQ14   | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data 14.                                                                                       |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| DMC0_DQ15   | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data 15.                                                                                       |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| DMC0_LDM    | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Mask for Lower Byte.<br>Notes: No notes.                                                  |

| DMC0_LDQS   | I/O  | С      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Strobe for Lower Byte.<br>Notes: For LPDDR, a 100k ohm pull-down<br>resistor is required. |

| DMC0_LDQS   | I/O  | С      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Strobe for Lower Byte (complement).                                                       |

|             |      |        |      |       |       |       |       |         | Notes: For single ended DDR2, connect to VREF_DMC. For LPDDR, leave unconnected.                          |

| DMC0_ODT    | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 On-die termination. Notes: For LPDDR, leave unconnected.                                       |

| DMC0_RAS    | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Row Address Strobe.                                                                            |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| DMC0_UDM    | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Mask for Upper Byte.<br>Notes: No notes.                                                  |

| DMC0_UDQS   | I/O  | С      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Strobe for Upper Byte.<br>Notes: For LPDDR, a 100k ohm pull-down<br>resistor is required. |

| DMC0_UDQS   | I/O  | С      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Data Strobe for Upper Byte (complement).                                                       |

|             |      |        |      |       |       |       |       |         | Notes: For single ended DDR2, connect to VREF_DMC. For LPDDR, leave unconnected.                          |

| DMC0_WE     | I/O  | В      | none | none  | none  | none  | none  | VDD_DMC | Desc: DMC0 Write Enable.                                                                                  |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| GND         | g    | na     | none | none  | none  | none  | none  | na      | Desc: Ground.                                                                                             |

|             |      |        |      |       |       |       |       |         | Notes: No notes.                                                                                          |

| JTG_EMU     | I/O  | Α      | none | none  | none  | none  | none  | VDD_EXT | Desc: Emulation Output.                                                                                   |

| ITC TCV     | 1/0  | 20     | nd   | nono  | nono  | nono  | nono  | VDD EVT | Notes: No notes. Desc: JTG Clock.                                                                         |

| JTG_TCK     | I/O  | na     | pd   | none  | none  | none  | none  | VDD_EXT | Notes: Functional during reset.                                                                           |

| JTG_TDI     | I/O  | na     | pu   | none  | none  | none  | none  | VDD_EXT | Desc: JTG Serial Data Input.                                                                              |

| 710_101     | 1,0  | l'id   | pu   | Horic | Horic | Horic | Horic | VDD_EXT | Notes: Functional during reset.                                                                           |

| JTG_TDO     | I/O  | Α      | none | none  | none  | none  | none  | VDD_EXT | Desc: JTG Serial Data Output.                                                                             |

| _           |      |        |      |       |       |       |       |         | Notes: Functional during reset, three-<br>state when JTG_TRST is asserted.                                |

| JTG_TMS     | I/O  | na     | pu   | none  | none  | none  | none  | VDD_EXT | Desc: JTG Mode Select.                                                                                    |

|             |      |        |      |       |       |       |       |         | Notes: Functional during reset.                                                                           |

| JTG_TRST    | I/O  | na     | pd   | none  | none  | none  | none  | VDD_EXT | Desc: JTG Reset.                                                                                          |

| -           |      |        |      |       |       |       |       |         | Notes: Functional during reset.                                                                           |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                                                                                                            |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| PD_12       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PD Position 12   SPI1 Slave Select<br>Output b   EPPI0 Data 20   SPORT1<br>Channel A Data 1   SPI1 Slave Select Input.<br>Notes: No notes. |

| PD_13       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PD Position 13   SPI1 Master Out,<br>Slave In   TIMERO Alternate Clock 5.<br>Notes: No notes.                                              |

| PD_14       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PD Position 14   SPI1 Master In, Slave Out   TIMERO Alternate Clock 6. Notes: No notes.                                                    |

| PD_15       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PD Position 15   SPI1 Slave Select<br>Output b   EPPI0 Data 21   SPORT1<br>Channel A Data 0.<br>Notes: No notes.                           |

| PE_00       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 0   SPI1 Data 3   EPPI0 Data 18   SPORT1 Channel B Data 1. Notes: No notes.                                                    |

| PE_01       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 1   SPI1 Data 2   EPPI0 Data 19   SPORT1 Channel B Data 0. Notes: No notes.                                                    |

| PE_02       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 2   SPI1 Ready   EPPI0 Data 22   SPORT1 Channel A Clock. Notes: No notes.                                                      |

| PE_03       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 3   EPPI0 Data 16   SPORT1 Channel B Frame Sync   ACM0 Frame Sync. Notes: No notes.                                            |

| PE_04       | I/O  | А              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 4   EPPI0 Data 17   SPORT1 Channel B Clock   ACM0 Clock. Notes: No notes.                                                      |

| PE_05       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 5   EPPI0 Data 23   SPORT1 Channel A Frame Sync. Notes: No notes.                                                              |

| PE_06       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 6   SPORT1 Channel A<br>Transmit Data Valid   EPPI0 Frame Sync 3<br>(FIELD)   LP3 Clock.<br>Notes: No notes.                   |

| PE_07       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 7   SPORT1 Channel B Transmit Data Valid   EPPI0 Frame Sync 2 (VSYNC)   LP3 Acknowledge. Notes: No notes.                      |

| PE_08       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: PE Position 8   PWM0 Sync   EPPI0 Frame Sync 1 (HSYNC)   LP2 Acknowledge   ACM0 External Trigger 0. Notes: No notes.                       |

| PE_09       | I/O  | A              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Notes: No notes.  Desc: PE Position 9   EPPI0 Clock   LP2 Clock   PWM0 Shutdown Input. Notes: No notes.                                          |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| Signal Name        | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                        |

|--------------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|--------------------------------------------------------------|

| SMC0_D06           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 6.                                           |

|                    |      |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SMC0_D07           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 7.                                           |

| SMC0 D00           | I/O  |                | wk          | wk            |                | wk            |                | VDD EVT         | Notes: No notes. Desc: SMC0 Data 8.                          |

| SMC0_D08           | 1/0  | Α              | WK          | WK            | none           | WK            | none           | VDD_EXT         | Notes: No notes.                                             |

| SMC0_D09           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 9.                                           |

|                    |      |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SMC0_D10           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 10.                                          |

| SMS0 D44           |      |                |             |               |                | ١.            |                | VDD 5VT         | Notes: No notes.                                             |

| SMC0_D11           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 11. Notes: No notes.                         |

| SMC0_D12           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 12.                                          |

|                    |      |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SMC0_D13           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 13.                                          |

|                    |      |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SMC0_D14           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 14.<br>Notes: No notes.                      |

| SMC0_D15           | I/O  | Α              | wk          | wk            | none           | wk            | none           | VDD_EXT         | Desc: SMC0 Data 15.                                          |

|                    | ,, - |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SYS_BMODE0         | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Boot Mode Control 0.                               |

|                    |      |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SYS_BMODE1         | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Boot Mode Control 1. Notes: No notes.              |

| SYS_BMODE2         | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Boot Mode Control 2.                               |

|                    | ,, - |                |             |               |                |               |                |                 | Notes: No notes.                                             |

| SYS_CLKIN          | a    | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Clock Input/Crystal Input.                         |

|                    |      |                |             |               |                |               |                |                 | Notes: Active during reset.                                  |

| SYS_CLKOUT         | I/O  | Α              | none        | none          | L              | none          | none           | VDD_EXT         | Desc: SYS Processor Clock Output. Notes: No notes.           |

| SYS_EXTWAKE        | I/O  | Α              | none        | none          | н              | none          | L              | VDD_EXT         | Desc: SYS External Wake Control.                             |

|                    |      |                |             |               |                |               |                |                 | Notes: Drives low during hibernate and high all other times. |

| SYS_FAULT          | I/O  | Α              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Fault.                                             |

|                    |      |                |             |               |                |               |                |                 | Notes: Open source, requires an external pull-down resistor. |

| SYS_FAULT          | I/O  | Α              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Complementary Fault.                               |

|                    |      |                |             |               |                |               |                |                 | Notes: Open drain, requires an external pull-up resistor.    |

| SYS_HWRST          | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Processor Hardware Reset Control.                  |

|                    |      |                |             |               |                |               |                |                 | Notes: Active during reset.                                  |

| SYS_NMI_<br>RESOUT | I/O  | Α              | none        | none          | L              | none          | none           | VDD_EXT         | Desc: SYS Reset Output   SYS Non-<br>maskable Interrupt.     |

|                    |      |                |             |               |                |               |                |                 | Notes: Requires an external pull-up resistor.                |

Table 15. ADSP-BF60x Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Hiber<br>Term | Hiber<br>Drive | Power<br>Domain | Description and Notes                                                                                                                                                                                         |

|-------------|------|----------------|-------------|---------------|----------------|---------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_PWRGD   | I/O  | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Power Good Indicator. Notes: If hibernate is not used or the internal Power Good Counter is used, connect to VDD_EXT.                                                                               |

| SYS_TDA     | a    | na             | none        | none          | none           | none          | none           | VDD_TD          | Desc: SYS Thermal Diode Anode. Notes: Active during reset and hibernate. If the thermal diode is not used, connect to ground.                                                                                 |

| SYS_TDK     | a    | na             | none        | none          | none           | none          | none           | VDD_TD          | Desc: SYS Thermal Diode Cathode. Notes: Active during reset and hibernate. If the thermal diode is not used, connect to ground.                                                                               |

| SYS_XTAL    | a    | na             | none        | none          | none           | none          | none           | VDD_EXT         | Desc: SYS Crystal Output.  Notes: Leave unconnected if an oscillator is used to provide SYS_CLKIN. Active during reset. State during hibernate is controlled by DPM_HIB_DIS.                                  |

| TWI0_SCL    | I/O  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Clock.  Notes: Open drain, requires external pull- up resistor. Consult Version 2.1 of the I2C specification for the proper resistor value. If TWI is not used, connect to ground.          |

| TWI0_SDA    | I/O  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI0 Serial Data.  Notes: Open drain, requires external pull- up resistor. Consult Version 2.1 of the I2C specification for the proper resistor value. If TWI is not used, connect to ground.           |

| TWI1_SCL    | I/O  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI1 Serial Clock.  Notes: Open drain, requires external pull- up resistor. Consult Version 2.1 of the I2C specification for the proper resistor value. If TWI is not used, connect to ground.          |

| TWI1_SDA    | I/O  | D              | none        | none          | none           | none          | none           | VDD_EXT         | Desc: TWI1 Serial Data.  Notes: Open drain, requires external pullup resistor. See the I2C-Bus Specification, Version 2.1, January 2000 for the proper resistor value. If TWI is not used, connect to ground. |

| USB0_CLKIN  | a    | na             | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Clock/Crystal Input. Notes: If USB is not used, connect to ground. Active during reset.                                                                                                            |

| USB0_DM     | I/O  | F              | none        | none          | none           | none          | none           | VDD_USB         | Desc: USB0 Data –.  Notes: Pull low if not using USB. For complete documentation of hibernate behavior when USB is used, see the USB chapter in the processor hardware reference.                             |

### **SPECIFICATIONS**

For information about product specifications please contact your ADI representative.

#### **OPERATING CONDITIONS**

| Parameter                                           |                              | Conditions                          | Min                         | Nominal | Max                          | Unit |

|-----------------------------------------------------|------------------------------|-------------------------------------|-----------------------------|---------|------------------------------|------|

| V <sub>DD_INT</sub>                                 | Internal Supply Voltage      | CCLK ≤ 500 MHz                      | 1.19                        | 1.25    | 1.32                         | ٧    |

| $V_{DD\_EXT}^{1}$                                   | External Supply Voltage      | 1.8 V I/O                           | 1.7                         | 1.8     | 1.9                          | ٧    |

| $V_{DD\_EXT}^{1}$                                   | External Supply Voltage      | 3.3 V I/O                           | 3.13                        | 3.3     | 3.47                         | ٧    |

| $V_{DD\_DMC}$                                       | DDR2/LPDDR Supply Voltage    |                                     | 1.7                         | 1.8     | 1.9                          | V    |

| $V_{DD\_USB}^2$                                     | USB Supply Voltage           |                                     | 3.13                        | 3.3     | 3.47                         | ٧    |

| $V_{DD\_TD}$                                        | Thermal Diode Supply Voltage |                                     | 3.13                        | 3.3     | 3.47                         | ٧    |

| $V_{IH}^{3}$                                        | High Level Input Voltage     | $V_{DD\_EXT} = 3.47 \text{ V}$      | 2.1                         |         |                              | V    |

| $V_{IH}^3$                                          | High Level Input Voltage     | $V_{DD\_EXT} = 1.9 \text{ V}$       | $0.7 \times V_{DD\_EXT}$    |         |                              | V    |

| V <sub>IHTWI</sub> 4, 5                             | High Level Input Voltage     | $V_{DD\_EXT} = Maximum$             | $0.7 \times V_{VBUSTWI}$    |         | $V_{\text{VBUSTWI}}$         | ٧    |

| $V_{IH\_DDR2}^{00000000000000000000000000000000000$ |                              | $V_{DD\_DMC} = 1.9 V$               | V <sub>DDR_REF</sub> + 0.25 |         |                              | V    |

| $V_{IH\_LPDDR}^{8}$                                 |                              | $V_{DD\_DMC} = 1.9 V$               | $0.8 \times V_{DD\_DMC}$    |         |                              | ٧    |

| $V_{ID\_DDR2}^{00000000000000000000000000000000000$ | Differential Input Voltage   | V <sub>IX</sub> = 1.075 V           | 0.50                        |         |                              | V    |

| $V_{\text{ID\_DDR2}}^{9}$                           | Differential Input Voltage   | $V_{IX} = 0.725 \text{ V}$          | 0.55                        |         |                              | ٧    |

| $V_{IL}^{3}$                                        | Low Level Input Voltage      | $V_{DD\_EXT} = 3.13 \text{ V}$      |                             |         | 0.8                          | ٧    |

| $V_{IL}^{3}$                                        | Low Level Input Voltage      | $V_{DD\_EXT} = 1.7 \text{ V}$       |                             |         | $0.3 \times V_{DD\_EXT}$     | ٧    |

| V <sub>ILTWI</sub> 4, 5                             | Low Level Input Voltage      | $V_{DD\_EXT} = Minimum$             |                             |         | $0.3 \times V_{VBUSTWI}$     | V    |

| $V_{IL\_DDR2}^{00000000000000000000000000000000000$ |                              | $V_{DD\_DMC} = 1.7 \text{ V}$       |                             |         | $V_{\text{DDR\_REF}} - 0.25$ | ٧    |

| $V_{IL\_LPDDR}^{8}$                                 |                              | $V_{DD\_DMC} = 1.7 \text{ V}$       |                             |         | $0.2 \times V_{DD\_DMC}$     | V    |

| $T_J$                                               | Junction Temperature         | T <sub>AMBIENT</sub> = 0°C to +70°C | 0                           |         | +105                         | °C   |

| $T_{J}$                                             | Junction Temperature         | $T_{AMBIENT} = -40$ °C to +85°C     | -40                         |         | +105                         | °C   |

| $T_J$                                               | Junction Temperature         | $T_{AMBIENT} = -40$ °C to $+105$ °C | -40                         |         | +125                         | °C   |

<sup>&</sup>lt;sup>1</sup> Must remain powered (even if the associated function is not used).

Table 16. TWI\_VSEL Selections and  $V_{\text{DD\_EXT}}\!/V_{\text{BUSTWI}}$

|                     | V <sub>DD_EXT</sub> Nominal | V <sub>BUSTWI</sub> Min | V <sub>BUSTWI</sub> Nom | V <sub>BUSTWI</sub> Max | Unit |

|---------------------|-----------------------------|-------------------------|-------------------------|-------------------------|------|

| TWI000 <sup>1</sup> | 3.30                        | 3.13                    | 3.30                    | 3.47                    | V    |

| TWI001              | 1.80                        | 1.70                    | 1.80                    | 1.90                    | V    |

| TWI011              | 1.80                        | 3.13                    | 3.30                    | 3.47                    | V    |

| TWI100              | 3.30                        | 4.75                    | 5.00                    | 5.25                    | V    |

Designs must comply with the VDD\_EXT and VBUSTWI voltages specified for the default TWI\_DT setting for correct JTAG boundary scan operation during reset.

<sup>&</sup>lt;sup>2</sup> If not used, connect to 1.8 V or 3.3 V.

<sup>&</sup>lt;sup>3</sup> Parameter value applies to all input and bidirectional signals except TWI signals, DMC0 signals and USB0 signals.

<sup>&</sup>lt;sup>4</sup>Parameter applies to TWI signals.

<sup>&</sup>lt;sup>5</sup> TWI signals are pulled up to V<sub>BUSTWI</sub>. See Table 16.

<sup>&</sup>lt;sup>6</sup> Parameter applies to DMC0 signals in DDR2 mode.

$<sup>^7\,</sup>V_{DDR\_REF}$  is the voltage applied to pin  $V_{REF\_DMC}$  , nominally  $V_{DD\_DMC}/2$  .

<sup>&</sup>lt;sup>8</sup> Parameter applies to DMC0 signals in LPDDR mode.

<sup>&</sup>lt;sup>9</sup> Parameter applies to signals DMC0\_CK, \overline{DMC0\_CK}, \overline{DMC0\_LDQS}, \overline{DMC0\_LDQS}, \overline{DMC0\_UDQS}, \overline{DMC0\_UDQS} when used in DDR2 differential input mode.

#### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                     |                                                              | Test Conditions                                                                                                    | Min                        | Typical     | Max   | Unit  |

|---------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|-------|-------|

| V <sub>OH</sub> <sup>1</sup>                                  | High Level Output Voltage                                    | $V_{DD\_EXT} = 1.7 \text{ V, } I_{OH} = -0.5 \text{ mA}$                                                           | V <sub>DD_EXT</sub> - 0.40 |             |       | V     |