Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | <u>.</u>                                                                         |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-TQFP-64-19                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4100f64f128baxqma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2015-10 Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Summary of Features**

|                          |              |              | evice Type    |               |                |                |

|--------------------------|--------------|--------------|---------------|---------------|----------------|----------------|

| Derivative <sup>1)</sup> | ADC<br>Chan. | DAC<br>Chan. | CCU4<br>Slice | CCU8<br>Slice | POSIF<br>Intf. | HRPWM<br>Intf. |

| XMC4200-F64x256          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4200-Q48x256          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4100-F64x128          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4100-Q48x128          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-F64x64           | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-Q48x64           | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-F64x128          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-Q48x128          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4108-F64x64           | 10           | 2            | 2 x 4         | 1 x 4         | 1              | -              |

| XMC4108-Q48x64           | 9            | 2            | 2 x 4         | 1 x 4         | 1              | -              |

|                          |              |              |               |               |                |                |

#### Table 4 Features of XMC4[12]00 Device Types

1) x is a placeholder for the supported temperature range.

# 1.5 Definition of Feature Variants

The XMC4[12]00 types are offered with several memory sizes and number of available VADC channels. **Table 5** describes the location of the available Flash memory, **Table 6** describes the location of the available SRAMs, **Table 7** the available VADC channels.

| Total Flash Size | Cached Range                                       | Uncached Range                                     |

|------------------|----------------------------------------------------|----------------------------------------------------|

| 256 Kbytes       | 0800 0000 <sub>H</sub> –<br>0803 FFFF <sub>H</sub> | 0C00 0000 <sub>н</sub> –<br>0C03 FFFF <sub>н</sub> |

| 128 Kbytes       | 0800 0000 <sub>H</sub> –<br>0801 FFFF <sub>H</sub> | 0C00 0000 <sub>н</sub> –<br>0C01 FFFF <sub>H</sub> |

| 64 Kbytes        | 0800 0000 <sub>H</sub> –<br>0800 FFFF <sub>H</sub> | 0С00 0000 <sub>н</sub> –<br>0С00 FFFF <sub>н</sub> |

Table 5 Flash Memory Ranges

# **Summary of Features**

| Table 9         XMC4100 Identification Registers |                        |               |  |  |  |  |  |  |  |

|--------------------------------------------------|------------------------|---------------|--|--|--|--|--|--|--|

| Register Name                                    | Value                  | Marking       |  |  |  |  |  |  |  |

| SCU_IDCHIP                                       | 0004 2001 <sub>H</sub> | EES-AA, ES-AA |  |  |  |  |  |  |  |

| SCU_IDCHIP                                       | 0004 2002 <sub>H</sub> | ES-AB, AB     |  |  |  |  |  |  |  |

| SCU_IDCHIP                                       | 0004 1003 <sub>H</sub> | BA            |  |  |  |  |  |  |  |

| JTAG IDCODE                                      | 101D D083 <sub>H</sub> | EES-AA, ES-AA |  |  |  |  |  |  |  |

| JTAG IDCODE                                      | 201D D083 <sub>H</sub> | ES-AB, AB     |  |  |  |  |  |  |  |

| JTAG IDCODE                                      | 301D D083 <sub>H</sub> | BA            |  |  |  |  |  |  |  |

#### . . \_

# XMC4100 / XMC4200 XMC4000 Family

#### **General Device Information**

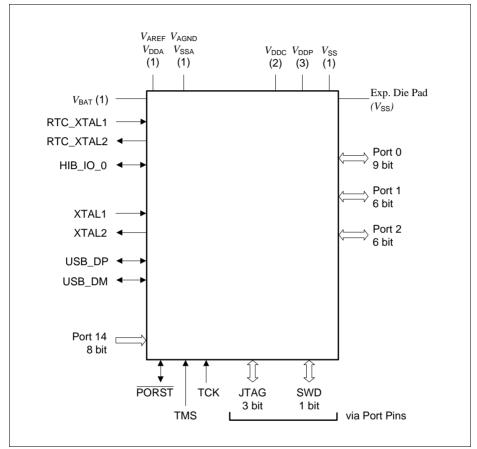

Figure 3 XMC4[12]00 Logic Symbol PG-VQFN-48

#### **General Device Information**

# 2.2 Pin Configuration and Definition

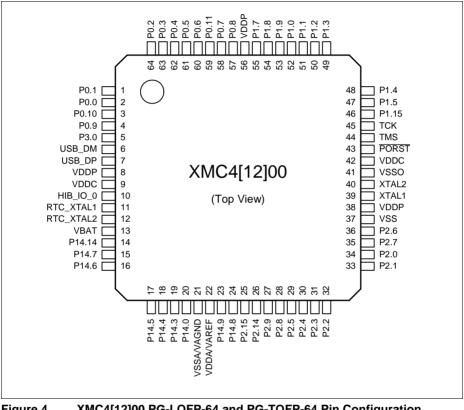

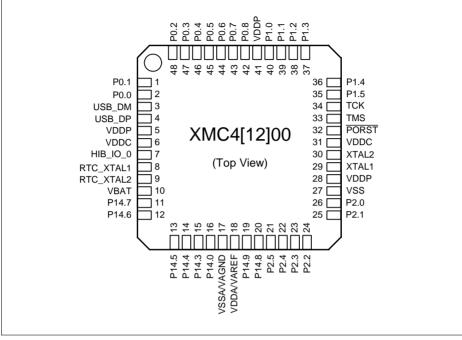

The following figures summarize all pins, showing their locations on the different packages.

#### Figure 4 XMC4[12]00 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

# XMC4100 / XMC4200 XMC4000 Family

#### **General Device Information**

Figure 5 XMC4[12]00 PG-VQFN-48 Pin Configuration (top view)

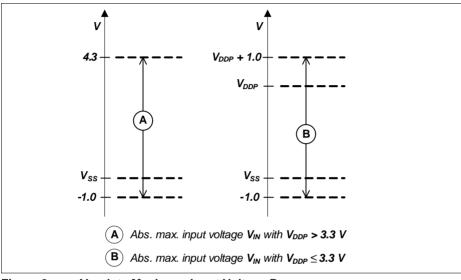

**Figure 8** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

Figure 8 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 15 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

| Parameter                                                                  | Symbol           |    | Values    |   |      | Unit | Note /                                                |

|----------------------------------------------------------------------------|------------------|----|-----------|---|------|------|-------------------------------------------------------|

|                                                                            |                  |    | Min. Typ. |   | Max. |      | Test Condition                                        |

| Input current on any port pin<br>during overload condition                 | I <sub>OV</sub>  | SR | -5        | - | 5    | mA   |                                                       |

| Absolute sum of all input circuit currents for one port                    | I <sub>OVG</sub> | SR | -         | - | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} < 0 \text{ mA}$ |

| group during overload condition <sup>1)</sup>                              |                  |    | -         | - | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} > 0 \text{ mA}$ |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> | SR | -         | - | 80   | mA   | ΣI <sub>OVG</sub>                                     |

## Table 15 Overload Parameters

1) The port groups are defined in **Table 18**.

**Figure 9** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

# Table 22 Standard Pads Class\_A1

| Parameter             | Symbol                  | Va                       | lues                   | Unit | Note /                                                     |

|-----------------------|-------------------------|--------------------------|------------------------|------|------------------------------------------------------------|

|                       |                         | Min. Max.                |                        |      | Test Condition                                             |

| Input leakage current | I <sub>OZA1</sub> CC    | -500                     | 500                    | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$       |

| Input high voltage    | $V_{\rm IHA1}~{\rm SR}$ | $0.6 \times V_{\rm DDP}$ | V <sub>DDP</sub> + 0.3 | V    | max. 3.6 V                                                 |

| Input low voltage     | $V_{\rm ILA1}{\rm SR}$  | -0.3                     | $0.36 	imes V_{ m DD}$ | - V  |                                                            |

| Output high voltage,  | $V_{OHA1}$              | V <sub>DDP</sub> - 0.4   | -                      | V    | $I_{OH} \ge$ -400 $\mu$ A                                  |

| $POD^{1)} = weak$     | CC                      | 2.4                      | -                      | V    | $I_{OH} \ge$ -500 $\mu$ A                                  |

| Output high voltage,  |                         | V <sub>DDP</sub> - 0.4   | -                      | V    | $I_{\rm OH} \ge$ -1.4 mA                                   |

| $POD^{1)} = medium$   |                         | 2.4                      | -                      | V    | $I_{OH} \ge$ -2 mA                                         |

| Output low voltage    | V <sub>OLA1</sub><br>CC | -                        | 0.4                    | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak      |

|                       |                         | -                        | 0.4                    | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium   |

| Fall time             | t <sub>FA1</sub> CC     | -                        | 150                    | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak       |

|                       |                         | -                        | 50                     | ns   | $C_{\rm L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium |

| Rise time             | t <sub>RA1</sub> CC     | -                        | 150                    | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak       |

|                       |                         | -                        | 50                     | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium     |

1) POD = Pin Out Driver

## Table 23 Standard Pads Class\_A1+

| Parameter             | Symbol                | Values                   |  | Values                    |    | Note /                                               |

|-----------------------|-----------------------|--------------------------|--|---------------------------|----|------------------------------------------------------|

|                       |                       | Min.                     |  | Max.                      |    | Test Condition                                       |

| Input leakage current | I <sub>OZA1+</sub> CC | -1                       |  | 1                         | μΑ | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |

| Input high voltage    | $V_{\rm IHA1+}\rm SR$ | $0.6 \times V_{\rm DDP}$ |  | $V_{\text{DDP}}$ + 0.3    | V  | max. 3.6 V                                           |

| Input low voltage     | $V_{\rm ILA1+}\rm SR$ | -0.3                     |  | $0.36 \times V_{\rm DDP}$ | V  |                                                      |

# XMC4100 / XMC4200 XMC4000 Family

### **Electrical Parameters**

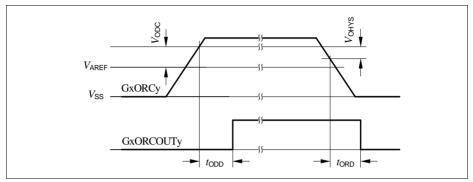

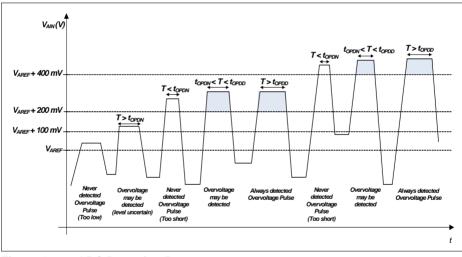

Figure 16 GxORCOUTy Trigger Generation

Figure 17 ORC Detection Ranges

| Parameter                                     | Symbol                    |                             | Value | S         | Unit | Note /         |

|-----------------------------------------------|---------------------------|-----------------------------|-------|-----------|------|----------------|

|                                               |                           | Min.                        | Тур.  | Max.      |      | Test Condition |

| CSG Output Jitter                             | D <sub>CSG</sub><br>CC    | -                           | -     | 1         | clk  |                |

| Bias startup time                             | t <sub>start</sub> CC     | -                           | -     | 98        | us   |                |

| Bias supply current                           | I <sub>DDbias</sub><br>CC | -                           | -     | 400       | μA   |                |

| CSGy startup time                             | t <sub>CSGS</sub><br>CC   | -                           | -     | 2         | μS   |                |

| Input operation current <sup>1)</sup>         | I <sub>DDCIN</sub><br>CC  | -10                         | -     | 33        | μA   | See Figure 19  |

| High Speed Mode                               |                           |                             |       | L         |      |                |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | V <sub>SS</sub>             | -     | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full scale         | t <sub>FShs</sub><br>CC   | -                           | -     | 80        | ns   | See Figure 20  |

| Input Selector propagation delay - Full scale | t <sub>Dhs</sub> CC       | -                           | -     | 100       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dhs</sub> CC       | 20                          | -     | -         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}$ SR          | -                           | -     | 30        | MHz  |                |

| Supply current                                | I <sub>DDhs</sub><br>CC   | -                           | -     | 940       | μA   |                |

| Low Speed Mode                                |                           |                             |       | L         |      |                |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | $0.1 	imes V_{ m DDP}^{2)}$ | -     | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full Scale         | t <sub>FSIs</sub> CC      | -                           | -     | 160       | ns   | See Figure 20  |

| Input Selector propagation delay - Full Scale | t <sub>DIs</sub> CC       | -                           | -     | 200       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dls</sub> CC       | 20                          | -     | -         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}~{\rm SR}$    | _                           | -     | 30        | MHz  |                |

| Supply current                                | I <sub>DDIs</sub><br>CC   | -                           | -     | 300       | μΑ   |                |

1) Typical input resistance  $R_{CIN} = 100$ kOhm.

2) The INL error increases for DAC output voltages below this limit.

# 3.2.7 Die Temperature Sensor

The Die Temperature Sensor (DTS) measures the junction temperature  $T_{1}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                         | Symbol              |    | Values    |    |      | Unit | Note /                                                                             |

|---------------------------------------------------|---------------------|----|-----------|----|------|------|------------------------------------------------------------------------------------|

|                                                   |                     |    | Min. Typ. |    | Max. |      | Test Condition                                                                     |

| Temperature sensor range                          | $T_{\rm SR}$        | SR | -40       | -  | 150  | °C   |                                                                                    |

| Linearity Error<br>(to the below defined formula) | $\Delta T_{\rm LE}$ | СС | -         | ±1 | -    | °C   | per $\Delta T_{\rm J} \leq 30  {\rm °C}$                                           |

| Offset Error                                      | $\Delta T_{\rm OE}$ | СС | -         | ±6 | -    | °C   | $\Delta T_{\rm OE} = T_{\rm J} - T_{\rm DTS}$ $V_{\rm DDP} \le 3.3 \ {\rm V}^{1)}$ |

| Measurement time                                  | t <sub>M</sub>      | СС | -         | -  | 100  | μS   |                                                                                    |

| Start-up time after reset inactive                | t <sub>TSST</sub>   | SR | _         | -  | 10   | μS   |                                                                                    |

Table 34 Die Temperature Sensor Parameters

1) At  $V_{\text{DDP max}}$  = 3.63 V the typical offset error increases by an additional  $\Delta T_{\text{OE}}$  = ±1 °C.

The following formula calculates the temperature measured by the DTS in [°C] from the RESULT bit field of the DTSSTAT register.

Temperature  $T_{\text{DTS}}$  = (RESULT - 605) / 2.05 [°C]

This formula and the values defined in **Table 34** apply with the following calibration values:

- DTSCON.BGTRIM = 8<sub>H</sub>

- DTSCON.REFTRIM = 4<sub>H</sub>

# 3.2.9 Oscillator Pins

- Note: It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimal parameters for the oscillator operation. Please refer to the limits specified by the crystal or ceramic resonator supplier.

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

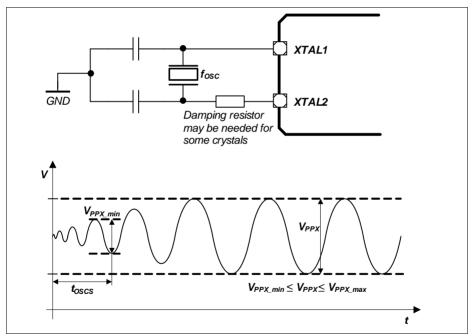

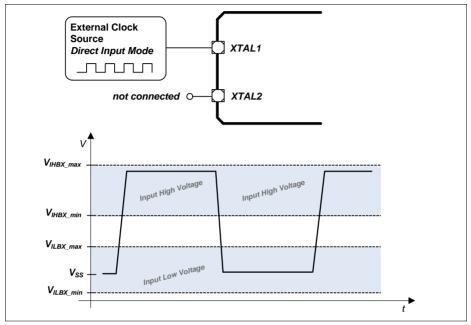

The oscillator pins can be operated with an external crystal (see Figure 21) or in direct input mode (see Figure 22).

Figure 21 Oscillator in Crystal Mode

Figure 22 Oscillator in Direct Input Mode

## Table 38 Power Supply Parameters

| Parameter                                                                   | Symbol                       |      | Value | S          | Unit | Note /                                               |

|-----------------------------------------------------------------------------|------------------------------|------|-------|------------|------|------------------------------------------------------|

|                                                                             |                              | Min. | Тур.  | Max.       | -    | Test Condition                                       |

| Sleep supply current <sup>3)</sup>                                          | I <sub>DDPS</sub> CC         | -    | 76    | -          | mA   | 80 / 80 / 80                                         |

| Peripherals enabled                                                         |                              | -    | 73    | -          |      | 80 / 40 / 40                                         |

| Frequency:<br>$f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                           |                              | _    | 70    | -          |      | 40 / 40 / 80                                         |

| JCPU' JPERIPH' JCCU III IVII 12                                             |                              | -    | 56    | -          |      | 24 / 24 / 24                                         |

|                                                                             |                              | -    | 47    | -          |      | 1/1/1                                                |

| $f_{CPU}/f_{PERIPH}/f_{CCU}$ in kHz                                         | -                            | _    | 46    | -          | -    | 100 / 100 / 100                                      |

| Sleep supply current <sup>4)</sup>                                          | I <sub>DDPS</sub> CC         | -    | 59    | -          | mA   | 80 / 80 / 80                                         |

| Peripherals disabled                                                        |                              | -    | 58    | -          |      | 80 / 40 / 40                                         |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                              |                              | -    | 57    | -          |      | 40 / 40 / 80                                         |

| JCPU, JPERIPH, JCCU                                                         |                              | _    | 51    | -          |      | 24 / 24 / 24                                         |

|                                                                             |                              | _    | 46    | -          | -    | 1/1/1                                                |

| $f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU}$ in kHz                             |                              | -    | 46    | -          |      | 100 / 100 / 100                                      |

| Deep Sleep supply                                                           | I <sub>DDPD</sub> CC         | -    | 6.9   | -          | mA   | 24 / 24 / 24                                         |

| current <sup>5)</sup>                                                       |                              | _    | 4.3   | -          |      | 4 / 4 / 4                                            |

| Flash in Sleep mode<br>Frequency:                                           |                              | -    | 3.8   | -          | -    | 1/1/1                                                |

| $\frac{f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU} \text{ in MHz}}{f_{\rm CCU}}$ |                              |      |       |            |      |                                                      |

| $f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU}$ in kHz                             |                              | -    | 4.5   | -          |      | 100 / 100 / 100<br><sub>6)</sub>                     |

| Hibernate supply current                                                    | I <sub>DDPH</sub> CC         | -    | 10.8  | -          | μA   | $V_{\rm BAT}$ = 3.3 V                                |

| RTC on <sup>7)</sup>                                                        |                              | -    | 8.0   | -          |      | $V_{\rm BAT}$ = 2.4 V                                |

|                                                                             |                              | _    | 6.8   | -          |      | $V_{\rm BAT}$ = 2.0 V                                |

| Hibernate supply current                                                    | I <sub>DDPH</sub> CC         | -    | 10.3  | -          | μA   | $V_{\rm BAT}$ = 3.3 V                                |

| RTC off <sup>8)</sup>                                                       |                              | _    | 7.5   | -          |      | $V_{\rm BAT}$ = 2.4 V                                |

|                                                                             |                              | -    | 6.3   | -          |      | $V_{\rm BAT}$ = 2.0 V                                |

| Worst case active supply current <sup>9)</sup>                              | I <sub>DDPA</sub> CC         | -    | -     | 140<br>10) | mA   | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C |

| $V_{\rm DDA}$ power supply current                                          | I <sub>DDA</sub> CC          | -    | -     | _11)       | mA   |                                                      |

| $I_{\text{DDP}}$ current at PORST Low                                       | I <sub>DDP_PORST</sub><br>CC | _    | -     | 24         | mA   | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C |

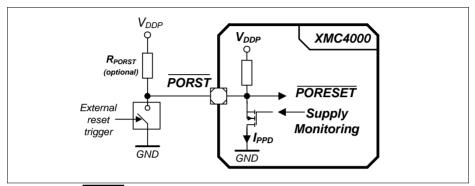

# 3.3.2 Power-Up and Supply Monitoring

PORST is always asserted when  $V_{\text{DDP}}$  and/or  $V_{\text{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# Figure 26 PORST Circuit

| Table 41 | Supply Monit | toring Parameters |

|----------|--------------|-------------------|

|----------|--------------|-------------------|

| Parameter                                                       | Symbol                   |                    | Value | s                  | Unit | Note /<br>Test Condition                                                                                         |

|-----------------------------------------------------------------|--------------------------|--------------------|-------|--------------------|------|------------------------------------------------------------------------------------------------------------------|

|                                                                 |                          | Min.               | Тур.  | Max.               |      |                                                                                                                  |

| Digital supply voltage reset threshold                          | V <sub>POR</sub> CC      | 2.79 <sup>1)</sup> | _     | 3.05 <sup>2)</sup> | V    | 3)                                                                                                               |

| Core supply voltage reset threshold                             | V <sub>PV</sub> CC       | -                  | -     | 1.17               | V    |                                                                                                                  |

| $V_{\text{DDP}}$ voltage to ensure defined pad states           | V <sub>DDPPA</sub><br>CC | -                  | 1.0   | -                  | V    |                                                                                                                  |

| PORST rise time                                                 | t <sub>PR</sub> SR       | _                  | _     | 2                  | μs   |                                                                                                                  |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC      | -                  | 2.5   | 3.5                | ms   | Time to the first<br>user code<br>instruction                                                                    |

| $V_{ m DDC}$ ramp up time                                       | t <sub>VCR</sub> CC      | _                  | 550   | _                  | μS   | Ramp up after<br>power-on or<br>after a reset<br>triggered by a<br>violation of<br>$V_{\rm POR}$ or $V_{\rm PV}$ |

1) Minimum threshold for reset assertion.

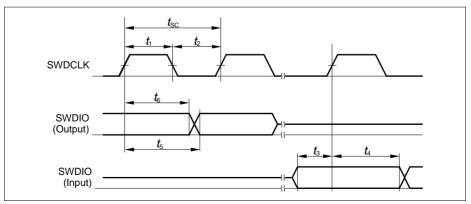

# 3.3.7 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

| Table 47 | SWD Interface Timing Parameters (Operating Conditions apply) |

|----------|--------------------------------------------------------------|

|----------|--------------------------------------------------------------|

| Parameter                                      | Symbol                |    | Values |      |        | Unit | Note /                 |

|------------------------------------------------|-----------------------|----|--------|------|--------|------|------------------------|

|                                                |                       |    | Min.   | Тур. | Max.   |      | Test Condition         |

| SWDCLK clock period                            | t <sub>SC</sub>       | SR | 25     | -    | -      | ns   | C <sub>L</sub> = 30 pF |

|                                                |                       |    | 40     | -    | -      | ns   | C <sub>L</sub> = 50 pF |

| SWDCLK high time                               | <i>t</i> <sub>1</sub> | SR | 10     | -    | 500000 | ns   |                        |

| SWDCLK low time                                | <i>t</i> <sub>2</sub> | SR | 10     | -    | 500000 | ns   |                        |

| SWDIO input setup to SWDCLK rising edge        | <i>t</i> <sub>3</sub> | SR | 6      | -    | _      | ns   |                        |

| SWDIO input hold<br>after SWDCLK rising edge   | <i>t</i> <sub>4</sub> | SR | 6      | -    | -      | ns   |                        |

| SWDIO output valid time                        | $t_5$                 | CC | -      | -    | 17     | ns   | C <sub>L</sub> = 50 pF |

| after SWDCLK rising edge                       |                       |    | -      | -    | 13     | ns   | C <sub>L</sub> = 30 pF |

| SWDIO output hold time from SWDCLK rising edge | <i>t</i> <sub>6</sub> | СС | 3      | -    | _      | ns   |                        |

### Package and Reliability

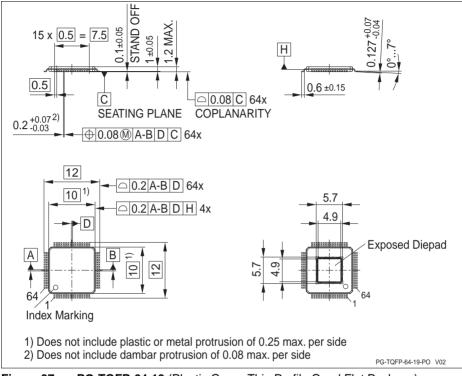

Figure 37 PG-TQFP-64-19 (Plastic Green Thin Profile Quad Flat Package)

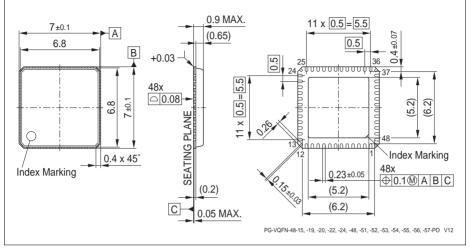

#### Table 57 Differences PG-VQFN-48-53 to PG-VQFN-48-71

| Change         | PG-VQFN-48-53            | PG-VQFN-48-71                     |

|----------------|--------------------------|-----------------------------------|

| Package corner | chamfered                | right-angled                      |

| Lead width     | 0.23 <sup>±0.05</sup> mm | 0.25 <sup>(+0.05, -0.07)</sup> mm |

| Lead height    | 0.4 <sup>±0.07</sup> mm  | 0.4 <sup>±0.05</sup> mm           |

# XMC4100 / XMC4200 XMC4000 Family

# Package and Reliability

Figure 38 PG-VQFN-48-53 (Plastic Green Very Thin Profile Flat Non Leaded Package)

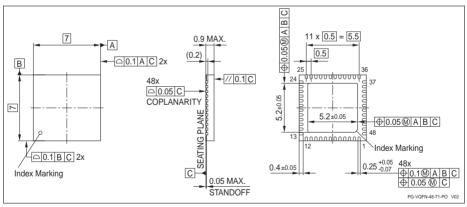

Figure 39 PG-VQFN-48-71 (Plastic Green Very Thin Profile Flat Non Leaded Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

www.infineon.com

Published by Infineon Technologies AG