Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 9x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | PG-VQFN-48-53                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4100q48k128baxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Summary of Features**

| Table 9 XMC4100 Identification Registers |                        |               |  |  |  |  |  |  |  |

|------------------------------------------|------------------------|---------------|--|--|--|--|--|--|--|

| Register Name                            | Value                  | Marking       |  |  |  |  |  |  |  |

| SCU_IDCHIP                               | 0004 2001 <sub>H</sub> | EES-AA, ES-AA |  |  |  |  |  |  |  |

| SCU_IDCHIP                               | 0004 2002 <sub>H</sub> | ES-AB, AB     |  |  |  |  |  |  |  |

| SCU_IDCHIP                               | 0004 1003 <sub>H</sub> | BA            |  |  |  |  |  |  |  |

| JTAG IDCODE                              | 101D D083 <sub>H</sub> | EES-AA, ES-AA |  |  |  |  |  |  |  |

| JTAG IDCODE                              | 201D D083 <sub>H</sub> | ES-AB, AB     |  |  |  |  |  |  |  |

| JTAG IDCODE                              | 301D D083 <sub>H</sub> | BA            |  |  |  |  |  |  |  |

#### . . \_

### **General Device Information**

# 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

### Table 10 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad<br>Type | Notes |

|----------|-----------|-----------|-----------------|-------|

| Name     | Ν         | Ax        | <br>A1+         |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

| Function | LQFP-64<br>TQFP-64 | VQFN-48 | Pad Type | Notes                                                                                                                |  |  |

|----------|--------------------|---------|----------|----------------------------------------------------------------------------------------------------------------------|--|--|

| P0.0     | 2                  | 2       | A1+      |                                                                                                                      |  |  |

| P0.1     | 1                  | 1       | A1+      |                                                                                                                      |  |  |

| P0.2     | 64                 | 48      | A1+      |                                                                                                                      |  |  |

| P0.3     | 63                 | 47      | A1+      |                                                                                                                      |  |  |

| P0.4     | 62                 | 46      | A1+      |                                                                                                                      |  |  |

| P0.5     | 61                 | 45      | A1+      |                                                                                                                      |  |  |

| P0.6     | 60                 | 44      | A1+      |                                                                                                                      |  |  |

| P0.7     | 58                 | 43      | A1+      | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDI function.                                          |  |  |

| P0.8     | 57                 | 42      | A1+      | After a system reset, via<br><u>HWSEL</u> this pin selects the<br>DB.TRST function, with a<br>weak pull-down active. |  |  |

| P0.9     | 4                  | -       | A1+      |                                                                                                                      |  |  |

| P0.10    | 3                  | -       | A1+      |                                                                                                                      |  |  |

## Table 11 Package Pin Mapping

# XMC4100 / XMC4200 XMC4000 Family

### **General Device Information**

| Table 11   | Package Pin Mapping (cont'd) |    |                     |                                                                                                                                                                                              |  |  |  |  |  |

|------------|------------------------------|----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Function   | LQFP-64 VQFN-48<br>TQFP-64   |    | Pad Type            | Notes                                                                                                                                                                                        |  |  |  |  |  |

| P14.9      | 23                           | 19 | AN/DAC/DIG_IN       |                                                                                                                                                                                              |  |  |  |  |  |

| P14.14     | 14                           | -  | AN/DIG_IN           |                                                                                                                                                                                              |  |  |  |  |  |

| USB_DP     | 7                            | 4  | special             |                                                                                                                                                                                              |  |  |  |  |  |

| USB_DM     | 6                            | 3  | special             |                                                                                                                                                                                              |  |  |  |  |  |

| HIB_IO_0   | 10                           | 7  | A1 special          | At the first power-up and with<br>every reset of the hibernate<br>domain this pin is configured<br>as open-drain output and<br>drives "0".<br>As output the medium driver<br>mode is active. |  |  |  |  |  |

| тск        | 45                           | 34 | A1                  | Weak pull-down active.                                                                                                                                                                       |  |  |  |  |  |

| TMS        | 44                           | 33 | A1+                 | Weak pull-up active.<br>As output the strong-soft<br>driver mode is active.                                                                                                                  |  |  |  |  |  |

| PORST      | 43                           | 32 | special             | Strong pull-down controlled<br>by EVR.<br>Weak pull-up active while<br>strong pull-down is not active.                                                                                       |  |  |  |  |  |

| XTAL1      | 39                           | 29 | clock_IN            |                                                                                                                                                                                              |  |  |  |  |  |

| XTAL2      | 40                           | 30 | clock_O             |                                                                                                                                                                                              |  |  |  |  |  |

| RTC_XTAL1  | 11                           | 8  | clock_IN            |                                                                                                                                                                                              |  |  |  |  |  |

| RTC_XTAL2  | 12                           | 9  | clock_O             |                                                                                                                                                                                              |  |  |  |  |  |

| VBAT       | 13                           | 10 | Power               | When VDDP is supplied<br>VBAT has to be supplied as<br>well.                                                                                                                                 |  |  |  |  |  |

| VDDA/VAREF | 22                           | 18 | AN_Power/AN_<br>Ref | Shared analog supply and reference voltage pin.                                                                                                                                              |  |  |  |  |  |

| VSSA/VAGND | 21                           | 17 | AN_Power/AN_<br>Ref | Shared analog supply and reference ground pin.                                                                                                                                               |  |  |  |  |  |

| VDDC       | 9                            | 6  | Power               |                                                                                                                                                                                              |  |  |  |  |  |

| VDDC       | 42                           | 31 | Power               |                                                                                                                                                                                              |  |  |  |  |  |

| VDDP       | 8                            | 5  | Power               |                                                                                                                                                                                              |  |  |  |  |  |

| VDDP       | 38                           | 28 | Power               |                                                                                                                                                                                              |  |  |  |  |  |

| VDDP       | 56                           | 41 | Power               |                                                                                                                                                                                              |  |  |  |  |  |

| VSS        | 37                           | 27 | Power               |                                                                                                                                                                                              |  |  |  |  |  |

# Table 11 Package Pin Mapping (cont'd)

The XMC4[12]00 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

There are no dedicated connections for the analog reference  $V_{\text{AREF}}$  and  $V_{\text{AGND}}$ . Instead, they share the same pins as the analog supply pins  $V_{\text{DDA}}$  and  $V_{\text{SSA}}$ . Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\text{DDP}}$  is supplied,  $V_{\text{BAT}}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\text{BAT}}$ , the  $V_{\text{BAT}}$  pin can also be connected directly to  $V_{\text{DDP}}$ .

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symbol               |    | Values |      |                                       | Unit | Note /                |

|------------------------------------------------------------------------------------------------------------------------|----------------------|----|--------|------|---------------------------------------|------|-----------------------|

|                                                                                                                        |                      |    | Min.   | Тур. | Max.                                  |      | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$         | SR | -65    | -    | 150                                   | °C   | -                     |

| Junction temperature                                                                                                   | TJ                   | SR | -40    | _    | 150                                   | °C   | -                     |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$            | SR | -      | -    | 4.3                                   | V    | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>      | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\text{AGND}}$                                                      | $V_{AIN}$ $V_{AREF}$ | SR | -1.0   | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Input current on any pin<br>during overload condition                                                                  | I <sub>IN</sub>      | SR | -10    | -    | +10                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$  | SR | -25    | -    | +25                                   | mA   |                       |

| Absolute maximum sum of all input circuit currents during overload condition                                           | $\Sigma I_{\rm IN}$  | SR | -100   | _    | +100                                  | mA   |                       |

### Table 14 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 18**.

# 3.1.4 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and its basic characteristics. More details (mainly DC parameters) are defined in the Section 3.2.1.

| Table 19 Pad Driver and Pad | Classes Overview |

|-----------------------------|------------------|

|-----------------------------|------------------|

| Class | Power<br>Supply | Туре             | Sub-Class                 | Speed<br>Grade | Load   | Termination                    |

|-------|-----------------|------------------|---------------------------|----------------|--------|--------------------------------|

| Α     | 3.3 V           | LVTTL<br>I/O,    | <b>A1</b><br>(e.g. GPIO)  | 6 MHz          | 100 pF | No                             |

| _     |                 | LVTTL<br>outputs | A1+<br>(e.g. serial I/Os) | 25 MHz         | 50 pF  | Series termination recommended |

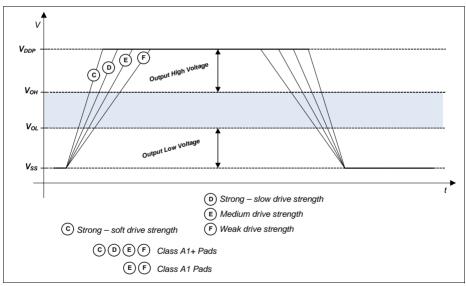

Figure 10 Output Slopes with different Pad Driver Modes

Figure 10 is a qualitative display of the resulting output slope performance with different output driver modes. The detailed input and output characteristics are listed in Section 3.2.1.

35

# XMC4100 / XMC4200 XMC4000 Family

### **Electrical Parameters**

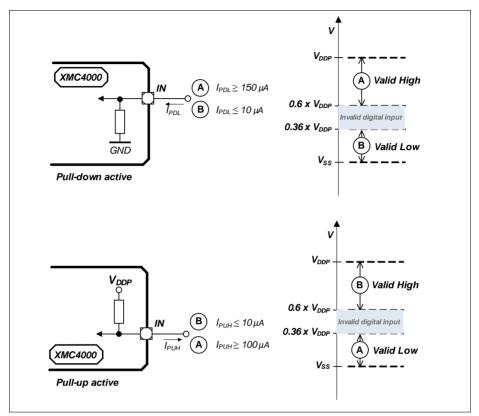

### Figure 11 Pull Device Input Characteristics

Figure 11 visualizes the input characteristics with an active internal pull device:

- in the cases "A" the internal pull device is overridden by a strong external driver;

- in the cases "B" the internal pull device defines the input logical state against a weak external load.

# Table 22 Standard Pads Class\_A1

| Parameter                | Symbol                  | Va                       | lues                   | Unit | Note /                                                   |  |

|--------------------------|-------------------------|--------------------------|------------------------|------|----------------------------------------------------------|--|

|                          |                         | Min.                     | Max.                   |      | Test Condition                                           |  |

| Input leakage current    | I <sub>OZA1</sub> CC    | -500                     | 500                    | nA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$     |  |

| Input high voltage       | $V_{\rm IHA1}~{\rm SR}$ | $0.6 \times V_{\rm DDP}$ | V <sub>DDP</sub> + 0.3 | V    | max. 3.6 V                                               |  |

| Input low voltage        | $V_{\rm ILA1}{\rm SR}$  | -0.3                     | $0.36 	imes V_{ m DD}$ | - V  |                                                          |  |

| Output high voltage,     | $V_{OHA1}$              | V <sub>DDP</sub> - 0.4   | -                      | V    | $I_{OH} \ge$ -400 $\mu$ A                                |  |

| POD <sup>1)</sup> = weak | CC                      | 2.4                      | -                      | V    | $I_{OH} \ge$ -500 $\mu$ A                                |  |

| Output high voltage,     |                         | V <sub>DDP</sub> - 0.4   | -                      | V    | $I_{\rm OH} \ge$ -1.4 mA                                 |  |

| $POD^{1)} = medium$      |                         | 2.4                      | -                      | V    | $I_{OH} \ge$ -2 mA                                       |  |

| Output low voltage       | V <sub>OLA1</sub><br>CC | -                        | 0.4                    | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak    |  |

|                          |                         | -                        | 0.4                    | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium |  |

| Fall time                | t <sub>FA1</sub> CC     | -                        | 150                    | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |  |

|                          |                         | -                        | 50                     | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium       |  |

| Rise time                | t <sub>RA1</sub> CC     | -                        | 150                    | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak     |  |

|                          |                         | -                        | 50                     | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium   |  |

1) POD = Pin Out Driver

# Table 23 Standard Pads Class\_A1+

| Parameter             | Symbol Values         |                          |  | Unit                      | Note / |                                                      |

|-----------------------|-----------------------|--------------------------|--|---------------------------|--------|------------------------------------------------------|

|                       |                       | Min.                     |  | Max.                      |        | Test Condition                                       |

| Input leakage current | I <sub>OZA1+</sub> CC | -1                       |  | 1                         | μΑ     | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{DDP}}$ |

| Input high voltage    | $V_{\rm IHA1+}\rm SR$ | $0.6 \times V_{\rm DDP}$ |  | $V_{\text{DDP}}$ + 0.3    | V      | max. 3.6 V                                           |

| Input low voltage     | $V_{\rm ILA1+}\rm SR$ | -0.3                     |  | $0.36 \times V_{\rm DDP}$ | V      |                                                      |

| Parameter                                          | Symbol                   | Va                     | lues                   | Unit | Note /                                                  |

|----------------------------------------------------|--------------------------|------------------------|------------------------|------|---------------------------------------------------------|

|                                                    |                          | Min.                   | Max.                   |      | Test Condition                                          |

| Input leakage current                              | I <sub>OZHIB</sub><br>CC | -500                   | 500                    | nA   | $0 \ V \le V_{IN} \le V_{BAT}$                          |

| Input high voltage                                 | V <sub>IHHIB</sub><br>SR | $0.6 	imes V_{BAT}$    | V <sub>BAT</sub> + 0.3 | V    | max. 3.6 V                                              |

| Input low voltage                                  | V <sub>ILHIB</sub><br>SR | -0.3                   | $0.36 	imes V_{BAT}$   | V    |                                                         |

| Input Hysteresis for                               | HYSHIB                   | $0.1 	imes V_{BAT}$    | -                      | V    | $V_{\rm BAT} \ge$ 3.13 V                                |

| HIB_IO pins <sup>1)</sup>                          | CC                       | $0.06 	imes V_{BAT}$   | -                      | V    | $V_{\rm BAT}$ < 3.13 V                                  |

| Output high voltage,<br>POD <sup>1)</sup> = medium | V <sub>OHHIB</sub><br>CC | V <sub>BAT</sub> - 0.4 | -                      | V    | I <sub>OH</sub> ≥ -1.4 mA                               |

| Output low voltage                                 | V <sub>OLHIB</sub><br>CC | -                      | 0.4                    | V    | $I_{\rm OL} \le 2  {\rm mA}$                            |

| Fall time                                          | t <sub>FHIB</sub> CC     | -                      | 50                     | ns   | $V_{\rm BAT} \ge 3.13 \text{ V}$<br>$C_{\rm L}$ = 50 pF |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF           |

| Rise time                                          | t <sub>RHIB</sub> CC     | -                      | 50                     | ns   | $V_{\rm BAT} \ge 3.13 \ { m V}$<br>$C_{\rm L}$ = 50 pF  |

|                                                    |                          | -                      | 100                    | ns   | $V_{\rm BAT}$ < 3.13 V<br>$C_{\rm L}$ = 50 pF           |

## Table 24 HIB\_IO Class\_A1 special Pads

1) Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

| Parameter                                                                       | Symbol                     |      | Value | S     | Unit | Note /                                                                                          |

|---------------------------------------------------------------------------------|----------------------------|------|-------|-------|------|-------------------------------------------------------------------------------------------------|

|                                                                                 |                            | Min. | Тур.  | Max.  |      | Test Condition                                                                                  |

| Total capacitance of the alternate reference inputs <sup>5)</sup>               | C <sub>AREFTOT</sub><br>CC | -    | 20    | 40    | pF   |                                                                                                 |

| Total Unadjusted Error                                                          | TUE CC                     | -6   | -     | 6     | LSB  | 12-bit resolution;                                                                              |

| Differential Non-Linearity<br>Error <sup>8)</sup>                               | EA <sub>DNL</sub><br>CC    | -4.5 | -     | 4.5   | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                       |

| Gain Error <sup>8)</sup>                                                        | EA <sub>GAIN</sub><br>CC   | -6   | -     | 6     | LSB  |                                                                                                 |

| Integral Non-Linearity <sup>8)</sup>                                            | EA <sub>INL</sub> CC       | -4.5 | -     | 4.5   | LSB  |                                                                                                 |

| Offset Error <sup>8)</sup>                                                      | EA <sub>OFF</sub><br>CC    | -6   | -     | 6     | LSB  |                                                                                                 |

| Worst case ADC $V_{\text{DDA}}$<br>power supply current per<br>active converter | I <sub>DDAA</sub><br>CC    | -    | 1.5   | 2     | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 ^{\circ}\text{C}$ |

| Charge consumption on alternate reference per conversion <sup>5)</sup>          | $Q_{\rm CONV}$             | -    | 30    | -     | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9}$                                                              |

| ON resistance of the analog input path                                          | R <sub>AIN</sub> CC        | -    | 600   | 1 200 | Ohm  |                                                                                                 |

| ON resistance for the ADC test (pull down for AIN7)                             | R <sub>AIN7T</sub><br>CC   | 180  | 550   | 900   | Ohm  |                                                                                                 |

### Table 25 ADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 14).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

43

8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

# 3.2.3 Digital to Analog Converters (DACx)

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                | Symb                      | Symbol            |      | Values | 5              | Unit          | Note /                                                                            |

|------------------------------------------|---------------------------|-------------------|------|--------|----------------|---------------|-----------------------------------------------------------------------------------|

|                                          | Min. Typ.                 |                   | Max. | _      | Test Condition |               |                                                                                   |

| RMS supply current                       | I <sub>DD</sub>           | CC                | _    | 2.5    | 4              | mA            | per active DAC<br>channel,<br>without load<br>currents of DAC<br>outputs          |

| Resolution                               | RES                       | CC                | -    | 12     | -              | Bit           |                                                                                   |

| Update rate                              | furate.                   | _ <sub>A</sub> CC | _    |        | 2              | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 1LSB accuracy     |

| Update rate                              | furate                    | _F CC             | _    |        | 5              | Msam<br>ple/s | data rate, where<br>DAC can follow<br>64 LSB code jumps<br>to ± 4 LSB accuracy    |

| Settling time                            | t <sub>SETTLE</sub>       | E CC              | -    | 1      | 2              | μs            | at full scale jump,<br>output voltage<br>reaches target<br>value ± 20 LSB         |

| Slew rate                                | SR                        | CC                | 2    | 5      | -              | V/µs          |                                                                                   |

| Minimum output<br>voltage                | V <sub>OUT_</sub> r<br>CC | MIN               | _    | 0.3    | -              | V             | code value<br>unsigned: 000 <sub>H</sub> ;<br>signed: 800 <sub>H</sub>            |

| Maximum output<br>voltage                | V <sub>OUT_</sub> r<br>CC | МАХ               | -    | 2.5    | -              | V             | code value<br>unsigned: FFF <sub>H</sub> ;<br>signed: 7FF <sub>H</sub>            |

| Integral non-<br>linearity <sup>1)</sup> | INL                       | CC                | -5.5 | ±2.5   | 5.5            | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |

| Differential non-<br>linearity           | DNL                       | CC                | -2   | ±1     | 2              | LSB           | $\begin{array}{l} R_L \geq 5 \text{ kOhm,} \\ C_L \leq 50 \text{ pF} \end{array}$ |

Table 27

DAC Parameters (Operating Conditions apply)

# 3.2.4 Out-of-Range Comparator (ORC)

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above the analog reference<sup>1</sup> ( $V_{AREF}$ ) on selected input pins (GxORCy) and generates a service request trigger (GxORCOUTy).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The parameters in Table 28 apply for the maximum reference voltage  $V_{\text{AREF}} = V_{\text{DDA}} + 50 \text{ mV}.$

| Parameter                            | Symb              | ol |      | Values | 5             | Unit | Note /                                                                   |

|--------------------------------------|-------------------|----|------|--------|---------------|------|--------------------------------------------------------------------------|

|                                      |                   |    | Min. | Тур.   | Max.          |      | Test Condition                                                           |

| DC Switching Level                   | V <sub>ODC</sub>  | СС | 100  | 125    | 200           | mV   | Ax-marking devices $V_{\text{AIN}} \ge V_{\text{AREF}} + V_{\text{ODC}}$ |

| Hysteresis                           | $V_{\rm OHYS}$    | CC | 50   | -      | $V_{\rm ODC}$ | mV   |                                                                          |

| Detection Delay of a persistent      | t <sub>ODD</sub>  | СС | 55   | -      | 450           | ns   | Ax-marking devices $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

| Overvoltage                          |                   |    | 45   | -      | 105           | ns   | $V_{\rm AIN} \ge V_{\rm AREF}$ + 400 mV                                  |

| Always detected<br>Overvoltage Pulse | t <sub>OPDD</sub> | СС | 440  | -      | -             | ns   | Ax-marking devices $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

|                                      |                   |    | 90   | -      | -             | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV                            |

| Never detected<br>Overvoltage Pulse  | t <sub>OPDN</sub> | СС | _    | -      | 49            | ns   | Ax-marking devices $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 200 mV         |

|                                      |                   |    | -    | -      | 30            | ns   | $V_{\text{AIN}} \ge V_{\text{AREF}}$ + 400 mV                            |

| Release Delay                        | t <sub>ORD</sub>  | СС | 65   | -      | 105           | ns   | $V_{\rm AIN} \leq V_{\rm AREF}$                                          |

| Enable Delay                         | t <sub>OED</sub>  | CC | _    | 100    | 200           | ns   |                                                                          |

# Table 28 ORC Parameters (Operating Conditions apply)

<sup>1)</sup> Always the standard VADC reference, alternate references do not apply to the ORC.

| Parameter                                     | Symbol                    |                             | Value | S         | Unit | Note /         |

|-----------------------------------------------|---------------------------|-----------------------------|-------|-----------|------|----------------|

|                                               |                           | Min.                        | Тур.  | Max.      |      | Test Condition |

| CSG Output Jitter                             | D <sub>CSG</sub><br>CC    | -                           | -     | 1         | clk  |                |

| Bias startup time                             | t <sub>start</sub> CC     | -                           | -     | 98        | us   |                |

| Bias supply current                           | I <sub>DDbias</sub><br>CC | -                           | -     | 400       | μA   |                |

| CSGy startup time                             | t <sub>CSGS</sub><br>CC   | -                           | -     | 2         | μS   |                |

| Input operation current <sup>1)</sup>         | I <sub>DDCIN</sub><br>CC  | -10                         | -     | 33        | μA   | See Figure 19  |

| High Speed Mode                               |                           |                             |       |           |      |                |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | V <sub>SS</sub>             | -     | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full scale         | t <sub>FShs</sub><br>CC   | -                           | -     | 80        | ns   | See Figure 20  |

| Input Selector propagation delay - Full scale | t <sub>Dhs</sub> CC       | -                           | -     | 100       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dhs</sub> CC       | 20                          | -     | -         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}~{\rm SR}$    | -                           | -     | 30        | MHz  |                |

| Supply current                                | I <sub>DDhs</sub><br>CC   | -                           | -     | 940       | μA   |                |

| Low Speed Mode                                |                           |                             |       | L         |      |                |

| DAC output voltage range                      | V <sub>DOUT</sub><br>CC   | $0.1 	imes V_{ m DDP}^{2)}$ | -     | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full Scale         | t <sub>FSIs</sub> CC      | -                           | -     | 160       | ns   | See Figure 20  |

| Input Selector propagation delay - Full Scale | t <sub>DIs</sub> CC       | -                           | -     | 200       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dls</sub> CC       | 20                          | -     | -         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}~{\rm SR}$    | -                           | _     | 30        | MHz  |                |

| Supply current                                | I <sub>DDIs</sub><br>CC   | -                           | -     | 300       | μA   |                |

1) Typical input resistance  $R_{CIN} = 100$ kOhm.

2) The INL error increases for DAC output voltages below this limit.

| Parameter | Symbol                  |                                   | Value | Unit              | Note / |                                       |

|-----------|-------------------------|-----------------------------------|-------|-------------------|--------|---------------------------------------|

|           |                         | Min.                              | Тур.  | Max.              |        | Test Con<br>dition                    |

| Frequency | $f_{eclk}$ SR           | -                                 | -     | $f_{\rm hrpwm}/4$ | MHz    |                                       |

| ON time   | t <sub>oneclk</sub> SR  | $2T_{\rm ccu}^{(1)2)}$            | -     | -                 | ns     |                                       |

| OFF time  | t <sub>offeclk</sub> SR | 2T <sub>ccu</sub> <sup>1)2)</sup> | -     | -                 | ns     | Only the<br>rising<br>edge is<br>used |

### Table 32 External clock operating conditions

1) 50% duty cycle is not obligatory

2) Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

# 3.2.6 Low Power Analog Comparator (LPAC)

The Low Power Analog Comparator (LPAC) triggers a wake-up event from Hibernate state or an interrupt trigger during normal operation. It does so by comparing  $V_{\rm BAT}$  or another external sensor voltage  $V_{\rm LPS}$  with a pre-programmed threshold voltage.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

|                                                       | -                              |           |        |      |      |                                            |

|-------------------------------------------------------|--------------------------------|-----------|--------|------|------|--------------------------------------------|

| Parameter                                             | Symbol                         |           | Values | ;    | Unit | Note /                                     |

|                                                       |                                | Min. Typ. |        | Max. |      | Test Condition                             |

| $V_{\rm BAT}$ supply voltage range for LPAC operation | $V_{\rm BAT}~{ m SR}$          | 2.1       | -      | 3.6  | V    |                                            |

| Sensor voltage range                                  | V <sub>LPCS</sub><br>CC        | 0         | -      | 1.2  | V    |                                            |

| Threshold step size                                   | $V_{\rm th}$ CC                | -         | 18.75  | _    | mV   |                                            |

| Threshold trigger accuracy                            | $\varDelta V_{\mathrm{th}}$ CC | -         | -      | ±10  | %    | for $V_{\rm th}$ > 0.4 V                   |

| Conversion time                                       | $t_{\rm LPCC}  {\rm CC}$       | -         | -      | 250  | μS   |                                            |

| Average current consumption over time                 | I <sub>LPCAC</sub><br>CC       | _         | -      | 15   | μA   | conversion<br>interval 10 ms <sup>1)</sup> |

| Current consumption during conversion                 | $I_{\rm LPCC}  {\rm CC}$       | _         | 150    | _    | μA   | 1)                                         |

|                                                       |                                |           |        |      |      |                                            |

Table 33Low Power Analog Comparator Parameters

1) Single channel conversion, measuring  $V_{\text{BAT}}$  = 3.3 V, 8 cycles settling time

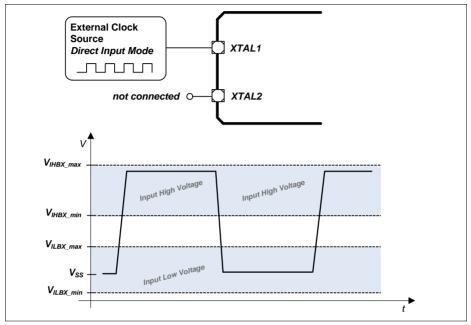

Figure 22 Oscillator in Direct Input Mode

# 3.3.2 Power-Up and Supply Monitoring

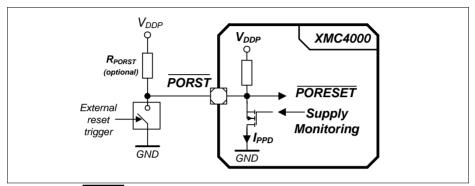

PORST is always asserted when  $V_{\text{DDP}}$  and/or  $V_{\text{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# Figure 26 PORST Circuit

| Table 41 | Supply Monit | toring Parameters |

|----------|--------------|-------------------|

|----------|--------------|-------------------|

| Parameter                                                       | Symbol                   |                    | Value | s                  | Unit | Note /                                                                                                           |

|-----------------------------------------------------------------|--------------------------|--------------------|-------|--------------------|------|------------------------------------------------------------------------------------------------------------------|

|                                                                 |                          | Min. Typ           |       | Max.               |      | Test Condition                                                                                                   |

| Digital supply voltage reset threshold                          | V <sub>POR</sub> CC      | 2.79 <sup>1)</sup> | _     | 3.05 <sup>2)</sup> | V    | 3)                                                                                                               |

| Core supply voltage reset threshold                             | V <sub>PV</sub> CC       | -                  | -     | 1.17               | V    |                                                                                                                  |

| $V_{\text{DDP}}$ voltage to ensure defined pad states           | V <sub>DDPPA</sub><br>CC | -                  | 1.0   | -                  | V    |                                                                                                                  |

| PORST rise time                                                 | t <sub>PR</sub> SR       | _                  | _     | 2                  | μs   |                                                                                                                  |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC      | -                  | 2.5   | 3.5                | ms   | Time to the first<br>user code<br>instruction                                                                    |

| $V_{\rm DDC}$ ramp up time                                      | t <sub>VCR</sub> CC      | -                  | 550   | _                  | μS   | Ramp up after<br>power-on or<br>after a reset<br>triggered by a<br>violation of<br>$V_{\rm POR}$ or $V_{\rm PV}$ |

1) Minimum threshold for reset assertion.

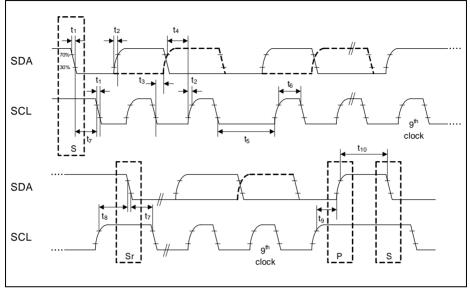

# Figure 32 USIC IIC Stand and Fast Mode Timing

# 3.3.8.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode. *Note: Operating Conditions apply.*

| Table 52 | USIC IIS Master | <b>Transmitter Timing</b> |

|----------|-----------------|---------------------------|

|----------|-----------------|---------------------------|

| Parameter       | Symbol            |                   | Values | 6                 | Unit | Note /         |

|-----------------|-------------------|-------------------|--------|-------------------|------|----------------|

|                 |                   | Min.              | Тур.   | Max.              |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3              | -      | -                 | ns   |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x            | -      | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x            | _      | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |        |                   |      |                |

| Hold time       | t <sub>4</sub> CC | 0                 | -      | -                 | ns   |                |

| Clock rise time | t <sub>5</sub> CC | -                 | -      | 0.15 x            | ns   |                |

|                 |                   |                   |        | t <sub>1min</sub> |      |                |

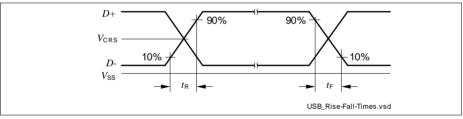

# 3.3.9 USB Interface Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter               | Symbol                |    | Values |      |        | Unit | Note /                 |

|-------------------------|-----------------------|----|--------|------|--------|------|------------------------|

|                         |                       |    | Min.   | Тур. | Max.   |      | Test Condition         |

| Rise time               | t <sub>R</sub>        | CC | 4      | -    | 20     | ns   | C <sub>L</sub> = 50 pF |

| Fall time               | t <sub>F</sub>        | CC | 4      | -    | 20     | ns   | C <sub>L</sub> = 50 pF |

| Rise/Fall time matching | $t_{\rm R}/t_{\rm F}$ | CC | 90     | -    | 111.11 | %    | C <sub>L</sub> = 50 pF |

| Crossover voltage       | V <sub>CRS</sub>      | CC | 1.3    | -    | 2.0    | V    | C <sub>L</sub> = 50 pF |

Table 54

USB Timing Parameters (operating conditions apply)

Figure 35 USB Signal Timing

### Package and Reliability

power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

### Package and Reliability

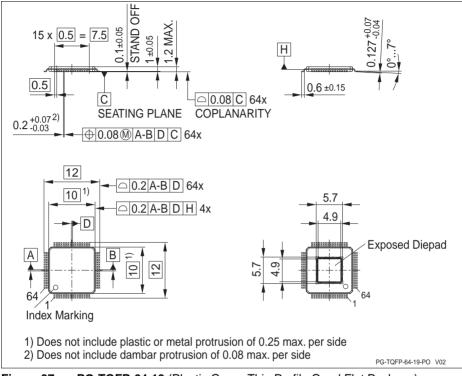

Figure 37 PG-TQFP-64-19 (Plastic Green Thin Profile Quad Flat Package)

### Table 57 Differences PG-VQFN-48-53 to PG-VQFN-48-71

| Change         | PG-VQFN-48-53            | PG-VQFN-48-71                     |

|----------------|--------------------------|-----------------------------------|

| Package corner | chamfered                | right-angled                      |

| Lead width     | 0.23 <sup>±0.05</sup> mm | 0.25 <sup>(+0.05, -0.07)</sup> mm |

| Lead height    | 0.4 <sup>±0.07</sup> mm  | 0.4 <sup>±0.05</sup> mm           |