Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 20K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 9x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | PG-VQFN-48-53                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4104q48k128baxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2015-10

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2015 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Trademarks**

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM®, ARM Powered®, Cortex®, Thumb® and AMBA® are registered trademarks of ARM, Limited.

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM. Limited.

Synopsys<sup>™</sup> is a trademark of Synopsys, Inc.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.3, 2015-10

# **Summary of Features**

Table 6 SRAM Memory Ranges

| Total SRAM Size | Program SRAM                                       | System Data SRAM                                   |

|-----------------|----------------------------------------------------|----------------------------------------------------|

| 40 Kbytes       | 1FFF C000 <sub>H</sub> –<br>1FFF FFFF <sub>H</sub> | 2000 0000 <sub>H</sub> –<br>2000 5FFF <sub>H</sub> |

| 20 Kbytes       | 1FFF E000 <sub>H</sub> –<br>1FFF FFFF <sub>H</sub> | 2000 0000 <sub>H</sub> –<br>2000 2FFF <sub>H</sub> |

Table 7 ADC Channels<sup>1)</sup>

| Package          | VADC G0     | VADC G1            |

|------------------|-------------|--------------------|

| LQFP-64, TQFP-64 | CH0, CH3CH7 | CH0, CH1, CH3, CH6 |

| PG-VQFN-48       | CH0, CH3CH7 | CH0, CH1, CH3      |

Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

# 1.6 Identification Registers

The identification registers allow software to identify the marking.

Table 8 XMC4200 Identification Registers

| Register Name | Value                  | Marking       |

|---------------|------------------------|---------------|

| SCU_IDCHIP    | 0004 2001 <sub>H</sub> | EES-AA, ES-AA |

| SCU_IDCHIP    | 0004 2002 <sub>H</sub> | ES-AB, AB     |

| SCU_IDCHIP    | 0004 2003 <sub>H</sub> | BA            |

| JTAG IDCODE   | 101D D083 <sub>H</sub> | EES-AA, ES-AA |

| JTAG IDCODE   | 201D D083 <sub>H</sub> | ES-AB, AB     |

| JTAG IDCODE   | 301D D083 <sub>H</sub> | ВА            |

#### **General Device Information**

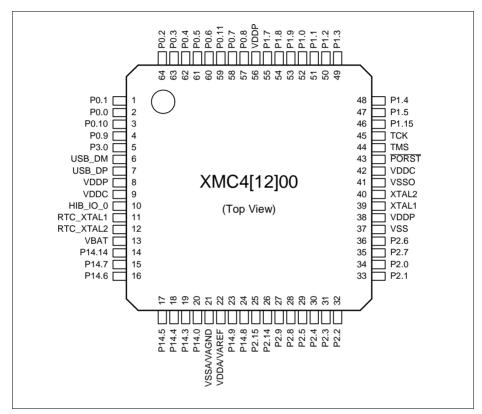

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

Figure 4 XMC4[12]00 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

### **General Device Information**

Table 11 Package Pin Mapping (cont'd)

| Function   | LQFP-64<br>TQFP-64     | VQFN-48 | Pad Type                                                                                                                                                                   | Notes                                                                                                  |

|------------|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| P14.9      | 23                     | 19      | AN/DAC/DIG_IN                                                                                                                                                              |                                                                                                        |

| P14.14     | 14                     | -       | AN/DIG_IN                                                                                                                                                                  |                                                                                                        |

| USB_DP     | 7                      | 4       | special                                                                                                                                                                    |                                                                                                        |

| USB_DM     | 6                      | 3       | special                                                                                                                                                                    |                                                                                                        |

| HIB_IO_0   | B_IO_0 10 7 A1 special |         | At the first power-up and with every reset of the hibernate domain this pin is configured as open-drain output and drives "0". As output the medium driver mode is active. |                                                                                                        |

| TCK        | 45                     | 34      | A1                                                                                                                                                                         | Weak pull-down active.                                                                                 |

| TMS        | 44                     | 33      | A1+                                                                                                                                                                        | Weak pull-up active. As output the strong-soft driver mode is active.                                  |

| PORST      | 43                     | 32      | special                                                                                                                                                                    | Strong pull-down controlled<br>by EVR.<br>Weak pull-up active while<br>strong pull-down is not active. |

| XTAL1      | 39                     | 29      | clock_IN                                                                                                                                                                   |                                                                                                        |

| XTAL2      | 40                     | 30      | clock_O                                                                                                                                                                    |                                                                                                        |

| RTC_XTAL1  | 11                     | 8       | clock_IN                                                                                                                                                                   |                                                                                                        |

| RTC_XTAL2  | 12                     | 9       | clock_O                                                                                                                                                                    |                                                                                                        |

| VBAT       | 13                     | 10      | Power                                                                                                                                                                      | When VDDP is supplied VBAT has to be supplied as well.                                                 |

| VDDA/VAREF | 22                     | 18      | AN_Power/AN_<br>Ref                                                                                                                                                        | Shared analog supply and reference voltage pin.                                                        |

| VSSA/VAGND | 21                     | 17      | AN_Power/AN_<br>Ref                                                                                                                                                        | Shared analog supply and reference ground pin.                                                         |

| VDDC       | 9                      | 6       | Power                                                                                                                                                                      |                                                                                                        |

| VDDC       | 42                     | 31      | Power                                                                                                                                                                      |                                                                                                        |

| VDDP       | 8                      | 5       | Power                                                                                                                                                                      |                                                                                                        |

| VDDP       | 38                     | 28      | Power                                                                                                                                                                      |                                                                                                        |

| VDDP       | 56                     | 41      | Power                                                                                                                                                                      |                                                                                                        |

| VSS        | 37                     | 27      | Power                                                                                                                                                                      |                                                                                                        |

#### **General Device Information**

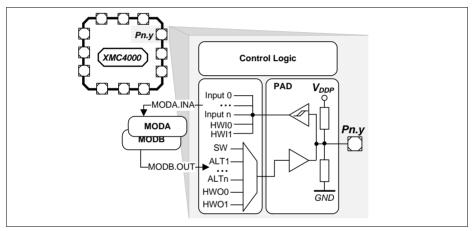

#### 2.2.2 Port I/O Functions

The following general scheme is used to describe each PORT pin:

Table 12 Port I/O Function Description

| Function |          | Outputs  |          | Inputs   |          |          |  |  |

|----------|----------|----------|----------|----------|----------|----------|--|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |  |

Figure 6 Simplified Port Structure

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to four alternate output functions (ALT1/2/3/4) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL it is possible to select between different hardware "masters" (HWO0/HWI0). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

Subject to Agreement on the Use of Product Information

# $\label{eq:continuous} V1.3,\,2015\text{-}10$ Subject to Agreement on the Use of Product Information

#### **Port I/O Function Table** 2.2.2.1

| Table 13 | Port I               | /O Funct         | ions            |                    |                |                |               |                 |              |                         |                |                  |                |                |

|----------|----------------------|------------------|-----------------|--------------------|----------------|----------------|---------------|-----------------|--------------|-------------------------|----------------|------------------|----------------|----------------|

| Function |                      |                  | Output          |                    |                |                |               |                 |              | Input                   |                |                  |                |                |

|          | ALT1                 | ALT2             | ALT3            | ALT4               | HWO0           | HWI0           | Input         | Input           | Input        | Input                   | Input          | Input            | Input          | Input          |

| P0.0     |                      | CAN.<br>N0_TXD   | CCU80.<br>OUT21 | LEDTS0.<br>COL2    |                |                | U1C1.<br>DX0D |                 | ERU0.<br>0B0 | USB.<br>VBUSDETECT<br>A |                | HRPWM0.<br>C1INB |                |                |

| P0.1     |                      | U1C1.<br>DOUT0   | CCU80.<br>OUT11 | LEDTS0.<br>COL3    |                |                |               |                 | ERU0.<br>0A0 |                         |                | HRPWM0.<br>C2INB |                |                |

| P0.2     |                      | U1C1.<br>SELO1   | CCU80.<br>OUT01 | HRPWM0.<br>HROUT01 | U1C0.<br>DOUT3 | U1C0.<br>HWIN3 |               |                 | ERU0.<br>3B3 |                         |                |                  |                |                |

| P0.3     |                      |                  | CCU80.<br>OUT20 | HRPWM0.<br>HROUT20 | U1C0.<br>DOUT2 | U1C0.<br>HWIN2 |               |                 |              | ERU1.<br>3B0            |                |                  |                |                |

| P0.4     |                      |                  | CCU80.<br>OUT10 | HRPWM0.<br>HROUT21 | U1C0.<br>DOUT1 | U1C0.<br>HWIN1 |               | U1C0.<br>DX0A   | ERU0.<br>2B3 |                         |                |                  |                |                |

| P0.5     |                      | U1C0.<br>DOUT0   | CCU80.<br>OUT00 | HRPWM0.<br>HROUT00 | U1C0.<br>DOUT0 | U1C0.<br>HWIN0 |               | U1C0.<br>DX0B   |              | ERU1.<br>3A0            |                |                  |                |                |

| P0.6     |                      | U1C0.<br>SELO0   | CCU80.<br>OUT30 | HRPWM0.<br>HROUT30 |                |                |               | U1C0.<br>DX2A   | ERU0.<br>3B2 |                         | CCU80.<br>IN2B |                  |                |                |

| P0.7     | WWDT.<br>SERVICE_OUT | U0C0.<br>SELO0   |                 | HRPWM0.<br>HROUT11 |                | DB.<br>TDI     | U0C0.<br>DX2B |                 | ERU0.<br>2B1 |                         | CCU80.<br>IN0A | CCU80.<br>IN1A   | CCU80.<br>IN2A | CCU80.<br>IN3A |

| P0.8     | SCU.<br>EXTCLK       | U0C0.<br>SCLKOUT |                 | HRPWM0.<br>HROUT10 |                | DB.<br>TRST    | U0C0.<br>DX1B |                 | ERU0.<br>2A1 |                         | CCU80.<br>IN1B |                  |                |                |

| P0.9     | HRPWM0.<br>HROUT31   | U1C1.<br>SELO0   | CCU80.<br>OUT12 | LEDTS0.<br>COL0    |                |                | U1C1.<br>DX2A |                 | ERU0.<br>1B0 |                         |                |                  |                |                |

| P0.10    |                      | U1C1.<br>SCLKOUT | CCU80.<br>OUT02 | LEDTS0.<br>COL1    |                |                | U1C1.<br>DX1A |                 | ERU0.<br>1A0 |                         |                |                  |                |                |

| P0.11    |                      | U1C0.<br>SCLKOUT | CCU80.<br>OUT31 |                    |                |                |               | U1C0.<br>DX1A   | ERU0.<br>3A2 |                         |                |                  |                |                |

| P1.0     |                      | U0C0.<br>SELO0   | CCU40.<br>OUT3  | ERU1.<br>PDOUT3    |                |                | U0C0.<br>DX2A |                 | ERU0.<br>3B0 |                         | CCU40.<br>IN3A | HRPWM0.<br>COINA |                |                |

| P1.1     |                      | U0C0.<br>SCLKOUT | CCU40.<br>OUT2  | ERU1.<br>PDOUT2    |                |                | U0C0.<br>DX1A | POSIF0.<br>IN2A | ERU0.<br>3A0 |                         | CCU40.<br>IN2A | HRPWM0.<br>C1INA |                |                |

| P1.2     |                      |                  | CCU40.<br>OUT1  | ERU1.<br>PDOUT1    | U0C0.<br>DOUT3 | U0C0.<br>HWIN3 |               | POSIF0.<br>IN1A |              | ERU1.<br>2B0            | CCU40.<br>IN1A | HRPWM0.<br>C2INA |                |                |

| P1.3     |                      | U0C0.<br>MCLKOUT | CCU40.<br>OUT0  | ERU1.<br>PDOUT0    | U0C0.<br>DOUT2 | U0C0.<br>HWIN2 |               | POSIFO.<br>INOA |              | ERU1.<br>2A0            | CCU40.<br>INOA | HRPWM0.<br>COINB |                |                |

| P1.4     | WWDT.<br>SERVICE_OUT | CAN.<br>NO_TXD   | CCU80.<br>OUT33 |                    | U0C0.<br>DOUT1 | U0C0.<br>HWIN1 | U0C0.<br>DX0B | CAN.<br>N1_RXDD | ERU0.<br>2B0 |                         | CCU41.<br>INOC | HRPWM0.<br>BL0A  |                |                |

| P1.5     | CAN.<br>N1_TXD       | U0C0.<br>DOUT0   | CCU80.<br>OUT23 |                    | U0C0.<br>DOUT0 | U0C0.<br>HWIN0 | U0C0.<br>DX0A | CAN.<br>NO_RXDA | ERU0.<br>2A0 | ERU1.<br>0A0            | CCU41.<br>IN1C |                  |                |                |

| P1.7     |                      | U0C0.<br>DOUT0   |                 | U1C1.<br>SELO2     |                |                |               |                 |              | USB.<br>VBUSDETECT<br>B |                |                  |                |                |

XMC4000 Family

Table 13 Port I/O Functions (CONt'd)

| Function  |        |                      | Output |      |                  | Input            |               |                |               |                         |       |       |        |       |

|-----------|--------|----------------------|--------|------|------------------|------------------|---------------|----------------|---------------|-------------------------|-------|-------|--------|-------|

|           | ALT1   | ALT2                 | ALT3   | ALT4 | HWO0             | HWI0             | Input         | Input          | Input         | Input                   | Input | Input | Input  | Input |

| P14.9     |        |                      |        |      | DAC.<br>OUT_1    |                  |               | VADC.<br>G1CH1 |               |                         |       |       |        |       |

| P14.14    |        |                      |        |      |                  |                  |               | VADC.<br>G1CH6 |               |                         |       |       | G1ORC6 |       |

| USB_DP    |        |                      |        |      |                  |                  |               |                |               |                         |       |       |        |       |

| USB_DM    |        |                      |        |      |                  |                  |               |                |               |                         |       |       |        |       |

| HIB_IO_0  | HIBOUT | WWDT.<br>SERVICE_OUT |        |      |                  |                  | WAKEUPA       |                |               | USB.<br>VBUSDETECT<br>C |       |       |        |       |

| тск       |        |                      |        |      |                  | DB.TCK/<br>SWCLK |               |                |               |                         |       |       |        |       |

| TMS       |        |                      |        |      | DB.TMS/<br>SWDIO |                  |               |                |               |                         |       |       |        |       |

| PORST     |        |                      |        |      |                  |                  |               |                |               |                         |       |       |        |       |

| XTAL1     |        |                      |        |      |                  |                  | U0C0.<br>DX0F | U0C1.<br>DX0F  | U1C0.<br>DX0F | U1C1.<br>DX0F           |       |       |        |       |

| XTAL2     |        |                      |        |      |                  |                  |               |                |               |                         |       |       |        |       |

| RTC_XTAL1 |        |                      |        |      |                  |                  |               |                | ERU0.<br>1B1  |                         |       |       |        |       |

| RTC_XTAL2 |        |                      |        |      |                  |                  |               |                |               |                         |       |       |        |       |

The XMC4[12]00 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

There are no dedicated connections for the analog reference  $V_{\rm AREF}$  and  $V_{\rm AGND}$ . Instead, they share the same pins as the analog supply pins  $V_{\rm DDA}$  and  $V_{\rm SSA}$ . Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\rm DDP}$  is supplied,  $V_{\rm BAT}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\rm BAT}$ , the  $V_{\rm BAT}$  pin can also be connected directly to  $V_{\rm DDP}$ .

# 3.1.5 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation and reliability of the XMC4[12]00. All parameters specified in the following tables refer to these operating conditions, unless noted otherwise.

Table 20 Operating Conditions Parameters

| Parameter                                                           | Symbol                          |                    | Values | 1                  | Unit | Note /                                                                   |

|---------------------------------------------------------------------|---------------------------------|--------------------|--------|--------------------|------|--------------------------------------------------------------------------|

|                                                                     |                                 | Min.               | Тур.   | Max.               |      | Test Condition                                                           |

| Ambient Temperature                                                 | $T_{A}$ SR                      | -40                | _      | 85                 | °C   | Temp. Range F                                                            |

|                                                                     |                                 | -40                | _      | 125                | °C   | Temp. Range K                                                            |

| Digital supply voltage                                              | $V_{\mathrm{DDP}}\mathrm{SR}$   | 3.13 <sup>1)</sup> | 3.3    | 3.63 <sup>2)</sup> | V    |                                                                          |

| Core Supply Voltage                                                 | $V_{ m DDC}$                    | _1)                | 1.3    | _                  | V    | Generated internally                                                     |

| Digital ground voltage                                              | $V_{\mathrm{SS}}$ SR            | 0                  | _      | _                  | ٧    |                                                                          |

| ADC analog supply voltage                                           | $V_{DDA}SR$                     | 3.0                | 3.3    | 3.6 <sup>2)</sup>  | V    |                                                                          |

| $ \overline{ \text{Analog ground voltage for} } \\ V_{\text{DDA}} $ | $V_{SSA}SR$                     | -0.1               | 0      | 0.1                | V    |                                                                          |

| Battery Supply Voltage for Hibernate Domain <sup>3)</sup>           | $V_{BAT}SR$                     | 1.95 <sup>4)</sup> | _      | 3.63               | V    | When $V_{\rm DDP}$ is supplied $V_{\rm BAT}$ has to be supplied as well. |

| System Frequency                                                    | $f_{\mathrm{SYS}}$ SR           | _                  | _      | 80                 | MHz  |                                                                          |

| Short circuit current of digital outputs                            | I <sub>SC</sub> SR              | -5                 | _      | 5                  | mA   |                                                                          |

| Absolute sum of short circuit currents per pin group <sup>5)</sup>  | $\Sigma I_{\mathrm{SC\_PG}}$ SR | _                  | _      | 20                 | mA   |                                                                          |

| Absolute sum of short circuit currents of the device                | $\Sigma I_{\text{SC\_D}}$ SR    | -                  | -      | 100                | mA   |                                                                          |

<sup>1)</sup> See also the Supply Monitoring thresholds, Section 3.3.2.

<sup>2)</sup> Voltage overshoot to 4.0 V is permissible at Power-Up and PORST low, provided the pulse duration is less than 100 μs and the cumulated sum of the pulses does not exceed 1 h over lifetime.

<sup>3)</sup> Different limits apply for LPAC operation, Section 3.2.6

<sup>4)</sup> To start the hibernate domain it is required that V<sub>BAT</sub> ≥ 2.1 V, for a reliable start of the oscillation of RTC\_XTAL in crystal mode it is required that V<sub>BAT</sub> ≥ 3.0 V.

<sup>5)</sup> The port groups are defined in Table 18.

Table 24 HIB\_IO Class\_A1 special Pads

| Parameter                                          | Symbol                  | Va                     | lues                 | Unit | Note /                                                                          |  |

|----------------------------------------------------|-------------------------|------------------------|----------------------|------|---------------------------------------------------------------------------------|--|

|                                                    |                         | Min.                   | Max.                 |      | Test Condition                                                                  |  |

| Input leakage current                              | $I_{OZHIB}$ CC          | -500                   | 500                  | nA   | $0 \text{ V} \leq V_{IN} \leq V_{BAT}$                                          |  |

| Input high voltage                                 | $V_{\mathrm{IHHIB}}$ SR | $0.6 	imes V_{BAT}$    | $V_{BAT}$ + 0.3      | V    | max. 3.6 V                                                                      |  |

| Input low voltage                                  | $V_{ILHIB}$ SR          | -0.3                   | $0.36 	imes V_{BAT}$ | V    |                                                                                 |  |

| Input Hysteresis for                               | HYSHIB                  | $0.1 	imes V_{BAT}$    | _                    | V    | $V_{BAT} \geq 3.13\;V$                                                          |  |

| HIB_IO pins <sup>1)</sup>                          | CC                      | $0.06 	imes V_{BAT}$   | -                    | V    | $V_{\mathrm{BAT}}$ < 3.13 V                                                     |  |

| Output high voltage,<br>POD <sup>1)</sup> = medium | $V_{OHHIB}$ CC          | V <sub>BAT</sub> - 0.4 | _                    | ٧    | $I_{\mathrm{OH}} \geq$ -1.4 mA                                                  |  |

| Output low voltage                                 | $V_{OLHIB}$ CC          | -                      | 0.4                  | V    | $I_{\rm OL} \le 2 \; {\rm mA}$                                                  |  |

| Fall time                                          | t <sub>FHIB</sub> CC    | -                      | 50                   | ns   | $V_{\rm BAT} \ge 3.13 \text{ V}$<br>$C_{\rm L} = 50 \text{ pF}$                 |  |

|                                                    |                         | _                      | 100                  | ns   | $V_{\mathrm{BAT}}$ < 3.13 V $C_{\mathrm{L}}$ = 50 pF                            |  |

| Rise time                                          | $t_{RHIB}CC$            | _                      | 50                   | ns   | $V_{\mathrm{BAT}} \ge 3.13 \ \mathrm{V}$<br>$C_{\mathrm{L}} = 50 \ \mathrm{pF}$ |  |

|                                                    |                         | -                      | 100                  | ns   | $V_{\mathrm{BAT}}$ < 3.13 V $C_{\mathrm{L}}$ = 50 pF                            |  |

<sup>1)</sup> Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

Table 30

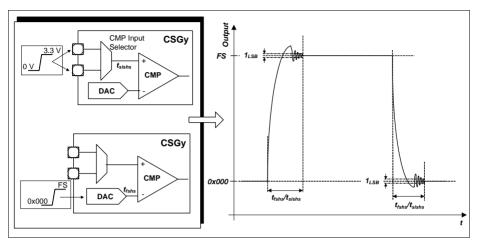

CMP and 10-bit DAC characteristics (Operating Conditions apply)

| Parameter                                     | Symbol                 |                                  | Values | 3         | Unit | Note /         |

|-----------------------------------------------|------------------------|----------------------------------|--------|-----------|------|----------------|

|                                               |                        | Min.                             | Тур.   | Max.      |      | Test Condition |

| CSG Output Jitter                             | $D_{	extsf{CSG}}$      | _                                | -      | 1         | clk  |                |

| Bias startup time                             | t <sub>start</sub> CC  | _                                | _      | 98        | us   |                |

| Bias supply current                           | I <sub>DDbias</sub> CC | _                                | _      | 400       | μА   |                |

| CSGy startup time                             | t <sub>CSGS</sub>      | _                                | _      | 2         | μS   |                |

| Input operation current <sup>1)</sup>         | $I_{ m DDCIN}$         | -10                              | _      | 33        | μА   | See Figure 19  |

| High Speed Mode                               |                        |                                  |        | •         | •    |                |

| DAC output voltage range                      | $V_{DOUT}$ CC          | $V_{ m SS}$                      | _      | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full scale         | t <sub>FShs</sub> CC   | _                                | _      | 80        | ns   | See Figure 20  |

| Input Selector propagation delay - Full scale | t <sub>Dhs</sub> CC    | _                                | _      | 100       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dhs</sub> CC    | 20                               | -      | _         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}$ SR       | _                                | _      | 30        | MHz  |                |

| Supply current                                | I <sub>DDhs</sub>      | _                                | _      | 940       | μА   |                |

| Low Speed Mode                                |                        |                                  |        |           |      |                |

| DAC output voltage range                      | $V_{DOUT}$ CC          | $0.1 \times V_{\text{DDP}}^{2)}$ | _      | $V_{DDP}$ | V    |                |

| DAC propagation delay -<br>Full Scale         | t <sub>FSIs</sub> CC   | _                                | _      | 160       | ns   | See Figure 20  |

| Input Selector propagation delay - Full Scale | t <sub>DIs</sub> CC    | _                                | -      | 200       | ns   | See Figure 20  |

| Comparator bandwidth                          | t <sub>Dls</sub> CC    | 20                               | _      | _         | ns   |                |

| DAC CLK frequency                             | $f_{\rm clk}$ SR       | _                                | _      | 30        | MHz  |                |

| Supply current                                | I <sub>DDIs</sub> CC   | _                                | -      | 300       | μΑ   |                |

<sup>1)</sup> Typical input resistance  $R_{CIN} = 100 \text{kOhm}$ .

Subject to Agreement on the Use of Product Information

<sup>2)</sup> The INL error increases for DAC output voltages below this limit.

Figure 20 DAC and Input Selector Propagation Delay

#### 3.2.5.3 Clocks

#### **HRPWM DAC Conversion Clock**

The DAC conversion clock can be generated internally or it can be controlled via a HRPWM module pin.

Table 31 External DAC conversion trigger operating conditions

|           |                         | • •                    |        | •                |        |                 |

|-----------|-------------------------|------------------------|--------|------------------|--------|-----------------|

| Parameter | Symbol                  | ,                      | /alues | Unit             | Note / |                 |

|           |                         | Min.                   | Тур.   | Max.             |        | Test Con dition |

| Frequency | $f_{ m etrg}$ SR        | _                      | -      | 30 <sup>2)</sup> | MHz    |                 |

| ON time   | t <sub>onetrg</sub> SR  | $2T_{\rm ccu}^{-1)2)}$ | -      | -                | ns     |                 |

| OFF time  | t <sub>offetrg</sub> SR | $2T_{\rm ccu}^{-1)2)}$ | -      | -                | ns     |                 |

<sup>1) 50%</sup> duty cycle is not obligatory

#### **CSG External Clock**

It is possible to select an external source, that can be used as a clock for the slope generation, HRPWMx.ECLKy. This clock is synchronized internally with the module clock and therefore the external clock needs to meet the criterion described on **Table 32**.

<sup>2)</sup> Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

# Table 38 Power Supply Parameters

| Parameter                                      | Symbol     |    | Values |      |      | Unit   | Note /                                                                     |

|------------------------------------------------|------------|----|--------|------|------|--------|----------------------------------------------------------------------------|

|                                                |            |    | Min.   | Тур. | Max. |        | Test Condition                                                             |

| Power Dissipation                              | $P_{DISS}$ | CC | _      | _    | 1    | W      | $V_{\rm DDP} = 3.6 \text{ V},$<br>$T_{\rm J} = 150 ^{\circ}\text{C}$       |

| Wake-up time from Sleep to Active mode         | $t_{SSA}$  | CC | _      | 6    | _    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |            |    | _      | _    | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |            |    | -      | _    | _    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

- 1) CPU executing code from Flash, all peripherals idle.

- 2) CPU executing code from Flash. USB and CCU clock off.

- 3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPII} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 80 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

- The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\rm DDP}$  decreases typically by 3.5 mA when  $f_{\rm SYS}$  decreases by 10 MHz, at constant  $T_{\rm J}$

- 11) Sum of currents of all active converters (ADC and DAC)

# 3.2.11 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 40 Flash Memory Parameters

| Parameter                                               | Symbol                 |      | Values | 5    | Unit  | Note /<br>Test Condition                                                                    |

|---------------------------------------------------------|------------------------|------|--------|------|-------|---------------------------------------------------------------------------------------------|

|                                                         |                        | Min. | Тур.   | Max. |       |                                                                                             |

| Erase Time per 256<br>Kbyte Sector                      | $t_{ERP}CC$            | _    | 5      | 5.5  | S     |                                                                                             |

| Erase Time per 64 Kbyte<br>Sector                       | t <sub>ERP</sub> CC    | _    | 1.2    | 1.4  | S     |                                                                                             |

| Erase Time per 16 Kbyte<br>Logical Sector               | t <sub>ERP</sub> CC    | _    | 0.3    | 0.4  | S     |                                                                                             |

| Program time per page <sup>1)</sup>                     | $t_{PRP}CC$            | _    | 5.5    | 11   | ms    |                                                                                             |

| Erase suspend delay                                     | t <sub>FL_ErSusp</sub> | _    | -      | 15   | ms    |                                                                                             |

| Wait time after margin change                           | t <sub>FL_Margin</sub> | 10   | -      | _    | μS    |                                                                                             |

| Wake-up time                                            | $t_{WU}CC$             | _    | _      | 270  | μS    |                                                                                             |

| Read access time                                        | t <sub>a</sub> CC      | 20   | -      | _    | ns    | For operation with $1/f_{\rm CPU} < t_{\rm a}$ wait states must be configured <sup>2)</sup> |

| Data Retention Time,<br>Physical Sector <sup>3)4)</sup> | $t_{RET}CC$            | 20   | -      | -    | years | Max. 1000<br>erase/program<br>cycles                                                        |

| Data Retention Time,<br>Logical Sector <sup>3)4)</sup>  | t <sub>RETL</sub> CC   | 20   | _      | -    | years | Max. 100<br>erase/program<br>cycles                                                         |

### 3.3 AC Parameters

# 3.3.1 Testing Waveforms

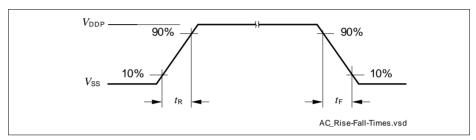

Figure 23 Rise/Fall Time Parameters

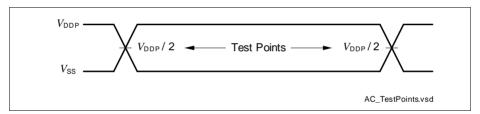

Figure 24 Testing Waveform, Output Delay

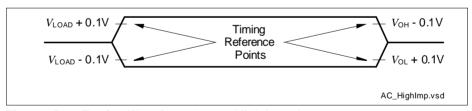

Figure 25 Testing Waveform, Output High Impedance

Table 42 Power Sequencing Parameters

| Parameter                                                        | Symbol               | Values |      |      | Unit | Note /                                                                  |

|------------------------------------------------------------------|----------------------|--------|------|------|------|-------------------------------------------------------------------------|

|                                                                  |                      | Min.   | Тур. | Max. |      | Test Condition                                                          |

| Positive Load Step Current                                       | $\Delta I_{PLS}SR$   | -      | _    | 50   | mA   | Load increase on $V_{\rm DDP}$ $\Delta t \leq 10 \text{ ns}$            |

| Negative Load Step<br>Current                                    | $\Delta I_{NLS}SR$   | -      | _    | 150  | mA   | Load decrease on $V_{\text{DDP}}$ $\Delta t \leq 10 \text{ ns}$         |

| V <sub>DDC</sub> Voltage Over-<br>/ Undershoot from Load<br>Step | $\Delta V_{LS}$ CC   | -      | _    | ±100 | mV   | For maximum positive or negative load step                              |

| Positive Load Step Settling Time                                 | t <sub>PLSS</sub> SR | 50     | _    | -    | μS   |                                                                         |

| Negative Load Step<br>Settling Time                              | t <sub>NLSS</sub> SR | 100    | -    | -    | μS   |                                                                         |

| External Buffer Capacitor on $V_{\mathrm{DDC}}$                  | C <sub>EXT</sub> SR  | 3      | 4.7  | 6    | μF   | In addition $C = 100 \text{ nF}$ capacitor on each $V_{\text{DDC}}$ pin |

### **Positive Load Step Examples**

System assumptions:

$f_{\rm CPU}$  =  $f_{\rm SYS}$ , target frequency  $f_{\rm CPU}$  = 80 MHz, main PLL  $f_{\rm VCO}$  = 480 MHz, stepping done by K2 divider,  $t_{\rm PLSS}$  between individual steps:

24 MHz - 48 MHz - 80 MHz (K2 steps 20 - 10 - 6)

24 MHz - 60 MHz - 80 MHz (K2 steps 20 - 8 - 6)

# 3.3.4 Phase Locked Loop (PLL) Characteristics

### Main and USB PLL

Table 43 PLL Parameters

| Parameter                | Symbol              |      | Value | S    | Unit | Note /<br>Test Condition                                                    |

|--------------------------|---------------------|------|-------|------|------|-----------------------------------------------------------------------------|

|                          |                     | Min. | Тур.  | Max. |      |                                                                             |

| Accumulated Jitter       | $D_{P}CC$           | _    | -     | ±5   | ns   | accumulated over 300 cycles $f_{\rm SYS}$ = 80 MHz                          |

| Duty Cycle <sup>1)</sup> | D <sub>DC</sub> CC  | 46   | 50    | 54   | %    | Low pulse to<br>total period,<br>assuming an<br>ideal input clock<br>source |

| PLL base frequency       | $f_{ m PLLBASE}$ CC | 30   | _     | 140  | MHz  |                                                                             |

| VCO input frequency      | $f_{REF}CC$         | 4    | _     | 16   | MHz  |                                                                             |

| VCO frequency range      | $f_{\sf VCO}\sf CC$ | 260  | _     | 520  | MHz  |                                                                             |

| PLL lock-in time         | $t_{L}$ CC          | _    | _     | 400  | μS   |                                                                             |

<sup>1) 50%</sup> for even K2 divider values, 50±(10/K2) for odd K2 divider values.

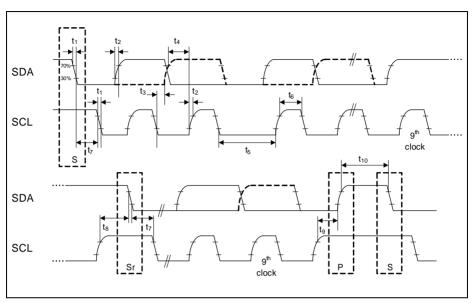

Figure 32 USIC IIC Stand and Fast Mode Timing

# 3.3.8.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.

Note: Operating Conditions apply.

Table 52 USIC IIS Master Transmitter Timing

| Parameter       | Symbol            |            | Values | 3          | Unit | Note /<br>Test Condition |

|-----------------|-------------------|------------|--------|------------|------|--------------------------|

|                 |                   | Min.       | Тур.   | Max.       |      |                          |

| Clock period    | t <sub>1</sub> CC | 33.3       | -      | _          | ns   |                          |

| Clock high time | t <sub>2</sub> CC | 0.35 x     | _      | _          | ns   |                          |

|                 |                   | $t_{1min}$ |        |            |      |                          |

| Clock low time  | t <sub>3</sub> CC | 0.35 x     | _      | _          | ns   |                          |

|                 |                   | $t_{1min}$ |        |            |      |                          |

| Hold time       | t <sub>4</sub> CC | 0          | _      | _          | ns   |                          |

| Clock rise time | t <sub>5</sub> CC | -          | _      | 0.15 x     | ns   |                          |

|                 |                   |            |        | $t_{1min}$ |      |                          |

#### Package and Reliability

power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}} - V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\mathsf{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\rm DDP}$ , if possible in the system

- · Reduce the system frequency

- Reduce the number of output pins

- · Reduce the load on active output drivers