Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Supplier Device Package    | PG-LQFP-64-19  https://www.e-xfl.com/product-detail/infineon-technologies/xmc4108f64k64abxqma: |

|----------------------------|------------------------------------------------------------------------------------------------|

| ackage / Case              | 64-LQFP Exposed Pad                                                                            |

| ounting Type               | Surface Mount                                                                                  |

| perating Temperature       | -40°C ~ 125°C (TA)                                                                             |

| Oscillator Type            | Internal                                                                                       |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                                  |

| RAM Size                   | 20K x 8                                                                                        |

| EEPROM Size                | -                                                                                              |

| Program Memory Type        | FLASH                                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                                                 |

| lumber of I/O              | 35                                                                                             |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                                         |

| ipeed                      | 80MHz                                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                             |

| Core Processor             | ARM® Cortex®-M4                                                                                |

| Product Status             | Not For New Designs                                                                            |

Edition 2015-10

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2015 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XMC4100 / XMC4200

Microcontroller Series for Industrial Applications

XMC4000 Family

ARM® Cortex®-M4 32-bit processor core

Data Sheet V1.3 2015-10

Microcontrollers

# XMC4[12]00 Data Sheet

# Revision History: V1.3 2015-10

**Previous Versions:**

V1.2 2014-06

V1.1 2014-03

V1.0 2013-10

V0.6 2012-11

| VU.0 201 | 2-11                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page     | Subjects                                                                                                                                                         |

| 12       | Added a section listing the packages of the different markings.                                                                                                  |

| 14       | Added BA marking variant.                                                                                                                                        |

| 14       | Corrected SCU_IDCHIP value of XMC4100 EES-AA/ES-AA.                                                                                                              |

| 36       | Added footnote explaining minimum $V_{\rm BAT}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL.                          |

| 37       | Changed pull device definition to System Requirement (SR) to reflect that the specified currents are defined by the characteristics of the external load/driver. |

| 37       | Added information that PORST Pull-up is identical to the pull-up on standard I/O pins.                                                                           |

| 42       | Updated $C_{\mathrm{AINSW}}$ , $C_{\mathrm{AINTOT}}$ and $R_{\mathrm{AIN}}$ parameters with improved values.                                                     |

| 56       | Added footnote on test configuration for LPAC measurement.                                                                                                       |

| 58       | Corrected parameter name of of USB pull device (upstream port receiving) definition according to USB standard (referenced to DM instead of DP)                   |

| 62       | Relaxed RTC_XTAL $V_{\rm PPX}$ parameter value and changed it to a system requirement.                                                                           |

| 66       | Added footnote on current consumption by enabling of $f_{\rm CCU}$ .                                                                                             |

| 67       | Added Flash endurance parameter for 64 Kbytes Physical Sector PS4 $N_{\rm EPS4}$ for devices with BA marking.                                                    |

| many     | Added PG-TQFP-64-19 and PG-VQFN-48-71 package information.                                                                                                       |

| 89, 91   | Added tables describing the differences between PG-LQFP-64-19 to PG-TQFP-64-19 as well as PG-VQFN-48-53 to PG-VQFN-48-71 packages.                               |

| 93       | Updated to JEDEC standard J-STD-020D for the moisture sensitivity level and added solder temperature parameter according to the same standard.                   |

|          |                                                                                                                                                                  |

Data Sheet V1.3, 2015-10

## **Table of Contents**

| 5                               | Quality Declarations                                                               | 93       |

|---------------------------------|------------------------------------------------------------------------------------|----------|

| <b>4</b><br>4.1<br>4.1.1<br>4.2 | Package and Reliability Package Parameters Thermal Considerations Package Outlines | 87<br>87 |

|                                 |                                                                                    |          |

| 3.3.9                           | USB Interface Characteristics                                                      | 86       |

| 3.3.8.3                         | Inter-IC Sound (IIS) Interface Timing                                              | 84       |

| 3.3.8.2                         | Inter-IC (IIC) Interface Timing                                                    |          |

| 3.3.8.1                         | Synchronous Serial Interface (USIC SSC) Timing                                     |          |

| 3.3.8                           | Peripheral Timing                                                                  |          |

| 3.3.7                           | Serial Wire Debug Port (SW-DP) Timing                                              |          |

| 3.3.6                           | JTAG Interface Timing                                                              |          |

| 3.3.5                           | Internal Clock Source Characteristics                                              |          |

| 3.3.4                           | Phase Locked Loop (PLL) Characteristics                                            |          |

|                                 | DI 1 1 1 (DII) OI 1 1 1 1                                                          |          |

**About this Document**

# **About this Document**

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4[12]00 series devices.

The document describes the characteristics of a superset of the XMC4[12]00 series devices. For simplicity, the various device types are referred to by the collective term XMC4[12]00 throughout this manual.

# XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to <a href="http://www.infineon.com/xmc4000">http://www.infineon.com/xmc4000</a> to get access to the latest versions of those documents.

## **Summary of Features**

#### **On-Chip Memories**

- 16 KB on-chip boot ROM

- · up to 16 KB on-chip high-speed program memory

- up to 24 KB on-chip high speed data memory

- · up to 256 KB on-chip Flash Memory with 1 KB instruction cache

#### **Communication Peripherals**

- Universal Serial Bus, USB 2.0 device, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with two nodes, 64 message objects (MO), data rate up to 1 MBit/s

- Four Universal Serial Interface Channels (USIC), providing four serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

# **Analog Frontend Peripherals**

- Two Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

## **Industrial Control Peripherals**

- Two Capture/Compare Units 4 (CCU4) for use as general purpose timers

- One Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four High Resoultion PWM (HRPWM) channels

- One Position Interface (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- · Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

#### Input/Output Lines

- Programmable port driver control module (PORTS)

- · Individual bit addressability

- Tri-stated in input mode

- Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

# **On-Chip Debug Support**

- Full support for debug features: 8 breakpoints, CoreSight, trace

- Various interfaces: ARM-JTAG, SWD, single wire trace

## **Summary of Features**

# 1.1 Ordering Information

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. The code "XMC4<DDD>-<Z><PPP><T><FFFF>" identifies:

- · <DDD> the derivatives function set

- <Z> the package variant

- E: LFBGA

- F: LQFP, TQFP

- Q: VQFN

- <PPP> package pin count

- <T> the temperature range:

- F: -40°C to 85°C

- K: -40°C to 125°C

- <FFFF> the Flash memory size.

For ordering codes for the XMC4[12]00 please contact your sales representative or local distributor.

This document describes several derivatives of the XMC4100 and XMC4200 series, some descriptions may not apply to a specific product. Please see **Table 1**.

For simplicity the term **XMC4[12]00** is used for all derivatives throughout this document.

# 1.2 Device Types

These device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XMC4[12]00 Device Types

| Derivative <sup>1)</sup> | Package                  | Flash Kbytes | SRAM Kbytes |

|--------------------------|--------------------------|--------------|-------------|

| XMC4200-F64x256          | PG-yQFP-64 <sup>2)</sup> | 256          | 40          |

| XMC4200-Q48x256          | PG-VQFN-48               | 256          | 40          |

| XMC4100-F64x128          | PG-yQFP-64 <sup>2)</sup> | 128          | 20          |

| XMC4100-Q48x128          | PG-VQFN-48               | 128          | 20          |

| XMC4104-F64x64           | PG-yQFP-64 <sup>2)</sup> | 64           | 20          |

| XMC4104-Q48x64           | PG-VQFN-48               | 64           | 20          |

| XMC4104-F64x128          | PG-yQFP-64 <sup>2)</sup> | 128          | 20          |

| XMC4104-Q48x128          | PG-VQFN-48               | 128          | 20          |

| XMC4108-F64x64           | PG-yQFP-64 <sup>2)</sup> | 64           | 20          |

| XMC4108-Q48x64           | PG-VQFN-48               | 64           | 20          |

<sup>1)</sup> x is a placeholder for the supported temperature range.

<sup>2)</sup> y is a placeholder for the QFP package variant, LQFP or TQFP depending on the stepping, see Section 1.3.

# **Summary of Features**

Table 4 Features of XMC4[12]00 Device Types

| Derivative <sup>1)</sup> | ADC<br>Chan. | DAC<br>Chan. | CCU4<br>Slice | CCU8<br>Slice | POSIF<br>Intf. | HRPWM<br>Intf. |

|--------------------------|--------------|--------------|---------------|---------------|----------------|----------------|

| XMC4200-F64x256          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4200-Q48x256          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4100-F64x128          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4100-Q48x128          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-F64x64           | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-Q48x64           | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-F64x128          | 10           | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4104-Q48x128          | 9            | 2            | 2 x 4         | 1 x 4         | 1              | 1              |

| XMC4108-F64x64           | 10           | 2            | 2 x 4         | 1 x 4         | 1              | _              |

| XMC4108-Q48x64           | 9            | 2            | 2 x 4         | 1 x 4         | 1              | _              |

<sup>1)</sup> x is a placeholder for the supported temperature range.

#### 1.5 Definition of Feature Variants

The XMC4[12]00 types are offered with several memory sizes and number of available VADC channels. **Table 5** describes the location of the available Flash memory, **Table 6** describes the location of the available SRAMs, **Table 7** the available VADC channels.

Table 5 Flash Memory Ranges

| Total Flash Size | Cached Range                                       | Uncached Range                                     |

|------------------|----------------------------------------------------|----------------------------------------------------|

| 256 Kbytes       | 0800 0000 <sub>H</sub> -<br>0803 FFF <sub>H</sub>  | 0C00 0000 <sub>H</sub> -<br>0C03 FFF <sub>H</sub>  |

| 128 Kbytes       | 0800 0000 <sub>H</sub> –<br>0801 FFFF <sub>H</sub> | 0C00 0000 <sub>H</sub> -<br>0C01 FFFF <sub>H</sub> |

| 64 Kbytes        | 0800 0000 <sub>H</sub> -<br>0800 FFFF <sub>H</sub> | 0C00 0000 <sub>H</sub> -<br>0C00 FFFF <sub>H</sub> |

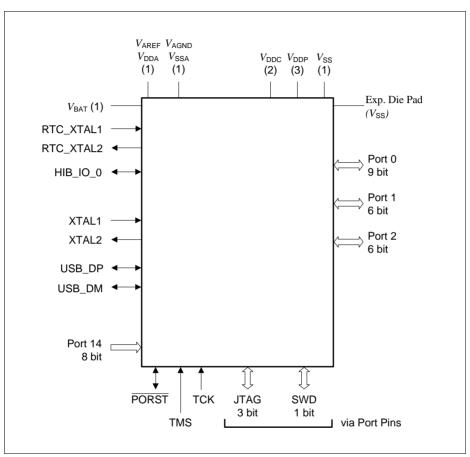

Figure 3 XMC4[12]00 Logic Symbol PG-VQFN-48

Table 11 Package Pin Mapping (cont'd)

| Function | LQFP-64<br>TQFP-64 | VQFN-48 | Pad Type      | Notes                                                                 |

|----------|--------------------|---------|---------------|-----------------------------------------------------------------------|

| P0.11    | 59                 | -       | A1+           |                                                                       |

| P1.0     | 52                 | 40      | A1+           |                                                                       |

| P1.1     | 51                 | 39      | A1+           |                                                                       |

| P1.2     | 50                 | 38      | A1+           |                                                                       |

| P1.3     | 49                 | 37      | A1+           |                                                                       |

| P1.4     | 48                 | 36      | A1+           |                                                                       |

| P1.5     | 47                 | 35      | A1+           |                                                                       |

| P1.7     | 55                 | -       | A1+           |                                                                       |

| P1.8     | 54                 | -       | A1+           |                                                                       |

| P1.9     | 53                 | -       | A1+           |                                                                       |

| P1.15    | 46                 | -       | A1+           |                                                                       |

| P2.0     | 34                 | 26      | A1+           |                                                                       |

| P2.1     | 33                 | 25      | A1+           | After a system reset, via HWSEL this pin selects the DB.TDO function. |

| P2.2     | 32                 | 24      | A1+           |                                                                       |

| P2.3     | 31                 | 23      | A1+           |                                                                       |

| P2.4     | 30                 | 22      | A1+           |                                                                       |

| P2.5     | 29                 | 21      | A1+           |                                                                       |

| P2.6     | 36                 | -       | A1+           |                                                                       |

| P2.7     | 35                 | -       | A1+           |                                                                       |

| P2.8     | 28                 | -       | A1+           |                                                                       |

| P2.9     | 27                 | -       | A1+           |                                                                       |

| P2.14    | 26                 | -       | A1+           |                                                                       |

| P2.15    | 25                 | -       | A1+           |                                                                       |

| P3.0     | 5                  | -       | A1+           |                                                                       |

| P14.0    | 20                 | 16      | AN/DIG_IN     |                                                                       |

| P14.3    | 19                 | 15      | AN/DIG_IN     |                                                                       |

| P14.4    | 18                 | 14      | AN/DIG_IN     |                                                                       |

| P14.5    | 17                 | 13      | AN/DIG_IN     |                                                                       |

| P14.6    | 16                 | 12      | AN/DIG_IN     |                                                                       |

| P14.7    | 15                 | 11      | AN/DIG_IN     |                                                                       |

| P14.8    | 24                 | 20      | AN/DAC/DIG_IN |                                                                       |

| -        |                    |         |               |                                                                       |

Subject to Agreement on the Use of Product Information

Table 11 Package Pin Mapping (cont'd)

| Function   | LQFP-64<br>TQFP-64 | VQFN-48 | Pad Type            | Notes                                                                                                                                                                      |

|------------|--------------------|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P14.9      | 23                 | 19      | AN/DAC/DIG_IN       |                                                                                                                                                                            |

| P14.14     | 14                 | -       | AN/DIG_IN           |                                                                                                                                                                            |

| USB_DP     | 7                  | 4       | special             |                                                                                                                                                                            |

| USB_DM     | 6                  | 3       | special             |                                                                                                                                                                            |

| HIB_IO_0   | 10                 | 7       | A1 special          | At the first power-up and with every reset of the hibernate domain this pin is configured as open-drain output and drives "0". As output the medium driver mode is active. |

| TCK        | 45                 | 34      | A1                  | Weak pull-down active.                                                                                                                                                     |

| TMS        | 44                 | 33      | A1+                 | Weak pull-up active. As output the strong-soft driver mode is active.                                                                                                      |

| PORST      | 43                 | 32      | special             | Strong pull-down controlled<br>by EVR.<br>Weak pull-up active while<br>strong pull-down is not active.                                                                     |

| XTAL1      | 39                 | 29      | clock_IN            |                                                                                                                                                                            |

| XTAL2      | 40                 | 30      | clock_O             |                                                                                                                                                                            |

| RTC_XTAL1  | 11                 | 8       | clock_IN            |                                                                                                                                                                            |

| RTC_XTAL2  | 12                 | 9       | clock_O             |                                                                                                                                                                            |

| VBAT       | 13                 | 10      | Power               | When VDDP is supplied VBAT has to be supplied as well.                                                                                                                     |

| VDDA/VAREF | 22                 | 18      | AN_Power/AN_<br>Ref | Shared analog supply and reference voltage pin.                                                                                                                            |

| VSSA/VAGND | 21                 | 17      | AN_Power/AN_<br>Ref | Shared analog supply and reference ground pin.                                                                                                                             |

| VDDC       | 9                  | 6       | Power               |                                                                                                                                                                            |

| VDDC       | 42                 | 31      | Power               |                                                                                                                                                                            |

| VDDP       | 8                  | 5       | Power               |                                                                                                                                                                            |

| VDDP       | 38                 | 28      | Power               |                                                                                                                                                                            |

| VDDP       | 56                 | 41      | Power               |                                                                                                                                                                            |

| VSS        | 37                 | 27      | Power               |                                                                                                                                                                            |

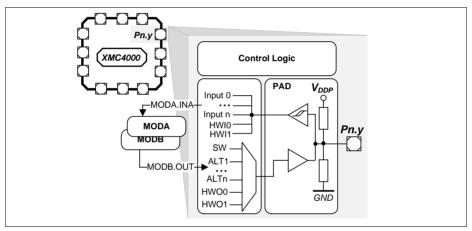

#### 2.2.2 Port I/O Functions

The following general scheme is used to describe each PORT pin:

Table 12 Port I/O Function Description

| Function |          | Outputs  |          | Inputs   |          |          |  |

|----------|----------|----------|----------|----------|----------|----------|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |

Figure 6 Simplified Port Structure

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to four alternate output functions (ALT1/2/3/4) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL it is possible to select between different hardware "masters" (HWO0/HWI0). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

Subject to Agreement on the Use of Product Information

The XMC4[12]00 has a common ground concept, all  $V_{\rm SS}$ ,  $V_{\rm SSA}$  and  $V_{\rm SSO}$  pins share the same ground potential. In packages with an exposed die pad it must be connected to the common ground as well.

There are no dedicated connections for the analog reference  $V_{\rm AREF}$  and  $V_{\rm AGND}$ . Instead, they share the same pins as the analog supply pins  $V_{\rm DDA}$  and  $V_{\rm SSA}$ . Some analog channels can optionally serve as "Alternate Reference"; further details on this operating mode are described in the Reference Manual.

When  $V_{\rm DDP}$  is supplied,  $V_{\rm BAT}$  must be supplied as well. If no other supply source (e.g. battery) is connected to  $V_{\rm BAT}$ , the  $V_{\rm BAT}$  pin can also be connected directly to  $V_{\rm DDP}$ .

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 15 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- · full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

Table 15 Overload Parameters

| Parameter                                                            | Symbol    |    |    | Values | 5    | Unit | Note /                                                |

|----------------------------------------------------------------------|-----------|----|----|--------|------|------|-------------------------------------------------------|

|                                                                      |           |    |    | Тур.   | Max. |      | Test Condition                                        |

| Input current on any port pin during overload condition              | $I_{OV}$  | SR | -5 | -      | 5    | mA   |                                                       |

| Absolute sum of all input circuit currents for one port              | $I_{OVG}$ | SR | _  | _      | 20   | mA   | $\Sigma  I_{\rm OVx} $ , for all $I_{\rm OVx} < 0$ mA |

| group during overload condition <sup>1)</sup>                        |           |    | _  | _      | 20   | mA   | $\Sigma  I_{\rm OVx} $ , for all $I_{\rm OVx} > 0$ mA |

| Absolute sum of all input circuit currents during overload condition | $I_{OVS}$ | SR | _  | _      | 80   | mA   | $\Sigma I_{OVG}$                                      |

<sup>1)</sup> The port groups are defined in Table 18.

**Figure 9** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\rm DDP}$  and ground are a simplified representation of these ESD protection structures.

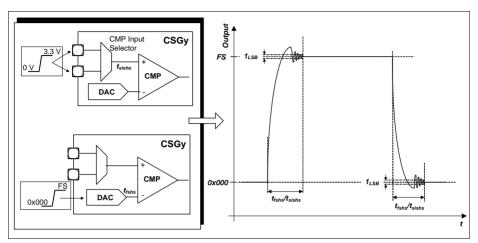

Figure 20 DAC and Input Selector Propagation Delay

#### 3.2.5.3 Clocks

#### **HRPWM DAC Conversion Clock**

The DAC conversion clock can be generated internally or it can be controlled via a HRPWM module pin.

Table 31 External DAC conversion trigger operating conditions

|           |                     |    | • •                    | •    | •                |     |                 |

|-----------|---------------------|----|------------------------|------|------------------|-----|-----------------|

| Parameter | Symb                | V  | alues                  | Unit | Note /           |     |                 |

|           |                     |    | Min.                   | Тур. | Max.             |     | Test Con dition |

| Frequency | $f_{etrg}$          | SR | _                      | _    | 30 <sup>2)</sup> | MHz |                 |

| ON time   | $t_{\text{onetrg}}$ | SR | $2T_{\rm ccu}^{-1)2)}$ | _    | _                | ns  |                 |

| OFF time  | $t_{ m offetrg}$    | SR | $2T_{\rm ccu}^{-1)2)}$ | _    | _                | ns  |                 |

<sup>1) 50%</sup> duty cycle is not obligatory

#### **CSG External Clock**

It is possible to select an external source, that can be used as a clock for the slope generation, HRPWMx.ECLKy. This clock is synchronized internally with the module clock and therefore the external clock needs to meet the criterion described on **Table 32**.

<sup>2)</sup> Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

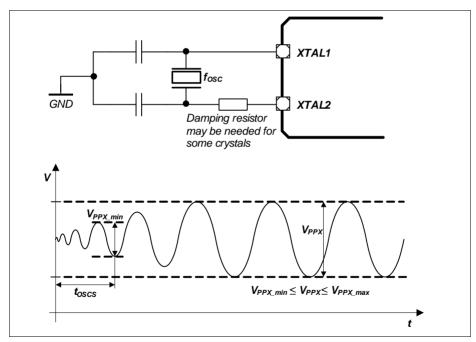

# 3.2.9 Oscillator Pins

Note: It is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimal parameters for the oscillator operation. Please refer to the limits specified by the crystal or ceramic resonator supplier.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

The oscillator pins can be operated with an external crystal (see Figure 21) or in direct input mode (see Figure 22).

Figure 21 Oscillator in Crystal Mode

# Table 38 Power Supply Parameters

| Parameter                                      | Symbol     |    |      | Value | s    | Unit   | Note /                                                                     |

|------------------------------------------------|------------|----|------|-------|------|--------|----------------------------------------------------------------------------|

|                                                |            |    | Min. | Тур.  | Max. |        | <b>Test Condition</b>                                                      |

| Power Dissipation                              | $P_{DISS}$ | CC | _    | -     | 1    | W      | $V_{\rm DDP} = 3.6 \text{ V},$<br>$T_{\rm J} = 150  ^{\circ}\text{C}$      |

| Wake-up time from Sleep to Active mode         | $t_{SSA}$  | СС | _    | 6     | _    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |            |    | -    | _     | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |            |    | _    | _     | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

- 1) CPU executing code from Flash, all peripherals idle.

- 2) CPU executing code from Flash. USB and CCU clock off.

- 3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPII} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 80 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

- The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\rm DDP}$  decreases typically by 3.5 mA when  $f_{\rm SYS}$  decreases by 10 MHz, at constant  $T_{\rm J}$

- 11) Sum of currents of all active converters (ADC and DAC)

Table 40 Flash Memory Parameters

| Parameter                                                                 | Symbol               | Values |      |      | Unit   | Note /                                                                                |

|---------------------------------------------------------------------------|----------------------|--------|------|------|--------|---------------------------------------------------------------------------------------|

|                                                                           |                      | Min.   | Тур. | Max. |        | Test Condition                                                                        |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC  | 20     | -    | -    | years  | Max. 4<br>erase/program<br>cycles per UCB                                             |

| Endurance on 64 Kbyte<br>Physical Sector PS4                              | N <sub>EPS4</sub> CC | 10000  | _    | -    | cycles | BA-marking<br>devices only!<br>Cycling<br>distributed over<br>life time <sup>5)</sup> |

In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

<sup>2)</sup> The following formula applies to the wait state configuration: FCON.WSPFLASH  $\times$  (1 /  $f_{CPU}$ )  $\geq t_a$ .

<sup>3)</sup> Storage and inactive time included.

<sup>4)</sup> Values given are valid for an average weighted junction temperature of  $T_J = 110$  °C.

Only valid with robust EEPROM emulation algorithm, equally cycling the logical sectors. For more details see

the Reference Manual.

Package and Reliability

# 4 Package and Reliability

The XMC4[12]00 is a member of the XMC4000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Die Pad may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

# 4.1 Package Parameters

**Table 55** provides the thermal characteristics of the packages used in XMC4[12]00. The availability of different packages for different markings is listed in **Table 2**.

Table 55 Thermal Characteristics of the Packages

| Parameter                              | Symbol              | Limit Values |                  | Unit | Package Types                                              |  |

|----------------------------------------|---------------------|--------------|------------------|------|------------------------------------------------------------|--|

|                                        |                     | Min. Max.    |                  |      |                                                            |  |

| Exposed Die Pad<br>Dimensions          | $Ex \times Ey$      | -            | $5.8 \times 5.8$ | mm   | PG-LQFP-64-19                                              |  |

|                                        | CC                  | -            | 5.7 × 5.7        | mm   | PG-TQFP-64-19                                              |  |

|                                        |                     | -            | 5.2 × 5.2        | mm   | PG-VQFN-48-53                                              |  |

|                                        |                     | -            | 5.2 × 5.2        | mm   | PG-VQFN-48-71                                              |  |

| Thermal resistance<br>Junction-Ambient | $R_{\Theta \sf JA}$ | -            | 30               | K/W  | PG-LQFP-64-19 <sup>1)</sup>                                |  |

|                                        | CC                  | -            | 23.4             | K/W  | PG-TQFP-64-19 <sup>1)</sup>                                |  |

|                                        |                     | -            | 34.8             | K/W  | PG-VQFN-48-53 <sup>1)</sup><br>PG-VQFN-48-71 <sup>1)</sup> |  |

<sup>1)</sup> Device mounted on a 4-layer JEDEC board (JESD 51-7) with thermal vias; exposed pad soldered.

Note: For electrical reasons, it is required to connect the exposed pad to the board ground  $V_{SS}$ , independent of EMC and thermal requirements.

#### 4.1.1 Thermal Considerations

When operating the XMC4[12]00 in a system, the total heat generated in the chip must be dissipated to the ambient environment to prevent overheating and the resulting thermal damage.

The maximum heat that can be dissipated depends on the package and its integration into the target board. The "Thermal resistance  $R_{\Theta,IA}$ " quantifies these parameters. The

www.infineon.com

Published by Infineon Technologies AG