Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                         |

| Core Processor            | ARM® Cortex®-M4                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| Speed                     | 80MHz                                                                            |

| Connectivity              | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals               | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| lumber of I/O             | 35                                                                               |

| Program Memory Size       | 256KB (256K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 40K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters           | A/D 16x12b; D/A 2x12b                                                            |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type             | Surface Mount                                                                    |

| Package / Case            | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package   | PG-LQFP-64-6                                                                     |

| urchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4200f64k256abxqsa1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Summary of Features**

Table 6 SRAM Memory Ranges

| Total SRAM Size | Program SRAM                                       | System Data SRAM                                   |

|-----------------|----------------------------------------------------|----------------------------------------------------|

| 40 Kbytes       | 1FFF C000 <sub>H</sub> –<br>1FFF FFFF <sub>H</sub> | 2000 0000 <sub>H</sub> –<br>2000 5FFF <sub>H</sub> |

| 20 Kbytes       | 1FFF E000 <sub>H</sub> –<br>1FFF FFFF <sub>H</sub> | 2000 0000 <sub>H</sub> –<br>2000 2FFF <sub>H</sub> |

Table 7 ADC Channels<sup>1)</sup>

| Package          | VADC G0     | VADC G1            |  |  |

|------------------|-------------|--------------------|--|--|

| LQFP-64, TQFP-64 | CH0, CH3CH7 | CH0, CH1, CH3, CH6 |  |  |

| PG-VQFN-48       | CH0, CH3CH7 | CH0, CH1, CH3      |  |  |

Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

# 1.6 Identification Registers

The identification registers allow software to identify the marking.

Table 8 XMC4200 Identification Registers

| Register Name | Value                  | Marking       |

|---------------|------------------------|---------------|

| SCU_IDCHIP    | 0004 2001 <sub>H</sub> | EES-AA, ES-AA |

| SCU_IDCHIP    | 0004 2002 <sub>H</sub> | ES-AB, AB     |

| SCU_IDCHIP    | 0004 2003 <sub>H</sub> | BA            |

| JTAG IDCODE   | 101D D083 <sub>H</sub> | EES-AA, ES-AA |

| JTAG IDCODE   | 201D D083 <sub>H</sub> | ES-AB, AB     |

| JTAG IDCODE   | 301D D083 <sub>H</sub> | ВА            |

## **Summary of Features**

Table 9 XMC4100 Identification Registers

| Register Name | Value                  | Marking       |

|---------------|------------------------|---------------|

| SCU_IDCHIP    | 0004 2001 <sub>H</sub> | EES-AA, ES-AA |

| SCU_IDCHIP    | 0004 2002 <sub>H</sub> | ES-AB, AB     |

| SCU_IDCHIP    | 0004 1003 <sub>H</sub> | BA            |

| JTAG IDCODE   | 101D D083 <sub>H</sub> | EES-AA, ES-AA |

| JTAG IDCODE   | 201D D083 <sub>H</sub> | ES-AB, AB     |

| JTAG IDCODE   | 301D D083 <sub>H</sub> | ВА            |

#### **General Device Information**

## 2.2.1 Package Pin Summary

The following general scheme is used to describe each pin:

Table 10 Package Pin Mapping Description

| Function | Package A | Package B |  | Pad<br>Type | Notes |

|----------|-----------|-----------|--|-------------|-------|

| Name     | N         | Ax        |  | A1+         |       |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the dedicated pins (i.e. PORST) and supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type (A1, A1+, special=special pad, In=input pad, AN/DIG\_IN=analog and digital input, Power=power supply). Details about the pad properties are defined in the Electrical Parameters.

In the "Notes", special information to the respective pin/function is given, i.e. deviations from the default configuration after reset. Per default the regular Port pins are configured as direct input with no internal pull device active.

Table 11 Package Pin Mapping

| Function | LQFP-64<br>TQFP-64 | VQFN-48 | Pad Type | Notes                                                                                                   |

|----------|--------------------|---------|----------|---------------------------------------------------------------------------------------------------------|

| P0.0     | 2                  | 2       | A1+      |                                                                                                         |

| P0.1     | 1                  | 1       | A1+      |                                                                                                         |

| P0.2     | 64                 | 48      | A1+      |                                                                                                         |

| P0.3     | 63                 | 47      | A1+      |                                                                                                         |

| P0.4     | 62                 | 46      | A1+      |                                                                                                         |

| P0.5     | 61                 | 45      | A1+      |                                                                                                         |

| P0.6     | 60                 | 44      | A1+      |                                                                                                         |

| P0.7     | 58                 | 43      | A1+      | After a system reset, via HWSEL this pin selects the DB.TDI function.                                   |

| P0.8     | 57                 | 42      | A1+      | After a system reset, via  HWSEL this pin selects the  DB.TRST function, with a  weak pull-down active. |

| P0.9     | 4                  | -       | A1+      |                                                                                                         |

| P0.10    | 3                  | -       | A1+      |                                                                                                         |

#### **General Device Information**

#### 2.2.2 Port I/O Functions

The following general scheme is used to describe each PORT pin:

Table 12 Port I/O Function Description

| Function |          | Outputs  |          | Inputs   |          |          |  |

|----------|----------|----------|----------|----------|----------|----------|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |

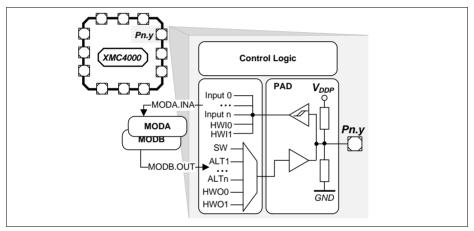

Figure 6 Simplified Port Structure

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to four alternate output functions (ALT1/2/3/4) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL it is possible to select between different hardware "masters" (HWO0/HWI0). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

Subject to Agreement on the Use of Product Information

# XMC4100 / XMC4200 XMC4000 Family

Infineon

Port I/O Functions (CONt'd) Table 13

| Function |                  | Output           |                 |                  |                      |                   | Input            |                 |              |              |                 |                 |                |                |

|----------|------------------|------------------|-----------------|------------------|----------------------|-------------------|------------------|-----------------|--------------|--------------|-----------------|-----------------|----------------|----------------|

|          | ALT1             | ALT2             | ALT3            | ALT4             | HWO0                 | HWI0              | Input            | Input           | Input        | Input        | Input           | Input           | Input          | Input          |

| P1.8     |                  | U0C0.<br>SELO1   |                 | U1C1.<br>SCLKOUT |                      |                   |                  |                 |              |              |                 |                 |                |                |

| P1.9     | U0C0.<br>SCLKOUT |                  |                 | U1C1.<br>DOUT0   |                      |                   |                  |                 |              |              |                 |                 |                |                |

| P1.15    | SCU.<br>EXTCLK   |                  |                 | U1C0.<br>DOUT0   |                      |                   |                  |                 |              | ERU1.<br>1A0 |                 |                 |                |                |

| P2.0     | CAN.<br>N0_TXD   |                  |                 | LEDTS0.<br>COL1  |                      |                   |                  |                 | ERU0.<br>0B3 |              | CCU40.<br>IN1C  |                 |                |                |

| P2.1     |                  |                  |                 | LEDTS0.<br>COL0  | DB.TDO/<br>TRACESWO  |                   |                  |                 |              | ERU1.<br>0B0 | CCU40.<br>INOC  |                 |                |                |

| P2.2     | VADC.<br>EMUX00  |                  | CCU41.<br>OUT3  | LEDTS0.<br>LINE0 | LEDTS0.<br>EXTENDED0 | LEDTS0.<br>TSIN0A |                  | U0C1.<br>DX0A   | ERU0.<br>1B2 |              | CCU41.<br>IN3A  |                 |                |                |

| P2.3     | VADC.<br>EMUX01  | U0C1.<br>SELO0   | CCU41.<br>OUT2  | LEDTS0.<br>LINE1 | LEDTS0.<br>EXTENDED1 | LEDTS0.<br>TSIN1A |                  | U0C1.<br>DX2A   | ERU0.<br>1A2 |              | CCU41.<br>IN2A  |                 |                |                |

| P2.4     | VADC.<br>EMUX02  | U0C1.<br>SCLKOUT | CCU41.<br>OUT1  | LEDTS0.<br>LINE2 | LEDTS0.<br>EXTENDED2 | LEDTS0.<br>TSIN2A |                  | U0C1.<br>DX1A   | ERU0.<br>0B2 |              | CCU41.<br>IN1A  | HRPWM0.<br>BL1A |                |                |

| P2.5     |                  | U0C1.<br>DOUT0   | CCU41.<br>OUT0  | LEDTS0.<br>LINE3 | LEDTS0.<br>EXTENDED3 | LEDTS0.<br>TSIN3A |                  | U0C1.<br>DX0B   | ERU0.<br>0A2 |              | CCU41.<br>INOA  | HRPWM0.<br>BL2A |                |                |

| P2.6     |                  |                  | CCU80.<br>OUT13 | LEDTS0.<br>COL3  |                      |                   |                  | CAN.<br>N1_RXDA | ERU0.<br>1B3 |              | CCU40.<br>IN3C  |                 |                |                |

| P2.7     |                  | CAN.<br>N1_TXD   | CCU80.<br>OUT03 | LEDTS0.<br>COL2  |                      |                   |                  |                 |              | ERU1.<br>1B0 | CCU40.<br>IN2C  |                 |                |                |

| P2.8     |                  |                  | CCU80.<br>OUT32 | LEDTS0.<br>LINE4 | LEDTS0.<br>EXTENDED4 | LEDTS0.<br>TSIN4A | DAC.<br>TRIGGER5 |                 |              |              | CCU40.<br>IN0B  | CCU40.<br>IN1B  | CCU40.<br>IN2B | CCU40.<br>IN3B |

| P2.9     |                  |                  | CCU80.<br>OUT22 | LEDTS0.<br>LINE5 | LEDTS0.<br>EXTENDED5 | LEDTS0.<br>TSIN5A | DAC.<br>TRIGGER4 |                 |              |              | CCU41.<br>IN0B  | CCU41.<br>IN1B  | CCU41.<br>IN2B | CCU41.<br>IN3B |

| P2.14    | VADC.<br>EMUX11  | U1C0.<br>DOUT0   | CCU80.<br>OUT21 |                  |                      |                   |                  | U1C0.<br>DX0D   |              |              |                 |                 |                |                |

| P2.15    | VADC.<br>EMUX12  |                  | CCU80.<br>OUT11 | LEDTS0.<br>LINE6 | LEDTS0.<br>EXTENDED6 | LEDTS0.<br>TSIN6A |                  | U1C0.<br>DX0C   |              |              |                 |                 |                |                |

| P3.0     |                  | U0C1.<br>SCLKOUT |                 |                  |                      |                   | U0C1.<br>DX1B    |                 |              |              | CCU80.<br>IN2C  |                 |                |                |

| P14.0    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH0   |                 |              |              |                 |                 |                |                |

| P14.3    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH3   | VADC.<br>G1CH3  |              |              | CAN.<br>N0_RXDB |                 |                |                |

| P14.4    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH4   |                 |              |              |                 |                 |                |                |

| P14.5    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH5   |                 |              |              | POSIF0.<br>IN2B |                 |                |                |

| P14.6    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH6   |                 |              |              | POSIF0.<br>IN1B |                 | G0ORC6         |                |

| 214.7    |                  |                  |                 |                  |                      |                   | VADC.<br>G0CH7   |                 |              |              | POSIF0.<br>IN0B |                 |                |                |

| 14.8     |                  |                  |                 |                  | DAC.<br>OUT_0        |                   |                  | VADC.<br>G1CH0  |              |              |                 |                 |                |                |

#### 2.3 Power Connection Scheme

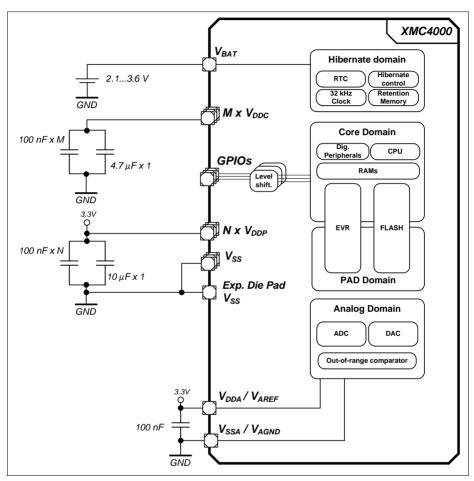

Figure 7. shows a reference power connection scheme for the XMC4[12]00.

Figure 7 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 4.7uF capacitor to the  $V_{\rm DDC}$  nets.

## 3 Electrical Parameters

#### 3.1 General Parameters

### 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4[12]00 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with an two-letter abbreviation in column "Symbol":

- CC

- Such parameters indicate Controller Characteristics, which are a distinctive feature of the XMC4[12]00 and must be regarded for system design.

- SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC4[12]00 is designed in.

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 15 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- · full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{DDP}$  or  $V_{DDA}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

Table 15 Overload Parameters

| Parameter                                                            | Syml      | Symbol |      | Values | 5    | Unit | Note /                                                |

|----------------------------------------------------------------------|-----------|--------|------|--------|------|------|-------------------------------------------------------|

|                                                                      |           |        | Min. | Тур.   | Max. |      | Test Condition                                        |

| Input current on any port pin during overload condition              | $I_{OV}$  | SR     | -5   | -      | 5    | mA   |                                                       |

| Absolute sum of all input circuit currents for one port              | $I_{OVG}$ | SR     | _    | _      | 20   | mA   | $\Sigma  I_{\rm OVx} $ , for all $I_{\rm OVx} < 0$ mA |

| group during overload condition <sup>1)</sup>                        |           |        | _    | _      | 20   | mA   | $\Sigma  I_{\rm OVx} $ , for all $I_{\rm OVx} > 0$ mA |

| Absolute sum of all input circuit currents during overload condition | $I_{OVS}$ | SR     | _    | _      | 80   | mA   | $\Sigma I_{OVG}$                                      |

<sup>1)</sup> The port groups are defined in Table 18.

Figure 9 shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\rm DDP}$  and ground are a simplified representation of these ESD protection structures.

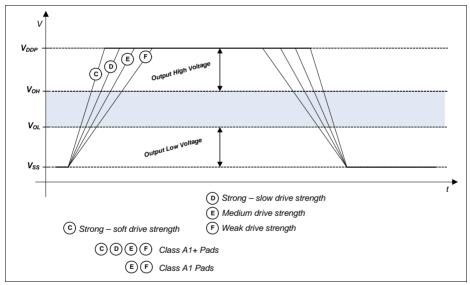

# 3.1.4 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and its basic characteristics. More details (mainly DC parameters) are defined in the **Section 3.2.1**.

Table 19 Pad Driver and Pad Classes Overview

| Class | Power<br>Supply  | Туре          | Sub-Class                 | Speed<br>Grade | Load   | Termination                    |

|-------|------------------|---------------|---------------------------|----------------|--------|--------------------------------|

| Α     | 3.3 V LVTTL I/O, |               | A1<br>(e.g. GPIO)         | 6 MHz          | 100 pF | No                             |

|       |                  | LVTTL outputs | A1+<br>(e.g. serial I/Os) | 25 MHz         | 50 pF  | Series termination recommended |

Figure 10 Output Slopes with different Pad Driver Modes

Figure 10 is a qualitative display of the resulting output slope performance with different output driver modes. The detailed input and output characteristics are listed in Section 3.2.1.

#### 3.2 DC Parameters

## 3.2.1 Input/Output Pins

The digital input stage of the shared analog/digital input pins is identical to the input stage of the standard digital input/output pins.

The pull-up characteristics ( $I_{\rm PUH}$ ) and the input high and low voltage levels ( $V_{\rm IH}$  and  $V_{\rm IL}$ ) of the PORST pin are identical to the respective values of the standard digital input/output pins.

Table 21 Standard Pad Parameters

| Parameter                                                | Symbol                  | Va                               | alues | Unit | Note / Test Condition                  |

|----------------------------------------------------------|-------------------------|----------------------------------|-------|------|----------------------------------------|

|                                                          |                         | Min.                             | Max.  |      |                                        |

| Pin capacitance (digital inputs/outputs)                 | $C_{IO}CC$              | _                                | 10    | pF   |                                        |

| Pull-down current                                        | $ I_{PDL} $             | 150                              | _     | μΑ   | $^{1)}V_{IN} \geq 0.6 	imes V_{DDP}$   |

|                                                          | SR                      | _                                | 10    | μΑ   | $^{2)}V_{IN} \leq 0.36 \times V_{DDP}$ |

| Pull-up current                                          | $ I_{\mathrm{PUH}} $ SR | _                                | 10    | μΑ   | $^{2)}V_{IN} \geq 0.6 	imes V_{DDP}$   |

|                                                          |                         | 100                              | _     | μΑ   | $^{1)}V_{IN} \leq 0.36 \times V_{DDP}$ |

| Input Hysteresis for pads of all A classes <sup>3)</sup> | HYSA<br>CC              | 0.1 ×<br><i>V</i> <sub>DDP</sub> | -     | V    |                                        |

| PORST spike filter always blocked pulse duration         | t <sub>SF1</sub> CC     | _                                | 10    | ns   |                                        |

| PORST spike filter pass-through pulse duration           | t <sub>SF2</sub> CC     | 100                              | -     | ns   |                                        |

| PORST pull-down current                                  | $ I_{\rm PPD} $ CC      | 13                               | -     | mA   | V <sub>i</sub> = 1.0 V                 |

Current required to override the pull device with the opposite logic level ("force current").

With active pull device, at load currents between force and keep current the input state is undefined.

Load current at which the pull device still maintains the valid logic level ("keep current").

With active pull device, at load currents between force and keep current the input state is undefined.

<sup>3)</sup> Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It can not be guaranteed that it suppresses switching due to external system noise.

Table 23 Standard Pads Class\_A1+

| Parameter                  | Symbol               | Va                     | lues | Unit | Note /                                                         |

|----------------------------|----------------------|------------------------|------|------|----------------------------------------------------------------|

|                            |                      | Min.                   | Max. |      | Test Condition                                                 |

| Output high voltage,       | $V_{OHA1+}$          | $V_{DDP}$ - 0.4        | _    | V    | $I_{OH} \geq$ -400 $\muA$                                      |

| POD <sup>1)</sup> = weak   | CC                   | 2.4                    | -    | V    | $I_{OH} \ge$ -500 μA                                           |

| Output high voltage,       |                      | V <sub>DDP</sub> - 0.4 | -    | V    | $I_{OH} \geq$ -1.4 mA                                          |

| POD <sup>1)</sup> = medium |                      | 2.4                    | _    | V    | $I_{OH} \ge$ -2 mA                                             |

| Output high voltage,       |                      | $V_{DDP}$ - 0.4        | _    | V    | $I_{\mathrm{OH}} \geq$ -1.4 mA                                 |

| POD <sup>1)</sup> = strong |                      | 2.4                    | _    | V    | $I_{OH} \ge$ -2 mA                                             |

| Output low voltage         | $V_{OLA1+}$          | _                      | 0.4  | V    | $I_{OL} \le 500 \mu A;$<br>POD <sup>1)</sup> = weak            |

|                            |                      | _                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium       |

|                            |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong       |

| Fall time                  | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_L = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak             |

|                            |                      | -                      | 50   | ns   | $C_L = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium           |

|                            |                      | _                      | 28   | ns   | $C_{L}$ = 50 pF;<br>POD <sup>1)</sup> = strong;<br>edge = slow |

|                            |                      | _                      | 16   | ns   | $C_L$ = 50 pF;<br>POD <sup>1)</sup> = strong;<br>edge = soft;  |

| Rise time                  | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_L = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak             |

|                            |                      | -                      | 50   | ns   | $C_L = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium           |

|                            |                      | _                      | 28   | ns   | $C_{L}$ = 50 pF;<br>POD <sup>1)</sup> = strong;<br>edge = slow |

|                            |                      | _                      | 16   | ns   | $C_L$ = 50 pF;<br>POD <sup>1)</sup> = strong;<br>edge = soft   |

<sup>1)</sup> POD = Pin Out Driver

Table 27

DAC Parameters (Operating Conditions apply) (cont'd)

| Parameter                       | Symbo                | Symbol |      | Values | 3    | Unit | Note /                                                  |

|---------------------------------|----------------------|--------|------|--------|------|------|---------------------------------------------------------|

|                                 |                      |        | Min. | Тур.   | Max. |      | Test Condition                                          |

| Offset error                    | $ED_{OFF}$           | CC     |      | ±20    |      | mV   |                                                         |

| Gain error                      | $ED_{G\_IN}$         | CC     | -5   | 0      | 5    | %    |                                                         |

| Startup time                    | t <sub>STARTU</sub>  | -CC    | _    | 15     | 30   | μS   | time from output<br>enabling till code<br>valid ±16 LSB |

| 3dB Bandwidth of Output Buffer  | $f_{C1}$             | СС     | 2.5  | 5      | _    | MHz  | verified by design                                      |

| Output sourcing current         | I <sub>OUT_SO</sub>  | URCE   | _    | -30    | _    | mA   |                                                         |

| Output sinking current          | I <sub>OUT_SIN</sub> | IK     | _    | 0.6    | _    | mA   |                                                         |

| Output resistance               | $R_{OUT}$            | CC     | -    | 50     | _    | Ohm  |                                                         |

| Load resistance                 | $R_{L}$              | SR     | 5    | -      | -    | kOhm |                                                         |

| Load capacitance                | $C_{L}$              | SR     | -    | -      | 50   | pF   |                                                         |

| Signal-to-Noise<br>Ratio        | SNR                  | СС     | _    | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |

| Total Harmonic<br>Distortion    | THD                  | CC     | _    | 70     | _    | dB   | examination<br>bandwidth < 25 kHz                       |

| Power Supply<br>Rejection Ratio | PSRR                 | СС     | _    | 56     | _    | dB   | to $V_{\rm DDA}$ verified by design                     |

<sup>1)</sup> According to best straight line method.

#### **Conversion Calculation**

Unsigned:

$\mathsf{DACxDATA} = 4095 \times (V_{\mathsf{OUT}} - V_{\mathsf{OUT}\ \mathsf{MIN}}) \, / \, (V_{\mathsf{OUT}\ \mathsf{MAX}} - V_{\mathsf{OUT}\ \mathsf{MIN}})$

Signed:

$\mathsf{DACxDATA} = 4095 \times (V_\mathsf{OUT} - V_\mathsf{OUT\_MIN}) \, / \, (V_\mathsf{OUT\_MAX} - V_\mathsf{OUT\_MIN}) \, - \, 2048$

Table 32 External clock operating conditions

| Parameter | Symbol                 |                        | Value | Unit                 | Note / |                              |

|-----------|------------------------|------------------------|-------|----------------------|--------|------------------------------|

|           |                        | Min.                   | Тур.  | Max.                 |        | Test Con dition              |

| Frequency | $f_{ m eclk}$ SR       | _                      | _     | $f_{\text{hrpwm}}/4$ | MHz    |                              |

| ON time   | t <sub>oneclk</sub> SR | $2T_{\rm ccu}^{-1)2)}$ | _     | _                    | ns     |                              |

| OFF time  | $t_{ m offeclk}$ SR    | $2T_{\rm ccu}^{-1)2)}$ | _     | _                    | ns     | Only the rising edge is used |

<sup>1) 50%</sup> duty cycle is not obligatory

## 3.2.6 Low Power Analog Comparator (LPAC)

The Low Power Analog Comparator (LPAC) triggers a wake-up event from Hibernate state or an interrupt trigger during normal operation. It does so by comparing  $V_{\rm BAT}$  or another external sensor voltage  $V_{\rm LPS}$  with a pre-programmed threshold voltage.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 33 Low Power Analog Comparator Parameters

| Parameter                                                  | Symbol                |      | Values | }    | Unit | Note /                                  |

|------------------------------------------------------------|-----------------------|------|--------|------|------|-----------------------------------------|

|                                                            |                       | Min. | Тур.   | Max. |      | Test Condition                          |

| $V_{\mathrm{BAT}}$ supply voltage range for LPAC operation | $V_{BAT}$ SR          | 2.1  | _      | 3.6  | V    |                                         |

| Sensor voltage range                                       | $V_{LPCS}$            | 0    | _      | 1.2  | V    |                                         |

| Threshold step size                                        | $V_{th}$ CC           | _    | 18.75  | _    | mV   |                                         |

| Threshold trigger accuracy                                 | $\varDelta V_{th}$ CC | _    | -      | ±10  | %    | for $V_{\text{th}}$ > 0.4 V             |

| Conversion time                                            | $t_{LPCC}$ CC         | _    | _      | 250  | μS   |                                         |

| Average current consumption over time                      | I <sub>LPCAC</sub> CC | _    | _      | 15   | μΑ   | conversion interval 10 ms <sup>1)</sup> |

| Current consumption during conversion                      | $I_{LPCC}$ CC         | _    | 150    | _    | μΑ   | 1)                                      |

<sup>1)</sup> Single channel conversion, measuring  $V_{\rm BAT}$  = 3.3 V, 8 cycles settling time

<sup>2)</sup> Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

Table 36 OSC\_XTAL Parameters

| Parameter                                               | ameter Symbol Values    |                  |      | Unit                   | Note / |                                   |  |

|---------------------------------------------------------|-------------------------|------------------|------|------------------------|--------|-----------------------------------|--|

|                                                         |                         | Min.             | Тур. | Max.                   |        | Test Condition                    |  |

| Input frequency                                         | $f_{ m OSC}{ m SR}$     | 4                | _    | 40                     | MHz    | Direct Input Mode selected        |  |

|                                                         |                         | 4                | _    | 25                     | MHz    | External Crystal<br>Mode selected |  |

| Oscillator start-up time <sup>1)2)</sup>                | t <sub>OSCS</sub><br>CC | _                | _    | 10                     | ms     |                                   |  |

| Input voltage at XTAL1                                  | $V_{IX}$ SR             | -0.5             | _    | V <sub>DDP</sub> + 0.5 | V      |                                   |  |

| Input amplitude (peak-to-peak) at XTAL1 <sup>2)3)</sup> | $V_{PPX}SR$             | $V_{\text{DDP}}$ | _    | V <sub>DDP</sub> + 1.0 | V      |                                   |  |

| Input high voltage at XTAL1 <sup>4)</sup>               | $V_{IHBX}SR$            | 1.0              | _    | V <sub>DDP</sub> + 0.5 | V      |                                   |  |

| Input low voltage at XTAL1 <sup>4)</sup>                | $V_{ILBX}SR$            | -0.5             | _    | 0.4                    | V      |                                   |  |

| Input leakage current at XTAL1                          | I <sub>ILX1</sub> CC    | -100             | _    | 100                    | nA     |                                   |  |

<sup>1)</sup>  $t_{\rm OSCS}$  is defined from the moment the oscillator is enabled wih SCU\_OSCHPCTRL.MODE until the oscillations reach an amplitude at XTAL1 of 0.4  $^*$   $V_{\rm DDP}$ .

<sup>2)</sup> The external oscillator circuitry must be optimized by the customer and checked for negative resistance and amplitude as recommended and specified by crystal suppliers.

<sup>3)</sup> If the shaper unit is enabled and not bypassed.

<sup>4)</sup> If the shaper unit is bypassed, dedicated DC-thresholds have to be met.

## Table 38 Power Supply Parameters

| Parameter                                      | Symb       | Symbol |      | Value | s    | Unit   | Note /                                                                     |

|------------------------------------------------|------------|--------|------|-------|------|--------|----------------------------------------------------------------------------|

|                                                |            |        | Min. | Тур.  | Max. |        | Test Condition                                                             |

| Power Dissipation                              | $P_{DISS}$ | CC     | _    | -     | 1    | W      | $V_{\rm DDP} = 3.6 \text{ V},$<br>$T_{\rm J} = 150  ^{\circ}\text{C}$      |

| Wake-up time from Sleep to Active mode         | $t_{SSA}$  | CC     | _    | 6     | _    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |            |        | -    | _     | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |            |        | _    | _     | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

- 1) CPU executing code from Flash, all peripherals idle.

- 2) CPU executing code from Flash. USB and CCU clock off.

- 3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPII} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 80 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

- The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\rm DDP}$  decreases typically by 3.5 mA when  $f_{\rm SYS}$  decreases by 10 MHz, at constant  $T_{\rm J}$

- 11) Sum of currents of all active converters (ADC and DAC)

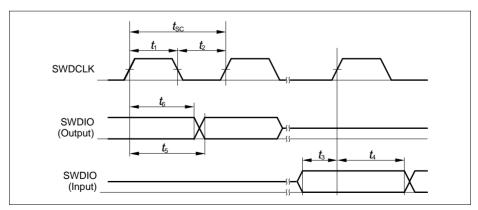

# 3.3.7 Serial Wire Debug Port (SW-DP) Timing

The following parameters are applicable for communication through the SW-DP interface.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Note: Operating conditions apply.

Table 47

SWD Interface Timing Parameters (Operating Conditions apply)

| Parameter                                      |                       | nbol |      | Values | 3      | Unit | Note /                 |

|------------------------------------------------|-----------------------|------|------|--------|--------|------|------------------------|

|                                                |                       |      | Min. | Тур.   | Max.   |      | Test Condition         |

| SWDCLK clock period                            | $t_{SC}$              | SR   | 25   | _      | _      | ns   | C <sub>L</sub> = 30 pF |

|                                                |                       |      | 40   | -      | _      | ns   | C <sub>L</sub> = 50 pF |

| SWDCLK high time                               | $t_1$                 | SR   | 10   | -      | 500000 | ns   |                        |

| SWDCLK low time                                | $t_2$                 | SR   | 10   | -      | 500000 | ns   |                        |

| SWDIO input setup to SWDCLK rising edge        | <i>t</i> <sub>3</sub> | SR   | 6    | _      | _      | ns   |                        |

| SWDIO input hold after SWDCLK rising edge      | $t_4$                 | SR   | 6    | -      | _      | ns   |                        |

| SWDIO output valid time                        | $t_5$                 | CC   | _    | -      | 17     | ns   | C <sub>L</sub> = 50 pF |

| after SWDCLK rising edge                       |                       |      | _    | -      | 13     | ns   | C <sub>L</sub> = 30 pF |

| SWDIO output hold time from SWDCLK rising edge | <i>t</i> <sub>6</sub> | CC   | 3    | -      | _      | ns   |                        |

Figure 30 SWD Timing

Subject to Agreement on the Use of Product Information

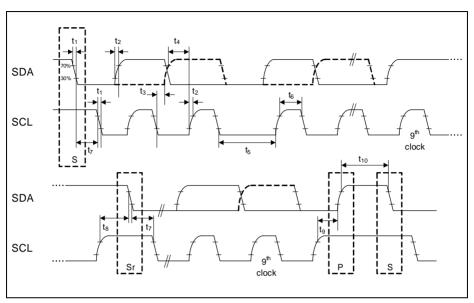

Figure 32 USIC IIC Stand and Fast Mode Timing

# 3.3.8.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode.

Note: Operating Conditions apply.

Table 52 USIC IIS Master Transmitter Timing

| Parameter       | Symbol            |            | Values | 3          | Unit | Note /         |

|-----------------|-------------------|------------|--------|------------|------|----------------|

|                 |                   | Min.       | Тур.   | Max.       |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3       | -      | _          | ns   |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x     | _      | _          | ns   |                |

|                 |                   | $t_{1min}$ |        |            |      |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x     | _      | _          | ns   |                |

|                 |                   | $t_{1min}$ |        |            |      |                |

| Hold time       | t <sub>4</sub> CC | 0          | _      | _          | ns   |                |

| Clock rise time | t <sub>5</sub> CC | -          | _      | 0.15 x     | ns   |                |

|                 |                   |            |        | $t_{1min}$ |      |                |

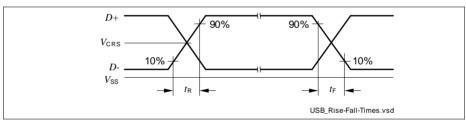

## 3.3.9 USB Interface Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

Table 54

USB Timing Parameters (operating conditions apply)

| Parameter               | Symbol                |    |      | Value | s      | Unit | Note /                 |

|-------------------------|-----------------------|----|------|-------|--------|------|------------------------|

|                         |                       |    | Min. | Тур.  | Max.   |      | Test Condition         |

| Rise time               | $t_{R}$               | CC | 4    | _     | 20     | ns   | $C_L = 50 \text{ pF}$  |

| Fall time               | $t_{F}$               | CC | 4    | _     | 20     | ns   | $C_L = 50 \text{ pF}$  |

| Rise/Fall time matching | $t_{\rm R}/t_{\rm F}$ | CC | 90   | -     | 111.11 | %    | C <sub>L</sub> = 50 pF |

| Crossover voltage       | $V_{CRS}$             | CC | 1.3  | _     | 2.0    | V    | C <sub>L</sub> = 50 pF |

Figure 35 USB Signal Timing

## Package and Reliability

# 4.2 Package Outlines

The availability of different packages for different devices types is listed in **Table 1**, specific packages for different device markings are listed in **Table 2**.

The exposed die pad dimensions are listed in Table 55.

Table 56 Differences PG-LQFP-64-19 to PG-TQFP-64-19

| Change                                                | PG-LQFP-64-19           | PG-TQFP-64-19           |

|-------------------------------------------------------|-------------------------|-------------------------|

| Thermal Resistance Junction Ambient $(R_{\Theta JA})$ | 30 K/W                  | 23.4 K/W                |

| Package thickness                                     | 1.4 <sup>±0.05</sup> mm | 1.0 <sup>±0.05</sup> mm |

|                                                       | 1.6 mm MAX              | 1.2 mm MAX              |

| Exposed Die Pad size                                  | 5.8 mm × 5.8 mm         | 5.7 mm × 5.7 mm         |

## **Quality Declarations**

# 5 Quality Declarations

The qualification of the XMC4[12]00 is executed according to the JEDEC standard JESD47H.

Note: For automotive applications refer to the Infineon automotive microcontrollers.

**Table 58** Quality Parameters

| Parameter                                                        | Symbol                 |      | Values | 3     | Unit | Note /                                                   |

|------------------------------------------------------------------|------------------------|------|--------|-------|------|----------------------------------------------------------|

|                                                                  |                        | Min. | Тур.   | Max.  |      | Test Condition                                           |

| Operation lifetime                                               | t <sub>OP</sub> CC     | 20   | _      | -     | а    | $T_{\rm J} \le 109 ^{\rm o}{\rm C},$ device permanent on |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)     | V <sub>HBM</sub><br>SR | _    | _      | 2 000 | V    | EIA/JESD22-<br>A114-B                                    |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) | $V_{CDM}$ SR           | _    | _      | 500   | V    | Conforming to<br>JESD22-C101-C                           |

| Moisture sensitivity level                                       | MSL<br>CC              | _    | -      | 3     | _    | JEDEC<br>J-STD-020D                                      |

| Soldering temperature                                            | T <sub>SDR</sub><br>SR | _    | _      | 260   | °C   | Profile according to JEDEC J-STD-020D                    |