Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                         |

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 40K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | PG-VQFN-48-53                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4200q48f256abxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2015-10 Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XMC4100 / XMC4200

Microcontroller Series for Industrial Applications

XMC4000 Family

ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit processor core

Data Sheet V1.3 2015-10

# Microcontrollers

#### XMC4[12]00 Data Sheet

| Revision  | History: V1.3 2015-10                                                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Versions:                                                                                                                                                        |

| V1.2 201  |                                                                                                                                                                  |

| V1.1 201  |                                                                                                                                                                  |

| V1.0 201  |                                                                                                                                                                  |

| V0.6 201  | 2-11                                                                                                                                                             |

| Page      | Subjects                                                                                                                                                         |

| 12        | Added a section listing the packages of the different markings.                                                                                                  |

| 14        | Added BA marking variant.                                                                                                                                        |

| 14        | Corrected SCU_IDCHIP value of XMC4100 EES-AA/ES-AA.                                                                                                              |

| 36        | Added footnote explaining minimum $V_{\text{BAT}}$ requirements to start the hibernate domain and/or oscillation of a crystal on RTC_XTAL.                       |

| 37        | Changed pull device definition to System Requirement (SR) to reflect that the specified currents are defined by the characteristics of the external load/driver. |

| 37        | Added information that PORST Pull-up is identical to the pull-up on standard I/O pins.                                                                           |

| 42        | Updated $C_{\text{AINSW}}$ , $C_{\text{AINTOT}}$ and $R_{\text{AIN}}$ parameters with improved values.                                                           |

| <b>56</b> | Added footnote on test configuration for LPAC measurement.                                                                                                       |

| 58        | Corrected parameter name of of USB pull device (upstream port receiving) definition according to USB standard (referenced to DM instead of DP)                   |

| 62        | Relaxed RTC_XTAL $V_{\rm PPX}$ parameter value and changed it to a system requirement.                                                                           |

| 66        | Added footnote on current consumption by enabling of $f_{CCU}$ .                                                                                                 |

| 67        | Added Flash endurance parameter for 64 Kbytes Physical Sector PS4 $N_{\rm EPS4}$ for devices with BA marking.                                                    |

| many      | Added PG-TQFP-64-19 and PG-VQFN-48-71 package information.                                                                                                       |

| 89, 91    | Added tables describing the differences between PG-LQFP-64-19 to PG-<br>TQFP-64-19 as well as PG-VQFN-48-53 to PG-VQFN-48-71 packages.                           |

| 93        | Updated to JEDEC standard J-STD-020D for the moisture sensitivity level and added solder temperature parameter according to the same standard.                   |

#### **Summary of Features**

# 1 Summary of Features

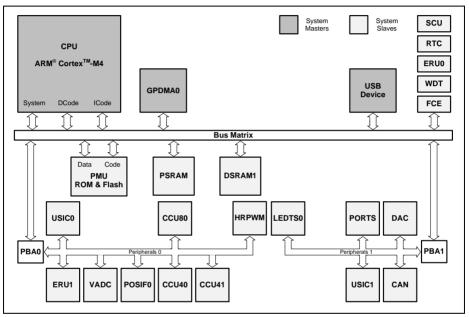

The XMC4[12]00 devices are members of the XMC4000 Family of microcontrollers based on the ARM Cortex-M4 processor core. The XMC4000 is a family of high performance and energy efficient microcontrollers optimized for Industrial Connectivity, Industrial Control, Power Conversion, Sense & Control.

Figure 1 System Block Diagram

#### **CPU Subsystem**

- CPU Core

- High Performance 32-bit ARM Cortex-M4 CPU

- 16-bit and 32-bit Thumb2 instruction set

- DSP/MAC instructions

- System timer (SysTick) for Operating System support

- Floating Point Unit

- Memory Protection Unit

- Nested Vectored Interrupt Controller

- One General Purpose DMA with up-to 8 channels

- Event Request Unit (ERU) for programmable processing of external and internal service requests

9

• Flexible CRC Engine (FCE) for multiple bit error detection

Data Sheet

#### **General Device Information**

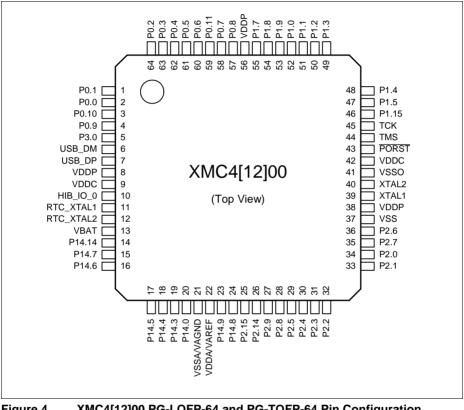

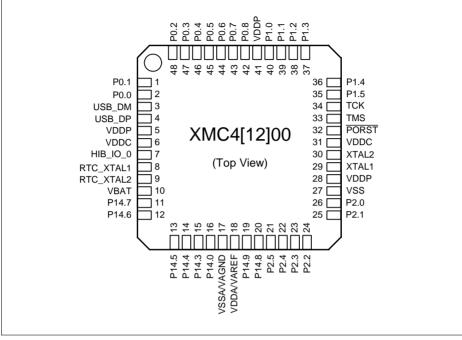

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

#### Figure 4 XMC4[12]00 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

# XMC4100 / XMC4200 XMC4000 Family

#### **General Device Information**

Figure 5 XMC4[12]00 PG-VQFN-48 Pin Configuration (top view)

# XMC4100 / XMC4200 XMC4000 Family

#### **General Device Information**

| Table 11   | Package Pin Mapping (cont'd) |    |                     |                                                                                                                                                                                              |  |  |  |  |  |  |

|------------|------------------------------|----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Function   | LQFP-64 VQFN-48<br>TQFP-64   |    | Pad Type            | Notes                                                                                                                                                                                        |  |  |  |  |  |  |

| P14.9      | 23                           | 19 | AN/DAC/DIG_IN       |                                                                                                                                                                                              |  |  |  |  |  |  |

| P14.14     | 14                           | -  | AN/DIG_IN           |                                                                                                                                                                                              |  |  |  |  |  |  |

| USB_DP     | 7                            | 4  | special             |                                                                                                                                                                                              |  |  |  |  |  |  |

| USB_DM     | 6                            | 3  | special             |                                                                                                                                                                                              |  |  |  |  |  |  |

| HIB_IO_0   | 10                           | 7  | A1 special          | At the first power-up and with<br>every reset of the hibernate<br>domain this pin is configured<br>as open-drain output and<br>drives "0".<br>As output the medium driver<br>mode is active. |  |  |  |  |  |  |

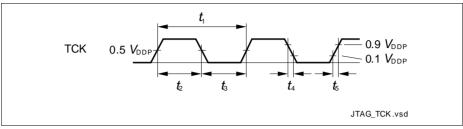

| тск        | 45                           | 34 | A1                  | Weak pull-down active.                                                                                                                                                                       |  |  |  |  |  |  |

| TMS        | 44                           | 33 | A1+                 | Weak pull-up active.<br>As output the strong-soft<br>driver mode is active.                                                                                                                  |  |  |  |  |  |  |

| PORST      | 43                           | 32 | special             | Strong pull-down controlled<br>by EVR.<br>Weak pull-up active while<br>strong pull-down is not active.                                                                                       |  |  |  |  |  |  |

| XTAL1      | 39                           | 29 | clock_IN            |                                                                                                                                                                                              |  |  |  |  |  |  |

| XTAL2      | 40                           | 30 | clock_O             |                                                                                                                                                                                              |  |  |  |  |  |  |

| RTC_XTAL1  | 11                           | 8  | clock_IN            |                                                                                                                                                                                              |  |  |  |  |  |  |

| RTC_XTAL2  | 12                           | 9  | clock_O             |                                                                                                                                                                                              |  |  |  |  |  |  |

| VBAT       | 13                           | 10 | Power               | When VDDP is supplied<br>VBAT has to be supplied as<br>well.                                                                                                                                 |  |  |  |  |  |  |

| VDDA/VAREF | 22                           | 18 | AN_Power/AN_<br>Ref | Shared analog supply and reference voltage pin.                                                                                                                                              |  |  |  |  |  |  |

| VSSA/VAGND | 21                           | 17 | AN_Power/AN_<br>Ref | Shared analog supply and reference ground pin.                                                                                                                                               |  |  |  |  |  |  |

| VDDC       | 9                            | 6  | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

| VDDC       | 42                           | 31 | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

| VDDP       | 8                            | 5  | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

| VDDP       | 38                           | 28 | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

| VDDP       | 56                           | 41 | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

| VSS        | 37                           | 27 | Power               |                                                                                                                                                                                              |  |  |  |  |  |  |

#### Table 11 Package Pin Mapping (cont'd)

# 3 Electrical Parameters

## 3.1 General Parameters

#### 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4[12]00 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with an two-letter abbreviation in column "Symbol":

• CC

Such parameters indicate Controller Characteristics, which are a distinctive feature of the XMC4[12]00 and must be regarded for system design.

• SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC4[12]00 is designed in.

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symb                    | ol |      | Va   | lues                                  | Unit | Note /                |

|------------------------------------------------------------------------------------------------------------------------|-------------------------|----|------|------|---------------------------------------|------|-----------------------|

|                                                                                                                        |                         |    | Min. | Тур. | Max.                                  |      | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$            | SR | -65  | -    | 150                                   | °C   | -                     |

| Junction temperature                                                                                                   | TJ                      | SR | -40  | _    | 150                                   | °C   | -                     |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$               | SR | -    | -    | 4.3                                   | V    | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>         | SR | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\text{AGND}}$                                                      | $V_{AIN}$<br>$V_{AREF}$ | SR | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Input current on any pin during overload condition                                                                     | I <sub>IN</sub>         | SR | -10  | -    | +10                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$     | SR | -25  | -    | +25                                   | mA   |                       |

| Absolute maximum sum of all input circuit currents during overload condition                                           | $\Sigma I_{\rm IN}$     | SR | -100 | -    | +100                                  | mA   |                       |

#### Table 14 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 18**.

# 3.1.4 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and its basic characteristics. More details (mainly DC parameters) are defined in the Section 3.2.1.

| Table 19 Pad Driver and Pad | Classes Overview |

|-----------------------------|------------------|

|-----------------------------|------------------|

| Class | Power<br>Supply | Туре             | Sub-Class                 | Speed<br>Grade | Load   | Termination                    |

|-------|-----------------|------------------|---------------------------|----------------|--------|--------------------------------|

| Α     | 3.3 V           | LVTTL<br>I/O,    | <b>A1</b><br>(e.g. GPIO)  | 6 MHz          | 100 pF | No                             |

| _     |                 | LVTTL<br>outputs | A1+<br>(e.g. serial I/Os) | 25 MHz         | 50 pF  | Series termination recommended |

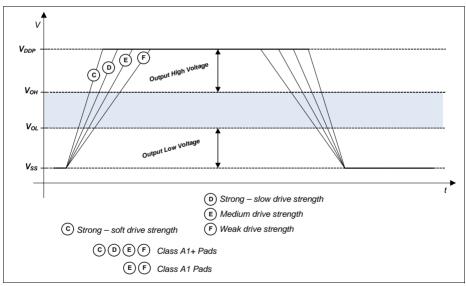

Figure 10 Output Slopes with different Pad Driver Modes

Figure 10 is a qualitative display of the resulting output slope performance with different output driver modes. The detailed input and output characteristics are listed in Section 3.2.1.

35

#### Table 23 Standard Pads Class\_A1+

| Parameter            | Symbol                   | Va                     | lues | Unit | Note /                                                                  |  |

|----------------------|--------------------------|------------------------|------|------|-------------------------------------------------------------------------|--|

|                      |                          | Min.                   | Max. |      | Test Condition                                                          |  |

| Output high voltage, | V <sub>OHA1+</sub>       | V <sub>DDP</sub> - 0.4 | -    | V    | $I_{OH} \ge$ -400 $\mu$ A                                               |  |

| $POD^{1)} = weak$    | CC                       | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |  |

| Output high voltage, |                          | V <sub>DDP</sub> - 0.4 | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |  |

| $POD^{1)} = medium$  |                          | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -2 mA                                          |  |

| Output high voltage, |                          | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -1.4 mA                                        |  |

| $POD^{1)} = strong$  |                          | 2.4                    | -    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |  |

| Output low voltage   | V <sub>OLA1+</sub><br>CC | -                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |  |

|                      |                          | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |  |

|                      |                          | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |  |

| Fall time            | t <sub>FA1+</sub> CC     | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |  |

|                      |                          | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |  |

|                      |                          | _                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |  |

|                      |                          | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |  |

| Rise time            | t <sub>RA1+</sub> CC     | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |  |

|                      |                          | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |  |

|                      |                          | -                      | 28   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = strong;<br>edge = slow      |  |

|                      |                          | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |  |

1) POD = Pin Out Driver

| Parameter                                                                       | Symbol                     |      | Value | S     | Unit | Note /                                                                                          |

|---------------------------------------------------------------------------------|----------------------------|------|-------|-------|------|-------------------------------------------------------------------------------------------------|

|                                                                                 |                            | Min. | Тур.  | Max.  |      | Test Condition                                                                                  |

| Total capacitance of the alternate reference inputs <sup>5)</sup>               | C <sub>AREFTOT</sub><br>CC | -    | 20    | 40    | pF   |                                                                                                 |

| Total Unadjusted Error                                                          | TUE CC                     | -6   | -     | 6     | LSB  | 12-bit resolution;                                                                              |

| Differential Non-Linearity<br>Error <sup>8)</sup>                               | EA <sub>DNL</sub><br>CC    | -4.5 | -     | 4.5   | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                       |

| Gain Error <sup>8)</sup>                                                        | EA <sub>GAIN</sub><br>CC   | -6   | -     | 6     | LSB  |                                                                                                 |

| Integral Non-Linearity <sup>8)</sup>                                            | EA <sub>INL</sub> CC       | -4.5 | -     | 4.5   | LSB  |                                                                                                 |

| Offset Error <sup>8)</sup>                                                      | EA <sub>OFF</sub><br>CC    | -6   | -     | 6     | LSB  |                                                                                                 |

| Worst case ADC $V_{\text{DDA}}$<br>power supply current per<br>active converter | I <sub>DDAA</sub><br>CC    | -    | 1.5   | 2     | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 ^{\circ}\text{C}$ |

| Charge consumption on alternate reference per conversion <sup>5)</sup>          | $Q_{\rm CONV}$             | -    | 30    | -     | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9}$                                                              |

| ON resistance of the analog input path                                          | R <sub>AIN</sub> CC        | -    | 600   | 1 200 | Ohm  |                                                                                                 |

| ON resistance for the ADC test (pull down for AIN7)                             | R <sub>AIN7T</sub><br>CC   | 180  | 550   | 900   | Ohm  |                                                                                                 |

#### Table 25 ADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 14).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

43

8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

| Parameter                         | Symbol                      | Symbol |      | Values | 5    | Unit | Note /                                                  |

|-----------------------------------|-----------------------------|--------|------|--------|------|------|---------------------------------------------------------|

|                                   |                             |        | Min. | Тур.   | Max. |      | Test Condition                                          |

| Offset error                      | ED <sub>OFF</sub>           | СС     |      | ±20    |      | mV   |                                                         |

| Gain error                        | ED <sub>G_IN</sub> C        | CC     | -5   | 0      | 5    | %    |                                                         |

| Startup time                      | t <sub>STARTUP</sub>        | СС     | _    | 15     | 30   | μs   | time from output<br>enabling till code<br>valid ±16 LSB |

| 3dB Bandwidth of<br>Output Buffer | f <sub>C1</sub>             | СС     | 2.5  | 5      | -    | MHz  | verified by design                                      |

| Output sourcing current           | I <sub>OUT_SOUL</sub><br>CC | RCE    | -    | -30    | -    | mA   |                                                         |

| Output sinking current            | I <sub>OUT_SINK</sub><br>CC |        | -    | 0.6    | -    | mA   |                                                         |

| Output resistance                 | R <sub>OUT</sub> 0          | CC     | -    | 50     | -    | Ohm  |                                                         |

| Load resistance                   | R <sub>L</sub> S            | SR     | 5    | -      | -    | kOhm |                                                         |

| Load capacitance                  | $C_{L}$                     | SR     | -    | -      | 50   | pF   |                                                         |

| Signal-to-Noise<br>Ratio          | SNR (                       | CC     | -    | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |

| Total Harmonic<br>Distortion      | THD (                       | CC     | -    | 70     | -    | dB   | examination<br>bandwidth < 25 kHz                       |

| Power Supply<br>Rejection Ratio   | PSRR C                      | CC     | -    | 56     | -    | dB   | to $V_{\rm DDA}$ verified by design                     |

#### Table 27 DAC Parameters (Operating Conditions apply) (cont'd)

1) According to best straight line method.

#### **Conversion Calculation**

$\begin{array}{l} \text{Unsigned:} \\ \text{DACxDATA} = 4095 \times (V_{\text{OUT}} \text{ - } V_{\text{OUT\_MIN}}) \ / \ (V_{\text{OUT\_MAX}} \text{ - } V_{\text{OUT\_MIN}}) \\ \text{Signed:} \\ \text{DACxDATA} = 4095 \times (V_{\text{OUT}} \text{ - } V_{\text{OUT\_MIN}}) \ / \ (V_{\text{OUT\_MAX}} \text{ - } V_{\text{OUT\_MIN}}) \ - \ 2048 \\ \end{array}$

# XMC4100 / XMC4200 XMC4000 Family

#### **Electrical Parameters**

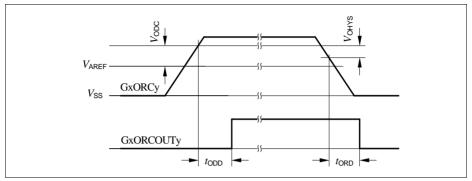

Figure 16 GxORCOUTy Trigger Generation

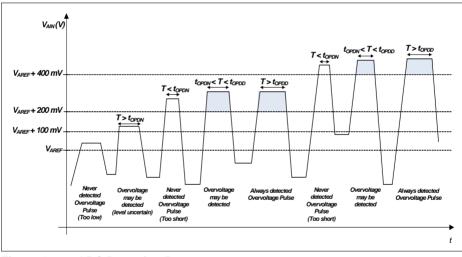

Figure 17 ORC Detection Ranges

# 3.2.10 Power Supply Current

The total power supply current defined below consists of a leakage and a switching component.

Application relevant values are typically lower than those given in the following tables, and depend on the customer's system operating conditions (e.g. thermal connection or used application configurations).

If not stated otherwise, the operating conditions for the parameters in the following table are:

$V_{\text{DDP}}$  = 3.3 V,  $T_{\text{A}}$  = 25 °C

| Parameter                                                                                           | Symbol            |    |      | Values | 5    | Unit | Note /         |

|-----------------------------------------------------------------------------------------------------|-------------------|----|------|--------|------|------|----------------|

|                                                                                                     |                   |    | Min. | Тур.   | Max. |      | Test Condition |

| Active supply current <sup>1)</sup>                                                                 | $I_{\rm DDPA}$    | CC | -    | 80     | -    | mA   | 80 / 80 / 80   |

| Peripherals enabled                                                                                 |                   |    | -    | 75     | -    |      | 80 / 40 / 40   |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz                                                      |                   |    | -    | 73     | -    |      | 40 / 40 / 80   |

| JCPU' JPERIPH' JCCU III WII IZ                                                                      |                   |    | -    | 59     | -    |      | 24 / 24 / 24   |

|                                                                                                     |                   |    | -    | 50     | -    |      | 1/1/1          |

| Active supply current                                                                               | $I_{\rm DDPA}$    | CC | -    | 24     | -    | mA   | 80 / 80 / 80   |

| Code execution from RAM<br>Flash in Sleep mode<br>Frequency:<br>$f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz |                   |    | _    | 19     | -    |      | 80 / 40 / 40   |

| Active supply current <sup>2)</sup>                                                                 | I <sub>DDPA</sub> | CC | -    | 63     | -    | mA   | 80 / 80 / 80   |

| Peripherals disabled<br>Frequency:<br>$f_{CPU}/f_{PERIPH}$ in MHz                                   |                   |    | -    | 62     | -    | -    | 80 / 40 / 40   |

|                                                                                                     |                   |    | -    | 60     | -    |      | 40 / 40 / 80   |

|                                                                                                     |                   |    | -    | 54     | -    |      | 24 / 24 / 24   |

|                                                                                                     |                   |    | -    | 50     | -    |      | 1/1/1          |

| Table 38 | Power Supply | Parameters |

|----------|--------------|------------|

|----------|--------------|------------|

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Symbol           |    |      | Values | 5    | Unit   | Note /<br>Test Condition                                                   |  |

|------------------------------------------------|------------------|----|------|--------|------|--------|----------------------------------------------------------------------------|--|

|                                                |                  |    | Min. | Тур.   | Max. | -      |                                                                            |  |

| Power Dissipation                              | $P_{DISS}$       | СС | -    | -      | 1    | W      | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C                       |  |

| Wake-up time from Sleep to Active mode         | t <sub>SSA</sub> | СС | -    | 6      | -    | cycles |                                                                            |  |

| Wake-up time from Deep<br>Sleep to Active mode |                  |    | -    | -      | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |  |

| Wake-up time from<br>Hibernate mode            |                  |    | -    | -      | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |  |

#### Table 38 Power Supply Parameters

1) CPU executing code from Flash, all peripherals idle.

2) CPU executing code from Flash. USB and CCU clock off.

3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPU} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 80 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\text{DDP}}$  decreases typically by 3.5 mA when  $f_{\text{SYS}}$  decreases by 10 MHz, at constant  $T_{\text{J}}$

- 11) Sum of currents of all active converters (ADC and DAC)

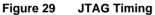

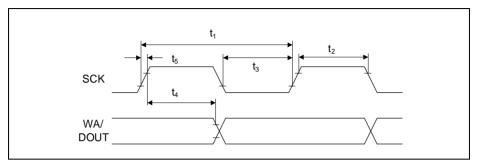

# 3.3.8.2 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode. *Note: Operating Conditions apply.*

| Table 50 | USIC IIC | Standard | Mode | Timing <sup>1)</sup> |

|----------|----------|----------|------|----------------------|

|----------|----------|----------|------|----------------------|

| Parameter                                              | Symbol                   | Values |      |      | Unit | Note /         |

|--------------------------------------------------------|--------------------------|--------|------|------|------|----------------|

|                                                        |                          | Min.   | Тур. | Max. |      | Test Condition |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | -      | -    | 300  | ns   |                |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | -      | -    | 1000 | ns   |                |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0      | -    | -    | μs   |                |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 250    | -    | -    | ns   |                |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 4.7    | -    | -    | μs   |                |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 4.0    | -    | -    | μs   |                |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 4.7    | -    | -    | μs   |                |

| Capacitive load for each bus line                      | $C_{\rm b}{\rm SR}$      | -      | -    | 400  | pF   |                |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

# Figure 32 USIC IIC Stand and Fast Mode Timing

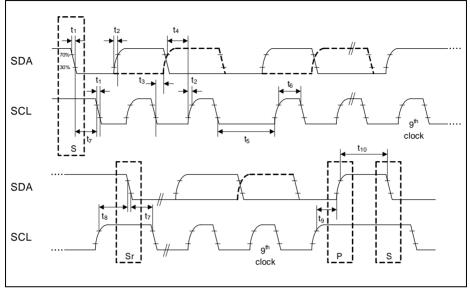

# 3.3.8.3 Inter-IC Sound (IIS) Interface Timing

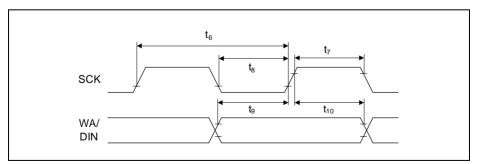

The following parameters are applicable for a USIC channel operated in IIS mode. *Note: Operating Conditions apply.*

| Table 52 | USIC IIS Master | <b>Transmitter Timing</b> |

|----------|-----------------|---------------------------|

|----------|-----------------|---------------------------|

| Parameter       | Symbol            | Values            |      |                   | Unit | Note /         |

|-----------------|-------------------|-------------------|------|-------------------|------|----------------|

|                 |                   | Min.              | Тур. | Max.              |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 33.3              | -    | -                 | ns   |                |

| Clock high time | t <sub>2</sub> CC | 0.35 x            | -    | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |      |                   |      |                |

| Clock low time  | t <sub>3</sub> CC | 0.35 x            | _    | -                 | ns   |                |

|                 |                   | t <sub>1min</sub> |      |                   |      |                |

| Hold time       | t <sub>4</sub> CC | 0                 | -    | -                 | ns   |                |

| Clock rise time | t <sub>5</sub> CC | -                 | -    | 0.15 x            | ns   |                |

|                 |                   |                   |      | t <sub>1min</sub> |      |                |

| Figure 33 | USIC IIS Master | Transmitter Timing |  |

|-----------|-----------------|--------------------|--|

|-----------|-----------------|--------------------|--|

| Table 53 USIC IIS S | lave Receiver Timing |

|---------------------|----------------------|

|---------------------|----------------------|

| Parameter       | Symbol                    | Values                      |      |      | Unit | Note /         |

|-----------------|---------------------------|-----------------------------|------|------|------|----------------|

|                 |                           | Min.                        | Тур. | Max. | 1    | Test Condition |

| Clock period    | t <sub>6</sub> SR         | 66.6                        | _    | -    | ns   |                |

| Clock high time | t <sub>7</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Clock low time  | t <sub>8</sub> SR         | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Set-up time     | t <sub>9</sub> SR         | 0.2 x<br>t <sub>6min</sub>  | _    | -    | ns   |                |

| Hold time       | <i>t</i> <sub>10</sub> SR | 0                           | -    | -    | ns   |                |

Figure 34 USIC IIS Slave Receiver Timing