Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                           |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 40K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                    |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | PG-VQFN-48-71                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4200q48f256baxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

$\mathsf{ARM}^{\texttt{®}}, \, \mathsf{ARM} \, \mathsf{Powered}^{\texttt{®}}, \, \mathsf{Cortex}^{\texttt{®}}, \, \mathsf{Thumb}^{\texttt{B}} \, \mathsf{and} \, \, \mathsf{AMBA}^{\texttt{B}} \, \mathsf{are} \, \, \mathsf{registered} \, \, \mathsf{trademarks} \, \, \mathsf{of} \, \, \mathsf{ARM}, \, \mathsf{Limited}.$

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

Synopsys<sup>™</sup> is a trademark of Synopsys, Inc.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

### Summary of Features

### **On-Chip Memories**

- 16 KB on-chip boot ROM

- up to 16 KB on-chip high-speed program memory

- up to 24 KB on-chip high speed data memory

- up to 256 KB on-chip Flash Memory with 1 KB instruction cache

## **Communication Peripherals**

- Universal Serial Bus, USB 2.0 device, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with two nodes, 64 message objects (MO), data rate up to 1 MBit/s

- Four Universal Serial Interface Channels (USIC), providing four serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

## **Analog Frontend Peripherals**

- Two Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Digital-Analog Converter (DAC) with two channels of 12-bit resolution

### **Industrial Control Peripherals**

- Two Capture/Compare Units 4 (CCU4) for use as general purpose timers

- One Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four High Resoultion PWM (HRPWM) channels

- One Position Interface (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

### Input/Output Lines

- Programmable port driver control module (PORTS)

- Individual bit addressability

- Tri-stated in input mode

- Push/pull or open drain output mode

- Boundary scan test support over JTAG interface

### **On-Chip Debug Support**

- Full support for debug features: 8 breakpoints, CoreSight, trace

- Various interfaces: ARM-JTAG, SWD, single wire trace

# XMC4100 / XMC4200 XMC4000 Family

### **General Device Information**

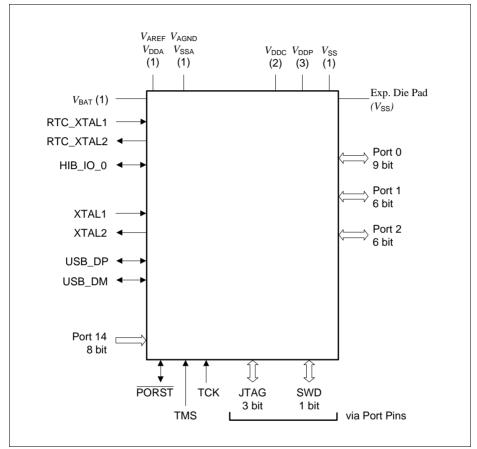

Figure 3 XMC4[12]00 Logic Symbol PG-VQFN-48

### **General Device Information**

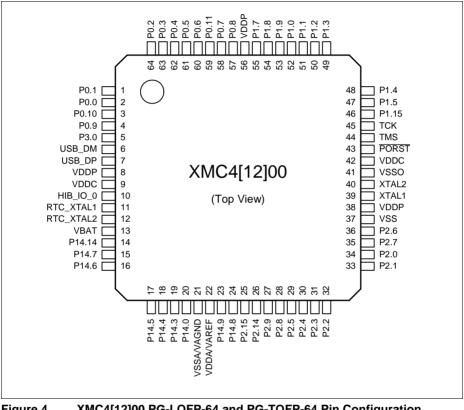

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

### Figure 4 XMC4[12]00 PG-LQFP-64 and PG-TQFP-64 Pin Configuration (top view)

# XMC4100 / XMC4200 XMC4000 Family

### **General Device Information**

| Table 11 | Package Pi         | n Mapping (co | ont'd)        |                                                                             |

|----------|--------------------|---------------|---------------|-----------------------------------------------------------------------------|

| Function | LQFP-64<br>TQFP-64 | VQFN-48       | Pad Type      | Notes                                                                       |

| P0.11    | 59                 | -             | A1+           |                                                                             |

| P1.0     | 52                 | 40            | A1+           |                                                                             |

| P1.1     | 51                 | 39            | A1+           |                                                                             |

| P1.2     | 50                 | 38            | A1+           |                                                                             |

| P1.3     | 49                 | 37            | A1+           |                                                                             |

| P1.4     | 48                 | 36            | A1+           |                                                                             |

| P1.5     | 47                 | 35            | A1+           |                                                                             |

| P1.7     | 55                 | -             | A1+           |                                                                             |

| P1.8     | 54                 | -             | A1+           |                                                                             |

| P1.9     | 53                 | -             | A1+           |                                                                             |

| P1.15    | 46                 | -             | A1+           |                                                                             |

| P2.0     | 34                 | 26            | A1+           |                                                                             |

| P2.1     | 33                 | 25            | A1+           | After a system reset, via<br>HWSEL this pin selects the<br>DB.TDO function. |

| P2.2     | 32                 | 24            | A1+           |                                                                             |

| P2.3     | 31                 | 23            | A1+           |                                                                             |

| P2.4     | 30                 | 22            | A1+           |                                                                             |

| P2.5     | 29                 | 21            | A1+           |                                                                             |

| P2.6     | 36                 | -             | A1+           |                                                                             |

| P2.7     | 35                 | -             | A1+           |                                                                             |

| P2.8     | 28                 | -             | A1+           |                                                                             |

| P2.9     | 27                 | -             | A1+           |                                                                             |

| P2.14    | 26                 | -             | A1+           |                                                                             |

| P2.15    | 25                 | -             | A1+           |                                                                             |

| P3.0     | 5                  | -             | A1+           |                                                                             |

| P14.0    | 20                 | 16            | AN/DIG_IN     |                                                                             |

| P14.3    | 19                 | 15            | AN/DIG_IN     |                                                                             |

| P14.4    | 18                 | 14            | AN/DIG_IN     |                                                                             |

| P14.5    | 17                 | 13            | AN/DIG_IN     |                                                                             |

| P14.6    | 16                 | 12            | AN/DIG_IN     |                                                                             |

| P14.7    | 15                 | 11            | AN/DIG_IN     |                                                                             |

| P14.8    | 24                 | 20            | AN/DAC/DIG_IN |                                                                             |

## Table 11 Package Pin Mapping (cont'd)

### **General Device Information**

| Function | LQFP-64<br>TQFP-64 | VQFN-48  | Pad Type | Notes                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSSO     | 41                 | -        | Power    |                                                                                                                                                                                                                                                                                                                                |

| VSS      | Exp. Pad           | Exp. Pad | Power    | Exposed Die Pad<br>The exposed die pad is<br>connected internally to VSS.<br>For proper operation, it is<br>mandatory to connect the<br>exposed pad directly to the<br>common ground on the<br>board.<br>For thermal aspects, please<br>refer to the Data Sheet.<br>Board layout examples are<br>given in an application note. |

### Table 11 Package Pin Mapping (cont'd)

# 3 Electrical Parameters

# 3.1 General Parameters

### 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4[12]00 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with an two-letter abbreviation in column "Symbol":

• CC

Such parameters indicate Controller Characteristics, which are a distinctive feature of the XMC4[12]00 and must be regarded for system design.

• SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC4[12]00 is designed in.

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 15 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload parameters, then the parameters functionality of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

| Parameter                                                                  | Symbol           |    |    | Values | 5    | Unit | Note /                                                |  |

|----------------------------------------------------------------------------|------------------|----|----|--------|------|------|-------------------------------------------------------|--|

|                                                                            |                  |    |    | Тур.   | Max. |      | <b>Test Condition</b>                                 |  |

| Input current on any port pin<br>during overload condition                 | I <sub>OV</sub>  | SR | -5 | -      | 5    | mA   |                                                       |  |

| Absolute sum of all input circuit currents for one port                    | I <sub>OVG</sub> | SR | -  | -      | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} < 0 \text{ mA}$ |  |

| group during overload condition <sup>1)</sup>                              |                  |    | -  | -      | 20   | mA   | $\Sigma  I_{OVx} $ , for all $I_{OVx} > 0 \text{ mA}$ |  |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> | SR | -  | -      | 80   | mA   | ΣI <sub>OVG</sub>                                     |  |

### Table 15 Overload Parameters

1) The port groups are defined in **Table 18**.

**Figure 9** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

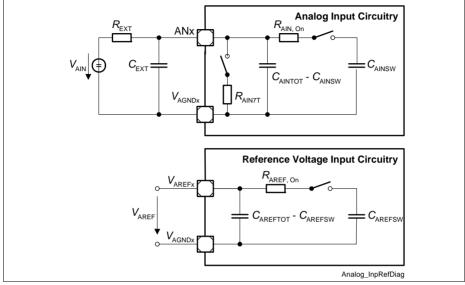

The power-up calibration of the ADC requires a maximum number of 4 352  $f_{ADCI}$  cycles.

Figure 13 ADCx Input Circuits

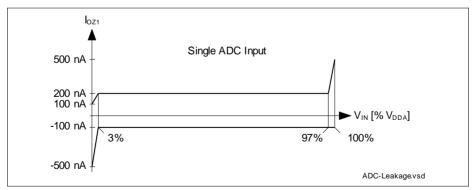

Figure 14 ADCx Analog Input Leakage Current

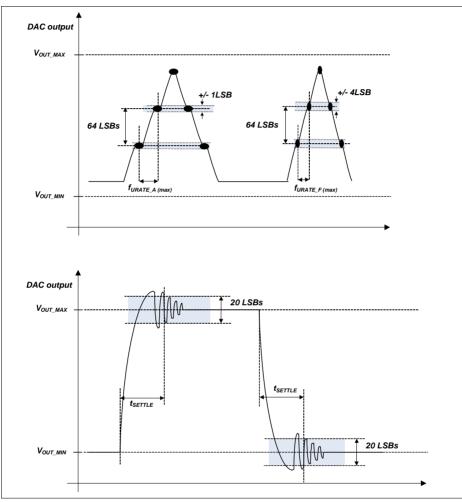

Figure 15 DAC Conversion Examples

# 3.2.5 High Resolution PWM (HRPWM)

The following chapters describe the operating conditions, characteristics and timing requirements, for all the components inside the HRPWM module. Each description is given for just one sub unit, e.g., one CSG or one HRC.

All the timing information is related to the module clock,  $f_{hrowm}$ .

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# 3.2.5.1 HRC characteristics

Table 29 summarizes the characteristics of the HRC units.

| Table 29 | HRC characteristics (Operating Conditi | ons apply) |

|----------|----------------------------------------|------------|

|----------|----------------------------------------|------------|

| Parameter                                 | Symbol                | Values |      |      | Unit | Note /         |

|-------------------------------------------|-----------------------|--------|------|------|------|----------------|

|                                           |                       | Min.   | Тур. | Max. |      | Test Condition |

| High resolution step size <sup>1)2)</sup> | t <sub>HRS</sub> CC   | -      | 150  | -    | ps   |                |

| Startup time (after reset release)        | t <sub>start</sub> CC | -      | -    | 2    | μS   |                |

1) The step size for clock frequencies equal to 180, 120 and 80 MHz is 150 ps.

The step size for clock frequencies different from 180, 120 and 80 MHz but within the range from 180 to 64 MHz can be between 118 to 180 ps (fixed over process and operating conditions)

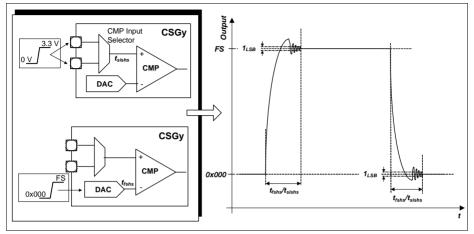

# 3.2.5.2 CMP and 10-bit DAC characteristics

The Table 30 summarizes the characteristics of the CSG unit.

The specified characteristics require that the setup of the HRPWM follows the initialization sequence as documented in the Reference Manual.

| Table 30 | <b>CMP and 10-bit DAC characteristics</b> (Operating Conditions apply) |

|----------|------------------------------------------------------------------------|

|----------|------------------------------------------------------------------------|

| Parameter                     | Symbol    |      | Values | 5    | Unit | Note /                                         |  |

|-------------------------------|-----------|------|--------|------|------|------------------------------------------------|--|

|                               |           | Min. | Тур.   | Max. |      | Test Condition                                 |  |

| DAC Resolution                | RES<br>CC |      | 10     |      | bits |                                                |  |

| DAC differential nonlinearity | DNL<br>CC | -1   | -      | 1.5  | LSB  | Monotonic<br>behavior,<br>See <b>Figure 18</b> |  |

| DAC integral nonlinearity     | INL CC    | -3   | -      | 3    | LSB  | See Figure 18                                  |  |

# 3.2.5.3 Clocks

### **HRPWM DAC Conversion Clock**

The DAC conversion clock can be generated internally or it can be controlled via a HRPWM module pin.

| Table 31 External DAC conversion trigger operating conditions |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Parameter | Symbol                  |                                   | Values | Unit             | Note / |                    |

|-----------|-------------------------|-----------------------------------|--------|------------------|--------|--------------------|

|           |                         | Min.                              | Тур.   | Max.             |        | Test Con<br>dition |

| Frequency | $f_{\rm etrg}$ SR       | _                                 | -      | 30 <sup>2)</sup> | MHz    |                    |

| ON time   | t <sub>onetrg</sub> SR  | 2T <sub>ccu</sub> <sup>1)2)</sup> | _      | -                | ns     |                    |

| OFF time  | t <sub>offetrg</sub> SR | 2T <sub>ccu</sub> <sup>1)2)</sup> | -      | -                | ns     |                    |

1) 50% duty cycle is not obligatory

2) Only valid if the signal was not previously synchronized/generated with the fccu clock (or a synchronous clock)

### CSG External Clock

It is possible to select an external source, that can be used as a clock for the slope generation, HRPWMx.ECLKy. This clock is synchronized internally with the module clock and therefore the external clock needs to meet the criterion described on Table 32.

# 3.2.8 USB Device Interface DC Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Condition                                           | /)               |    |        |      |       |      |                                  |

|-----------------------------------------------------|------------------|----|--------|------|-------|------|----------------------------------|

| Parameter                                           | Symbol           |    | Values |      |       | Unit | Note /                           |

|                                                     |                  |    | Min.   | Тур. | Max.  |      | Test Condition                   |

| Input low voltage                                   | $V_{IL}$         | SR | -      | -    | 0.8   | V    |                                  |

| Input high voltage<br>(driven)                      | $V_{IH}$         | SR | 2.0    | -    | -     | V    |                                  |

| Input high voltage<br>(floating) <sup>1)</sup>      | $V_{IHZ}$        | SR | 2.7    | -    | 3.6   | V    |                                  |

| Differential input sensitivity                      | $V_{DIS}$        | СС | 0.2    | -    | -     | V    |                                  |

| Differential common mode range                      | $V_{\rm CM}$     | СС | 0.8    | -    | 2.5   | V    |                                  |

| Output low voltage                                  | $V_{OL}$         | СС | 0.0    | -    | 0.3   | V    | 1.5 kOhm pull-<br>up to 3.6 V    |

| Output high voltage                                 | V <sub>OH</sub>  | СС | 2.8    | -    | 3.6   | V    | 15 kOhm pull-<br>down to 0 V     |

| DP pull-up resistor (idle bus)                      | R <sub>PUI</sub> | CC | 900    | -    | 1 575 | Ohm  |                                  |

| DP pull-up resistor<br>(upstream port<br>receiving) | R <sub>PUA</sub> | CC | 1 425  | -    | 3 090 | Ohm  |                                  |

| Input impedance DP,<br>DM                           | $Z_{\rm INP}$    | СС | 300    | -    | -     | kOhm | $0 \ V \leq V_{IN} \leq V_{DDP}$ |

| Driver output resistance<br>DP, DM                  | $Z_{\rm DRV}$    | СС | 28     | -    | 44    | Ohm  |                                  |

| Table 35 | USB Device Data Line (USB_DP, USB_DM) Parameters (Operating |

|----------|-------------------------------------------------------------|

|          | Conditions apply)                                           |

Measured at A-connector with 1.5 kOhm ± 5% to 3.3 V ± 0.3 V connected to USB\_DP or USB\_DM and at Bconnector with 15 kOhm ± 5% to ground connected to USB\_DP and USB\_DM.

| Parameter Power Dissipation                    | Symbol           |    |      | Values | 5    | Unit   | Note /                                                                     |

|------------------------------------------------|------------------|----|------|--------|------|--------|----------------------------------------------------------------------------|

|                                                |                  |    | Min. | Тур.   | Max. |        | Test Condition                                                             |

|                                                | $P_{DISS}$       | СС | -    | -      | 1    | W      | V <sub>DDP</sub> = 3.6 V,<br>T <sub>J</sub> = 150 °C                       |

| Wake-up time from Sleep to Active mode         | t <sub>SSA</sub> | СС | -    | 6      | -    | cycles |                                                                            |

| Wake-up time from Deep<br>Sleep to Active mode |                  |    | -    | -      | -    | ms     | Defined by the<br>wake-up of the<br>Flash module,<br>see<br>Section 3.2.11 |

| Wake-up time from<br>Hibernate mode            |                  |    | -    | -      | -    | ms     | Wake-up via<br>power-on reset<br>event, see<br>Section 3.3.2               |

### Table 38 Power Supply Parameters

1) CPU executing code from Flash, all peripherals idle.

2) CPU executing code from Flash. USB and CCU clock off.

3) CPU in sleep, all peripherals idle, Flash in Active mode.

- 4) CPU in sleep, Flash in Active mode.

- 5) CPU in sleep, peripherals disabled, after wake-up code execution from RAM.

- 6) To wake-up the Flash from its Sleep mode,  $f_{CPU} \ge 1$  MHz is required.

- 7) OSC\_ULP operating with external crystal on RTC\_XTAL

- 8) OSC\_ULP off, Hibernate domain operating with OSC\_SI clock

- 9) Test Power Loop: f<sub>SYS</sub> = 80 MHz, CPU executing benchmark code from Flash, all CCUs in 100kHz timer mode, all ADC groups in continuous conversion mode, USICs as SPI in internal loop-back mode, CAN in 500kHz internal loop-back mode, interrupt triggered DMA block transfers to parity protected RAMs and FCE, DTS measurements and FPU calculations.

The power consumption of each customer application will most probably be lower than this value, but must be evaluated separately.

- 10)  $I_{\text{DDP}}$  decreases typically by 3.5 mA when  $f_{\text{SYS}}$  decreases by 10 MHz, at constant  $T_{\text{J}}$

- 11) Sum of currents of all active converters (ADC and DAC)

# 3.3 AC Parameters

# 3.3.1 Testing Waveforms

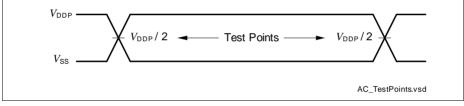

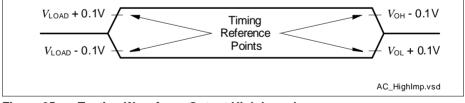

Figure 24 Testing Waveform, Output Delay

Figure 25 Testing Waveform, Output High Impedance

# 3.3.2 Power-Up and Supply Monitoring

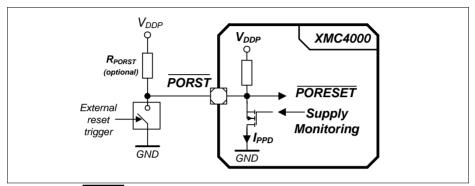

PORST is always asserted when  $V_{\text{DDP}}$  and/or  $V_{\text{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# Figure 26 PORST Circuit

| Table 41 | Supply Monit | toring Parameters |

|----------|--------------|-------------------|

|----------|--------------|-------------------|

| Parameter                                                       | Symbol                   | Values             |     |                    | Unit | Note /<br>Test Condition                                                                                         |

|-----------------------------------------------------------------|--------------------------|--------------------|-----|--------------------|------|------------------------------------------------------------------------------------------------------------------|

|                                                                 |                          | Min. Typ. Max.     |     |                    |      |                                                                                                                  |

| Digital supply voltage reset threshold                          | V <sub>POR</sub> CC      | 2.79 <sup>1)</sup> | _   | 3.05 <sup>2)</sup> | V    | 3)                                                                                                               |

| Core supply voltage reset threshold                             | V <sub>PV</sub> CC       | -                  | -   | 1.17               | V    |                                                                                                                  |

| $V_{\text{DDP}}$ voltage to ensure defined pad states           | V <sub>DDPPA</sub><br>CC | -                  | 1.0 | -                  | V    |                                                                                                                  |

| PORST rise time                                                 | t <sub>PR</sub> SR       | _                  | _   | 2                  | μs   |                                                                                                                  |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC      | -                  | 2.5 | 3.5                | ms   | Time to the first<br>user code<br>instruction                                                                    |

| $V_{ m DDC}$ ramp up time                                       | t <sub>VCR</sub> CC      | _                  | 550 | _                  | μS   | Ramp up after<br>power-on or<br>after a reset<br>triggered by a<br>violation of<br>$V_{\rm POR}$ or $V_{\rm PV}$ |

1) Minimum threshold for reset assertion.

# 3.3.5 Internal Clock Source Characteristics

### Fast Internal Clock Source

| Parameter         | Symbol                         |      | Values | 5    | Unit | Note /<br>Test Condition                                                            |

|-------------------|--------------------------------|------|--------|------|------|-------------------------------------------------------------------------------------|

|                   |                                | Min. | Тур.   | Max. |      |                                                                                     |

| Nominal frequency | $f_{\rm OFINC}$                | -    | 36.5   | _    | MHz  | not calibrated                                                                      |

|                   | CC                             | -    | 24     | -    | MHz  | calibrated                                                                          |

| Accuracy          | <i>∆f</i> <sub>OFI</sub><br>CC | -0.5 | -      | 0.5  | %    | automatic<br>calibration <sup>1)2)</sup>                                            |

|                   |                                | -15  | -      | 15   | %    | factory<br>calibration,<br>$V_{\rm DDP}$ = 3.3 V                                    |

|                   |                                | -25  | -      | 25   | %    | no calibration,<br>$V_{\rm DDP}$ = 3.3 V                                            |

|                   |                                | -7   | -      | 7    | %    | Variation over<br>voltage range <sup>3)</sup><br>$3.13 V \le V_{DDP} \le$<br>3.63 V |

| Start-up time     | t <sub>OFIS</sub> CC           | -    | 50     | -    | μS   |                                                                                     |

#### Table 44 Fast Internal Clock Parameters

1) Error in addition to the accuracy of the reference clock.

2) Automatic calibration compensates variations of the temperature and in the  $V_{\text{DDP}}$  supply voltage.

Deviations from the nominal V<sub>DDP</sub> voltage induce an additional error to the uncalibrated and/or factory calibrated oscillator frequency.

## Table 49 USIC SSC Slave Mode Timing

| Parameter                                                                                 | Symbol           |    | Values |      |      | Unit | Note /         |  |  |

|-------------------------------------------------------------------------------------------|------------------|----|--------|------|------|------|----------------|--|--|

|                                                                                           |                  |    | Min.   | Тур. | Max. |      | Test Condition |  |  |

| DX1 slave clock period                                                                    | t <sub>CLK</sub> | SR | 66.6   | -    | -    | ns   |                |  |  |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>               | t <sub>10</sub>  | SR | 3      | -    | -    | ns   |                |  |  |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | t <sub>11</sub>  | SR | 4      | -    | -    | ns   |                |  |  |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub>  | SR | 6      | -    | -    | ns   |                |  |  |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub>  | SR | 4      | -    | _    | ns   |                |  |  |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub>  | СС | 0      | -    | 24   | ns   |                |  |  |

These input timing are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

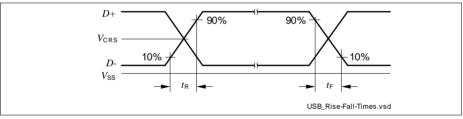

# 3.3.9 USB Interface Characteristics

The Universal Serial Bus (USB) Interface is compliant to the USB Rev. 2.0 Specification. High-Speed Mode is not supported.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter               | Sym                   | bol |      | Value | s      | Unit | Note /                 |

|-------------------------|-----------------------|-----|------|-------|--------|------|------------------------|

|                         |                       |     | Min. | Тур.  | Max.   |      | Test Condition         |

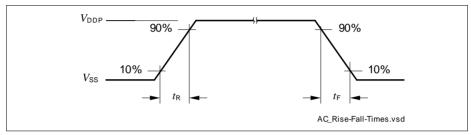

| Rise time               | t <sub>R</sub> CC     |     | 4    | -     | 20     | ns   | C <sub>L</sub> = 50 pF |

| Fall time               | t <sub>F</sub> CC     |     | 4    | -     | 20     | ns   | C <sub>L</sub> = 50 pF |

| Rise/Fall time matching | $t_{\rm R}/t_{\rm F}$ | CC  | 90   | -     | 111.11 | %    | C <sub>L</sub> = 50 pF |

| Crossover voltage       | V <sub>CRS</sub>      | CC  | 1.3  | -     | 2.0    | V    | C <sub>L</sub> = 50 pF |

Table 54

USB Timing Parameters (operating conditions apply)

Figure 35 USB Signal Timing

### Package and Reliability

power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers