#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 400MHz                                                                   |

| Co-Processors/DSP               | Communications; QUICC Engine, Security; SEC                              |

| RAM Controllers                 | DDR, DDR2                                                                |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (1)                                                      |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                    |

| Package / Case                  | 668-BBGA Exposed Pad                                                     |

| Supplier Device Package         | 668-PBGA-PGE (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc8358ecvragdga |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.3 Gigabit Reference Clock Input Timing

Table 8 provides the Gigabit reference clocks (GTX\_CLK125) AC timing specifications.

#### Table 8. GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  = 2.5 ± 0.125 mV/ 3.3 V ± 165 mV

| Parameter/Condition                                                | Symbol                                 | Min      | Typical | Max         | Unit | Notes |

|--------------------------------------------------------------------|----------------------------------------|----------|---------|-------------|------|-------|

| GTX_CLK125 frequency                                               | t <sub>G125</sub>                      | —        | 125     | _           | MHz  | _     |

| GTX_CLK125 cycle time                                              | t <sub>G125</sub>                      | —        | 8       | —           | ns   | _     |

| GTX_CLK rise and fall time $LV_{DD} = 2.5 V$ $LV_{DD} = 3.3 V$     | <sup>t</sup> G125R <sup>/t</sup> G125F | —        |         | 0.75<br>1.0 | ns   | 1     |

| GTX_CLK125 duty cycle<br>GMII & TBI<br>1000Base-T for RGMII & RTBI | t <sub>G125H</sub> /t <sub>G125</sub>  | 45<br>47 |         | 55<br>53    | %    | 2     |

| GTX_CLK125 jitter                                                  | —                                      | —        | —       | ±150        | ps   | 2     |

#### Notes:

1. Rise and fall times for GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

2. GTX\_CLK125 is used to generate the GTX clock for the UCC Ethernet transmitter with 2% degradation. The GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by GTX\_CLK. See Section 8.2.2, "MII AC Timing Specifications," Section 8.2.3, "RMII AC Timing Specifications," and Section 8.2.5, "RGMII and RTBI AC Timing Specifications" for the duty cycle for 10Base-T and 100Base-T reference clock.

## 5 **RESET Initialization**

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8358E.

## 5.1 **RESET DC Electrical Characteristics**

Table 9 provides the DC electrical characteristics for the RESET pins of the device.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | _                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | _                         | _    | ±10                    | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

**RESET** Initialization

#### Table 9. RESET Pins DC Electrical Characteristics (continued)

| Characteristic     | Symbol          | Condition                | Min | Max | Unit |

|--------------------|-----------------|--------------------------|-----|-----|------|

| Output low voltage | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA | _   | 0.4 | V    |

Notes:

1. This table applies for pins PORESET, HRESET, SRESET, and QUIESCE.

2. HRESET and SRESET are open drain pins, thus  $V_{OH}$  is not relevant for those pins.

## 5.2 **RESET AC Electrical Characteristics**

This section describes the AC electrical specifications for the reset initialization timing requirements of the device. Table 10 provides the reset initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                                                                        | Min | Max | Unit                     | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                 | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of PORESET with stable clock applied to CLKIN when the device is in PCI host mode                                                  | 32  | -   | t <sub>CLKIN</sub>       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the device is in PCI agent mode                                           | 32  | -   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET/SRESET assertion (output)                                                                                                                           | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET negation to SRESET negation (output)                                                                                                                | 16  | —   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI host mode  | 4   | _   | <sup>t</sup> CLKIN       | 2     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | -   | <sup>t</sup> PCI_SYNC_IN | 1     |

| Input hold time for POR config signals with respect to negation of HRESET                                                                                  | 0   | —   | ns                       |       |

| Time for the device to turn off POR config signals with respect to the assertion of HRESET                                                                 |     | 4   | ns                       | 3     |

| Time for the device to turn on POR config signals with respect to the negation of $\overline{\text{HRESET}}$                                               | 1   | -   | t <sub>PCI_SYNC_IN</sub> | 1, 3  |

#### Table 10. RESET Initialization Timing Specifications

#### Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. See the *MPC8360E PowerQUICC II Pro Integrated Communications Processor Family Reference Manual* for more details.

2. t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. See the MPC8360E PowerQUICC II Pro Integrated Communications Processor Family Reference Manual for more details.

3. POR config signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

DDR and DDR2 SDRAM

## Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of (1.8 V or 2.5 V) ± 5%.

| Parameter <sup>8</sup>                                                              | Symbol <sup>1</sup>                          | Min                      | Мах                         | Unit | Notes |

|-------------------------------------------------------------------------------------|----------------------------------------------|--------------------------|-----------------------------|------|-------|

| ADDR/CMD output setup with respect to MCK<br>266 MHz<br>200 MHz                     | t <sub>DDKHAS</sub>                          | 2.8<br>3.5               | _                           | ns   | 4     |

| ADDR/CMD output hold with respect to MCK<br>266 MHz—DDR1<br>266 MHz—DDR2<br>200 MHz | t <sub>ddkhax</sub>                          | 2.6<br>2.8<br>3.5        | _                           | ns   | 4     |

| MCS(n) output setup with respect to MCK<br>266 MHz<br>200 MHz                       | t <sub>DDKHCS</sub>                          | 2.8<br>3.5               | —                           | ns   | 4     |

| MCS(n) output hold with respect to MCK<br>266 MHz<br>200 MHz                        | <sup>t</sup> DDKHCX                          | 2.7<br>3.5               | —                           | ns   | 4     |

| MCK to MDQS                                                                         | t <sub>DDKHMH</sub>                          | -0.75                    | 0.6                         | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to MDQS<br>266 MHz<br>200 MHz                | t <sub>DDKHDS</sub> ,<br>t <sub>DDKLDS</sub> | 1.0<br>1.2               | —                           | ns   | 6     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>266 MHz<br>200 MHz                 | t <sub>DDKHDX</sub> ,<br>t <sub>DDKLDX</sub> | 1.0<br>1.2               | —                           | ns   | 6     |

| MDQS preamble start                                                                 | t <sub>DDKHMP</sub>                          | $-0.5\times t_{MCK}-0.6$ | $-0.5 \times t_{MCK} + 0.6$ | ns   | 7     |

#### UCC Ethernet Controller: Three-Speed Ethernet, MII Management

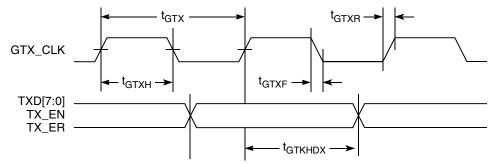

Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

### 8.2.1.2 GMII Receive AC Timing Specifications

Table 27 provides the GMII receive AC timing specifications.

Table 27. GMII Receive AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DD}}/\text{OV}_{\text{DD}}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | —   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | —     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | —   | ns   | —     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.3 | —   | —   | ns   | —     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | —     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   |     | _   | 1.0 | ns   | —     |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

#### UCC Ethernet Controller: Three-Speed Ethernet, MII Management

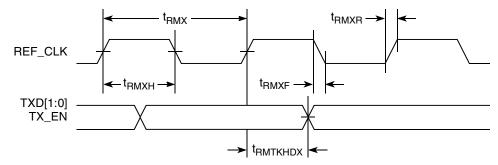

Figure 14 shows the RMII transmit AC timing diagram.

Figure 14. RMII Transmit AC Timing Diagram

### 8.2.3.2 RMII Receive AC Timing Specifications

Table 31 provides the RMII receive AC timing specifications.

#### Table 31. RMII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V  $\pm$  10%.

| Parameter/Condition                           | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|-----------------------------------------------|-------------------------------------|-----|-----|-----|------|

| REF_CLK clock period                          | t <sub>RMX</sub>                    | —   | 20  | —   | ns   |

| REF_CLK duty cycle                            | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | —   | 65  | %    |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK | t <sub>RMRDVKH</sub>                | 4.0 | —   | —   | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK  | t <sub>RMRDXKH</sub>                | 2.0 | —   | —   | ns   |

| REF_CLK clock rise time                       | t <sub>RMXR</sub>                   | 1.0 | —   | 4.0 | ns   |

| REF_CLK clock fall time                       | t <sub>RMXF</sub>                   | 1.0 |     | 4.0 | ns   |

Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first three letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>RMRDVKH</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>RMX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>RMRDXKL</sub> symbolizes RMII receive timing (RMR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>RMX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>RMX</sub> represents the RMII (RM) reference (X) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

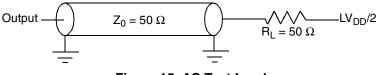

Figure 15 provides the AC test load.

Figure 15. AC Test Load

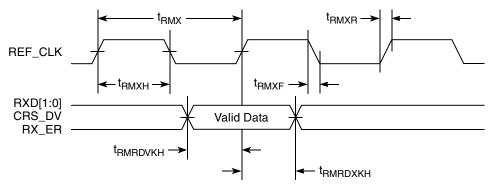

Figure 16 shows the RMII receive AC timing diagram.

Figure 16. RMII Receive AC Timing Diagram

### 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

### 8.2.4.1 TBI Transmit AC Timing Specifications

Table 32 provides the TBI transmit AC timing specifications.

#### Table 32. TBI Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                   | Symbol <sup>1</sup>                        | Min | Тур | Мах     | Unit | Notes |

|---------------------------------------|--------------------------------------------|-----|-----|---------|------|-------|

| GTX_CLK clock period                  | t <sub>TTX</sub>                           | —   | 8.0 | —       | ns   | —     |

| GTX_CLK duty cycle                    | t <sub>TTXH</sub> /t <sub>TTX</sub>        | 40  | —   | 60      | %    | —     |

| GTX_CLK to TBI data TCG[9:0] delay    | <sup>t</sup> тткнох<br><sup>t</sup> тткноv | 0.9 | —   | <br>5.0 | ns   |       |

| GTX_CLK clock rise time, (20% to 80%) | t <sub>TTXR</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK clock fall time, (80% to 20%) | t <sub>TTXF</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK125 reference clock period     | t <sub>G125</sub>                          | —   | 8.0 | —       | ns   | 2     |

| GTX_CLK125 reference clock duty cycle | t <sub>G125H</sub> /t <sub>G125</sub>      | 45  | —   | 55      | ns   | —     |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

#### Table 37. IEEE 1588 Timer AC Specifications (continued)

| Parameter                   | Symbol             | Min | Мах | Unit | Notes |

|-----------------------------|--------------------|-----|-----|------|-------|

| Timer alarm to output valid | t <sub>TMRAL</sub> |     |     |      | 2     |

Notes:

1. The timer can operate on rtc\_clock or tmr\_clock. These clocks get muxed and any one of them can be selected. The minimum and maximum requirement for both rtc\_clock and tmr\_clock are the same.

2. These are asynchronous signals.

3. Inputs need to be stable at least one TMR clock.

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8358E.

## 9.1 Local Bus DC Electrical Characteristics

Table 38 provides the DC electrical characteristics for the local bus interface.

#### Table 38. Local Bus DC Electrical Characteristics

| Parameter                                          | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.4 | _                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current                                      | I <sub>IN</sub> | —                      | ±10                    | μA   |

## 9.2 Local Bus AC Electrical Specifications

Table 39 describes the general timing parameters of the local bus interface of the device.

Table 39. Local Bus General Timing Parameters—DLL Enabled

| Parameter                                                   | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|-------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus cycle time                                        | t <sub>LBK</sub>     | 7.5 | —   | ns   | 2     |

| Input setup to local bus clock (except LUPWAIT)             | t <sub>LBIVKH1</sub> | 1.7 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                      | t <sub>LBIVKH2</sub> | 1.9 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)            | t <sub>LBIXKH1</sub> | 1.0 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                     | t <sub>LBIXKH2</sub> | 1.0 | —   | ns   | 3, 4  |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT1</sub> | 1.5 | —   | ns   | 5     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT2</sub> | 3.0 | —   | ns   | 6     |

| LALE output fall to LAD output transition (LATCH hold time) | t <sub>LBOTOT3</sub> | 2.5 | —   | ns   | 7     |

1<sup>2</sup>C

#### Table 44. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 43).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                                  | Мах                  | Unit |

|---------------------------------------------------------------------------------|---------------------|--------------------------------------|----------------------|------|

| Data hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices      | t <sub>I2DXKL</sub> | 0 <sup>2</sup>                       | <br>0.9 <sup>3</sup> | μs   |

| Rise time of both SDA and SCL signals                                           | t <sub>I2CR</sub>   | 20 + 0.1 C <sub>b</sub> <sup>4</sup> | 300                  | ns   |

| Fall time of both SDA and SCL signals                                           | t <sub>I2CF</sub>   | 20 + 0.1 C <sub>b</sub> <sup>4</sup> | 300                  | ns   |

| Set-up time for STOP condition                                                  | t <sub>I2PVKH</sub> | 0.6                                  | _                    | μs   |

| Bus free time between a STOP and START condition                                | t <sub>I2KHDX</sub> | 1.3                                  | _                    | μs   |

| Noise margin at the LOW level for each connected device (including hysteresis)  | V <sub>NL</sub>     | $0.1 \times OV_{DD}$                 | _                    | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times OV_{DD}$                 | _                    | V    |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> clock reference (K) going to the t<sub>I2C</sub> clock reference (K) going to the timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the low (L) state or hold time. Also, t<sub>I2PVKH</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the t<sub>I2C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. The device provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IH</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum  $t_{I2DVKH}$  has only to be met if the device does not stretch the LOW period ( $t_{I2CL}$ ) of the SCL signal.

- 4.  $C_B$  = capacitance of one bus line in pF.

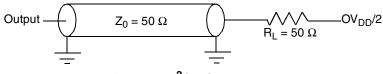

Figure 33 provides the AC test load for the  $I^2C$ .

Figure 33. I<sup>2</sup>C AC Test Load

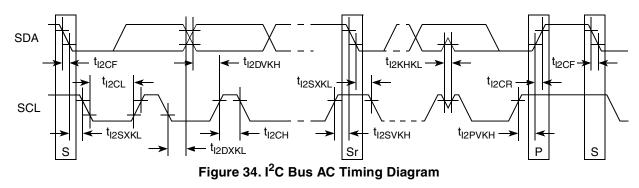

Figure 34 shows the AC timing diagram for the  $I^2C$  bus.

TDM/SI

#### Table 56. TDM/SI DC Electrical Characteristics (continued)

| Characteristic    | Symbol          | Condition                      | Min  | Мах | Unit |

|-------------------|-----------------|--------------------------------|------|-----|------|

| Input low voltage | V <sub>IL</sub> | —                              | -0.3 | 0.8 | V    |

| Input current     | I <sub>IN</sub> | $0 \ V \le V_{IN} \le OV_{DD}$ | _    | ±10 | μA   |

## 17.2 TDM/SI AC Timing Specifications

Table 57 provides the TDM/SI input and output AC timing specifications.

Table 57. TDM/SI AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Max <sup>3</sup> | Unit |

|-----------------------------------------------|---------------------|-----|------------------|------|

| TDM/SI outputs—External clock delay           | t <sub>SEKHOV</sub> | 2   | 10               | ns   |

| TDM/SI outputs—External clock high impedance  | t <sub>SEKHOX</sub> | 2   | 10               | ns   |

| TDM/SI inputs—External clock input setup time | t <sub>SEIVKH</sub> | 5   | -                | ns   |

| TDM/SI inputs—External clock input hold time  | t <sub>SEIXKH</sub> | 2   | _                | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>SEKHOX</sub> symbolizes the TDM/SI outputs external timing (SE) for the time t<sub>TDM/SI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).</sub></sub>

- 3. Timings are measured from the positive or negative edge of the clock, according to SIxMR [CE] and SITXCEI[TXCEIx]. See the MPC8360E Integrated Communications Processor Family Reference Manual for more details.

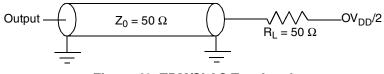

Figure 43 provides the AC test load for the TDM/SI.

Figure 43. TDM/SI AC Test Load

Figure 44 represents the AC timing from Table 55. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

| Characteristic                                | Symbol <sup>2</sup> | Min | Мах | Unit | Notes |

|-----------------------------------------------|---------------------|-----|-----|------|-------|

| UTOPIA inputs—External clock input setup time | t <sub>UEIVKH</sub> | 4.2 | _   | ns   | —     |

| UTOPIA inputs—Internal clock input hold time  | t <sub>UIIXKH</sub> | 2.4 | _   | ns   | —     |

| UTOPIA inputs—External clock input hold time  | t <sub>UEIXKH</sub> | 1   | _   | ns   | —     |

#### Table 59. UTOPIA AC Timing Specifications<sup>1</sup> (continued)

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>UIKHOX</sub> symbolizes the UTOPIA outputs internal timing (UI) for the time t<sub>UTOPIA</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).</sub>

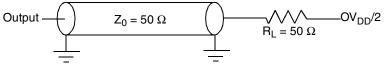

Figure 45 provides the AC test load for the UTOPIA.

Figure 45. UTOPIA AC Test Load

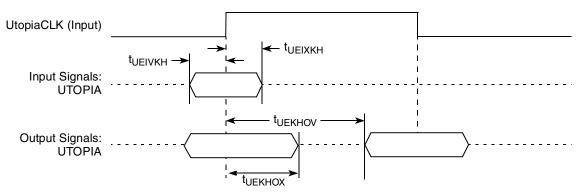

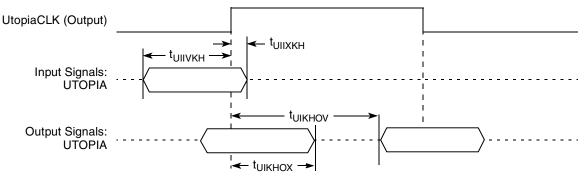

Figure 46 and Figure 47 represent the AC timing from Table 55. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 46 shows the UTOPIA timing with external clock.

Figure 46. UTOPIA AC Timing (External Clock) Diagram

Figure 47 shows the UTOPIA timing with internal clock.

Figure 47. UTOPIA AC Timing (Internal Clock) Diagram

# 19 HDLC, BISYNC, Transparent, and Synchronous UART

This section describes the DC and AC electrical specifications for the high level data link control (HDLC), BISYNC, transparent, and synchronous UART protocols of the MPC8358E.

## 19.1 HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

Table 60 provides the DC electrical characteristics for the device HDLC, BISYNC, transparent, and synchronous UART protocols.

| Characteristic      | Symbol          | Condition                        | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -2.0 mA        | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA         | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \leq V_{IN} \leq OV_{DD}$ | _    | ±10                    | μA   |

Table 60. HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

USB

## 20 USB

This section provides the AC and DC electrical specifications for the USB interface of the MPC8358E.

## 20.1 USB DC Electrical Characteristics

Table 63 provides the DC electrical characteristics for the USB interface.

#### Table 63. USB DC Electrical Characteristics

| Parameter                                          | Symbol          | Min                    | Мах                    | Unit |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> – 0.4 | _                      | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA | V <sub>OL</sub> | _                      | 0.2                    | V    |

| Input current                                      | I <sub>IN</sub> | _                      | ±10                    | μA   |

## 20.2 USB AC Electrical Specifications

Table 64 describes the general timing parameters of the USB interface of the device.

Table 64. USB General Timing Parameters

| Parameter                    | Symbol <sup>1</sup>  | Min    | Max | Unit | Notes                  |

|------------------------------|----------------------|--------|-----|------|------------------------|

| USB clock cycle time         | t <sub>USCK</sub>    | 20.83  | _   | ns   | Full speed 48 MHz      |

| USB clock cycle time         | t <sub>USCK</sub>    | 166.67 | _   | ns   | Low speed 6 MHz        |

| Skew between TXP and TXN     | t <sub>USTSPN</sub>  | _      | 5   | ns   | —                      |

| Skew among RXP, RXN, and RXD | t <sub>USRSPND</sub> | _      | 10  | ns   | Full speed transitions |

| Skew among RXP, RXN, and RXD | t <sub>USRPND</sub>  | —      | 100 | ns   | Low speed transitions  |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(state)(signal)</sub> for receive signals and t<sub>(first two letters of functional block)(state)(signal)</sub> for transmit signals. For example, t<sub>USRSPND</sub> symbolizes USB timing (US) for the USB receive signals skew (RS) among RXP, RXN, and RXD (PND). Also, t<sub>USTSPN</sub> symbolizes USB timing (US) for the USB transmit signals skew (TS) between TXP and TXN (PN).

2.Skew measurements are done at  $OV_{DD}/2$  of the rising or falling edge of the signals.

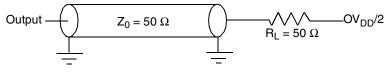

Figure 51 provide the AC test load for the USB.

Figure 51. USB AC Test Load

Package and Pin Listings

| Signal                       | Package Pin Number                | Pin Type | Power              | Notes    |

|------------------------------|-----------------------------------|----------|--------------------|----------|

|                              |                                   |          | Supply             |          |

| LGPL2/<br>LSDRAS/            | AH19                              | 0        | OV <sub>DD</sub>   | _        |

| LOE                          |                                   |          |                    |          |

| LGPL3/                       | AE18                              | I/O      | OV <sub>DD</sub>   | _        |

| LSDCAS/<br>cfg_reset_source2 |                                   |          |                    |          |

| LGPL4/                       | AG19                              | I/O      | OV <sub>DD</sub>   | <u> </u> |

| LGTA/                        | halo                              | 1,0      | 0,00               |          |

| LUPWAIT/                     |                                   |          |                    |          |

| LPBSE<br>LGPL5/              |                                   |          | 01/                |          |

| cfg_clkin_div                | AF19                              | I/O      | OV <sub>DD</sub>   | _        |

|                              | AD8                               | 0        | OV <sub>DD</sub>   |          |

| LCLK[0]                      | AC9                               | 0        | OV <sub>DD</sub>   | _        |

| LCLK[1]/                     | AG6                               | 0        | OV <sub>DD</sub>   |          |

| LCS[6]                       |                                   |          |                    |          |

| LCLK[2]/<br>LCS[7]           | AE7                               | 0        | OV <sub>DD</sub>   | —        |

| LSYNC_OUT                    | AG4                               | 0        | OV <sub>DD</sub>   |          |

| LSYNC_IN                     | AC8                               |          | OV <sub>DD</sub>   |          |

|                              | Programmable Interrupt Controller |          | 0.00               |          |

|                              |                                   |          |                    |          |

| MCP_OUT                      | AG3                               | 0        | OV <sub>DD</sub>   | 2        |

| IRQ0/<br>MCP_IN              | AH4                               |          | OV <sub>DD</sub>   | _        |

| IRQ[1:2]                     | AG5, AH5                          | I/O      | OV <sub>DD</sub>   | —        |

| IRQ[3]/<br>CORE_SRESET       | AD7                               | I/O      | OV <sub>DD</sub>   | -        |

| IRQ[4:5]                     | AC7, AD6                          | I/O      | OV <sub>DD</sub>   | _        |

| IRQ[6:7]                     | AC6, AC10                         | I/O      | OV <sub>DD</sub>   | —        |

|                              | DUART                             | ·        |                    |          |

| UART1_SOUT                   | AE3                               | 0        | OV <sub>DD</sub>   | _        |

| UART1_SIN                    | AE4                               | I/O      | OV <sub>DD</sub>   | —        |

| UART1_CTS                    | AG2                               | I/O      | OV <sub>DD</sub>   | —        |

| UART1_RTS                    | AA6                               | 0        | OV <sub>DD</sub>   | _        |

|                              | I <sup>2</sup> C Interface        | 1        |                    |          |

| IIC1_SDA                     | AB6                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC1_SCL                     | AD5                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SDA                     | AF3                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SCL                     | AH2                               | I/O      | OV <sub>DD</sub>   | 2        |

|                              | QUICC Engine                      | ·        |                    |          |

| CE_PA[0]                     | F6                                | I/O      | LV <sub>DD</sub> 0 | _        |

|                              |                                   |          |                    | 1        |

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL<br>Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF]) |

|-------------|-------------|-------------------------------------------------------------------------------|

| 01011       | 1           | × 5.5                                                                         |

| 01101       | 1           | × 6.5                                                                         |

| 01111       | 1           | × 7.5                                                                         |

| 10001       | 1           | × 8.5                                                                         |

| 10011       | 1           | × 9.5                                                                         |

| 10101       | 1           | × 10.5                                                                        |

| 10111       | 1           | × 11.5                                                                        |

| 11001       | 1           | × 12.5                                                                        |

| 11011       | 1           | × 13.5                                                                        |

| 11101       | 1           | × 14.5                                                                        |

Table 72. QUICC Engine Block PLL Multiplication Factors (continued)

Note:

1. Reserved modes are not listed.

The RCWL[CEVCOD] denotes the QUICC Engine Block PLL VCO internal frequency as shown in Table 73.

Table 73. QUICC Engine Block PLL VCO Divider

| RCWL[CEVCOD] | VCO Divider |

|--------------|-------------|

| 00           | 4           |

| 01           | 8           |

| 10           | 2           |

| 11           | Reserved    |

#### NOTE

The VCO divider (RCWL[CEVCOD]) must be set properly so that the QUICC Engine block VCO frequency is in the range of 600–1400 MHz. The QUICC Engine block frequency is not restricted by the CSB and core frequencies. The CSB, core, and QUICC Engine block frequencies should be selected according to the performance requirements.

The QUICC Engine block VCO frequency is derived from the following equations:

$ce_clk = (primary clock input \times CEPMF) \div (1 + CEPDF)$

QE VCO Frequency =  $ce_clk \times$  VCO divider  $\times$  (1 + CEPDF)

| Conf<br>No. <sup>1</sup> | SPMF | CORE<br>PLL | CEPMF | CEPDF | Input<br>Clock Freq<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine<br>Freq (MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|--------------------------|------|-------------|-------|-------|------------------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

| c5                       | æ    | æ           | 10000 | 0     | 33                           | —                 | —                  | 533                           | —            | 8            | 8            |

| c6                       | æ    | æ           | 10001 | 0     | 33                           | —                 | —                  | 566                           | —            | —            | 8            |

|                          |      |             |       | 66 MH | z CLKIN/PCI                  | _SYNC_IN (        | Options            |                               |              |              |              |

| s1h                      | 0011 | 0000110     | æ     | æ     | 66                           | 200               | 400                | —                             | 8            | ∞            | ∞            |

| s2h                      | 0011 | 0000101     | 8     | æ     | 66                           | 200               | 500                | _                             | —            | ∞            | 8            |

| s3h                      | 0011 | 0000110     | 8     | æ     | 66                           | 200               | 600                | _                             | —            | —            | 8            |

| s4h                      | 0100 | 0000011     | 8     | æ     | 66                           | 266               | 400                | _                             | 8            | ∞            | 8            |

| s5h                      | 0100 | 0000100     | æ     | æ     | 66                           | 266               | 533                | _                             | —            | ∞            | 8            |

| s6h                      | 0100 | 0000101     | æ     | æ     | 66                           | 266               | 667                | _                             | _            | —            | 8            |

| s7h                      | 0101 | 0000010     | æ     | æ     | 66                           | 333               | 333                | _                             | ∞            | ∞            | 8            |

| s8h                      | 0101 | 0000011     | 8     | æ     | 66                           | 333               | 500                | _                             | —            | ∞            | 8            |

| s9h                      | 0101 | 0000100     | 8     | æ     | 66                           | 333               | 667                |                               | _            | —            | 8            |

| c1h                      | æ    | æ           | 00101 | 0     | 66                           | —                 | —                  | 333                           | 8            | 8            | 8            |

| c2h                      | æ    | æ           | 00110 | 0     | 66                           | —                 | —                  | 400                           | ∞            | 8            | 8            |

| c3h                      | æ    | æ           | 00111 | 0     | 66                           | —                 | —                  | 466                           | _            | 8            | 8            |

| c4h                      | æ    | æ           | 01000 | 0     | 66                           | —                 | —                  | 533                           | —            | 8            | 8            |

| c5h                      | æ    | æ           | 01001 | 0     | 66                           | —                 | _                  | 600                           | —            | —            | 8            |

The Conf No. consist of prefix, an index and a postfix. The prefix "s" and "c" stands for "syset" and "ce" respectively. The postfix "h" stands for "high input clock."The index is a serial number.

The following steps describe how to use Table 74. See Example 1.

- 1. Choose the up or down sections in the table according to input clock rate 33 MHz or 66 MHz.

- 2. Select a suitable CSB and core clock rates from Table 74. Copy the SPMF and CORE PLL configuration bits.

- 3. Select a suitable QUICC Engine block clock rate from Table 74. Copy the CEPMF and CEPDF configuration bits.

- 4. Insert the chosen SPMF, COREPLL, CEPMF and CEPDF to the RCWL fields, respectively.

#### Example 1. Sample Table Use

| SPMF | CORE<br>PLL | CEPMF | CEPDF | Input Clock<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine Freq<br>(MHz) | 400<br>(MHz) |

|------|-------------|-------|-------|----------------------|-------------------|--------------------|-------------------------------|--------------|

| 1000 | 0000011     | 01001 | 0     | 33                   | 266               | 400                | 300                           | ∞            |

#### MPC8358E PowerQUICC II Pro Processor Revision 2.1 PBGA Silicon Hardware Specifications, Rev. 3

1

Thermal

## 23.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (°C)

$T_T$  = thermocouple temperature on top of package (°C)

$\Psi_{JT}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 23.2.4 Heat Sinks and Junction-to-Ambient Thermal Resistance

In some application environments, a heat sink will be required to provide the necessary thermal management of the device. When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

Thermal

|          | Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-millennium.com                | 408-436-8770 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|          | Tyco Electronics<br>Chip Coolers™<br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com                              | 800-522-6752 |

|          | Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                                     | 603-635-5102 |

| Interfac | e material vendors include the following:                                                                                                     |              |

|          | Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                                      | 781-935-4850 |

|          | Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

|          | Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                                | 888-642-7674 |

|          | The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                                    | 800-347-4572 |

## 23.3 Heat Sink Attachment

When attaching heat sinks to these devices, an interface material is required. The best method is to use thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces which would lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. Recommended maximum force on the top of the package is 10 lb force (4.5 kg force). If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

## 23.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package (°C)  $R_{\theta JC}$  = junction to case thermal resistance (°C/W)  $P_D$  = power dissipation (W)

## 24 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8358E. Additional information can be found in *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

## 24.1 System Clocking

The device includes two PLLs, as follows.

- The platform PLL (AV<sub>DD</sub>1) generates the platform clock from the externally supplied CLKIN input. The frequency ratio between the platform and CLKIN is selected using the platform PLL ratio configuration bits as described in Section 22.1, "System PLL Configuration."

- The e300 core PLL (AV<sub>DD</sub>2) generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 22.2, "Core PLL Configuration."

## 24.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, respectively). The AV<sub>DD</sub> level should always be equivalent to  $V_{DD}$ , and preferably these voltages will be derived directly from  $V_{DD}$  through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide five independent filter circuits as illustrated in Figure 54, one to each of the five  $AV_{DD}$  pins. By providing independent filters to each PLL, the opportunity to cause noise injection from one PLL to the other is reduced.

|   | Impedance    | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | PCI | DDR DRAM | Symbol            | Unit |

|---|--------------|----------------------------------------------------------------------------|-----|----------|-------------------|------|

| I | Differential | NA                                                                         | NA  | NA       | Z <sub>DIFF</sub> | W    |

| Table 77. Im | pedance | Characteristics | (continued) |

|--------------|---------|-----------------|-------------|

|              |         |                 |             |

Note: Nominal supply voltages. See Table 1,  $T_J = 105^{\circ}C$ .

## 24.6 Configuration Pin Muxing

The device provides the user with power-on configuration options that can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While HRESET is asserted however, these pins are treated as inputs. The value presented on these pins while HRESET is asserted, is latched when HRESET deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

## 24.7 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins, Ethernet Management MDIO pin, and EPIC interrupt pins.

For more information on required pull-up resistors and the connections required for the JTAG interface, see *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

## 25 Ordering Information

## 25.1 Part Numbers Fully Addressed by this Document

Table 78 provides the Freescale part numbering nomenclature for the MPC8358E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also

```

Ordering Information

```

includes an application modifier, which may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| Table 78 | Part | Numbering | Nomenclature <sup>1</sup> |

|----------|------|-----------|---------------------------|

|----------|------|-----------|---------------------------|

| MPC             | nnnn               | е                                       | t                                                                                                                | рр                                  | aa                                              | а                     | а                            | Α                           |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------|-----------------------|------------------------------|-----------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature<br>Range                                                                                             | Package <sup>2</sup>                | Processor<br>Frequency <sup>3</sup>             | Platform<br>Frequency | QUICC<br>Engine<br>Frequency | Die<br>Revision             |

| MPC             | 8358               | Blank = Not<br>included<br>E = included | Blank =<br>0 °C T <sub>A</sub> to<br>105 °C T <sub>J</sub><br>C= -40°C T <sub>A</sub><br>to 105°C T <sub>J</sub> | ZQ = PBGA<br>VR = PBGA<br>(no lead) | e300 core speed<br>AD = 266 MHz<br>AG = 400 MHz | D = 266 MHz           | D = 266 MHz<br>G = 400 MHz   | A = revision<br>2.1 silicon |

<sup>1</sup> Not all processor, platform, and QUICC Engine block frequency combinations are supported. For available frequency combinations, contact your local Freescale sales office or authorized distributor.

<sup>2</sup> See Section 21, "Package and Pin Listings," for more information on available package types.

<sup>3</sup> Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

Table 79 shows the SVR settings by device and package type.

|          |         | -                 |

|----------|---------|-------------------|

| Device   | Package | SVR<br>(Rev. 2.1) |

| MPC8358E | PBGA    | 0x804E_0021       |

| MPC8358  | PBGA    | 0x804F_0021       |

Table 79. SVR Settings