#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 400MHz                                                                   |

| Co-Processors/DSP               | Communications; QUICC Engine                                             |

| RAM Controllers                 | DDR, DDR2                                                                |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (1)                                                      |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                        |

| Package / Case                  | 668-BBGA Exposed Pad                                                     |

| Supplier Device Package         | 668-PBGA-PGE (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8358cvragdda |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Data bus widths:

- Single 32-bit data PCI interface that operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- PCI host bridge capabilities on both interfaces

- PCI agent mode supported on PCI interface

- Support for PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Support for posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration, supporting five masters on PCI

- Support for accesses to all PCI address spaces

- Parity support

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle supported when the device is the target

- Internal configuration registers accessible from PCI

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for one external (optional) and seven internal machine checkstop interrupt sources

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to communication processor

- Redirects interrupts to external INTA pin when in core disable mode

- Unique vector number for each interrupt source

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

## 4.3 Gigabit Reference Clock Input Timing

Table 8 provides the Gigabit reference clocks (GTX\_CLK125) AC timing specifications.

### Table 8. GTX\_CLK125 AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  = 2.5 ± 0.125 mV/ 3.3 V ± 165 mV

| Parameter/Condition                                                | Symbol                                 | Min      | Typical | Max         | Unit | Notes |

|--------------------------------------------------------------------|----------------------------------------|----------|---------|-------------|------|-------|

| GTX_CLK125 frequency                                               | t <sub>G125</sub>                      | —        | 125     | _           | MHz  | _     |

| GTX_CLK125 cycle time                                              | t <sub>G125</sub>                      | —        | 8       | —           | ns   | _     |

| GTX_CLK rise and fall time $LV_{DD} = 2.5 V$ $LV_{DD} = 3.3 V$     | <sup>t</sup> G125R <sup>/t</sup> G125F | —        |         | 0.75<br>1.0 | ns   | 1     |

| GTX_CLK125 duty cycle<br>GMII & TBI<br>1000Base-T for RGMII & RTBI | t <sub>G125H</sub> /t <sub>G125</sub>  | 45<br>47 |         | 55<br>53    | %    | 2     |

| GTX_CLK125 jitter                                                  | —                                      | —        | —       | ±150        | ps   | 2     |

### Notes:

1. Rise and fall times for GTX\_CLK125 are measured from 0.5 and 2.0 V for  $LV_{DD}$  = 2.5 V and from 0.6 and 2.7 V for  $LV_{DD}$  = 3.3 V.

2. GTX\_CLK125 is used to generate the GTX clock for the UCC Ethernet transmitter with 2% degradation. The GTX\_CLK125 duty cycle can be loosened from 47%/53% as long as the PHY device can tolerate the duty cycle generated by GTX\_CLK. See Section 8.2.2, "MII AC Timing Specifications," Section 8.2.3, "RMII AC Timing Specifications," and Section 8.2.5, "RGMII and RTBI AC Timing Specifications" for the duty cycle for 10Base-T and 100Base-T reference clock.

# 5 **RESET Initialization**

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8358E.

## 5.1 **RESET DC Electrical Characteristics**

Table 9 provides the DC electrical characteristics for the RESET pins of the device.

| Characteristic      | Symbol          | Condition                 | Min  | Мах                    | Unit |

|---------------------|-----------------|---------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | _                         | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                         | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | _                         | _    | ±10                    | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA  | —    | 0.5                    | V    |

### Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of (1.8 V or 2.5 V)  $\pm$  5%.

| Parameter <sup>8</sup> | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|------------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end      | t <sub>DDKHME</sub> | -0.6 | 0.9 | ns   | 7     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. In the source synchronous mode, MCK/MCK can be shifted in ¼ applied cycle increments through the clock control register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the MPC8360E PowerQUICC II Pro Integrated Communications Processor Family Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the device.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the device. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 8. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

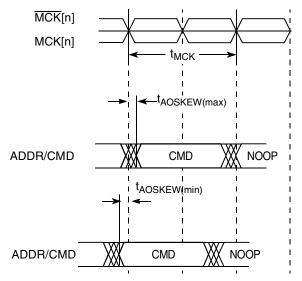

Figure 6 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 6. Timing Diagram for t<sub>AOSKEW</sub> Measurement

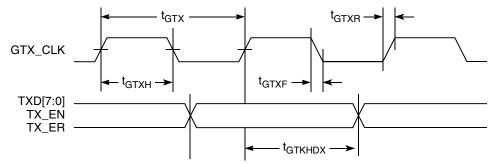

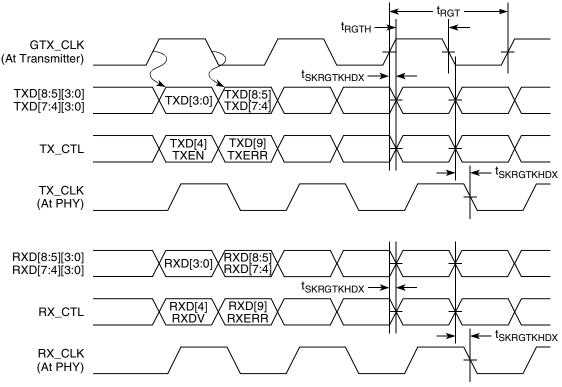

Figure 9 shows the GMII transmit AC timing diagram.

Figure 9. GMII Transmit AC Timing Diagram

### 8.2.1.2 GMII Receive AC Timing Specifications

Table 27 provides the GMII receive AC timing specifications.

Table 27. GMII Receive AC Timing Specifications

At recommended operating conditions with  $\text{LV}_{\text{DD}}/\text{OV}_{\text{DD}}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit | Notes |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | —   | ns   | —     |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 40  | —   | 60  | %    | —     |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | —   | —   | ns   | —     |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0.3 | —   | —   | ns   | —     |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>GRXR</sub>                   | _   | —   | 1.0 | ns   | —     |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>GRXF</sub>                   |     | _   | 1.0 | ns   | —     |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

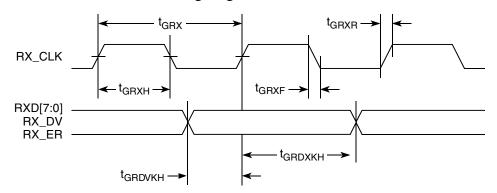

Figure 10 shows the GMII receive AC timing diagram.

Figure 10. GMII Receive AC Timing Diagram

### 8.2.2 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.2.1 MII Transmit AC Timing Specifications

Table 28 provides the MII transmit AC timing specifications.

### Table 28. MII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                             | Symbol <sup>1</sup>                        | Min | Тур | Мах     | Unit |

|-------------------------------------------------|--------------------------------------------|-----|-----|---------|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub>                           | —   | 400 | —       | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                           | —   | 40  | —       | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub>        | 35  | —   | 65      | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub><br>t <sub>MTKHDV</sub> | 1   | 5   | —<br>15 | ns   |

| TX_CLK data clock rise time, (20% to 80%)       | t <sub>MTXR</sub>                          | 1.0 | —   | 4.0     | ns   |

| TX_CLK data clock fall time, (80% to 20%)       | t <sub>MTXF</sub>                          | 1.0 | —   | 4.0     | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

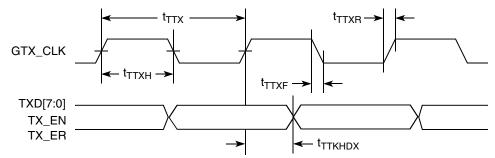

Figure 17 shows the TBI transmit AC timing diagram.

Figure 17. TBI Transmit AC Timing Diagram

### 8.2.4.2 TBI Receive AC Timing Specifications

Table 33 provides the TBI receive AC timing specifications.

### Table 33. TBI Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур  | Max | Unit | Notes |

|--------------------------------------------------------|-------------------------------------|-----|------|-----|------|-------|

| PMA_RX_CLK clock period                                | t <sub>TRX</sub>                    | _   | 16.0 | _   | ns   | —     |

| PMA_RX_CLK skew                                        | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   | —     |

| RX_CLK duty cycle                                      | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    | —     |

| RCG[9:0] setup time to rising PMA_RX_CLK               | t <sub>TRDVKH</sub>                 | 2.5 | —    | _   | ns   | 2     |

| RCG[9:0] hold time to rising PMA_RX_CLK                | t <sub>TRDXKH</sub>                 | 1.0 | —    | —   | ns   | 2     |

| RX_CLK clock rise time, $V_{IL}(min)$ to $V_{IH}(max)$ | t <sub>TRXR</sub>                   | 0.7 | —    | 2.4 | ns   | —     |

| RX_CLK clock fall time, $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>TRXF</sub>                   | 0.7 | _    | 2.4 | ns   | _     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub>

- 2. Setup and hold time of even numbered RCG are measured from riding edge of PMA\_RX\_CLK1. Setup and hold time of odd numbered RCG are measured from riding edge of PMA\_RX\_CLK0.

### Table 34. RGMII and RTBI AC Timing Specifications (continued)

At recommended operating conditions with LV\_{DD} of 2.5 V  $\pm$  5%.

| Parameter/Condition                   | Symbol <sup>1</sup>                   | Min | Тур | Мах | Unit | Notes |

|---------------------------------------|---------------------------------------|-----|-----|-----|------|-------|

| GTX_CLK125 reference clock duty cycle | t <sub>G125H</sub> /t <sub>G125</sub> | 47  | _   | 53  | %    | —     |

Notes:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (Rx) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design will require clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

- 5. Duty cycle reference is LV<sub>DD</sub>/2.

- 6. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

- 7. In rev. 2.1 silicon, due to errata, t<sub>SKRGTKHDX</sub> minimum is –0.65 ns for UCC2 option 1 and –0.9 for UCC2 option 2, and t<sub>SKRGTKHDV</sub> maximum is 0.75 ns for UCC1 and UCC2 option 1 and 0.85 for UCC2 option 2. UCC1 does meet t<sub>SKRGTKHDX</sub> minimum for rev. 2.1 silicon.

Figure 19 shows the RGMII and RTBI AC timing and multiplexing diagrams.

Figure 19. RGMII and RTBI AC Timing and Multiplexing Diagrams

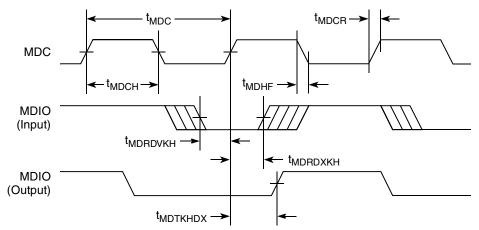

### Table 36. MII Management AC Timing Specifications (continued)

At recommended operating conditions with LV\_{DD} is 3.3 V  $\pm$  10%.

| Parameter/Condition | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Notes |

|---------------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time       | t <sub>MDHF</sub>   | _   | _   | 10  | ns   |       |

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDRDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- This parameter is dependent on the csb\_clk speed (that is, for a csb\_clk of 267 MHz, the maximum frequency is 8.3 MHz and the minimum frequency is 1.2 MHz; for a csb\_clk of 375 MHz, the maximum frequency is 11.7 MHz and the minimum frequency is 1.7 MHz).

- 3. This parameter is dependent on the ce\_clk speed (that is, for a ce\_clk of 200 MHz, the delay is 90 ns and for a ce\_clk of 300 MHz, the delay is 63 ns).

### Figure 20 shows the MII management AC timing diagram.

Figure 20. MII Management Interface Timing Diagram

### 8.3.3 IEEE 1588 Timer AC Specifications

Table 37 provides the IEEE 1588 timer AC specifications.

| Parameter                    | Symbol              | Min | Max | Unit | Notes |

|------------------------------|---------------------|-----|-----|------|-------|

| Timer clock frequency        | t <sub>TMRCK</sub>  | 0   | 70  | MHz  | 1     |

| Input setup to timer clock   | t <sub>TMRCKS</sub> | —   | —   | _    | 2, 3  |

| Input hold from timer clock  | t <sub>TMRCKH</sub> | —   | —   | _    | 2, 3  |

| Output clock to output valid | <sup>t</sup> GCLKNV | 0   | 6   | ns   | _     |

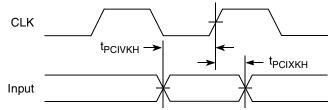

| Parameter                      | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|--------------------------------|---------------------|-----|-----|------|-------|

| Clock to output valid          | t <sub>PCKHOV</sub> | _   | 11  | ns   | 2     |

| Output hold from clock         | t <sub>PCKHOX</sub> | 2   | —   | ns   | 2     |

| Clock to output high impedance | t <sub>PCKHOZ</sub> | —   | 14  | ns   | 2, 3  |

| Input setup to clock           | t <sub>PCIVKH</sub> | 7.0 | —   | ns   | 2, 4  |

| Input hold from clock          | t <sub>PCIXKH</sub> | 0.3 |     | ns   | 2, 4  |

### Table 47. PCI AC Timing Specifications at 33 MHz

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the PCI\_SYNC\_IN clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

3. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

4. Input timings are measured at the pin.

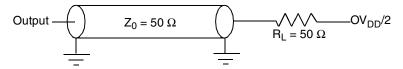

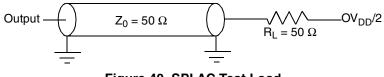

Figure 35 provides the AC test load for PCI.

Figure 35. PCI AC Test Load

Figure 36 shows the PCI input AC timing conditions.

Figure 36. PCI Input AC Timing Measurement Conditions

SPI

## 16.1 SPI DC Electrical Characteristics

Table 54 provides the DC electrical characteristics for the device SPI.

| Characteristic      | Symbol          | Condition                        | Min  | Мах                    | Unit |

|---------------------|-----------------|----------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA        | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | l <sub>OL</sub> = 6.0 mA         | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA         | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                                | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \leq V_{IN} \leq OV_{DD}$ | _    | ±10                    | μA   |

## 16.2 SPI AC Timing Specifications

Table 55 and provide the SPI input and output AC timing specifications.

| Table 55. | SPI AC 1 | Timing Specifications <sup>1</sup> |

|-----------|----------|------------------------------------|

|-----------|----------|------------------------------------|

| Characteristic                                           | Symbol <sup>2</sup>                        | Min | Мах | Unit |

|----------------------------------------------------------|--------------------------------------------|-----|-----|------|

| SPI outputs—Master mode (internal clock) delay           | t <sub>NIKHOX</sub><br>t <sub>NIKHOV</sub> | 0.4 | 8   | ns   |

| SPI outputs—Slave mode (external clock) delay            | t <sub>NEKHOX</sub><br>t <sub>NEKHOV</sub> | 2   | 8   | ns   |

| SPI inputs—Master mode (internal clock) input setup time | t <sub>NIIVKH</sub>                        | 8   | —   | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub>                        | 0   | —   | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub>                        | 4   | —   | ns   |

| SPI inputs—Slave mode (external clock) input hold time   | t <sub>NEIXKH</sub>                        | 2   | —   | ns   |

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).</sub>

Figure 40 provides the AC test load for the SPI.

Figure 40. SPI AC Test Load

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement must exclude any effect of mark on top surface of package.

- 6. Distance from the seating plane to the encapsulant material.

## 21.3 Pinout Listings

Refer to AN3097, "MPC8360/MPC8358E PowerQUICC Design Checklist," for proper pin termination and usage.

Table 65 shows the pin list of the MPC8358E PBGA package.

| Signal                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                                          | Pin Type | Power<br>Supply    | Notes |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

|                            | DDR SDRAM Memory Controller Interface                                                                                                                                                                                                                                                                                                                                       | ł        | <u> </u>           | ļ     |

| MEMC_MDQ[0:63]             | AD20, AG24, AF24, AH24, AF23, AE22, AH26, AD21,<br>AH25, AD22, AF27, AB24, AG25, AC22, AE25, AC24,<br>AD25, AB25, AC25, AG28, AD26, AE23, AG26, AC26,<br>AD27, V25, AA28, AA25, Y26, W27, U24, W24, E28,<br>H24, E26, D25, G27, H25, G26, F26, F27, F25, D26, F24,<br>G25, E27, D27, C28, C27, F22, B26, F21, B28, E22, D24,<br>C24, A25, E20, F20, D20, A23, C21, C23, E19 | I/O      | GV <sub>DD</sub>   | _     |

| MEMC_MECC[0:7]             | N26, N24, J26, H28, N28, P24, L26, K24                                                                                                                                                                                                                                                                                                                                      | I/O      | GV <sub>DD</sub>   | -     |

| MEMC_MDM[0:8]              | AG23, AD23, AE26, V28, G28, D28, D23, B24, U27                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MDQS[0:8]             | AH23, AH27, AF28, T28, H26, E25, B25, A24, R28                                                                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub>   | —     |

| MEMC_MBA[0:2]              | V26, W28, Y28                                                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MA[0:14]              | L25, M25, M24, K28, P28, T24, M27, R25, P25, L28,<br>U26, M28, L27, K27, H27                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MODT[0:3]             | AE21, AC19, E23, B23                                                                                                                                                                                                                                                                                                                                                        | —        | GV <sub>DD</sub>   | 6     |

| MEMC_MWE                   | R27                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MRAS                  | W25                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCAS                  | R24                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCS[0:3]              | T26, U28, J25, F28                                                                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCKE[0:1]             | AD24, AE28                                                                                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCK[0:5]              | AG22, AG27, A26, C26, P26, E21                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCK[0:5]              | AF22, AF26, A27, B27, N27, D22                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MDIC[0:1]                  | F19, AA27                                                                                                                                                                                                                                                                                                                                                                   | I/O      | GV <sub>DD</sub>   | 11    |

|                            | PCI                                                                                                                                                                                                                                                                                                                                                                         |          |                    | •     |

| PCI_INTA/<br>PF[5]         | R3                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | 2     |

| PCI_RESET_OUT/<br>PF[6]    | P6                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_AD[0:31]/<br>PG[0:31]  | AB5, AC5, AG1, AA5, AF2, AD4, Y6, AF1, AE2, AC4,<br>AD3, AE1, Y4, AC3, AD2, AD1, AB2, Y3, AA1, Y1, W1,<br>V6, W3, V4, T5, W2, V5, V1, U4, V2, U2, T2                                                                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_C_BE[0:3]/<br>PF[7:10] | Y5, AC2, Y2, U5                                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub>   | _     |

### Table 65. MPC8358E PBGA Pinout Listing

Package and Pin Listings

| Signal                       | Package Pin Number                | Pin Type | Power              | Notes    |

|------------------------------|-----------------------------------|----------|--------------------|----------|

|                              |                                   |          | Supply             |          |

| LGPL2/<br>LSDRAS/            | AH19                              | 0        | OV <sub>DD</sub>   | _        |

| LOE                          |                                   |          |                    |          |

| LGPL3/                       | AE18                              | I/O      | OV <sub>DD</sub>   | _        |

| LSDCAS/<br>cfg_reset_source2 |                                   |          |                    |          |

| LGPL4/                       | AG19                              | I/O      | OV <sub>DD</sub>   | <u> </u> |

| LGTA/                        | halo                              | 1,0      | 0,00               |          |

| LUPWAIT/                     |                                   |          |                    |          |

| LPBSE<br>LGPL5/              |                                   |          | 01/                |          |

| cfg_clkin_div                | AF19                              | I/O      | OV <sub>DD</sub>   | _        |

|                              | AD8                               | 0        | OV <sub>DD</sub>   |          |

| LCLK[0]                      | AC9                               | 0        | OV <sub>DD</sub>   | _        |

| LCLK[1]/                     | AG6                               | 0        | OV <sub>DD</sub>   |          |

| LCS[6]                       |                                   |          |                    |          |

| LCLK[2]/<br>LCS[7]           | AE7                               | 0        | OV <sub>DD</sub>   | —        |

| LSYNC_OUT                    | AG4                               | 0        | OV <sub>DD</sub>   |          |

| LSYNC_IN                     | AC8                               |          | OV <sub>DD</sub>   |          |

|                              | Programmable Interrupt Controller |          | 0.00               |          |

|                              |                                   |          |                    |          |

| MCP_OUT                      | AG3                               | 0        | OV <sub>DD</sub>   | 2        |

| IRQ0/<br>MCP_IN              | AH4                               |          | OV <sub>DD</sub>   | _        |

| IRQ[1:2]                     | AG5, AH5                          | I/O      | OV <sub>DD</sub>   | —        |

| IRQ[3]/<br>CORE_SRESET       | AD7                               | I/O      | OV <sub>DD</sub>   | -        |

| IRQ[4:5]                     | AC7, AD6                          | I/O      | OV <sub>DD</sub>   | _        |

| IRQ[6:7]                     | AC6, AC10                         | I/O      | OV <sub>DD</sub>   | —        |

|                              | DUART                             | ·        |                    |          |

| UART1_SOUT                   | AE3                               | 0        | OV <sub>DD</sub>   | _        |

| UART1_SIN                    | AE4                               | I/O      | OV <sub>DD</sub>   | —        |

| UART1_CTS                    | AG2                               | I/O      | OV <sub>DD</sub>   | _        |

| UART1_RTS                    | AA6                               | 0        | OV <sub>DD</sub>   | _        |

|                              | I <sup>2</sup> C Interface        | 1        |                    |          |

| IIC1_SDA                     | AB6                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC1_SCL                     | AD5                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SDA                     | AF3                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SCL                     | AH2                               | I/O      | OV <sub>DD</sub>   | 2        |

|                              | QUICC Engine                      | ·        |                    |          |

| CE_PA[0]                     | F6                                | I/O      | LV <sub>DD</sub> 0 | _        |

|                              |                                   |          |                    | 1        |

### Table 65. MPC8358E PBGA Pinout Listing (continued)

| Signal             | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin Type                              | Power<br>Supply    | Notes |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------|

| TDI                | AE8                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | OV <sub>DD</sub>   | 4     |

| TDO                | AG7                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                     | OV <sub>DD</sub>   | 3     |

| TMS                | AH7                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | OV <sub>DD</sub>   | 4     |

| TRST               | AG8                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | OV <sub>DD</sub>   | 4     |

|                    | Test                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |                    |       |

| TEST               | AF9                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | OV <sub>DD</sub>   | 7     |

| TEST_SEL           | AE27                                                                                                                                                                                                                                                                                                                                                                                                                                | I                                     | GV <sub>DD</sub>   | 9     |

|                    | PMC                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | I                  | 1     |

| QUIESCE            | AF4                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                     | OV <sub>DD</sub>   | —     |

|                    | System Control                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | I                  | 1     |

| PORESET            | AE9                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | OV <sub>DD</sub>   | _     |

| HRESET             | AG9                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                                   | OV <sub>DD</sub>   | 1     |

| SRESET             | AH10                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O                                   | OV <sub>DD</sub>   | 2     |

|                    | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |                    |       |

| THERM0             | K25                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                     | GV <sub>DD</sub>   | —     |

| THERM1             | AA26                                                                                                                                                                                                                                                                                                                                                                                                                                | I                                     | GV <sub>DD</sub>   | —     |

|                    | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | I                  | 1     |

| AV <sub>DD</sub> 1 | AF8                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>LBIU DLL<br>(1.2 V)      | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | AH8                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>CE PLL<br>(1.2 V)        | AV <sub>DD</sub> 2 | _     |

| AV <sub>DD</sub> 5 | AB26                                                                                                                                                                                                                                                                                                                                                                                                                                | Power for<br>e300 PLL<br>(1.2 V)      | AV <sub>DD</sub> 5 | _     |

| AV <sub>DD</sub> 6 | AH9                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>system<br>PLL (1.2<br>V) | AV <sub>DD</sub> 6 | _     |

| GND                | C16, D11, D21, E24, F7, J10, J12, J15, J16, J17, J28,<br>K11, K13, K14, K17, K18, L4, L9, L11, L12, L13, L14,<br>L15, L16, L17, L18, L19, L24, M10, M11, M14, M15, M18,<br>M19, N11, N18, N25, P9, P11, P18, P19, R9, R11, R14,<br>R15, R18, R19, R26, T10, T11, T14, T15, T18, T25, U10,<br>U11, U18, V9, V11, V14, V15, V18, V24, V27, W18, W19,<br>Y11, Y14, Y18, Y19, Y25, Y27, AB4, AB27, AC27, AE20,<br>AE24, AF5, AF15, AG10 | _                                     | _                  | _     |

NP

Note that *lb\_clk* is not the external local bus or DDRC2 frequency; *lb\_clk* passes through the a LB clock divider to create the external local bus clock outputs (LSYNC\_OUT and LCLK[0:2]). The LB clock divider ratio is controlled by LCRR[CLKDIV].

In addition, some of the internal units may be required to be shut off or operate at lower frequency than the  $csb\_clk$  frequency. Those units have a default clock ratio that can be configured by a memory mapped register after the device comes out of reset. Table 66 specifies which units have a configurable clock frequency.

| Unit                | Default<br>Frequency | Options                                             |

|---------------------|----------------------|-----------------------------------------------------|

| Security core       | csb_clk/3            | Off, csb_clk <sup>1</sup> , csb_clk/2,<br>csb_clk/3 |

| PCI and DMA complex | csb_clk              | Off, csb_clk                                        |

### Table 66. Configurable Clock Units

<sup>1</sup> With limitation, only for slow csb\_clk rates, up to 166 MHz.

Table 67 provides the operating frequencies for the PBGA package under recommended operating conditions (see Table 2). All frequency combinations shown in the table below may not be available. Maximum operating frequencies depend on the part ordered, see Section 25.1, "Part Numbers Fully Addressed by this Document," for part ordering details and contact your Freescale sales representative or authorized distributor for more information.

### Table 67. Operating Frequencies for the PBGA Package

| Characteristic <sup>1</sup>                           | 400 MHz   | Unit |

|-------------------------------------------------------|-----------|------|

| e300 core frequency (core_clk)                        | 266–400   | MHz  |

| Coherent system bus frequency<br>( <i>csb_clk</i> )   | 133–266   | MHz  |

| QUICC Engine frequency ( <i>ce_clk</i> )              | 266–400   | MHz  |

| DDR and DDR2 memory bus frequency (MCLK) <sup>2</sup> | 100–133   | MHz  |

| Local bus frequency (LCLK <i>n</i> ) <sup>3</sup>     | 16.67–133 | MHz  |

| PCI input frequency (CLKIN or PCI_CLK)                | 25–66.67  | MHz  |

| Security core maximum internal operating frequency    | 133       | MHz  |

<sup>1</sup> The CLKIN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCLK, LCLK[0:2], and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies.

<sup>2</sup> The DDR data rate is 2x the DDR memory bus frequency.

<sup>3</sup> The local bus frequency is 1/2, 1/4, or 1/8 of the *lb\_clk* frequency (depending on LCRR[CLKDIV]) which is in turn 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

# 22.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] and RCWL[SVCOD] parameters. Table 68 shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0000       | × 16                                |

| 0001       | Reserved                            |

| 0010       | × 2                                 |

| 0011       | × 3                                 |

| 0100       | × 4                                 |

| 0101       | × 5                                 |

| 0110       | × 6                                 |

| 0111       | × 7                                 |

| 1000       | × 8                                 |

| 1001       | × 9                                 |

| 1010       | × 10                                |

| 1011       | × 11                                |

| 1100       | × 12                                |

| 1101       | × 13                                |

| 1110       | × 14                                |

| 1111       | × 15                                |

### Table 68. System PLL Multiplication Factors

The RCWL[SVCOD] denotes the system PLL VCO internal frequency as shown in Table 69.

# Table 69. System PLL VCO Divider

| RCWL[SVCOD] | VCO Divider |

|-------------|-------------|

| 00          | 4           |

| 01          | 8           |

| 10          | 2           |

| 11          | Reserved    |

### NOTE

The VCO divider must be set properly so that the system VCO frequency is in the range of 600–1400 MHz.

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL<br>Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF]) |

|-------------|-------------|-------------------------------------------------------------------------------|

| 01011       | 1           | × 5.5                                                                         |

| 01101       | 1           | × 6.5                                                                         |

| 01111       | 1           | × 7.5                                                                         |

| 10001       | 1           | × 8.5                                                                         |

| 10011       | 1           | × 9.5                                                                         |

| 10101       | 1           | × 10.5                                                                        |

| 10111       | 1           | × 11.5                                                                        |

| 11001       | 1           | × 12.5                                                                        |

| 11011       | 1           | × 13.5                                                                        |

| 11101       | 1           | × 14.5                                                                        |

Table 72. QUICC Engine Block PLL Multiplication Factors (continued)

Note:

1. Reserved modes are not listed.

The RCWL[CEVCOD] denotes the QUICC Engine Block PLL VCO internal frequency as shown in Table 73.

Table 73. QUICC Engine Block PLL VCO Divider

| RCWL[CEVCOD] | VCO Divider |

|--------------|-------------|

| 00           | 4           |

| 01           | 8           |

| 10           | 2           |

| 11           | Reserved    |

### NOTE

The VCO divider (RCWL[CEVCOD]) must be set properly so that the QUICC Engine block VCO frequency is in the range of 600–1400 MHz. The QUICC Engine block frequency is not restricted by the CSB and core frequencies. The CSB, core, and QUICC Engine block frequencies should be selected according to the performance requirements.

The QUICC Engine block VCO frequency is derived from the following equations:

$ce_clk = (primary clock input \times CEPMF) \div (1 + CEPDF)$

QE VCO Frequency =  $ce_clk \times$  VCO divider  $\times$  (1 + CEPDF)

Clocking

## 22.4 Suggested PLL Configurations

To simplify the PLL configurations, the device might be separated into two clock domains. The first domain contains the CSB PLL and the core PLL. The core PLL is connected serially to the CSB PLL, and has the csb\_clk as its input clock. The second clock domain has the QUICC Engine block PLL. The clock domains are independent, and each of their PLLs are configured separately. Both of the domains has one common input clock. Table 74 shows suggested PLL configurations for 33 and 66 MHz input clocks and illustrates each of the clock domains separately. Any combination of clock domains setting with same input clock are valid. Refer to Section 22, "Clocking," for the appropriate operating frequencies for your device.

| Conf<br>No. <sup>1</sup> | SPMF                             | CORE<br>PLL | CEPMF | CEPDF | Input<br>Clock Freq<br>(MHz) | CSB Freq<br>(MHz) | Core Freq<br>(MHz) | QUICC<br>Engine<br>Freq (MHz) | 400<br>(MHz) | 533<br>(MHz) | 667<br>(MHz) |

|--------------------------|----------------------------------|-------------|-------|-------|------------------------------|-------------------|--------------------|-------------------------------|--------------|--------------|--------------|

|                          | 33 MHz CLKIN/PCI_SYNC_IN Options |             |       |       |                              |                   |                    |                               |              |              |              |

| s1                       | 0100                             | 0000100     | æ     | æ     | 33                           | 133               | 266                | —                             | ~            | ∞            | 8            |

| s2                       | 0100                             | 0000101     | 8     | 8     | 33                           | 133               | 333                |                               | ~            | ∞            | 8            |

| s3                       | 0101                             | 0000100     | 8     | æ     | 33                           | 166               | 333                | _                             | ∞            | ∞            | ∞            |

| s4                       | 0101                             | 0000101     | 8     | æ     | 33                           | 166               | 416                | _                             | —            | ~            | ∞            |

| s5                       | 0110                             | 0000100     | 8     | æ     | 33                           | 200               | 400                | _                             | ∞            | ~            | ∞            |

| s6                       | 0110                             | 0000110     | æ     | æ     | 33                           | 200               | 600                | _                             |              |              | ∞            |

| s7                       | 0111                             | 0000011     | æ     | æ     | 33                           | 233               | 350                | _                             | ∞            | ∞            | 8            |

| s8                       | 0111                             | 0000100     | æ     | æ     | 33                           | 233               | 466                | _                             | —            | ∞            | 8            |

| s9                       | 0111                             | 0000101     | æ     | æ     | 33                           | 233               | 583                | _                             | —            | _            | 8            |

| s10                      | 1000                             | 0000011     | æ     | æ     | 33                           | 266               | 400                | _                             | ∞            | 8            | 8            |

| s11                      | 1000                             | 0000100     | æ     | æ     | 33                           | 266               | 533                | -                             | —            | 8            | 8            |

| s12                      | 1000                             | 0000101     | æ     | æ     | 33                           | 266               | 667                | -                             | —            | —            | 8            |

| s13                      | 1001                             | 0000010     | æ     | æ     | 33                           | 300               | 300                | -                             | 8            | 8            | 8            |

| s14                      | 1001                             | 0000011     | æ     | æ     | 33                           | 300               | 450                | -                             | —            | 8            | 8            |

| s15                      | 1001                             | 0000100     | æ     | æ     | 33                           | 300               | 600                |                               | —            | —            | 8            |

| s16                      | 1010                             | 0000010     | 8     | æ     | 33                           | 333               | 333                |                               | 8            | 8            | 8            |

| s17                      | 1010                             | 0000011     | æ     | æ     | 33                           | 333               | 500                | -                             | —            | 8            | 8            |

| s18                      | 1010                             | 0000100     | æ     | æ     | 33                           | 333               | 667                | _                             | —            | —            | 8            |

| c1                       | æ                                | æ           | 01001 | 0     | 33                           | —                 | _                  | 300                           | 8            | 8            | 8            |

| c2                       | æ                                | æ           | 01100 | 0     | 33                           | —                 | —                  | 400                           | 8            | 8            | 8            |

| c3                       | æ                                | æ           | 01110 | 0     | 33                           | —                 | —                  | 466                           | —            | 8            | 8            |

| c4                       | æ                                | æ           | 01111 | 0     | 33                           |                   |                    | 500                           | —            | ~            | ~            |

Thermal

### 23.2.3 Experimental Determination of Junction Temperature

To determine the junction temperature of the device in the application after prototypes are available, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (°C)

$T_T$  = thermocouple temperature on top of package (°C)

$\Psi_{JT}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

## 23.2.4 Heat Sinks and Junction-to-Ambient Thermal Resistance

In some application environments, a heat sink will be required to provide the necessary thermal management of the device. When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the airflow around the device, the interface material, the mounting arrangement on printed-circuit board, or change the thermal dissipation on the printed-circuit board surrounding the device.

To illustrate the thermal performance of the devices with heat sinks, the thermal performance has been simulated with a few commercially available heat sinks. The heat sink choice is determined by the application environment (temperature, airflow, adjacent component power dissipation) and the physical space available. Because there is not a standard application environment, a standard heat sink is not required.

### 23.3.1 Experimental Determination of the Junction Temperature with a Heat Sink

When heat sink is used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

$$T_J = T_C + (R_{\theta JC} \times P_D)$$

where:

$T_J$  = junction temperature (°C)  $T_C$  = case temperature of the package (°C)  $R_{\theta JC}$  = junction to case thermal resistance (°C/W)  $P_D$  = power dissipation (W)

# 24 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8358E. Additional information can be found in *MPC8360E/MPC8358E PowerQUICC Design Checklist* (AN3097).

## 24.1 System Clocking

The device includes two PLLs, as follows.

- The platform PLL (AV<sub>DD</sub>1) generates the platform clock from the externally supplied CLKIN input. The frequency ratio between the platform and CLKIN is selected using the platform PLL ratio configuration bits as described in Section 22.1, "System PLL Configuration."

- The e300 core PLL (AV<sub>DD</sub>2) generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 22.2, "Core PLL Configuration."

## 24.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, respectively). The AV<sub>DD</sub> level should always be equivalent to  $V_{DD}$ , and preferably these voltages will be derived directly from  $V_{DD}$  through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide five independent filter circuits as illustrated in Figure 54, one to each of the five  $AV_{DD}$  pins. By providing independent filters to each PLL, the opportunity to cause noise injection from one PLL to the other is reduced.

**Document Revision History**

# 26 Document Revision History

Table 80 provides a revision history for this hardware specification.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|