#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                 |

|---------------------------------|--------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                           |

| Speed                           | 400MHz                                                                   |

| Co-Processors/DSP               | Communications; QUICC Engine                                             |

| RAM Controllers                 | DDR, DDR2                                                                |

| Graphics Acceleration           | No                                                                       |

| Display & Interface Controllers | -                                                                        |

| Ethernet                        | 10/100/1000Mbps (1)                                                      |

| SATA                            | -                                                                        |

| USB                             | USB 1.x (1)                                                              |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                         |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                        |

| Package / Case                  | 668-BBGA Exposed Pad                                                     |

| Supplier Device Package         | 668-PBGA-PGE (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8358czqagdga |

|                                 |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the Freescale processor families implementing the Power Architecture<sup>TM</sup> technology

- QUICC Engine unit

- Two 32-bit RISC controllers for flexible support of the communications peripherals, each operating up to 400 MHz (for the MPC8358E)

- Serial DMA channel for receive and transmit on all serial channels

- QUICC Engine module peripheral request interface (for SEC, PCI, IEEE Std. 1588<sup>TM</sup>)

- Six UCCs on the MPC8358E supporting the following protocols and interfaces (not all of them simultaneously):

- IEEE 1588 protocol supported

- 10/100 Mbps Ethernet/IEEE Std. 802.3<sup>TM</sup> CDMA/CS interface through a media-independent interface (MII, RMII, RGMII)<sup>1</sup>

- 1000 Mbps Ethernet/IEEE 802.3 CDMA/CS interface through a media-independent interface (GMII, RGMII, TBI, RTBI) on UCC1 and UCC2

- 9.6-Kbyte jumbo frames

- ATM full-duplex SAR, up to 622 Mbps (OC-12/STM-4), AAL0, AAL1, and AAL5 in accordance ITU-T I.363.5

- ATM AAL2 CPS, SSSAR, and SSTED up to 155 Mbps (OC-3/STM-1) Mbps full duplex (with 4 CPS packets per cell) in accordance ITU-T I.366.1 and I.363.2

- ATM traffic shaping for CBR, VBR, UBR, and GFR traffic types compatible with ATM forum TM4.1 for up to 64-Kbyte simultaneous ATM channels

- ATM AAL1 structured and unstructured circuit emulation service (CES 2.0) in accordance with ITU-T I.163.1 and ATM Forum af-vtoa-00-0078.000

- IMA (Inverse Multiplexing over ATM) for up to 31 IMA links over 8 IMA groups in accordance with the ATM forum AF-PHY-0086.000 (Version 1.0) and AF-PHY-0086.001 (Version 1.1)

- ATM Transmission Convergence layer support in accordance with ITU-T I.432

- ATM OAM handling features compatible with ITU-T I.610

- PPP, Multi-Link (ML-PPP), Multi-Class (MC-PPP) and PPP mux in accordance with the following RFCs: 1661, 1662, 1990, 2686, and 3153

- IP support for IPv4 packets including TOS, TTL, and header checksum processing

- Ethernet over first mile IEEE 802.3ah

- Shim header

- Ethernet-to-Ethernet/AAL5/AAL2 inter-working

- L2 Ethernet switching using MAC address or IEEE Std. 802.1P/Q<sup>™</sup> VLAN tags

<sup>1.</sup>SMII or SGMII media-independent interface is not currently supported.

- Advanced encryption standard unit (AESU)

- Implements the Rinjdael symmetric key cipher

- Key lengths of 128, 192, and 256 bits, two key

- ECB, CBC, CCM, and counter modes

- ARC four execution unit (AFEU)

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160-, 224-, or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either SHA or MD5 algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Storage/NAS XOR parity generation accelerator for RAID applications

- DDR SDRAM memory controller on the MPC8358E

- Programmable timing supporting both DDR1 and DDR2 SDRAM

- On the MPC8358E, the DDR bus can be configured as a 32- or 64-bit bus

- 32- or 64-bit data interface, up to 266 MHz (for the MPC8358E) data rate

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbits to 1 Gigabit with  $\times 8/\times 16$  data ports

- Full ECC support

- Page mode support (up to 16 simultaneous open pages for DDR1, up to 32 simultaneous open pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode support for self refresh SDRAM

- Supports auto refreshing

- Supports source clock mode

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- External driver impedance calibration

- On-die termination (ODT)

- PCI interface

- PCI Specification Revision 2.3 compatible

# 2.1.2 Power Supply Voltage Specification

Table 2 provides the recommended operating conditions for the device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                                                                 | Symbol             | Recommended<br>Value             | Unit | Notes |

|------------------------------------------------------------------------------------------------|--------------------|----------------------------------|------|-------|

| Core supply voltage                                                                            | V <sub>DD</sub>    | 1.2 V ± 60 mV                    | V    | 1     |

| PLL supply voltage                                                                             | AV <sub>DD</sub>   | 1.2 V ± 60 mV                    | V    | 1     |

| DDR and DDR2 DRAM I/O supply voltage<br>DDR<br>DDR2                                            | GV <sub>DD</sub>   | 2.5 V ± 125 mV<br>1.8 V ± 90 mV  | V    | _     |

| Three-speed Ethernet I/O supply voltage                                                        | LV <sub>DD</sub> 0 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    | —     |

| Three-speed Ethernet I/O supply voltage                                                        | LV <sub>DD</sub> 1 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    | _     |

| Three-speed Ethernet I/O supply voltage                                                        | LV <sub>DD</sub> 2 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    | —     |

| PCI, local bus, DUART, system control and power management, $I^2C$ , SPI, and JTAG I/O voltage | OV <sub>DD</sub>   | 3.3 V ± 330 mV                   | V    | —     |

| Junction temperature                                                                           | Τ <sub>J</sub>     | 0 to 105<br>-40 to 105           | °C   | _     |

### **Table 2. Recommended Operating Conditions**

Notes:

1. GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

Power Characteristics

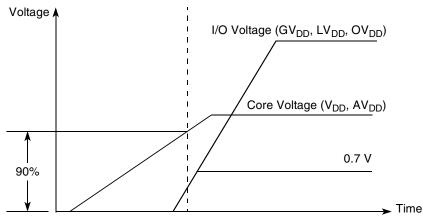

Figure 4. Power Sequencing Example

I/O voltage supplies ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) do not have any ordering requirements with respect to one another.

# 2.2.2 Power-Down Sequencing

The MPC8358E does not require the core supply voltage and I/O supply voltages to be powered down in any particular order.

# **3** Power Characteristics

The estimated typical power dissipation values are shown in Table 4.

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Frequency (MHz) |     | Unit | Notes   |

|-------------------------|------------------------|---------------------------------|-----------------|-----|------|---------|

| 266                     | 266                    | 266                             | 2.2             | 2.3 | w    | 2, 3, 4 |

| 400                     | 266                    | 266                             | 2.4             | 2.5 | w    | 2, 3, 4 |

| 400                     | 266                    | 400                             | 2.5             | 2.6 | W    | 2, 3, 4 |

| Table 4. | MPC8358E | PBGA | Core | Power   | Dissipation <sup>1</sup> |  |

|----------|----------|------|------|---------|--------------------------|--|

|          |          | DOA  | 0010 | 1 01101 | Dissipution              |  |

#### Notes:

1. The values do not include I/O supply power (OV<sub>DD</sub>,  $LV_{DD}$ ,  $GV_{DD}$ ) or  $AV_{DD}$ . For I/O power values, see Table 5.

2. Typical power is based on a voltage of  $V_{DD}$  = 1.2 V, a junction temperature of  $T_J$  = 105°C, and a Dhrystone benchmark application.

Thermal solutions will likely need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

4. Maximum power is based on a voltage of  $V_{DD}$  = 1.2 V, WC process, a junction  $T_J$  = 105°C, and an artificial smoke test.

| Interface       | Interface Operating<br>Frequency (MHz) | Max Interface Bit<br>Rate (Mbps) | Min QUICC Engine<br>Operating<br>Frequency <sup>1</sup> (MHz) | Notes |

|-----------------|----------------------------------------|----------------------------------|---------------------------------------------------------------|-------|

| UART/async HDLC | 3.68 (max internal ref clock)          | 115 (Kbps)                       | 20                                                            | —     |

| BISYNC          | 2 (max)                                | 2                                | 20                                                            | _     |

| USB             | 48 (ref clock)                         | 12                               | 96                                                            | —     |

### Table 12. QUICC Engine Block Operating Frequency Limitations (continued)

### Notes:

1. The QUICC Engine module needs to run at a frequency higher than or equal to what is listed in this table.

2. 'F' is the actual interface operating frequency.

3. The bit rate limit is independent of the data bus width (that is, the same for serial, nibble, or octal interfaces).

4. TDM in high-speed mode for serial data interface.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR and DDR2 SDRAM interface of the MPC8358E.

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

Table 13 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | —                         | ±10                       | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | _                         | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —     |

| MV <sub>REF</sub> input leakage current          | I <sub>VREF</sub> | —                         | ±10                       | μA   | —     |

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

DDR and DDR2 SDRAM

### Table 16 provides the DDR capacitance when $GV_{DD}(typ) = 2.5 V$ .

### Table 16. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | —   | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz, T<sub>A</sub> = 25°C, V<sub>OUT</sub> =  $GV_{DD}/2$ , V<sub>OUT</sub> (peak-to-peak) = 0.2 V.

# 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

# 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

Table 17 provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 \text{ V}.$

### Table 17. DDR2 SDRAM Input AC Timing Specifications for GV<sub>DD</sub>(typ) = 1.8 V

At recommended operating conditions with  $GV_{DD}$  of 1.8 V  $\pm$  5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —     |

Table 18 provides the input AC timing specifications for the DDR SDRAM interface when  $GV_{DD}(typ) = 2.5 \text{ V}.$

### Table 18. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 |                          | V    | —     |

Note:

1. Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n +  $\{0...7\}$ ] if  $0 \le n \le 7$ ) or ECC (MECC[ $\{0...7\}$ ] if n = 8).

#### UCC Ethernet Controller: Three-Speed Ethernet, MII Management

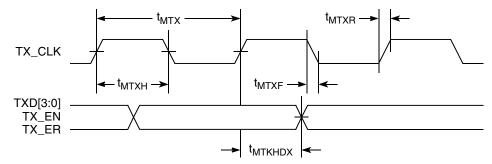

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

# 8.2.2.2 MII Receive AC Timing Specifications

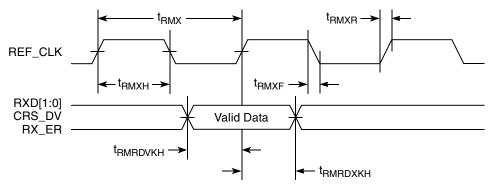

Table 29 provides the MII receive AC timing specifications.

### Table 29. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | —   | ns   |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>MRXR</sub>                   | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>MRXF</sub>                   | 1.0  | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

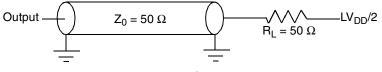

Figure 12 provides the AC test load.

Figure 12. AC Test Load

Figure 16 shows the RMII receive AC timing diagram.

Figure 16. RMII Receive AC Timing Diagram

# 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

# 8.2.4.1 TBI Transmit AC Timing Specifications

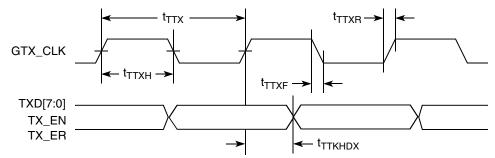

Table 32 provides the TBI transmit AC timing specifications.

### Table 32. TBI Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                   | Symbol <sup>1</sup>                        | Min | Тур | Мах     | Unit | Notes |

|---------------------------------------|--------------------------------------------|-----|-----|---------|------|-------|

| GTX_CLK clock period                  | t <sub>TTX</sub>                           | —   | 8.0 | —       | ns   | —     |

| GTX_CLK duty cycle                    | t <sub>TTXH</sub> /t <sub>TTX</sub>        | 40  | —   | 60      | %    | —     |

| GTX_CLK to TBI data TCG[9:0] delay    | <sup>t</sup> тткнdх<br><sup>t</sup> тткнdv | 0.9 | —   | <br>5.0 | ns   |       |

| GTX_CLK clock rise time, (20% to 80%) | t <sub>TTXR</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK clock fall time, (80% to 20%) | t <sub>TTXF</sub>                          | —   | —   | 1.0     | ns   | —     |

| GTX_CLK125 reference clock period     | t <sub>G125</sub>                          | —   | 8.0 | —       | ns   | 2     |

| GTX_CLK125 reference clock duty cycle | t <sub>G125H</sub> /t <sub>G125</sub>      | 45  | —   | 55      | ns   | —     |

### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. This symbol is used to represent the external GTX\_CLK125 and does not follow the original symbol naming convention.

#### UCC Ethernet Controller: Three-Speed Ethernet, MII Management

Figure 17 shows the TBI transmit AC timing diagram.

Figure 17. TBI Transmit AC Timing Diagram

# 8.2.4.2 TBI Receive AC Timing Specifications

Table 33 provides the TBI receive AC timing specifications.

### Table 33. TBI Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min | Тур  | Max | Unit | Notes |

|--------------------------------------------------------|-------------------------------------|-----|------|-----|------|-------|

| PMA_RX_CLK clock period                                | t <sub>TRX</sub>                    | _   | 16.0 | _   | ns   | —     |

| PMA_RX_CLK skew                                        | t <sub>SKTRX</sub>                  | 7.5 | —    | 8.5 | ns   | —     |

| RX_CLK duty cycle                                      | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | —    | 60  | %    | —     |

| RCG[9:0] setup time to rising PMA_RX_CLK               | t <sub>TRDVKH</sub>                 | 2.5 | —    | _   | ns   | 2     |

| RCG[9:0] hold time to rising PMA_RX_CLK                | t <sub>TRDXKH</sub>                 | 1.0 | —    | —   | ns   | 2     |

| RX_CLK clock rise time, $V_{IL}(min)$ to $V_{IH}(max)$ | t <sub>TRXR</sub>                   | 0.7 | —    | 2.4 | ns   | —     |

| RX_CLK clock fall time, $V_{IH}(max)$ to $V_{IL}(min)$ | t <sub>TRXF</sub>                   | 0.7 | _    | 2.4 | ns   | _     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub>

- 2. Setup and hold time of even numbered RCG are measured from riding edge of PMA\_RX\_CLK1. Setup and hold time of odd numbered RCG are measured from riding edge of PMA\_RX\_CLK0.

# 8.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI, and RTBI are specified in Section 8.1, "Three-Speed Ethernet Controller (10/100/1000 Mbps)— GMII/MII/RMII/TBI/RGMII/RTBI Electrical Characteristics."

# 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 35.

| Parameter              | Symbol           | Cond                       | itions                 | Min  | Мах                    | Unit |

|------------------------|------------------|----------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | -                          | _                      | 2.97 | 3.63                   | V    |

| Output high voltage    | V <sub>OH</sub>  | $I_{OH} = -1.0 \text{ mA}$ | OV <sub>DD</sub> = Min | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA   | OV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | -                          | _                      | 2.00 | —                      | V    |

| Input low voltage      | V <sub>IL</sub>  | -                          | _                      | —    | 0.80                   | V    |

| Input current          | I <sub>IN</sub>  | 0 V ≤ V <sub>I</sub> ۱     | $V \le ON^{DD}$        | —    | ±10                    | μA   |

Table 35. MII Management DC Electrical Characteristics When Powered at 3.3 V

# 8.3.2 MII Management AC Electrical Specifications

Table 36 provides the MII management AC timing specifications.

### Table 36. MII Management AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> is 3.3 V  $\pm$  10%.

| Parameter/Condition        | Symbol <sup>1</sup>                          | Min     | Тур | Мах      | Unit | Notes |

|----------------------------|----------------------------------------------|---------|-----|----------|------|-------|

| MDC frequency              | f <sub>MDC</sub>                             | _       | 2.5 | _        | MHz  | 2     |

| MDC period                 | t <sub>MDC</sub>                             | —       | 400 | _        | ns   | —     |

| MDC clock pulse width high | t <sub>MDCH</sub>                            | 32      | _   | _        | ns   | —     |

| MDC to MDIO delay          | t <sub>MDTKHDX</sub><br>t <sub>MDTKHDV</sub> | 10<br>— | _   | —<br>110 | ns   | 3     |

| MDIO to MDC setup time     | t <sub>MDRDVKH</sub>                         | 10      | —   | _        | ns   | —     |

| MDIO to MDC hold time      | t <sub>MDRDXKH</sub>                         | 0       | _   | —        | ns   | —     |

| MDC rise time              | t <sub>MDCR</sub>                            | _       | _   | 10       | ns   | —     |

Local Bus

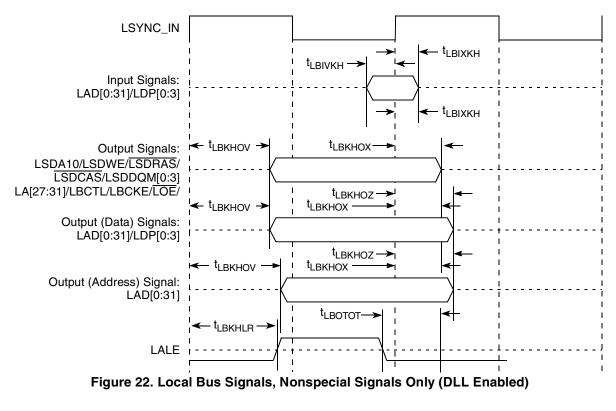

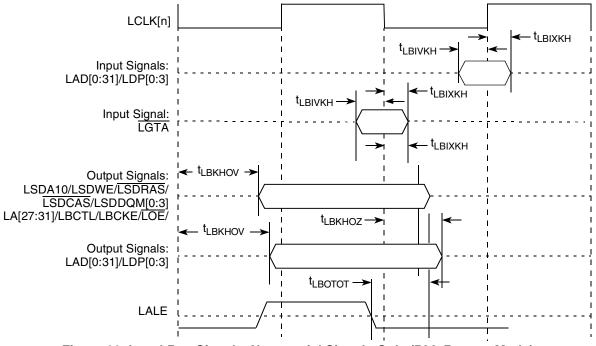

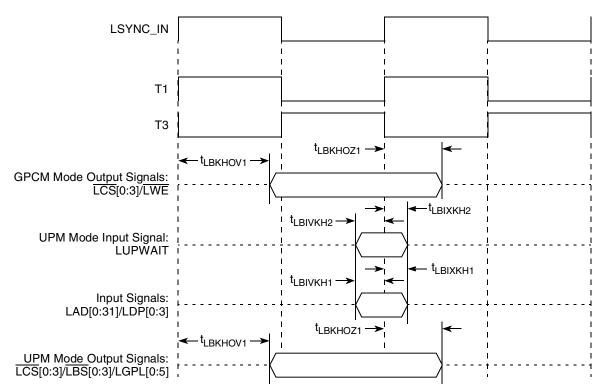

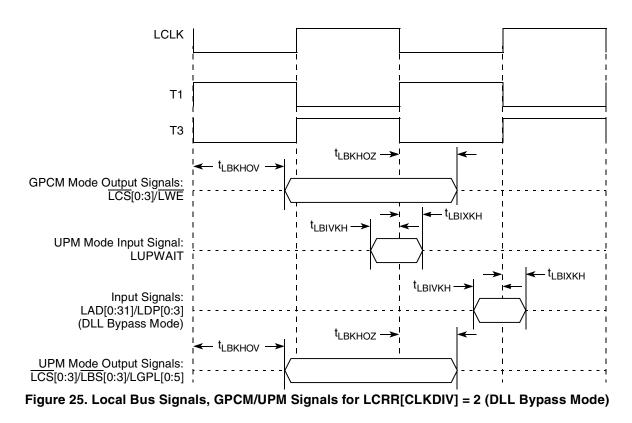

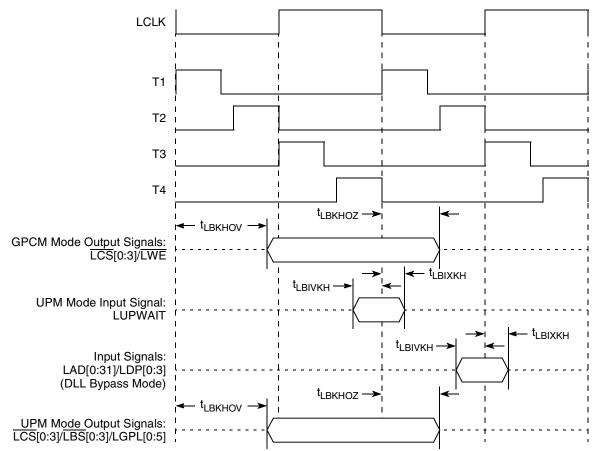

Figure 22 through Figure 27 show the local bus signals.

Figure 23. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

Figure 24. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 2 (DLL Enabled)

Local Bus

Figure 26. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (DLL Bypass Mode)

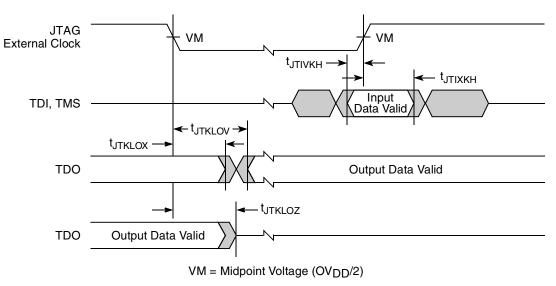

Figure 32 provides the test access port timing diagram.

Figure 32. Test Access Port Timing Diagram

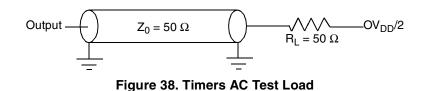

Figure 38 provides the AC test load for the timers.

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO of the MPC8358E.

# 14.1 GPIO DC Electrical Characteristics

Table 50 provides the DC electrical characteristics for the device GPIO.

| Characteristic      | Symbol          | Condition                                                          | Min  | Мах                    | Unit | Notes |

|---------------------|-----------------|--------------------------------------------------------------------|------|------------------------|------|-------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA                                          | 2.4  | —                      | V    | 1     |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA                                           | _    | 0.5                    | V    | 1     |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                                           | _    | 0.4                    | V    | 1     |

| Input high voltage  | V <sub>IH</sub> | —                                                                  | 2.0  | OV <sub>DD</sub> + 0.3 | V    | 1     |

| Input low voltage   | V <sub>IL</sub> | —                                                                  | -0.3 | 0.8                    | V    | —     |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{OV}_{\text{DD}}$ | —    | ±10                    | μA   | —     |

## Table 50. GPIO DC Electrical Characteristics

Note: This specification applies when operating from 3.3-V supply.

# 14.2 GPIO AC Timing Specifications

Table 51 provides the GPIO input and output AC timing specifications.

## Table 51. GPIO Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Тур | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

### Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any

external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement must exclude any effect of mark on top surface of package.

- 6. Distance from the seating plane to the encapsulant material.

# 21.3 Pinout Listings

Refer to AN3097, "MPC8360/MPC8358E PowerQUICC Design Checklist," for proper pin termination and usage.

Table 65 shows the pin list of the MPC8358E PBGA package.

| Signal                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                                          | Pin Type | Power<br>Supply    | Notes |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

|                            | DDR SDRAM Memory Controller Interface                                                                                                                                                                                                                                                                                                                                       |          |                    | •     |

| MEMC_MDQ[0:63]             | AD20, AG24, AF24, AH24, AF23, AE22, AH26, AD21,<br>AH25, AD22, AF27, AB24, AG25, AC22, AE25, AC24,<br>AD25, AB25, AC25, AG28, AD26, AE23, AG26, AC26,<br>AD27, V25, AA28, AA25, Y26, W27, U24, W24, E28,<br>H24, E26, D25, G27, H25, G26, F26, F27, F25, D26, F24,<br>G25, E27, D27, C28, C27, F22, B26, F21, B28, E22, D24,<br>C24, A25, E20, F20, D20, A23, C21, C23, E19 | I/O      | GV <sub>DD</sub>   | _     |

| MEMC_MECC[0:7]             | N26, N24, J26, H28, N28, P24, L26, K24                                                                                                                                                                                                                                                                                                                                      | I/O      | GV <sub>DD</sub>   | —     |

| MEMC_MDM[0:8]              | AG23, AD23, AE26, V28, G28, D28, D23, B24, U27                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MDQS[0:8]             | AH23, AH27, AF28, T28, H26, E25, B25, A24, R28                                                                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub>   | —     |

| MEMC_MBA[0:2]              | V26, W28, Y28                                                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MA[0:14]              | L25, M25, M24, K28, P28, T24, M27, R25, P25, L28,<br>U26, M28, L27, K27, H27                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MODT[0:3]             | AE21, AC19, E23, B23                                                                                                                                                                                                                                                                                                                                                        | —        | GV <sub>DD</sub>   | 6     |

| MEMC_MWE                   | R27                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MRAS                  | W25                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCAS                  | R24                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCS[0:3]              | T26, U28, J25, F28                                                                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCKE[0:1]             | AD24, AE28                                                                                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCK[0:5]              | AG22, AG27, A26, C26, P26, E21                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MEMC_MCK[0:5]              | AF22, AF26, A27, B27, N27, D22                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   | —     |

| MDIC[0:1]                  | F19, AA27                                                                                                                                                                                                                                                                                                                                                                   | I/O      | GV <sub>DD</sub>   | 11    |

|                            | PCI                                                                                                                                                                                                                                                                                                                                                                         |          |                    |       |

| PCI_INTA/<br>PF[5]         | R3                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | 2     |

| PCI_RESET_OUT/<br>PF[6]    | P6                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | -     |

| PCI_AD[0:31]/<br>PG[0:31]  | AB5, AC5, AG1, AA5, AF2, AD4, Y6, AF1, AE2, AC4,<br>AD3, AE1, Y4, AC3, AD2, AD1, AB2, Y3, AA1, Y1, W1,<br>V6, W3, V4, T5, W2, V5, V1, U4, V2, U2, T2                                                                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_C_BE[0:3]/<br>PF[7:10] | Y5, AC2, Y2, U5                                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub>   | —     |

## Table 65. MPC8358E PBGA Pinout Listing

Clocking

| RCWL[CEPMF] | RCWL[CEPDF] | QUICC Engine PLL<br>Multiplication Factor = RCWL[CEPMF]/<br>(1 + RCWL[CEPDF]) |

|-------------|-------------|-------------------------------------------------------------------------------|

| 00101       | 0           | × 5                                                                           |

| 00110       | 0           | × 6                                                                           |

| 00111       | 0           | × 7                                                                           |

| 01000       | 0           | × 8                                                                           |

| 01001       | 0           | × 9                                                                           |

| 01010       | 0           | × 10                                                                          |

| 01011       | 0           | × 11                                                                          |

| 01100       | 0           | × 12                                                                          |

| 01101       | 0           | × 13                                                                          |

| 01110       | 0           | × 14                                                                          |

| 01111       | 0           | × 15                                                                          |

| 10000       | 0           | × 16                                                                          |

| 10001       | 0           | × 17                                                                          |

| 10010       | 0           | × 18                                                                          |

| 10011       | 0           | × 19                                                                          |

| 10100       | 0           | × 20                                                                          |

| 10101       | 0           | × 21                                                                          |

| 10110       | 0           | × 22                                                                          |

| 10111       | 0           | × 23                                                                          |

| 11000       | 0           | × 24                                                                          |

| 11001       | 0           | × 25                                                                          |

| 11010       | 0           | × 26                                                                          |

| 11011       | 0           | × 27                                                                          |

| 11100       | 0           | × 28                                                                          |

| 11101       | 0           | × 29                                                                          |

| 11110       | 0           | × 30                                                                          |

| 11111       | 0           | × 31                                                                          |

| 00011       | 1           | × 1.5                                                                         |

| 00101       | 1           | × 2.5                                                                         |

| 00111       | 1           | × 3.5                                                                         |

| 01001       | 1           | × 4.5                                                                         |

Table 72. QUICC Engine Block PLL Multiplication Factors (continued)

| Table 76 shows heat sinks and | junction-to-ambient therma | l resistance for PBGA package. |

|-------------------------------|----------------------------|--------------------------------|

|                               |                            |                                |

| Host Sink Assuming Thormal Grosso                          | Air Flow           | 29 $	imes$ 29 mm PBGA |  |

|------------------------------------------------------------|--------------------|-----------------------|--|

| Heat Sink Assuming Thermal Grease                          | All Flow           | Thermal Resistance    |  |

| AAVID 30 $\times$ 30 $\times$ 9.4 mm Pin Fin               | Natural Convection | 12.6                  |  |

| AAVID 30 $	imes$ 30 $	imes$ 9.4 mm Pin Fin                 | 1 m/s              | 8.2                   |  |

| AAVID 30 $	imes$ 30 $	imes$ 9.4 mm Pin Fin                 | 2 m/s              | 7.0                   |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | Natural Convection | 10.5                  |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | 1 m/s              | 6.6                   |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | 2 m/s              | 6.1                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | Natural Convection | 9.0                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | 1 m/s              | 5.6                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | 2 m/s              | 5.1                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | Natural Convection | 9.0                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | 1 m/s              | 5.7                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | 2 m/s              | 5.1                   |  |

### Table 76. Heat Sinks and Junction-to-Ambient Thermal Resistance of PBGA Package

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in the thermal resistance table. More detailed thermal models can be made available on request.

Heat sink vendors include the following:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                              | 603-224-9988 |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

#### System Design Information

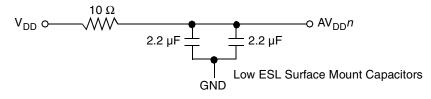

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

Figure 54 shows the PLL power supply filter circuit.

Figure 54. PLL Power Supply Filter Circuit

# 24.3 Decoupling Recommendations

Due to large address and data buses as well as high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the device system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pins of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

# 24.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the device.

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan @freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and PowerQUICC are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. QUICC Engine is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2011 Freescale Semiconductor, Inc.

Document Number: MPC8358EEC Rev. 3 01/2011