## NXP USA Inc. - KMPC8358ZQAGDGA Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 400MHz                                                                  |

| Co-Processors/DSP               | Communications; QUICC Engine                                            |

| RAM Controllers                 | DDR, DDR2                                                               |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (1)                                                     |

| SATA                            | -                                                                       |

| USB                             | USB 1.x (1)                                                             |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                        |

| Security Features               | -                                                                       |

| Package / Case                  | 668-BBGA Exposed Pad                                                    |

| Supplier Device Package         | 668-PBGA-PGE (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8358zqagdga |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Data bus widths:

- Single 32-bit data PCI interface that operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- PCI host bridge capabilities on both interfaces

- PCI agent mode supported on PCI interface

- Support for PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Support for posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration, supporting five masters on PCI

- Support for accesses to all PCI address spaces

- Parity support

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle supported when the device is the target

- Internal configuration registers accessible from PCI

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for one external (optional) and seven internal machine checkstop interrupt sources

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to communication processor

- Redirects interrupts to external INTA pin when in core disable mode

- Unique vector number for each interrupt source

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave  $I^2C$  mode support

- On-chip digital filtering rejects spikes on the bus

- System initialization data is optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- All channels accessible by local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DMA external handshake signals: DMA\_DREQ[0:3]/DMA\_DACK[0:3]/DMA\_DONE[0:3]. There is one set for each DMA channel. The pins are multiplexed to the parallel IO pins with other QE functions.

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- IEEE Std. 1149.1<sup>TM</sup>-compliant, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8358E. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

Table 5 shows the estimated typical I/O power dissipation for the device.

| Interface                                      | Parameter          | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | Unit | Comments    |

|------------------------------------------------|--------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|-------------|

| DDR I/O                                        | 200 MHz, 1x32 bits | 0.3                         | 0.46                        | —                           |                             | —                           | W    | _           |

| 65% utilization<br>2.5 V                       | 200 MHz, 1x64 bits | 0.4                         | 0.58                        | —                           |                             | —                           | W    |             |

| R <sub>s</sub> = 20 Ω<br>R <sub>t</sub> = 50 Ω | 200 MHz, 2x32 bits | 0.6                         | 0.92                        | —                           |                             | —                           | W    | —           |

| 2 pairs of clocks                              | 266 MHz, 1x32 bits | 0.35                        | 0.56                        | —                           |                             | —                           | W    | _           |

|                                                | 266 MHz, 1x64 bits | 0.46                        | 0.7                         | —                           |                             | —                           | W    | _           |

|                                                | 266 MHz, 2x32 bits | 0.7                         | 1.11                        | —                           |                             | —                           | W    | _           |

| Local Bus I/O                                  | 133 MHz, 32 bits   | —                           | —                           | 0.22                        |                             | —                           | W    | _           |

| Load = 25 pf<br>3 pairs of clocks              | 83 MHz, 32 bits    | —                           | —                           | 0.14                        | _                           | —                           | W    | _           |

|                                                | 66 MHz, 32 bits    | —                           | —                           | 0.12                        | _                           | —                           | W    | _           |

|                                                | 50 MHz, 32 bits    | —                           | —                           | 0.09                        | _                           | —                           | W    | _           |

| PCI I/O                                        | 33 MHz, 32 bits    | —                           | —                           | 0.05                        | _                           | —                           | W    | _           |

| Load = 30 pF                                   | 66 MHz, 32 bits    | —                           | —                           | 0.07                        | _                           | —                           | W    | _           |

| 10/100/1000                                    | MII or RMII        | —                           | —                           | —                           | 0.01                        | —                           | W    | Multiply by |

| Ethernet I/O<br>Load = 20 pF                   | GMII or TBI        | <u> </u>                    | W                           | number of interfaces used.  |                             |                             |      |             |

|                                                | RGMII or RTBI      | —                           | —                           | —                           | —                           | 0.04                        | W    |             |

| Other I/O                                      | _                  | —                           | —                           | 0.1                         | —                           | —                           | W    | _           |

Table 5. Estimated Typical I/O Power Dissipation

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8358E.

## NOTE

The rise/fall time on QUICC Engine block input pins should not exceed 5 ns. This should be enforced especially on clock signals. Rise time refers to signal transitions from 10% to 90% of  $V_{DD}$ ; fall time refers to transitions from 90% to 10% of  $V_{DD}$ .

| Interface       | Interface Operating<br>Frequency (MHz) | Max Interface Bit<br>Rate (Mbps) | Uperating |   |

|-----------------|----------------------------------------|----------------------------------|-----------|---|

| UART/async HDLC | 3.68 (max internal ref clock)          | 115 (Kbps)                       | 20        | — |

| BISYNC          | 2 (max)                                | 2                                | 20        | _ |

| USB             | 48 (ref clock)                         | 12                               | 96        | — |

## Table 12. QUICC Engine Block Operating Frequency Limitations (continued)

### Notes:

1. The QUICC Engine module needs to run at a frequency higher than or equal to what is listed in this table.

2. 'F' is the actual interface operating frequency.

3. The bit rate limit is independent of the data bus width (that is, the same for serial, nibble, or octal interfaces).

4. TDM in high-speed mode for serial data interface.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR and DDR2 SDRAM interface of the MPC8358E.

## 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

Table 13 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | —                         | ±10                       | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | _                         | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —     |

| MV <sub>REF</sub> input leakage current          | I <sub>VREF</sub> | —                         | ±10                       | μA   | —     |

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

## Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications Mode

At recommended operating conditions with  $GV_{DD}$  of (1.8 or 2.5 V) ± 5%.

| Parameter                                               | Symbol | Min            | Мах          | Unit | Notes |

|---------------------------------------------------------|--------|----------------|--------------|------|-------|

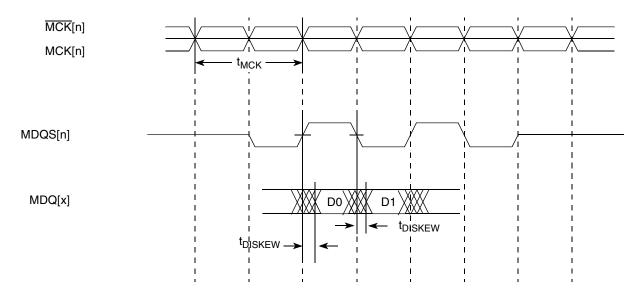

| MDQS—MDQ/MECC input skew per byte<br>266 MHz<br>200 MHz |        | -1125<br>-1250 | 1125<br>1250 | ps   | 1, 2  |

Notes:

1. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

2. Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n +  $\{0...7\}$ ] if  $0 \le n \le 7$ ) or ECC (MECC[ $\{0...7\}$ ] if n = 8).

Figure 5 shows the input timing diagram for the DDR controller.

Figure 5. DDR Input Timing Diagram

## 6.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

Table 20 and Table 21 provide the output AC timing specifications and measurement conditions for the DDR and DDR2 SDRAM interface.

# Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode

At recommended operating conditions with  $\text{GV}_{\text{DD}}$  of (1.8 V or 2.5 V)  $\pm$  5%.

| Parameter <sup>8</sup>                                 | Symbol <sup>1</sup> | Min          | Мах        | Unit | Notes |

|--------------------------------------------------------|---------------------|--------------|------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)            | t <sub>MCK</sub>    | 6            | 10         | ns   | 2     |

| Skew between any MCK to ADDR/CMD<br>266 MHz<br>200 MHz |                     | -1.1<br>-1.2 | 0.3<br>0.4 | ns   | 3     |

#### UCC Ethernet Controller: Three-Speed Ethernet, MII Management

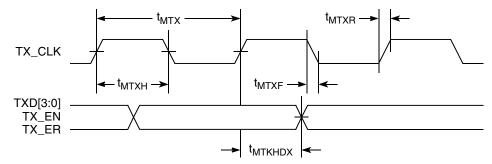

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

## 8.2.2.2 MII Receive AC Timing Specifications

Table 29 provides the MII receive AC timing specifications.

#### Table 29. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}/OV_{DD}$  of 3.3 V ± 10%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub>                    | _    | 400 | —   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | —   | ns   |

| RX_CLK clock rise time, (20% to 80%)        | t <sub>MRXR</sub>                   | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time, (80% to 20%)        | t <sub>MRXF</sub>                   | 1.0  | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

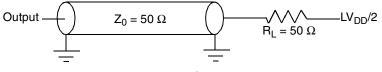

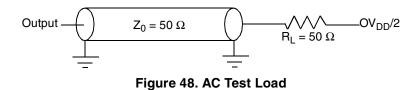

Figure 12 provides the AC test load.

Figure 12. AC Test Load

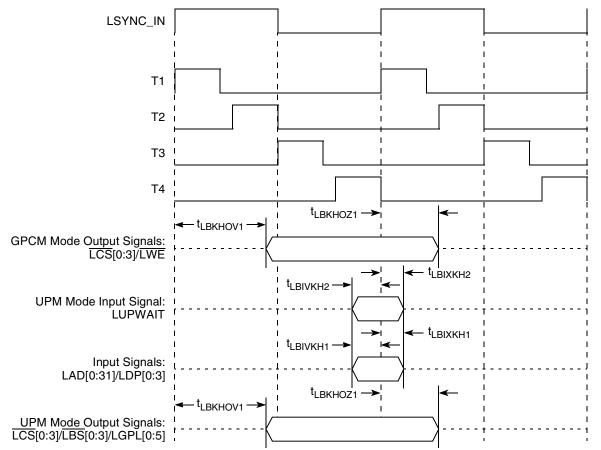

#### Table 40. Local Bus General Timing Parameters—DLL Bypass Mode (continued)

| Parameter                                            | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|------------------------------------------------------|---------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ</sub> |     | 4   | ns   |       |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to falling edge of LCLK0 (for all outputs and for LGTA and LUPWAIT inputs) or rising edge of LCLK0 (for all other inputs).

- 3. All signals are measured from  $OV_{DD}/2$  of the rising/falling edge of LCLK0 to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. t<sub>LBOTOT1</sub> should be used when RCWH[LALE] is not set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 6. t<sub>LBOTOT2</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin is at least 10 pF less than the load on LAD output pins.

- 7. t<sub>LBOTOT3</sub> should be used when RCWH[LALE] is set and when the load on LALE output pin equals to the load on LAD output pins.

- 8. For purposes of active/float timing measurements, the Hi-Z or off-state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 9. DLL bypass mode is not recommended for use at frequencies above 66 MHz.

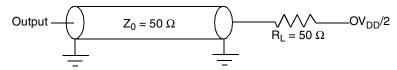

Figure 21 provides the AC test load for the local bus.

Figure 21. Local Bus C Test Load

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 4 (DLL Enabled)

# 10 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8358E.

## **10.1 JTAG DC Electrical Characteristics**

Table 41 provides the DC electrical characteristics for the IEEE 1149.1 (JTAG) interface of the device.

Table 41. JTAG interface DC Electrical Characteristics

| Characteristic      | Symbol          | Condition                    | Min  | Max                    | Unit |

|---------------------|-----------------|------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA    | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA     |      | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA     | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                            | 2.5  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                            | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 V \le V_{IN} \le OV_{DD}$ | _    | ±10                    | μA   |

JTAG

## **10.2 JTAG AC Electrical Characteristics**

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the device.

Table 42 provides the JTAG AC timing specifications as defined in Figure 29 through Figure 32.

## Table 42. JTAG AC Timing Specifications (Independent of CLKIN)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes     |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-----------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —         |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       | _        | ns   | —         |

| JTAG external clock duty cycle                                             | t <sub>JTKHKL</sub> /t <sub>JTG</sub>      | 45       | 55       | %    | —         |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | _         |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       | _        | ns   | 3         |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>4   |          | ns   | 4         |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 10<br>10 |          | ns   | 4         |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 2<br>2   | 11<br>11 | ns   | 5         |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2<br>2   |          | ns   | 5         |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 2<br>2   | 19<br>9  | ns   | 5, 6<br>6 |

#### Notes:

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to  $t_{TCLK}$ .

- 5. Non-JTAG signal output timing with respect to  $\ensuremath{t_{\text{TCLK}}}$  .

- 6. Guaranteed by design and characterization.

<sup>1.</sup> All outputs are measured from the midpoint voltage of the falling/rising edge of  $t_{TCLK}$  to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50- $\Omega$  load (see Figure 21). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

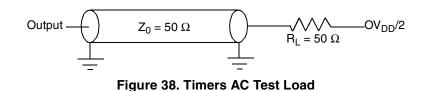

Figure 38 provides the AC test load for the timers.

# 14 GPIO

This section describes the DC and AC electrical specifications for the GPIO of the MPC8358E.

## 14.1 GPIO DC Electrical Characteristics

Table 50 provides the DC electrical characteristics for the device GPIO.

| Characteristic      | Symbol          | Condition                                                          | Min  | Мах                    | Unit | Notes |

|---------------------|-----------------|--------------------------------------------------------------------|------|------------------------|------|-------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA                                          | 2.4  | —                      | V    | 1     |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA                                           | _    | 0.5                    | V    | 1     |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                                           | _    | 0.4                    | V    | 1     |

| Input high voltage  | V <sub>IH</sub> | —                                                                  | 2.0  | OV <sub>DD</sub> + 0.3 | V    | 1     |

| Input low voltage   | V <sub>IL</sub> | —                                                                  | -0.3 | 0.8                    | V    | —     |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{OV}_{\text{DD}}$ | —    | ±10                    | μA   | —     |

## Table 50. GPIO DC Electrical Characteristics

Note: This specification applies when operating from 3.3-V supply.

## 14.2 GPIO AC Timing Specifications

Table 51 provides the GPIO input and output AC timing specifications.

## Table 51. GPIO Input AC Timing Specifications<sup>1</sup>

| Characteristic                  | Symbol <sup>2</sup> | Тур | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

## Notes:

1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any

external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

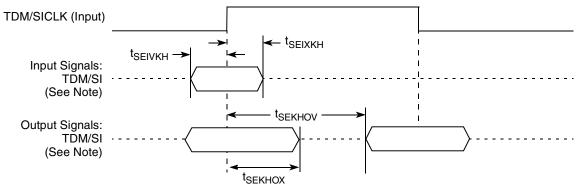

Figure 44 shows the TDM/SI timing with external clock.

Note: The clock edge is selectable on TDM/SI

# 18 UTOPIA/POS

This section describes the DC and AC electrical specifications for the UTOPIA/POS of the MPC8358E.

## **18.1 UTOPIA/POS DC Electrical Characteristics**

Table 58 provides the DC electrical characteristics for the device UTOPIA.

| Table 58. UTOPIA | <b>DC Electrical</b> | Characteristics |

|------------------|----------------------|-----------------|

|------------------|----------------------|-----------------|

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA      | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA       | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq OV_{DD}$ | _    | ±10                    | μA   |

## 18.2 UTOPIA/POS AC Timing Specifications

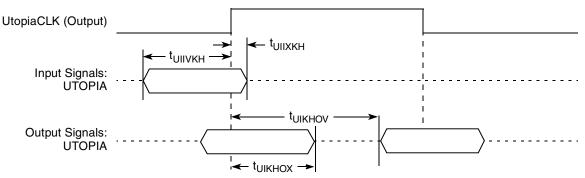

Table 59 provides the UTOPIA input and output AC timing specifications.

Table 59. UTOPIA AC Timing Specifications<sup>1</sup>

| Characteristic                                | Symbol <sup>2</sup> | Min | Мах  | Unit | Notes |

|-----------------------------------------------|---------------------|-----|------|------|-------|

| UTOPIA outputs—Internal clock delay           | t <sub>UIKHOV</sub> | 0   | 11.5 | ns   | —     |

| UTOPIA outputs—External clock delay           | t <sub>UEKHOV</sub> | 1   | 11.6 | ns   | —     |

| UTOPIA outputs—Internal clock high impedance  | t <sub>UIKHOX</sub> | 0   | 8.0  | ns   | —     |

| UTOPIA outputs—External clock high impedance  | t <sub>UEKHOX</sub> | 1   | 10.0 | ns   | —     |

| UTOPIA inputs—Internal clock input setup time | t <sub>UIIVKH</sub> | 6   | —    | ns   | —     |

Figure 47 shows the UTOPIA timing with internal clock.

Figure 47. UTOPIA AC Timing (Internal Clock) Diagram

# 19 HDLC, BISYNC, Transparent, and Synchronous UART

This section describes the DC and AC electrical specifications for the high level data link control (HDLC), BISYNC, transparent, and synchronous UART protocols of the MPC8358E.

## 19.1 HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

Table 60 provides the DC electrical characteristics for the device HDLC, BISYNC, transparent, and synchronous UART protocols.

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -2.0 mA      | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.5                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \le V_{IN} \le OV_{DD}$ | _    | ±10                    | μA   |

Table 60. HDLC, BISYNC, Transparent, and Synchronous UART DC Electrical Characteristics

Figure 48 provides the AC test load.

## 19.3 AC Test Load

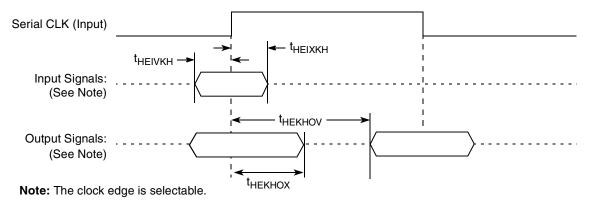

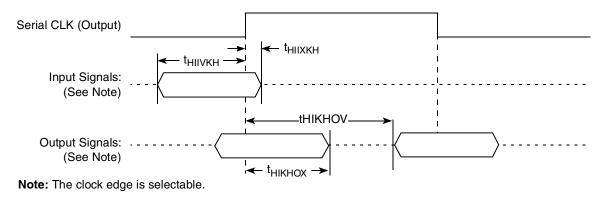

Figure 49 and Figure 50 represent the AC timing from Table 61 and Table 62. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 49 shows the timing with external clock.

Figure 49. AC Timing (External Clock) Diagram

Figure 50 shows the timing with internal clock.

Figure 50. AC Timing (Internal Clock) Diagram

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement must exclude any effect of mark on top surface of package.

- 6. Distance from the seating plane to the encapsulant material.

## 21.3 Pinout Listings

Refer to AN3097, "MPC8360/MPC8358E PowerQUICC Design Checklist," for proper pin termination and usage.

Table 65 shows the pin list of the MPC8358E PBGA package.

| Signal                     | Package Pin Number                                                                                                                                                                                                                                                                                                                                                          | Pin Type | Power<br>Supply    | Notes |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------|

|                            | DDR SDRAM Memory Controller Interface                                                                                                                                                                                                                                                                                                                                       |          |                    | •     |

| MEMC_MDQ[0:63]             | AD20, AG24, AF24, AH24, AF23, AE22, AH26, AD21,<br>AH25, AD22, AF27, AB24, AG25, AC22, AE25, AC24,<br>AD25, AB25, AC25, AG28, AD26, AE23, AG26, AC26,<br>AD27, V25, AA28, AA25, Y26, W27, U24, W24, E28,<br>H24, E26, D25, G27, H25, G26, F26, F27, F25, D26, F24,<br>G25, E27, D27, C28, C27, F22, B26, F21, B28, E22, D24,<br>C24, A25, E20, F20, D20, A23, C21, C23, E19 | I/O      | GV <sub>DD</sub>   | _     |

| MEMC_MECC[0:7]             | N26, N24, J26, H28, N28, P24, L26, K24                                                                                                                                                                                                                                                                                                                                      | I/O      | GV <sub>DD</sub>   | _     |

| MEMC_MDM[0:8]              | AG23, AD23, AE26, V28, G28, D28, D23, B24, U27                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   |       |

| MEMC_MDQS[0:8]             | AH23, AH27, AF28, T28, H26, E25, B25, A24, R28                                                                                                                                                                                                                                                                                                                              | I/O      | GV <sub>DD</sub>   |       |

| MEMC_MBA[0:2]              | V26, W28, Y28                                                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub>   |       |

| MEMC_MA[0:14]              | L25, M25, M24, K28, P28, T24, M27, R25, P25, L28,<br>U26, M28, L27, K27, H27                                                                                                                                                                                                                                                                                                | 0        | GV <sub>DD</sub>   | _     |

| MEMC_MODT[0:3]             | AE21, AC19, E23, B23                                                                                                                                                                                                                                                                                                                                                        | —        | GV <sub>DD</sub>   | 6     |

| MEMC_MWE                   | R27                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   |       |

| MEMC_MRAS                  | W25                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   |       |

| MEMC_MCAS                  | R24                                                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub>   |       |

| MEMC_MCS[0:3]              | T26, U28, J25, F28                                                                                                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub>   |       |

| MEMC_MCKE[0:1]             | AD24, AE28                                                                                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub>   |       |

| MEMC_MCK[0:5]              | AG22, AG27, A26, C26, P26, E21                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   |       |

| MEMC_MCK[0:5]              | AF22, AF26, A27, B27, N27, D22                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub>   |       |

| MDIC[0:1]                  | F19, AA27                                                                                                                                                                                                                                                                                                                                                                   | I/O      | GV <sub>DD</sub>   | 11    |

|                            | PCI                                                                                                                                                                                                                                                                                                                                                                         |          |                    |       |

| PCI_INTA/<br>PF[5]         | R3                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | 2     |

| PCI_RESET_OUT/<br>PF[6]    | P6                                                                                                                                                                                                                                                                                                                                                                          | I/O      | LV <sub>DD</sub> 2 | -     |

| PCI_AD[0:31]/<br>PG[0:31]  | AB5, AC5, AG1, AA5, AF2, AD4, Y6, AF1, AE2, AC4,<br>AD3, AE1, Y4, AC3, AD2, AD1, AB2, Y3, AA1, Y1, W1,<br>V6, W3, V4, T5, W2, V5, V1, U4, V2, U2, T2                                                                                                                                                                                                                        | I/O      | LV <sub>DD</sub> 2 | —     |

| PCI_C_BE[0:3]/<br>PF[7:10] | Y5, AC2, Y2, U5                                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub>   | —     |

## Table 65. MPC8358E PBGA Pinout Listing

Package and Pin Listings

| Signal                       | Package Pin Number                | Pin Type | Power              | Notes    |

|------------------------------|-----------------------------------|----------|--------------------|----------|

|                              |                                   |          | Supply             |          |

| LGPL2/<br>LSDRAS/            | AH19                              | 0        | OV <sub>DD</sub>   | _        |

| LOE                          |                                   |          |                    |          |

| LGPL3/                       | AE18                              | I/O      | OV <sub>DD</sub>   | _        |

| LSDCAS/<br>cfg_reset_source2 |                                   |          |                    |          |

| LGPL4/                       | AG19                              | I/O      | OV <sub>DD</sub>   | <u> </u> |

| LGTA/                        | halo                              | 1,0      | 0,00               |          |

| LUPWAIT/                     |                                   |          |                    |          |

| LPBSE<br>LGPL5/              |                                   |          | 01/                |          |

| cfg_clkin_div                | AF19                              | I/O      | OV <sub>DD</sub>   | _        |

|                              | AD8                               | 0        | OV <sub>DD</sub>   |          |

| LCLK[0]                      | AC9                               | 0        | OV <sub>DD</sub>   | _        |

| LCLK[1]/                     | AG6                               | 0        | OV <sub>DD</sub>   |          |

| LCS[6]                       |                                   |          |                    |          |

| LCLK[2]/<br>LCS[7]           | AE7                               | 0        | OV <sub>DD</sub>   | —        |

| LSYNC_OUT                    | AG4                               | 0        | OV <sub>DD</sub>   |          |

| LSYNC_IN                     | AC8                               |          | OV <sub>DD</sub>   |          |

|                              | Programmable Interrupt Controller |          | 0.00               |          |

|                              |                                   |          |                    |          |

| MCP_OUT                      | AG3                               | 0        | OV <sub>DD</sub>   | 2        |

| IRQ0/<br>MCP_IN              | AH4                               |          | OV <sub>DD</sub>   | _        |

| IRQ[1:2]                     | AG5, AH5                          | I/O      | OV <sub>DD</sub>   | —        |

| IRQ[3]/<br>CORE_SRESET       | AD7                               | I/O      | OV <sub>DD</sub>   | -        |

| IRQ[4:5]                     | AC7, AD6                          | I/O      | OV <sub>DD</sub>   | _        |

| IRQ[6:7]                     | AC6, AC10                         | I/O      | OV <sub>DD</sub>   | —        |

|                              | DUART                             | ·        |                    |          |

| UART1_SOUT                   | AE3                               | 0        | OV <sub>DD</sub>   | _        |

| UART1_SIN                    | AE4                               | I/O      | OV <sub>DD</sub>   | —        |

| UART1_CTS                    | AG2                               | I/O      | OV <sub>DD</sub>   | _        |

| UART1_RTS                    | AA6                               | 0        | OV <sub>DD</sub>   | _        |

|                              | I <sup>2</sup> C Interface        | 1        |                    |          |

| IIC1_SDA                     | AB6                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC1_SCL                     | AD5                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SDA                     | AF3                               | I/O      | OV <sub>DD</sub>   | 2        |

| IIC2_SCL                     | AH2                               | I/O      | OV <sub>DD</sub>   | 2        |

|                              | QUICC Engine                      | ·        |                    |          |

| CE_PA[0]                     | F6                                | I/O      | LV <sub>DD</sub> 0 | _        |

|                              |                                   |          |                    | 1        |

Package and Pin Listings

| Signal             | Package Pin Number                                                                                                                                                                                                                | Pin Type                                                          | Power<br>Supply                 | Notes |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------|-------|

| GV <sub>DD</sub>   | C19, C22, C25, G24, J18, J19, J20, J24, K19, K20, K26,<br>L20, M20, M26, N19, N20, P20, P27, R20, T19, T20, T27,<br>U19, U20, U25, V19, V20, W20, W26, Y20, AA24, AB28,<br>AC21, AC28, AD28, AF21, AF25                           | Power for<br>DDR<br>DRAM<br>I/O<br>Voltage<br>(2.5 V or<br>1.8 V) | GV <sub>DD</sub>                |       |

| LV <sub>DD</sub> 0 | F3, J9                                                                                                                                                                                                                            | —                                                                 | LV <sub>DD</sub> 0              | —     |

| LV <sub>DD</sub> 1 | P3, P10                                                                                                                                                                                                                           | —                                                                 | LV <sub>DD</sub> 1              | 10    |

| LV <sub>DD</sub> 2 | R4, R10                                                                                                                                                                                                                           |                                                                   | LV <sub>DD</sub> 2              | 10    |

| V <sub>DD</sub>    | M12, M13, M16, M17, N10, N12, N13, N14, N15, N16,<br>N17, P12, P13, P14, P15, P16, P17, R12, R13, R16,<br>R17, T12, T13, T16, T17, U12, U13, U14, U15, U16, U17,<br>V12, V13, V16, V17, W11, W12, W13, W15, W16, W17,<br>Y16, Y17 | Power for<br>Core<br>(1.2 V)                                      | V <sub>DD</sub>                 | _     |

| OV <sub>DD</sub>   | C6, C12, D17, J11, J13, J14, K3, K9, K10, K12, K15,<br>K16, L10, M9, N9, T9, U9, V3, V10, W9, W10, W14, Y9,<br>Y10, Y12, Y13, Y15, AA3, AE6, AE16, AF11, AF20                                                                     | PCI,<br>10/100<br>Ethernet,<br>and other<br>Standard<br>(3.3 V)   | OV <sub>DD</sub>                | _     |

| MVREF1             | J27                                                                                                                                                                                                                               | I                                                                 | DDR<br>Referenc<br>e<br>Voltage | _     |

| MVREF2             | Y24                                                                                                                                                                                                                               | I                                                                 | DDR<br>Referenc<br>e<br>Voltage | _     |

|                    | No Connect                                                                                                                                                                                                                        |                                                                   |                                 |       |

| NC                 | F23, G23, H23, J23, K23, L23, M23, N23, P23, R23, T23, U23, V23, W23, Y23, AA23, AB23, AC23                                                                                                                                       | _                                                                 | —                               |       |

## Table 65. MPC8358E PBGA Pinout Listing (continued)

#### Notes:

1. This pin is an open drain signal. A weak pull-up resistor (1 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

2. This pin is an open drain signal. A weak pull-up resistor (2–10 k $\Omega$ ) should be placed on this pin to OV<sub>DD</sub>.

3. This output is actively driven during reset rather than being three-stated during reset.

4. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

5. This pin should have a weak pull up if the chip is in PCI host mode. Follow PCI specifications recommendation.

6. These are On Die Termination pins, used to control DDR2 memories internal termination resistance.

7. This pin must always be tied to GND.

8. This pin must always be left not connected.

9. This pin must always be tied to GV<sub>DD</sub>.

10. Refers to *MPC8360E PowerQUICC II™ Pro Integrated Communications Processor Reference Manual* section on "RGMII Pins" for information about the two UCC2 Ethernet interface options.

11. It is recommended that MDIC0 be tied to GND using an 18.2  $\Omega$  resistor and MDIC1 be tied to DDR power using an 18.2  $\Omega$  resistor for DDR2.

# 22.1 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] and RCWL[SVCOD] parameters. Table 68 shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | System PLL<br>Multiplication Factor |

|------------|-------------------------------------|

| 0000       | × 16                                |

| 0001       | Reserved                            |

| 0010       | × 2                                 |

| 0011       | × 3                                 |

| 0100       | × 4                                 |

| 0101       | × 5                                 |

| 0110       | × 6                                 |

| 0111       | × 7                                 |

| 1000       | × 8                                 |

| 1001       | × 9                                 |

| 1010       | × 10                                |

| 1011       | × 11                                |

| 1100       | × 12                                |

| 1101       | × 13                                |

| 1110       | × 14                                |

| 1111       | × 15                                |

## Table 68. System PLL Multiplication Factors

The RCWL[SVCOD] denotes the system PLL VCO internal frequency as shown in Table 69.

# Table 69. System PLL VCO Divider

| RCWL[SVCOD] | VCO Divider |

|-------------|-------------|

| 00          | 4           |

| 01          | 8           |

| 10          | 2           |

| 11          | Reserved    |

## NOTE

The VCO divider must be set properly so that the system VCO frequency is in the range of 600–1400 MHz.

| Table 76 shows heat sinks and | junction-to-ambient therma | l resistance for PBGA package. |

|-------------------------------|----------------------------|--------------------------------|

|                               |                            |                                |

| Host Sink Assuming Thormal Grosso                          | Air Flow           | 29 $	imes$ 29 mm PBGA |  |

|------------------------------------------------------------|--------------------|-----------------------|--|

| Heat Sink Assuming Thermal Grease                          | All Flow           | Thermal Resistance    |  |

| AAVID 30 $\times$ 30 $\times$ 9.4 mm Pin Fin               | Natural Convection | 12.6                  |  |

| AAVID 30 $	imes$ 30 $	imes$ 9.4 mm Pin Fin                 | 1 m/s              | 8.2                   |  |

| AAVID 30 $	imes$ 30 $	imes$ 9.4 mm Pin Fin                 | 2 m/s              | 7.0                   |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | Natural Convection | 10.5                  |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | 1 m/s              | 6.6                   |  |

| AAVID 31 $	imes$ 35 $	imes$ 23 mm Pin Fin                  | 2 m/s              | 6.1                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | Natural Convection | 9.0                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | 1 m/s              | 5.6                   |  |

| Wakefield, $53 \times 53 \times 25$ mm Pin Fin             | 2 m/s              | 5.1                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | Natural Convection | 9.0                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | 1 m/s              | 5.7                   |  |

| MEI, $75 \times 85 \times 12$ no adjacent board, extrusion | 2 m/s              | 5.1                   |  |

## Table 76. Heat Sinks and Junction-to-Ambient Thermal Resistance of PBGA Package

Accurate thermal design requires thermal modeling of the application environment using computational fluid dynamics software which can model both the conduction cooling and the convection cooling of the air moving through the application. Simplified thermal models of the packages can be assembled using the junction-to-case and junction-to-board thermal resistances listed in the thermal resistance table. More detailed thermal models can be made available on request.

Heat sink vendors include the following:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                              | 603-224-9988 |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                             | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com | 818-842-7277 |

Thermal

|          | Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-millennium.com                | 408-436-8770 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|          | Tyco Electronics<br>Chip Coolers™<br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com                              | 800-522-6752 |

|          | Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                                     | 603-635-5102 |

| Interfac | ce material vendors include the following:                                                                                                    |              |

|          | Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                                      | 781-935-4850 |

|          | Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

|          | Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                                | 888-642-7674 |

|          | The Bergquist Company<br>18930 West 78th St.<br>Chanhassen, MN 55317<br>Internet: www.bergquistcompany.com                                    | 800-347-4572 |

## 23.3 Heat Sink Attachment

When attaching heat sinks to these devices, an interface material is required. The best method is to use thermal grease and a spring clip. The spring clip should connect to the printed-circuit board, either to the board itself, to hooks soldered to the board, or to a plastic stiffener. Avoid attachment forces which would lift the edge of the package or peel the package from the board. Such peeling forces reduce the solder joint lifetime of the package. Recommended maximum force on the top of the package is 10 lb force (4.5 kg force). If an adhesive attachment is planned, the adhesive should be intended for attachment to painted or plastic surfaces and its performance verified under the application requirements.

**Document Revision History**

# 26 Document Revision History

Table 80 provides a revision history for this hardware specification.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3              | 01/2011 | <ul> <li>Updated references to the LCRR register throughout</li> <li>Removed references to DDR DLL mode in Section 6.2.2, "DDR and DDR2 SDRAM Output AC Timing Specifications."</li> <li>Changed "Junction-to-Case" to "Junction-to-Ambient" in Section 23.2.4, "Heat Sinks and Junction-to-Ambient Thermal Resistance," and Table 76, "Heat Sinks and Junction-to-Ambient Thermal Resistance of PBGA Package," titles.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2              | 03/2010 | <ul> <li>Changed references to RCWH[PCICKEN] to RCWH[PCICKDRV].</li> <li>In Table 2, added extended temperature characteristics.</li> <li>Added Figure 5, "DDR Input Timing Diagram."</li> <li>In Figure 52, "Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package," removed watermark.</li> <li>In Table 4, "MPC8358E PBGA Core Power Dissipation<sup>1</sup>," added row for 400/266/400 part offering.</li> <li>Updated the title of Table 18,"DDR SDRAM Input AC Timing Specifications."</li> <li>In Table 29, and Table 32,—Table 33, changed the rise and fall time specifications to reference 20–80% and 80–20% of the voltage supply, respectively.</li> <li>In Table 37, "IEEE 1588 Timer AC Specifications," changed units to "ns" for t<sub>I2DVKH</sub>.</li> <li>In Table 65, "Operating Frequencies for the PBGA Package," and Table 78, "Part Numbering Nomenclature," updated for 400 MHz QE part offering</li> <li>In Section 4, "Clock Input Timing," added note regarding rise/fall time on QUICC Engine block input pins.</li> <li>Added Section 4.3, "Gigabit Reference Clock Input Timing."</li> <li>Updated Section 4.1, "10/100/1000 Ethernet DC Electrical Characteristics."</li> <li>In Section 22, "Clocking," removed statement: "The OCCR[PCICDI] parameters select whether CLKIN or CLKIN/2 is driven out on the PCI_CLK_OUTn signals."</li> </ul> |

| 1              | 12/2007 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Table 80. Revision History