## **Cypress Semiconductor Corp - <u>CY8CLED16-48LFXIT Datasheet</u>**

Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific</u>?

Application enacific microcontrollars are anaineered to

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                     |

| Applications            | HB LED Controller                                                            |

| Core Processor          | M8C                                                                          |

| Program Memory Type     | FLASH (32KB)                                                                 |

| Controller Series       | CY8CLED CY8CLED                                                              |

| RAM Size                | 2K x 8                                                                       |

| Interface               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Number of I/O           | 44                                                                           |

| Voltage - Supply        | 3V ~ 5.25V                                                                   |

| Operating Temperature   | -40°C ~ 85°C                                                                 |

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 48-VFQFN Exposed Pad                                                         |

| Supplier Device Package | 48-QFN (7x7)                                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy8cled16-48lfxit |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

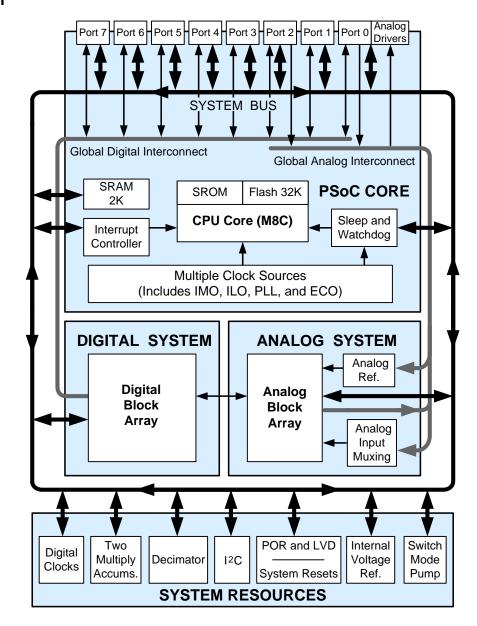

## **Logic Block Diagram**

## Contents

| EZ-Color™ Functional Overview     | 4  |

|-----------------------------------|----|

| Target Applications               | 4  |

| The PSoC Core                     |    |

| The Digital System                | 4  |

| The Analog System                 |    |

| Additional System Resources       |    |

| EZ-Color Device Characteristics   |    |

| Getting Started                   | 6  |

| Application Notes                 |    |

| Development Kits                  | 6  |

| Training                          | 6  |

| CYPros Consultants                | 6  |

| Solutions Library                 | 6  |

| Technical Support                 | 6  |

| Development Tools                 | 7  |

| PSoC Designer Software Subsystems | 7  |

| Designing with PSoC Designer      | 8  |

| Select User Modules               | 8  |

| Configure User Modules            | 8  |

| Organize and Connect              | 8  |

| Generate, Verify, and Debug       |    |

| Pin Information                   | 9  |

| Pinouts                           | 9  |

| Register Reference                |    |

| Register Conventions              | 11 |

| Register Mapping Tables           |    |

| Electrical Specifications         |    |

| Absolute Maximum Ratings          | 15 |

| Operating Temperature                   | 15 |

|-----------------------------------------|----|

| DC Electrical Characteristics           | 16 |

| AC Electrical Characteristics           | 31 |

| Packaging Information                   | 41 |

| Packaging Dimensions                    |    |

| Thermal Impedances                      |    |

| Capacitance on Crystal Pins             | 42 |

| Solder Reflow Peak Temperature          | 42 |

| Development Tool Selection              |    |

| Software                                | 43 |

| Evaluation Tools                        | 43 |

| Device Programmers                      | 44 |

| Accessories (Emulation and Programming) | 44 |

| Ordering Information                    | 44 |

| Key Device Features                     | 44 |

| Ordering Code Definitions               |    |

| Acronyms                                | 45 |

| Acronyms Used                           | 45 |

| Reference Documents                     | 45 |

| Document Conventions                    |    |

| Units of Measure                        | 46 |

| Numeric Conventions                     | 46 |

| Glossary                                |    |

| Document History Page                   | 51 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      | 52 |

| Products                                | 52 |

| DSoC@ Solutions                         | 52 |

### EZ-Color™ Functional Overview

Cypress's EZ-Color family of devices offers the ideal control solution for High Brightness LED applications requiring intelligent dimming control. EZ-Color devices combine the power and flexibility of Programmable System-on-Chip (PSoC); with Cypress's precise illumination signal modulation (PrISM) modulation technology providing lighting designers a fully customizable and integrated lighting solution platform.

The EZ-Color family supports a range of independent LED channels from 4 channels at 32 bits of resolution each, up to 16 channels at 8 bits of resolution each. This enables lighting designers the flexibility to choose the LED array size and color quality. PSoC Designer software, with lighting specific drivers, can significantly cut development time and simplify implementation of fixed color points through temperature, optical, and LED binning compensation. EZ-Color's virtually limitless analog and digital customization allow for simple integration of features in addition to intelligent lighting, such as Battery Charging, Image Stabilization, and Motor Control during the development process. These features, along with Cypress' best-in-class quality and design support, make EZ-Color the ideal choice for intelligent HB LED control applications.

#### Target Applications

- LCD Backlight

- Large Signs

- General Lighting

- Architectural Lighting

- Camera/Cell Phone flash

- flashlights

#### The PSoC Core

The PSoC core is a powerful engine that supports a rich feature set. The core includes a central processing unit (CPU), memory, clocks, and configurable general purpose I/O (GPIO).

The M8C CPU core is a powerful processor with speeds up to 48 MHz, providing a four million instructions per second (MIPS) 8-bit Harvard-architecture microprocessor. The CPU utilizes an interrupt controller with 25 vectors, to simplify programming of real time embedded events. Program execution is timed and protected using the included Sleep and watchdog timers (WDT).

Memory encompasses 32 KB of flash for program storage, 2 KB of SRAM for data storage, and up to 2 KB of EEPROM emulated using the flash. Program flash utilizes four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The EZ-Color family incorporates flexible internal clock generators, including a 24 MHz internal main oscillator (IMO) accurate to 2.5% over temperature and voltage. The 24 MHz IMO can also

be doubled to 48 MHz for use by the digital system. A low power 32 kHz internal low speed oscillator (ILO) is provided for the Sleep timer and WDT. If crystal accuracy is desired, the 32.768 kHz external crystal oscillator (ECO) is available for use as a real time clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the EZ-Color device.

EZ-Color GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

#### The Digital System

The digital system is composed of 16 digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user modules. Digital peripheral configurations include those listed below.

- PrISM (8-to 32-bit)

- PWMs (8-to 32-bit)

- PWMs with Dead band (8-to 32-bit)

- Counters (8-to 32-bit)

- Timers (8-to 32-bit)

- UART 8 bit with selectable parity (up to 4)

- SPI master and slave (up to 4 each)

- I<sup>2</sup>C slave and multi-master (1 available as a System Resource)

- Cyclical Redundancy Checker/Generator (8- to 32-bit)

- IrDA (up to 4)

- Generators (8-to 32-bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by EZ-Color device family. This allows you the optimum choice of system resources for your application. Family resources are shown in Table 1 on page 6.

## DC GPIO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and -40  $^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 7. DC GPIO Specifications

| Symbol           | Description                       | Min                   | Тур | Max  | Units | Notes                                                                                                                                                                                        |

|------------------|-----------------------------------|-----------------------|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull-up Resistor                  | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                              |

| R <sub>PD</sub>  | Pull-down Resistor                | 4                     | 5.6 | 8    | kΩ    |                                                                                                                                                                                              |

| V <sub>OH</sub>  | High output level                 | V <sub>DD</sub> - 1.0 | -   | _    | V     | IOH = 10 mA, $V_{DD}$ = 4.75 to 5.25 V (8 total loads, 4 on even port pins (for example, P0[2], P1[4]), 4 on odd port pins (for example, P0[3], P1[5])). 80 mA maximum combined IOH budget.  |

| V <sub>OL</sub>  | Low output level                  | _                     | -   | 0.75 | V     | IOL = 25 mA, $V_{DD}$ = 4.75 to 5.25 V (8 total loads, 4 on even port pins (for example, P0[2], P1[4]), 4 on odd port pins (for example, P0[3], P1[5])). 150 mA maximum combined IOL budget. |

| I <sub>OH</sub>  | High level source current         | 10                    | _   | _    | mA    | VOH = V <sub>DD</sub> -1.0 V. See the limitations of the total current in the Note for VOH.                                                                                                  |

| I <sub>OL</sub>  | Low level sink current            | 25                    | _   | _    | mA    | VOL = 0.75 V. See the limitations of the total current in the Note for VOL.                                                                                                                  |

| V <sub>IL</sub>  | Input low level                   | -                     | _   | 0.8  | V     | V <sub>DD</sub> = 3.0 to 5.25.                                                                                                                                                               |

| V <sub>IH</sub>  | Input high level                  | 2.1                   | _   |      | V     | V <sub>DD</sub> = 3.0 to 5.25.                                                                                                                                                               |

| $V_{H}$          | Input hysterisis                  | _                     | 60  | _    | mV    |                                                                                                                                                                                              |

| I <sub>IL</sub>  | Input leakage (Absolute Value)    | _                     | 1   | -    | nA    | Gross tested to 1 μA.                                                                                                                                                                        |

| C <sub>IN</sub>  | Capacitive load on pins as input  | _                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                  |

| C <sub>OUT</sub> | Capacitive load on pins as output | _                     | 3.5 | 10   | pF    | Package and pin dependent.<br>Temp =25 °C.                                                                                                                                                   |

Table 9. 3.3-V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                                                      | Min                    | Тур                               | Max                               | Unit                             | Notes                                                                                                                                                                                    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input offset voltage (absolute value) Power = Low, Opamp bias = Low Power = Low, Opamp bias = High                                                                                                                                               | _<br>_                 | 1.4<br>1.4                        | 10<br>10                          | mV<br>mV                         | Power = High, Opamp bias = High setting is not allowed for 3.3 V V <sub>DD</sub> operation.                                                                                              |

|                      | Power = Medium, Opamp bias = Low                                                                                                                                                                                                                 | _                      | 1.4                               | 10                                | mV                               |                                                                                                                                                                                          |

|                      | Power = Medium, Opamp bias = High                                                                                                                                                                                                                | _                      | 1.4                               | 10                                | mV                               |                                                                                                                                                                                          |

|                      | Power = High, Opamp bias = Low<br>Power = High, Opamp bias = High                                                                                                                                                                                | _<br>_                 | 1.4<br>–                          | 10<br>-                           | mV<br>mV                         |                                                                                                                                                                                          |

| TCV <sub>OSOA</sub>  | Average input offset voltage drift                                                                                                                                                                                                               | -                      | 7                                 | 40                                | μV/°C                            | -                                                                                                                                                                                        |

| EBOA                 | Input leakage current (port 0 analog pins)                                                                                                                                                                                                       | -                      | 200                               | _                                 | pА                               | Gross tested to 1 μA.                                                                                                                                                                    |

| C <sub>INOA</sub>    | Input capacitance (port 0 analog pins)                                                                                                                                                                                                           | _                      | 4.5                               | 9.5                               | pF                               | Package and pin dependent.<br>Temp = 25 °C                                                                                                                                               |

| СМОА                 | Common mode voltage range                                                                                                                                                                                                                        | 0                      | _                                 | V <sub>DD</sub>                   | V                                | The common-mode input voltage range is measured through an analog output buffer.  The specification includes the limitations imposed by the characteristics of the analog output buffer. |

| CMRR <sub>OA</sub>   | Common mode rejection ratio                                                                                                                                                                                                                      | 60                     | _                                 | -                                 | dB                               | _                                                                                                                                                                                        |

| G <sub>OLOA</sub>    | Open loop gain                                                                                                                                                                                                                                   | 80                     | -                                 | _                                 | dB                               | -                                                                                                                                                                                        |

| V <sub>OHIGHOA</sub> | High output voltage swing (internal signals)                                                                                                                                                                                                     | V <sub>DD</sub> – 0.01 | _                                 | _                                 | V                                | _                                                                                                                                                                                        |

| $V_{OLOWOA}$         | Low output voltage swing (internal signals)                                                                                                                                                                                                      | -                      | _                                 | 0.01                              | V                                | _                                                                                                                                                                                        |

| ISOA                 | Supply current (including associated AGND buffer) Power = Low, Opamp bias = Low Power = Low, Opamp bias = High Power = Medium, Opamp bias = Low Power = Medium, Opamp bias = High Power = High, Opamp bias = Low Power = High, Opamp bias = High | -<br>-<br>-<br>-<br>-  | 150<br>300<br>600<br>1200<br>2400 | 200<br>400<br>800<br>1600<br>3200 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | Power = High, Opamp bias = High setting is not allowed for 3.3 V V <sub>DD</sub> operation.                                                                                              |

| PSRR <sub>OA</sub>   | Supply voltage rejection ratio                                                                                                                                                                                                                   | 54                     | 80                                | _                                 | dB                               | $V_{SS} \le V_{IN} \le (V_{DD} - 2.25)$ or $(V_{DD} - 1.25 \ V) \le V_{IN} \le V_{DD}$                                                                                                   |

### DC Low Power Comparator Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and -40  $^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 10. DC Low Power Comparator Specifications

| Symbol              | Description                                        | Min | Тур | Max                 | Units | Notes |

|---------------------|----------------------------------------------------|-----|-----|---------------------|-------|-------|

| V <sub>REFLPC</sub> | Low power comparator (LPC) reference voltage range | 0.2 | -   | V <sub>DD</sub> - 1 | V     | -     |

| I <sub>SLPC</sub>   | LPC supply current                                 | _   | 10  | 40                  | μΑ    | _     |

| V <sub>OSLPC</sub>  | LPC voltage offset                                 | -   | 2.5 | 30                  | mV    | -     |

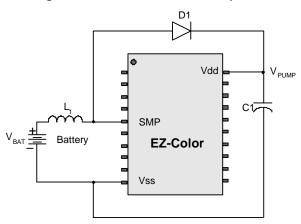

Figure 6. Basic Switch Mode Pump Circuit

#### DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

The guaranteed specifications are measured through the analog continuous time PSoC blocks. The power levels for AGND refer to the power of the Analog Continuous Time PSoC block. The power levels for RefHi and RefLo refer to the analog reference control register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block. Reference control power is high.

Table 14. 5-V DC Analog Reference Specifications

| Reference ARF_CR[5:3] | Reference Power<br>Settings | Symbol             | Reference | Description                  | Min                        | Тур                        | Max                        | Unit |

|-----------------------|-----------------------------|--------------------|-----------|------------------------------|----------------------------|----------------------------|----------------------------|------|

|                       | RefPower = High             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.228 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.352 | V    |

|                       | Opamp bias = High           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 – 0.078 | V <sub>DD</sub> /2 – 0.007 | $V_{DD}/2 + 0.063$         | V    |

|                       |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.336 | V <sub>DD</sub> /2 – 1.295 | V <sub>DD</sub> /2 – 1.250 | V    |

|                       | RefPower = High             | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.224 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.356 | V    |

|                       | Opamp bias = Low            | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 - 0.056 | V <sub>DD</sub> /2 – 0.005 | $V_{DD}/2 + 0.043$         | V    |

| 0b000                 |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.338 | V <sub>DD</sub> /2 – 1.298 | V <sub>DD</sub> /2 – 1.255 | V    |

| 00000                 | RefPower = Med              | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.226 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.356 | V    |

|                       | Opamp bias = High           | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 – 0.057 | V <sub>DD</sub> /2 – 0.006 | $V_{DD}/2 + 0.044$         | V    |

|                       |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.337 | V <sub>DD</sub> /2 – 1.298 | V <sub>DD</sub> /2 – 1.256 | V    |

|                       | RefPower = Med              | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap | V <sub>DD</sub> /2 + 1.226 | V <sub>DD</sub> /2 + 1.294 | $V_{DD}/2 + 1.359$         | V    |

|                       | Opamp bias = Low            | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2           | V <sub>DD</sub> /2 – 0.047 | V <sub>DD</sub> /2 – 0.004 | $V_{DD}/2 + 0.035$         | V    |

|                       |                             | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap | V <sub>DD</sub> /2 – 1.338 | V <sub>DD</sub> /2 – 1.299 | V <sub>DD</sub> /2 – 1.258 | V    |

Table 14. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR[5:3] | Reference Power<br>Settings          | Symbol             | Reference | Description                               | Min           | Тур           | Max           | Unit |

|--------------------------|--------------------------------------|--------------------|-----------|-------------------------------------------|---------------|---------------|---------------|------|

|                          | RefPower = High                      | V <sub>REFHI</sub> | Ref High  | 3 x Bandgap                               | 3.788         | 3.891         | 3.986         | V    |

|                          | Opamp bias = High                    | $V_{AGND}$         | AGND      | 2 x Bandgap                               | 2.500         | 2.604         | 3.699         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | Bandgap                                   | 1.257         | 1.306         | 1.359         | V    |

|                          | RefPower = High                      | V <sub>REFHI</sub> | Ref High  | 3 x Bandgap                               | 3.792         | 3.893         | 3.982         | V    |

|                          | Opamp bias = Low                     | $V_{AGND}$         | AGND      | 2 x Bandgap                               | 2.518         | 2.602         | 2.692         | V    |

| 0b011                    |                                      | V <sub>REFLO</sub> | Ref Low   | Bandgap                                   | 1.256         | 1.302         | 1.354         | V    |

| 00011                    | RefPower = Med                       | $V_{REFHI}$        | Ref High  | 3 x Bandgap                               | 3.795         | 3.894         | 3.993         | V    |

|                          | Opamp bias = High                    | $V_{AGND}$         | AGND      | 2 x Bandgap                               | 2.516         | 2.603         | 2.698         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | Bandgap                                   | 1.256         | 1.303         | 1.353         | V    |

|                          | RefPower = Med                       | V <sub>REFHI</sub> | Ref High  | 3 x Bandgap                               | 3.792         | 3.895         | 3.986         | V    |

|                          | Opamp bias = Low                     | V <sub>AGND</sub>  | AGND      | 2 x Bandgap                               | 2.522         | 2.602         | 2.685         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | Bandgap                                   | 1.255         | 1.301         | 1.350         | V    |

|                          | RefPower = High<br>Opamp bias = High | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap +<br>P2[6] (P2[6] =<br>1.3 V) | 2.495 – P2[6] | 2.586 – P2[6] | 2.657 - P2[6] | V    |

|                          |                                      | V <sub>AGND</sub>  | AGND      | 2 x Bandgap                               | 2.502         | 2.604         | 2.719         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap –<br>P2[6] (P2[6] =<br>1.3 V) | 2.531 – P2[6] | 2.611 – P2[6] | 2.681 – P2[6] | V    |

|                          | RefPower = High<br>Opamp bias = Low  | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap +<br>P2[6] (P2[6] =<br>1.3 V) | 2.500 - P2[6] | 2.591 – P2[6] | 2.662 - P2[6] | V    |

|                          |                                      | V <sub>AGND</sub>  | AGND      | 2 x Bandgap                               | 2.519         | 2.602         | 2.693         | V    |

| 01-400                   |                                      | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap –<br>P2[6] (P2[6] =<br>1.3 V) | 2.530 - P2[6] | 2.605 - P2[6] | 2.666 - P2[6] | V    |

| 0b100                    | RefPower = Med<br>Opamp bias = High  | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap +<br>P2[6] (P2[6] =<br>1.3 V) | 2.503 – P2[6] | 2.592 – P2[6] | 2.662 - P2[6] | V    |

|                          |                                      | $V_{AGND}$         | AGND      | 2 x Bandgap                               | 2.517         | 2.603         | 2.698         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap –<br>P2[6] (P2[6] =<br>1.3 V) | 2.529 – P2[6] | 2.606 – P2[6] | 2.665 - P2[6] | V    |

|                          | RefPower = Med<br>Opamp bias = Low   | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap +<br>P2[6] (P2[6] =<br>1.3 V) | 2.505 – P2[6] | 2.594 – P2[6] | 2.665 - P2[6] | V    |

|                          |                                      | $V_{AGND}$         | AGND      | 2 x Bandgap                               | 2.525         | 2.602         | 2.685         | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap –<br>P2[6] (P2[6] =<br>1.3 V) | 2.528 – P2[6] | 2.603 – P2[6] | 2.661 – P2[6] | V    |

Table 15. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR[5:3] | Reference Power<br>Settings          | Symbol             | Reference | Description                                                     | Min                        | Тур                        | Max                        | Unit |

|--------------------------|--------------------------------------|--------------------|-----------|-----------------------------------------------------------------|----------------------------|----------------------------|----------------------------|------|

|                          |                                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + BandGap                                    | V <sub>DD</sub> /2 + 1.225 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.361 | V    |

|                          | RefPower = High<br>Opamp bias = High | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                              | V <sub>DD</sub> /2 - 0.067 | V <sub>DD</sub> /2 - 0.002 | V <sub>DD</sub> /2 + 0.063 | V    |

|                          |                                      | $V_{REFLO}$        | Ref Low   | V <sub>DD</sub> /2 – BandGap                                    | V <sub>DD</sub> /2 – 1.35  | V <sub>DD</sub> /2 – 1.293 | V <sub>DD</sub> /2 – 1.210 | V    |

|                          |                                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + BandGap                                    | V <sub>DD</sub> /2 + 1.218 | V <sub>DD</sub> /2 + 1.294 | V <sub>DD</sub> /2 + 1.370 | V    |

| Db000                    | RefPower = High<br>Opamp bias = Low  | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                              | V <sub>DD</sub> /2 - 0.038 | V <sub>DD</sub> /2 - 0.001 | V <sub>DD</sub> /2 + 0.035 | V    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – BandGap                                    | V <sub>DD</sub> /2 – 1.329 | V <sub>DD</sub> /2 – 1.296 | V <sub>DD</sub> /2 – 1.259 | V    |

|                          |                                      | $V_{REFHI}$        | Ref High  | V <sub>DD</sub> /2 + BandGap                                    | V <sub>DD</sub> /2 + 1.221 | V <sub>DD</sub> /2 + 1.294 | V <sub>DD</sub> /2 + 1.366 | V    |

|                          | RefPower = Med<br>Opamp bias = High  | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                              | V <sub>DD</sub> /2 - 0.050 | V <sub>DD</sub> /2 – 0.002 | V <sub>DD</sub> /2 + 0.046 | V    |

|                          | Spamp state ingit                    | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – BandGap                                    | V <sub>DD</sub> /2 – 1.331 | V <sub>DD</sub> /2 – 1.296 | V <sub>DD</sub> /2 – 1.260 | V    |

|                          |                                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + BandGap                                    | V <sub>DD</sub> /2 + 1.226 | V <sub>DD</sub> /2 + 1.295 | V <sub>DD</sub> /2 + 1.365 | V    |

|                          | RefPower = Med<br>Opamp bias = Low   | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                              | V <sub>DD</sub> /2 - 0.028 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.025 | V    |

|                          | Spamp blas = Low                     | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – BandGap                                    | V <sub>DD</sub> /2 – 1.329 | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.262 | V    |

|                          |                                      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V)   | P2[4] + P2[6] -<br>0.098   | P2[4] + P2[6] -<br>0.018   | P2[4] + P2[6] +<br>0.055   | V    |

|                          | RefPower = High<br>Opamp bias = High | V <sub>AGND</sub>  | AGND      | P2[4]                                                           | P2[4]                      | P2[4]                      | P2[4]                      | _    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V) | P2[4] – P2[6] –<br>0.055   | P2[4] – P2[6] +<br>0.013   | P2[4] – P2[6] +<br>0.086   | V    |

|                          |                                      | V <sub>REFHI</sub> | Ref High  | P2[4] + P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V) | P2[4] + P2[6] -<br>0.082   | P2[4] + P2[6] -<br>0.011   | P2[4] + P2[6] +<br>0.050   | V    |

|                          | RefPower = High<br>Opamp bias = Low  | V <sub>AGND</sub>  | AGND      | P2[4]                                                           | P2[4]                      | P2[4]                      | P2[4]                      | _    |

| 0b001                    |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4] – P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V) | P2[4] – P2[6] –<br>0.037   | P2[4] – P2[6] +<br>0.006   | P2[4] – P2[6] +<br>0.054   | V    |

| 05001                    |                                      | V <sub>REFHI</sub> | Ref High  | P2[4] + P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V) | P2[4] + P2[6] -<br>0.079   | P2[4] + P2[6] -<br>0.012   | P2[4] + P2[6] +<br>0.047   | V    |

|                          | RefPower = Med<br>Opamp bias = High  | V <sub>AGND</sub>  | AGND      | P2[4]                                                           | P2[4]                      | P2[4]                      | P2[4]                      | _    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V)   | P2[4] – P2[6] –<br>0.038   | P2[4] – P2[6] +<br>0.006   | P2[4] – P2[6] +<br>0.057   | V    |

|                          |                                      | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V)   | P2[4] + P2[6] -<br>0.080   | P2[4] + P2[6] -<br>0.008   | P2[4] + P2[6] +<br>0.055   | V    |

|                          | RefPower = Med<br>Opamp bias = Low   | V <sub>AGND</sub>  | AGND      | P2[4]                                                           | P2[4]                      | P2[4]                      | P2[4]                      | _    |

|                          |                                      | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4]<br>= V <sub>DD</sub> /2, P2[6] =<br>0.5 V)   | P2[4] – P2[6] –<br>0.032   | P2[4] – P2[6] +<br>0.003   | P2[4] – P2[6] +<br>0.042   | V    |

Table 15. 3.3-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR[5:3] | Reference Power<br>Settings                   | Symbol             | Reference | Description | Min   | Тур         | Max         | Unit |

|--------------------------|-----------------------------------------------|--------------------|-----------|-------------|-------|-------------|-------------|------|

|                          |                                               | V <sub>REFHI</sub> | Ref High  | 2 x BandGap | 2.507 | 2.598       | 2.698       | V    |

|                          | RefPower = High<br>Opamp bias = High          | V <sub>AGND</sub>  | AGND      | BandGap     | 1.203 | 1.307       | 1.424       | V    |

|                          |                                               | V <sub>REFLO</sub> | Ref Low   | Vss         | Vss   | Vss + 0.012 | Vss + 0.067 | V    |

|                          |                                               | V <sub>REFHI</sub> | Ref High  | 2 x BandGap | 2.516 | 2.598       | 2.683       | V    |

|                          | RefPower = High<br>Opamp bias = Low           | V <sub>AGND</sub>  | AGND      | BandGap     | 1.241 | 1.303       | 1.376       | V    |

| 0b110                    |                                               | V <sub>REFLO</sub> | Ref Low   | Vss         | Vss   | Vss + 0.007 | Vss + 0.040 | V    |

| OBTTO                    | RefPower = Med<br>Opamp bias = High           | $V_{REFHI}$        | Ref High  | 2 x BandGap | 2.510 | 2.599       | 2.693       | V    |

|                          |                                               | V <sub>AGND</sub>  | AGND      | BandGap     | 1.240 | 1.305       | 1.374       | V    |

|                          |                                               | V <sub>REFLO</sub> | Ref Low   | Vss         | Vss   | Vss + 0.008 | Vss + 0.048 | V    |

|                          |                                               | V <sub>REFHI</sub> | Ref High  | 2 x BandGap | 2.515 | 2.598       | 2.683       | V    |

|                          | RefPower = Med<br>Opamp bias = Low            | V <sub>AGND</sub>  | AGND      | BandGap     | 1.258 | 1.302       | 1.355       | V    |

|                          |                                               | V <sub>REFLO</sub> | Ref Low   | Vss         | Vss   | Vss + 0.005 | Vss + 0.03  | V    |

| 0b111                    | All power settings.<br>Not allowed for 3.3 V. | _                  | _         | -           | _     | -           | _           | _    |

#### DC Analog PSoC Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 16. DC Analog PSoC Block Specifications

| Symbol          | Description                               | Min | Тур  | Max | Units | Notes |

|-----------------|-------------------------------------------|-----|------|-----|-------|-------|

| R <sub>CT</sub> | Resistor Unit Value (Continuous Time)     | _   | 12.2 | _   | kΩ    |       |

| C <sub>SC</sub> | Capacitor Unit Value (Switched Capacitor) | _   | 80   | ı   | fF    |       |

#### DC POR, SMP, and LVD Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \le T_A \le 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 17. DC POR, SMP, and LVD Specifications

| Symbol                                                            | Description                                                                                                        | Min         | Тур                  | Max         | Units          | Notes |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------|----------------------|-------------|----------------|-------|

| V <sub>PPOR0R</sub><br>V <sub>PPOR1R</sub><br>V <sub>PPOR2R</sub> | V <sub>DD</sub> Value for PPOR Trip (positive ramp)<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b | _           | 2.91<br>4.39<br>4.55 | -           | > > >          |       |

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub><br>V <sub>PPOR2</sub>    | V <sub>DD</sub> Value for PPOR Trip (negative ramp)<br>PORLEV[1:0] = 00b<br>PORLEV[1:0] = 01b<br>PORLEV[1:0] = 10b | _           | 2.82<br>4.39<br>4.55 | _           | V<br>V<br>V    |       |

| V <sub>PH0</sub><br>V <sub>PH1</sub><br>V <sub>PH2</sub>          | PPOR Hysteresis PORLEV[1:0] = 00b PORLEV[1:0] = 01b PORLEV[1:0] = 10b                                              | _<br>_<br>_ | 92<br>0<br>0         | -<br>-<br>- | mV<br>mV<br>mV |       |

#### Notes

- Always greater than 50 mV above PPOR (PORLEV = 00) for falling supply.

- 5. Always greater than 50 mV above PPOR (PORLEV = 10) for falling supply.

Table 17. DC POR, SMP, and LVD Specifications (continued)

| Symbol                                                                       | Description                                                                                                                                                                        | Min                                                          | Тур                                                          | Max                                                                   | Units                                 | Notes |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------|-------|

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD6<br>VLVD7         | V <sub>DD</sub> Value for LVD Trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.86<br>2.96<br>3.07<br>3.92<br>4.39<br>4.55<br>4.63<br>4.72 | 2.92<br>3.02<br>3.13<br>4.00<br>4.48<br>4.64<br>4.73<br>4.81 | 2.98 <sup>[4]</sup> 3.08 3.20 4.08 4.57 4.74 <sup>[5]</sup> 4.82 4.91 | V V V V V V V V V V V V V V V V V V V |       |

| VPUMP0<br>VPUMP1<br>VPUMP2<br>VPUMP3<br>VPUMP4<br>VPUMP5<br>VPUMP6<br>VPUMP7 | V <sub>DD</sub> Value for SMP Trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.96<br>3.03<br>3.18<br>4.11<br>4.55<br>4.63<br>4.72<br>4.90 | 3.02<br>3.10<br>3.25<br>4.19<br>4.64<br>4.73<br>4.82<br>5.00 | 3.08<br>3.16<br>3.32<br>4.28<br>4.74<br>4.82<br>4.91<br>5.10          | V<br>V<br>V<br>V<br>V<br>V            |       |

### DC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \,^{\circ}\text{C} \le T_{A} \le 85 \,^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $--40 \,^{\circ}\text{C} \le T_{A} \le 85 \,^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$ and are for design guidance only.

**Table 18. DC Programming Specifications**

| Symbol                | Description                                                                                 | Min                   | Тур | Max           | Units | Notes                                                                                   |

|-----------------------|---------------------------------------------------------------------------------------------|-----------------------|-----|---------------|-------|-----------------------------------------------------------------------------------------|

| V <sub>DDP</sub>      | V <sub>DD</sub> for programming and erase                                                   | 4.5                   | 5   | 5.5           | V     | This specification applies to the functional requirements of external programmer tools. |

| V <sub>DDLV</sub>     | Low V <sub>DD</sub> for verify                                                              | 3.0                   | 3.1 | 3.2           | V     | This specification applies to the functional requirements of external programmer tools. |

| V <sub>DDHV</sub>     | High V <sub>DD</sub> for verify                                                             | 5.1                   | 5.2 | 5.3           | V     | This specification applies to the functional requirements of external programmer tools. |

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operation                                                    | 3.15                  | -   | 5.25          | V     | This specification applies to this device when it is executing internal flash writes.   |

| I <sub>DDP</sub>      | Supply current during programming or verify                                                 | -                     | 10  | 30            | mA    |                                                                                         |

| $V_{ILP}$             | Input Low-voltage during programming or verify                                              | -                     | _   | 0.8           | V     |                                                                                         |

| $V_{IHP}$             | Input High-voltage during programming or verify                                             | 2.2                   | _   | _             | V     |                                                                                         |

| I <sub>ILP</sub>      | Input Current when Applying V <sub>ILP</sub> to P1[0] or P1[1] During Programming or Verify | -                     | _   | 0.2           | mA    | Driving internal pull-down resistor.                                                    |

| I <sub>IHP</sub>      | Input Current when Applying V <sub>IHP</sub> to P1[0] or P1[1] During Programming or Verify | -                     | -   | 1.5           | mA    | Driving internal pull-down resistor.                                                    |

| V <sub>OLV</sub>      | Output Low-voltage during programming or verify                                             | -                     | -   | Vss +<br>0.75 | V     |                                                                                         |

| V <sub>OHV</sub>      | Output High-voltage during programming or verify                                            | V <sub>DD</sub> - 1.0 | -   | $V_{DD}$      | V     |                                                                                         |

| Flash <sub>ENPB</sub> | flash endurance (per block)                                                                 | 50,000 <sup>[6]</sup> | -   | _             | -     | Erase/write cycles per block.                                                           |

| Flash <sub>ENT</sub>  | flash endurance (total)[7]                                                                  | 1,800,000             | _   | _             | -     | Erase/write cycles.                                                                     |

| Flash <sub>DR</sub>   | flash data retention                                                                        | 10                    | _   | _             | Years |                                                                                         |

## DC I<sup>2</sup>C Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \,^{\circ}\text{C} \le T_{A} \le 85 \,^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $-40 \,^{\circ}\text{C} \le T_{A} \le 85 \,^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$ and are for design guidance only.

Table 19. DC I<sup>2</sup>C Specifications

| Parameter                         | Description      | Min                 | Тур | Max                  | Units | Notes                                                      |

|-----------------------------------|------------------|---------------------|-----|----------------------|-------|------------------------------------------------------------|

| V <sub>ILI2C</sub> <sup>[8]</sup> | Input low level  | -                   | -   | $0.3 \times V_{DD}$  | V     | $3.0~V \leq V_{DD} \leq 3.6~V$                             |

|                                   |                  | _                   | -   | $0.25 \times V_{DD}$ | V     | $4.75 \text{ V} \le \text{V}_{DD} \le 5.25 \text{ V}$      |

| V <sub>IHI2C</sub> <sup>[8]</sup> | Input high level | $0.7 \times V_{DD}$ | -   | ı                    | V     | $3.0~\textrm{V} \leq \textrm{V}_{DD} \leq 5.25~\textrm{V}$ |

#### Notes

- 6. The 50,000 cycle flash endurance per block is only guaranteed if the Flash is operating within one voltage range. Voltage ranges are 3.0 V to 3.6 V and

- 4.75 V to 5.25 V.

7. A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36x2 blocks of 25,000 maximum cycles each, or 36x4 blocks of 12,500 maximum cycles each (to limit the total number of cycles to 36x50,000 and that no single block ever sees more than 50,000 cycles).

For the full industrial range, the user must employ a temperature sensor user module (flashTemp) and feed the result to the temperature argument before writing. Refer to the Flash APIs Application Note AN2015 at http://www.cypress.com under Application Notes for more information.

8. All GPIOs meet the DC GPIO V<sub>IL</sub> and V<sub>IH</sub> specifications found in the DC GPIO specifications sections. The I<sup>2</sup>C GPIO pins also meet the mentioned specs.

Document Number: 001-13105 Rev. \*I

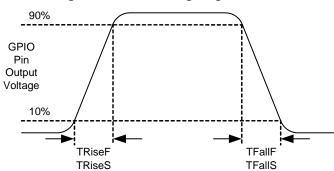

## AC GPIO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 21. AC GPIO Specifications

| Symbol            | Description                                  | Min | Тур | Max  | Units | Notes                                       |

|-------------------|----------------------------------------------|-----|-----|------|-------|---------------------------------------------|

| F <sub>GPIO</sub> | GPIO operating frequency                     | 0   | ı   | 12.3 | MHz   | Normal Strong Mode                          |

| TRiseF            | Rise time, normal strong mode, Cload = 50 pF | 3   | -   | 18   | ns    | V <sub>DD</sub> = 4.75 to 5.25 V, 10% - 90% |

| TFallF            | Fall time, normal strong mode, Cload = 50 pF | 2   | _   | 18   | ns    | V <sub>DD</sub> = 4.75 to 5.25 V, 10% - 90% |

| TRiseS            | Rise time, slow strong mode, Cload = 50 pF   | 10  | 27  | _    | ns    | V <sub>DD</sub> = 3 to 5.25 V, 10% - 90%    |

| TFallS            | Fall time, slow strong mode, Cload = 50 pF   | 10  | 22  | ı    | ns    | V <sub>DD</sub> = 3 to 5.25 V, 10% - 90%    |

Figure 10. GPIO Timing Diagram

## AC Operational Amplifier Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Settling times, slew rates, and gain bandwidth are based on the Analog Continuous Time PSoC block.

Power = High and Opamp Bias = High is not supported at 3.3V.

Table 22. 5-V AC Operational Amplifier Specifications

| Symbol            | Description                                                           | Min  | Тур | Max  | Units    | Notes |

|-------------------|-----------------------------------------------------------------------|------|-----|------|----------|-------|

| T <sub>ROA</sub>  | Rising Settling Time to 0.1% for a 1 V Step (10 pF load, Unity Gain)  |      |     |      |          | _     |

|                   | Power = Low, Opamp Bias = Low                                         | _    | _   | 3.9  | μS       |       |

|                   | Power = Medium, Opamp Bias = High                                     | _    | _   | 0.72 | μS       |       |

|                   | Power = High, Opamp Bias = High                                       | _    | _   | 0.62 | μS       |       |

| T <sub>SOA</sub>  | Falling Settling Time to 0.1% for a 1 V Step (10 pF load, Unity Gain) |      |     |      |          | _     |

|                   | Power = Low, Opamp Bias = Low                                         | _    | _   | 5.9  | μS       |       |

|                   | Power = Medium, Opamp Bias = High                                     | _    | _   | 0.92 | μS       |       |

|                   | Power = High, Opamp Bias = High                                       | _    | _   | 0.72 | μS       |       |

| SR <sub>ROA</sub> | Rising Slew Rate (20% to 80%) of a 1 V Step (10 pF load, Unity Gain)  |      |     |      |          | _     |

| 1.O/              | Power = Low, Opamp Bias = Low                                         | 0.15 | _   | _    | V/μs     |       |

|                   | Power = Medium, Opamp Bias = High                                     | 1.7  | _   | _    | V/μs     |       |

|                   | Power = High, Opamp Bias = High                                       | 6.5  | _   | _    | V/μs     |       |

| SR <sub>FOA</sub> | Falling Slew Rate (20% to 80%) of a 1 V Step (10 pF load, Unity Gain) |      |     |      |          | _     |

| 1 0/1             | Power = Low, Opamp Bias = Low                                         | 0.01 | _   | _    | V/μs     |       |

|                   | Power = Medium, Opamp Bias = High                                     | 0.5  | _   | _    | V/μs     |       |

|                   | Power = High, Opamp Bias = High                                       | 4.0  | _   | _    | V/μs     |       |

| BW <sub>OA</sub>  | Gain Bandwidth Product                                                |      |     |      |          | _     |

| 0,1               | Power = Low, Opamp Bias = Low                                         | 0.75 | _   | _    | MHz      |       |

|                   | Power = Medium, Opamp Bias = High                                     | 3.1  | _   | _    | MHz      |       |

|                   | Power = High, Opamp Bias = High                                       | 5.4  | _   | _    | MHz      |       |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = Medium, Opamp Bias = High)                    | _    | 100 | _    | nV/rt-Hz | -     |

|                   |                                                                       |      |     |      |          |       |

Table 23. 3.3-V AC Operational Amplifier Specifications

| Symbol            | Description                                                           | Min  | Тур | Max  | Units    | Notes |

|-------------------|-----------------------------------------------------------------------|------|-----|------|----------|-------|

| T <sub>ROA</sub>  | Rising settling time to 0.1% of a 1 V Step (10 pF load, Unity Gain)   |      |     |      |          | _     |

| 110/1             | Power = Low, Opamp Bias = Low                                         | _    | _   | 3.92 | μS       |       |

|                   | Power = Medium, Opamp Bias = High                                     | _    | _   | 0.72 | μS       |       |

| T <sub>SOA</sub>  | Falling settling time to 0.1% of a 1 V Step (10 pF load, Unity Gain)  |      |     |      |          | _     |

| 00/1              | Power = Low, Opamp Bias = Low                                         | _    | _   | 5.41 | μS       |       |

|                   | Power = Medium, Opamp Bias = High                                     | _    | _   | 0.72 | μS       |       |

| SR <sub>ROA</sub> | Rising Slew Rate (20% to 80%) of a 1 V Step (10 pF load, Unity Gain)  |      |     |      |          | -     |

|                   | Power = Low, Opamp Bias = Low                                         | 0.31 | _   | _    | V/μs     |       |

|                   | Power = Medium, Opamp Bias = High                                     | 2.7  | _   | _    | V/µs     |       |

| SR <sub>FOA</sub> | Falling slew rate (20% to 80%) of a 1 V Step (10 pF load, Unity Gain) |      |     |      |          | -     |

|                   | Power = Low, Opamp Bias = Low                                         | 0.24 | _   | _    | V/μs     |       |

|                   | Power = Medium, Opamp Bias = High                                     | 1.8  | _   | _    | V/µs     |       |

| BW <sub>OA</sub>  | Gain bandwidth product                                                |      |     |      |          | -     |

| 07.               | Power = Low, Opamp Bias = Low                                         | 0.67 | _   | _    | MHz      |       |

|                   | Power = Medium, Opamp Bias = High                                     | 2.8  | _   | _    | MHz      |       |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = Medium, Opamp Bias = High)                    | _    | 100 | _    | nV/rt-Hz | -     |

|                   |                                                                       |      |     |      |          |       |

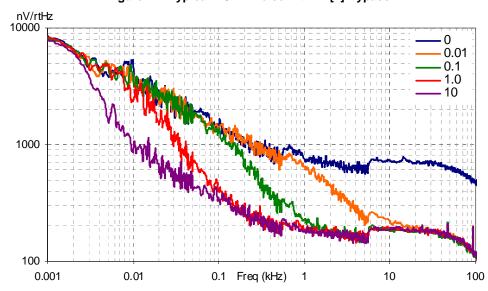

When bypassed by a capacitor on P2[4], the noise of the analog ground signal distributed to each block is reduced by a factor of up to 5 (14 dB). This is at frequencies above the corner frequency defined by the on-chip 8.1k resistance and the external capacitor.

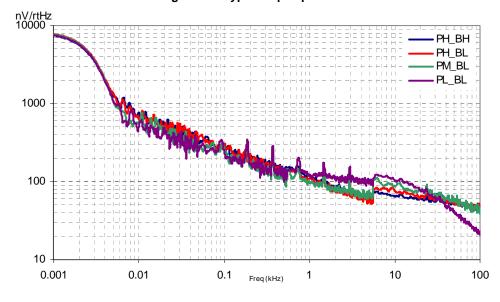

Figure 11. Typical AGND Noise with P2[4] Bypass

At low frequencies, the opamp noise is proportional to 1/f, power independent, and determined by device geometry. At high frequencies, increased power level reduces the noise spectrum level.

Figure 12. Typical Opamp Noise

## AC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

**Table 30. AC Programming Specifications**

| Symbol                    | Description                                | Min | Тур | Max                 | Units | Notes                                           |

|---------------------------|--------------------------------------------|-----|-----|---------------------|-------|-------------------------------------------------|

| T <sub>RSCLK</sub>        | Rise Time of SCLK                          | 1   | _   | 20                  | ns    | -                                               |

| T <sub>FSCLK</sub>        | Fall Time of SCLK                          | 1   | _   | 20                  | ns    | -                                               |

| T <sub>SSCLK</sub>        | Data Set up Time to Falling Edge of SCLK   | 40  | _   | _                   | ns    | -                                               |

| T <sub>HSCLK</sub>        | Data Hold Time from Falling Edge of SCLK   | 40  | _   | _                   | ns    | -                                               |

| F <sub>SCLK</sub>         | Frequency of SCLK                          | 0   | _   | 8                   | MHz   | -                                               |

| T <sub>ERASEB</sub>       | flash Erase Time (Block)                   | _   | 10  | _                   | ms    | _                                               |

| T <sub>WRITE</sub>        | flash Block Write Time                     | _   | 40  | _                   | ms    | -                                               |

| T <sub>DSCLK</sub>        | Data Out Delay from Falling Edge of SCLK   | _   | _   | 45                  | ns    | V <sub>DD</sub> > 3.6                           |

| T <sub>DSCLK3</sub>       | Data Out Delay from Falling Edge of SCLK   | _   | _   | 50                  | ns    | $3.0 \le V_{DD} \le 3.6$                        |

| T <sub>ERASEALL</sub>     | flash Erase Time (Bulk)                    | -   | 80  | _                   | ms    | Erase all blocks and protection fields at once. |

| T <sub>PROGRAM_HOT</sub>  | flash Block Erase + flash Block Write Time | _   | _   |                     | ms    | $0^{\circ}C \leq T_{J} \leq 100 ^{\circ}C$      |

| T <sub>PROGRAM_COLD</sub> | flash Block Erase + flash Block Write Time | _   | _   | 200 <sup>[15]</sup> | ms    | $-40$ °C $\leq$ T <sub>J</sub> $\leq$ 0 °C      |

### Note

<sup>15.</sup> For the full industrial range, the user must employ a Temperature Sensor User Module (flashTemp) and feed the result to the temperature argument before writing. Refer to the flash APIs Application Note AN2015 at http://www.cypress.com under Application Notes for more information.

### AC I<sup>2</sup>C Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 31. AC Characteristics of the I<sup>2</sup>C SDA and SCL Pins

| Cumbal                | Description                                                                                  | Standa | d-Mode | Fast-l              | Mode | Units | Notes |

|-----------------------|----------------------------------------------------------------------------------------------|--------|--------|---------------------|------|-------|-------|

| Symbol                | Description                                                                                  | Min    | Max    | Min                 | Max  | Units | Notes |

| F <sub>SCLI2C</sub>   | SCL Clock Frequency                                                                          | 0      | 100    | 0                   | 400  | kHz   | _     |

| T <sub>HDSTAI2C</sub> | Hold Time (repeated) START Condition. After this period, the first clock pulse is generated. | 4.0    | -      | 0.6                 | -    | μS    | -     |

| T <sub>LOWI2C</sub>   | LOW Period of the SCL Clock                                                                  | 4.7    | _      | 1.3                 | _    | μS    | _     |

| T <sub>HIGHI2C</sub>  | HIGH Period of the SCL Clock                                                                 | 4.0    | _      | 0.6                 | _    | μS    | _     |

| T <sub>SUSTAI2C</sub> | Set-up Time for a Repeated START Condition                                                   | 4.7    | _      | 0.6                 | _    | μS    | _     |

| T <sub>HDDATI2C</sub> | Data Hold Time                                                                               | 0      | _      | 0                   | _    | μS    | -     |

| T <sub>SUDATI2C</sub> | Data Set-up Time                                                                             | 250    | _      | 100 <sup>[16]</sup> | _    | ns    | _     |

| T <sub>SUSTOI2C</sub> | Set-up Time for STOP Condition                                                               | 4.0    | _      | 0.6                 | _    | μS    | _     |

| T <sub>BUFI2C</sub>   | Bus Free Time Between a STOP and START Condition                                             | 4.7    | _      | 1.3                 | _    | μS    | -     |

| T <sub>SPI2C</sub>    | Pulse Width of spikes are suppressed by the input filter.                                    | _      | _      | 0                   | 50   | ns    | _     |

I2C\_SDA

T\_SUDATI2C

T\_HDDATI2C

T\_HDDATI2C

T\_HUDATI2C

T\_HUDATI2C

T\_SUSTAI2C

T\_SUSTAI2C

T\_SUSTAI2C

T\_SUSTAI2C

T\_SUSTOI2C

T\_SUSTOI2

Figure 13. Definition for Timing for Fast-/Standard-Mode on the I<sup>2</sup>C Bus

#### Note

<sup>16.</sup> A Fast-Mode I2C-bus device can be used in a Standard-Mode I2C-bus system, but the requirement t<sub>SU-DAT</sub> ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-Mode I2C-bus specification) before the SCL line is released.

## **Accessories (Emulation and Programming)**

Table 35. Emulation and Programming Accessories

| Part No.         | Pin Package | Flex-Pod Kit <sup>[19]</sup> | Foot Kit <sup>[20]</sup> | Adapter <sup>[21]</sup>                            |

|------------------|-------------|------------------------------|--------------------------|----------------------------------------------------|

| CY8CLED16-48LFXI | 48-pin QFN  | CY3250-LED16QFN              |                          | Adapters can be found at http://www.emulation.com. |

## **Ordering Information**

### **Key Device Features**

The following table lists the CY8CLED16 EZ-Color devices' key package features and ordering codes.

Table 36. Device Key Features and Ordering Information

| Package                              | Ordering<br>Code  | Flash<br>(Bytes) | RAM<br>(Bytes) | Switch Mode<br>Pump | Temperature<br>Range | Digital PSoC<br>Blocks | Analog PSoC<br>Blocks | Digital I/O<br>Pins | Analog<br>Inputs | Analog<br>Outputs | XRES Pin |

|--------------------------------------|-------------------|------------------|----------------|---------------------|----------------------|------------------------|-----------------------|---------------------|------------------|-------------------|----------|

| 48-Pin QFN (Sawn)                    | CY8CLED16-48LTXI  | 32 K             | 2 K            | Yes                 | -40 °C to +85 °C     | 16                     | 12                    | 44                  | 12               | 4                 | Yes      |

| 48-Pin QFN<br>(Tape and Reel) (Sawn) | CY8CLED16-48LTXIT | 32 K             | 2 K            | Yes                 | –40 °C to +85 °C     | 16                     | 12                    | 44                  | 12               | 4                 | Yes      |

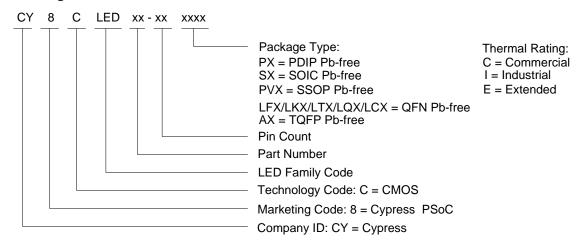

### **Ordering Code Definitions**

#### Note

<sup>19.</sup> Flex-Pod kit includes a practice flex-pod and a practice PCB, in addition to two flex-pods.

<sup>20.</sup> Foot kit includes surface mount feet that can be soldered to the target PCB.

<sup>21.</sup> Programming adapter converts non-DIP package to DIP footprint. Specific details and ordering information for each of the adapters can be found at <a href="http://www.emulation.com">http://www.emulation.com</a>.

Page 45 of 52

## **Acronyms**

## **Acronyms Used**

Table 37 lists the acronyms that are used in this document.

Table 37. Acronyms Used in this Datasheet

| Acronym | Description                                         | Acronym           | Description                                   |

|---------|-----------------------------------------------------|-------------------|-----------------------------------------------|

| AC      | alternating current                                 | MAC               | multiply-accumulate                           |

| ADC     | analog-to-digital converter                         | MIPS              | million instructions per second               |

| API     | application programming interface                   | PCB               | printed circuit board                         |

| CMOS    | complementary metal oxide semiconductor             | PDIP              | plastic dual-in-line package                  |

| CPU     | central processing unit                             | PLL               | phase-locked loop                             |

| CRC     | cyclic redundancy check                             | POR               | power-on reset                                |

| СТ      | continuous time                                     | PPOR              | precision power on reset                      |

| DAC     | digital-to-analog converter                         | PRS               | pseudo-random sequence                        |

| DC      | direct current                                      | PSoC <sup>®</sup> | Programmable System-on-Chip                   |

| DTMF    | dual-tone multi-frequency                           | PWM               | pulse-width modulator                         |

| ECO     | external crystal oscillator                         | QFN               | quad flat no leads                            |

| EEPROM  | electrically erasable programmable read-only memory | RTC               | real time clock                               |

| GPIO    | general purpose I/O                                 | SAR               | successive approximation                      |

| ICE     | in-circuit emulator                                 | SC                | switched capacitor                            |

| IDE     | integrated development environment                  | SMP               | switch mode pump                              |

| ILO     | internal low speed oscillator                       | SPI               | serial peripheral interface                   |

| IMO     | internal main oscillator                            | SRAM              | static random access memory                   |

| I/O     | input/output                                        | SROM              | supervisory read only memory                  |

| IrDA    | infrared data association                           | SSOP              | shrink small-outline package                  |

| ISSP    | in-system serial programming                        | UART              | universal asynchronous reciever / transmitter |

| LCD     | liquid crystal display                              | USB               | universal serial bus                          |

| LED     | light-emitting diode                                | WDT               | watchdog timer                                |

| LPC     | low power comparator                                | XRES              | external reset                                |

| LVD     | low-voltage detect                                  |                   | •                                             |

## **Reference Documents**

Design Aids – Reading and Writing PSoC® Flash – AN2015 (001-40459)

Understanding Datasheet Jitter Specifications for Cypress Timing Products – AN5054 (001-14503)

Application Notes for Surface Mount Assembly of Amkor's MicroLeadFrame (MLF) Packages – available at http://www.amkor.com.

Document Number: 001-13105 Rev. \*I

#### **Document Conventions**

#### Units of Measure

Table 38 lists the units of measures.

#### Table 38. Units of Measure

| Symbol | Unit of Measure | Symbol | Unit of Measure   |

|--------|-----------------|--------|-------------------|

| dB     | decibels        | ms     | milliseconds      |

| °C     | degree Celsius  | mH     | millihenry        |

| fF     | femtofarad      | ns     | nanoseconds       |