Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | S08                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | LINbus, SCI                                               |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 10x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 28-PDIP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08se8mrl |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

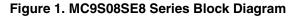

# 1 MCU Block Diagram

The block diagram, Figure 1, shows the structure of the MC9S08SE8 series MCUs.

pins not available on 16-pin package

Notes:

When PTA4 is configured as BKGD, pin is bi-directional.

For the 16-pin package: V<sub>SSA</sub>/V<sub>REFL</sub> and V<sub>DDA</sub>/V<sub>REFH</sub> are double bonded to V<sub>SS</sub> and V<sub>DD</sub> respectively.

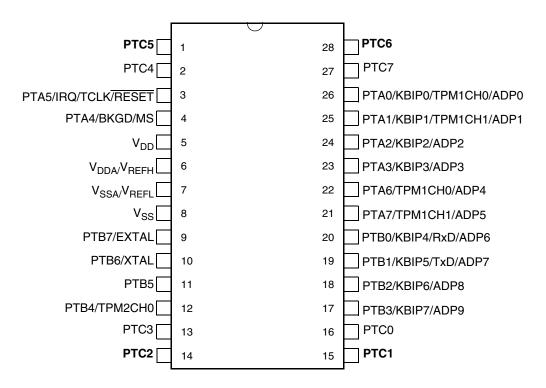

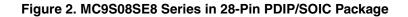

**Pin Assignments**

# 2 Pin Assignments

This chapter shows the pin assignments in the packages available for the MC9S08SE8 series.

Table 1. Pin Availability by Package Pin-Count

| Pin Nu<br>(Packa  |               | <        | - Lowest Pr | iority> Hig          | hest              |

|-------------------|---------------|----------|-------------|----------------------|-------------------|

| 28<br>(SOIC/PDIP) | 16<br>(TSSOP) | Port Pin | Alt 1       | Alt 2                | Alt 3             |

| 1                 |               | PTC5     |             |                      |                   |

| 2                 |               | PTC4     |             |                      |                   |

| 3                 | 1             | PTA5     | IRQ         | TCLK                 | RESET             |

| 4                 | 2             | PTA4     |             | BKGD                 | MS                |

| 5                 | 3             |          |             |                      | V <sub>DD</sub>   |

| 6                 |               |          |             | V <sub>DDA</sub>     | V <sub>REFH</sub> |

| 7                 |               |          |             | V <sub>SSA</sub>     | V <sub>REFL</sub> |

| 8                 | 4             |          |             |                      | V <sub>SS</sub>   |

| 9                 | 5             | PTB7     | EXTAL       |                      |                   |

| 10                | 6             | PTB6     | XTAL        |                      |                   |

| 11                | 7             | PTB5     |             |                      |                   |

| 12                | 8             | PTB4     |             | TPM2CH0              |                   |

| 13                |               | PTC3     |             |                      |                   |

| 14                | _             | PTC2     |             |                      |                   |

| 15                | _             | PTC1     |             |                      |                   |

| 16                |               | PTC0     |             |                      |                   |

| 17                | 9             | PTB3     | KBIP7       |                      | ADP9              |

| 18                | 10            | PTB2     | KBIP6       |                      | ADP8              |

| 19                | 11            | PTB1     | KBIP5       | TxD                  | ADP7              |

| 20                | 12            | PTB0     | KBIP4       | RxD                  | ADP6              |

| 21                | _             | PTA7     |             | TPM1CH1 <sup>1</sup> | ADP5              |

| 22                |               | PTA6     |             | TPM1CH0 <sup>1</sup> | ADP4              |

| 23                | 13            | PTA3     | KBIP3       |                      | ADP3              |

| 24                | 14            | PTA2     | KBIP2       |                      | ADP2              |

| 25                | 15            | PTA1     | KBIP1       | TPM1CH1 <sup>1</sup> | ADP1              |

| 26                | 16            | PTA0     | KBIP0       | TPM1CH0 <sup>1</sup> | ADP0              |

| 27                |               | PTC7     |             |                      |                   |

| 28                |               | PTC6     |             |                      |                   |

<sup>1</sup> TPM1 pins can be remapped to PTA7, PTA6 and PTA1,PTA0

Pins in **bold** are lost in the next lower pin count package.

The average chip-junction temperature  $(T_J)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

Where:

$\begin{array}{l} T_{A} = \text{Ambient temperature, }^{\circ}\text{C} \\ \theta_{JA} = \text{Package thermal resistance, junction-to-ambient, }^{\circ}\text{C/W} \\ P_{D} = P_{int} + P_{I/O} \\ P_{int} = I_{DD} \times V_{DD}, \text{Watts } - \text{chip internal power} \\ P_{I/O} = \text{Power dissipation on input and output pins } - \text{user-determined} \end{array}$

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2 \qquad Eqn. 3$$

Where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## 3.4 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM) and the charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model         | Description              | Symbol | Value | Unit |

|---------------|--------------------------|--------|-------|------|

| Human<br>body | Series resistance        | R1     | 1500  | Ω    |

|               | Storage capacitance      | С      | 100   | pF   |

|               | Number of pulses per pin | —      | 3     | —    |

|               | Series resistance        | R1     | 0     | Ω    |

| Machine       | Storage capacitance      | С      | 200   | pF   |

|               | Number of pulses per pin | _      | 3     | —    |

Table 5. ESD and Latch-up Test Conditions

| Num | С | Parameter                                                                                                                                                                                  | Symbol             | Min                         | Typical <sup>1</sup> | Max                  | Unit |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------|----------------------|----------------------|------|

| 5   | Ρ | Output low current — Max total I <sub>OL</sub> for all ports<br>5 V<br>3 V                                                                                                                 | I <sub>OLT</sub>   |                             |                      | 100<br>60            | mA   |

| 6   | Ρ | Input high voltage; all digital inputs                                                                                                                                                     | V <sub>IH</sub>    | $0.65 \times V_{DD}$        | _                    | —                    | v    |

| 7   | Ρ | Input low voltage; all digital inputs                                                                                                                                                      | V <sub>IL</sub>    |                             |                      | $0.35 \times V_{DD}$ | v    |

| 8   | Ρ | Input hysteresis; all digital inputs                                                                                                                                                       | V <sub>hys</sub>   | $0.06 \times V_{\text{DD}}$ | _                    | —                    | mV   |

| 9   | С | Input leakage current; input only pins <sup>2</sup>                                                                                                                                        | ll <sub>In</sub> l | —                           | 0.1                  | 1                    | μA   |

| 10  | Ρ | High impedance (off-state) leakage current <sup>2</sup>                                                                                                                                    | I <sub>oz</sub>    | —                           | 0.1                  | 1                    | μΑ   |

| 11  | С | Total leakage combined for all inputs and Hi-Z pins<br>— All input only and I/O <sup>2</sup>                                                                                               | I <sub>OZTOT</sub> | _                           | _                    | 2                    | μA   |

| 12  | Ρ | Internal pullup resistors <sup>3</sup>                                                                                                                                                     | R <sub>PU</sub>    | 20                          | 45                   | 65                   | kΩ   |

| 13  | Ρ | Internal pulldown resistors <sup>4</sup>                                                                                                                                                   | R <sub>PD</sub>    | 20                          | 45                   | 65                   | kΩ   |

| 14  | D | DC injection current <sup>5, 6, 7</sup><br>V <sub>IN</sub> < V <sub>SS</sub> , V <sub>IN</sub> > V <sub>DD</sub><br>Single pin limit<br>Total MCU limit, includes sum of all stressed pins | I <sub>IC</sub>    | 0.2<br>5                    |                      | 0.2<br>5             | mA   |

| 15  | С | Input capacitance; all non-supply pins                                                                                                                                                     | C <sub>In</sub>    |                             | _                    | 8                    | pF   |

| 16  | С | RAM retention voltage                                                                                                                                                                      | V <sub>RAM</sub>   | 0.6                         | 1.0                  | —                    | V    |

| 17  | Ρ | POR re-arm voltage <sup>8</sup>                                                                                                                                                            | V <sub>POR</sub>   | 0.9                         | 1.4                  | 2.0                  | V    |

| 18  | D | POR re-arm time                                                                                                                                                                            | t <sub>POR</sub>   | 10                          |                      | —                    | μs   |

| 19  | Ρ | Low-voltage detection threshold —<br>high range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                       | V <sub>LVD1</sub>  | 3.9<br>4.0                  | 4.0<br>4.1           | 4.1<br>4.2           | V    |

| 20  | Ρ | Low-voltage detection threshold —<br>low range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                        | V <sub>LVD0</sub>  | 2.48<br>2.54                | 2.56<br>2.62         | 2.64<br>2.70         | V    |

| 21  | С | Low-voltage warning threshold —<br>high range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                       | V <sub>LVW3</sub>  | 4.5<br>4.6                  | 4.6<br>4.7           | 4.7<br>4.8           | V    |

| 22  | Ρ | Low-voltage warning threshold —<br>high range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                       | V <sub>LVW2</sub>  | 4.2<br>4.3                  | 4.3<br>4.4           | 4.4<br>4.5           | v    |

| 23  | Ρ | Low-voltage warning threshold<br>low range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                          | V <sub>LVW1</sub>  | 2.84<br>2.90                | 2.92<br>2.98         | 3.00<br>3.06         | V    |

| 24  | С | Low-voltage warning threshold —<br>low range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                                                                                        | V <sub>LVW0</sub>  | 2.66<br>2.72                | 2.74<br>2.80         | 2.82<br>2.88         | V    |

### Table 7. DC Characteristics (continued)

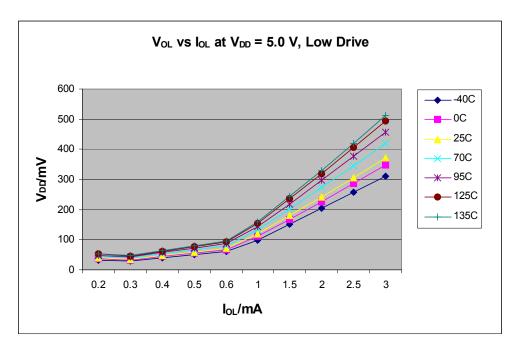

Figure 6. Typical V<sub>OL</sub> vs.  $I_{OL}$  for Low Drive Enabled Pad (V<sub>DD</sub> = 5 V)

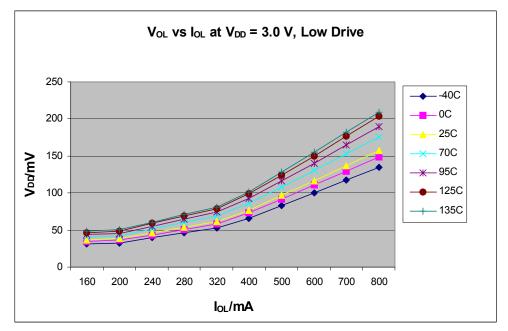

Figure 7. Typical V<sub>OL</sub> vs. I<sub>OL</sub> for Low Drive Enabled Pad (V<sub>DD</sub> = 3 V)

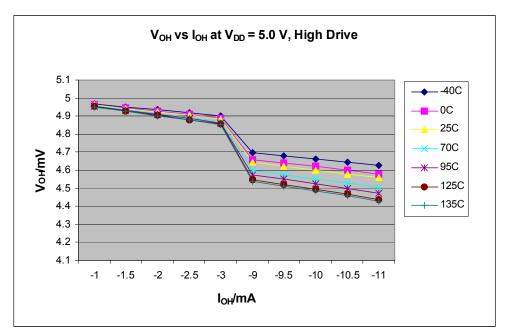

Figure 8. Typical V<sub>OH</sub> vs. I<sub>OH</sub> for High Drive Enabled Pad (V<sub>DD</sub> = 5 V)

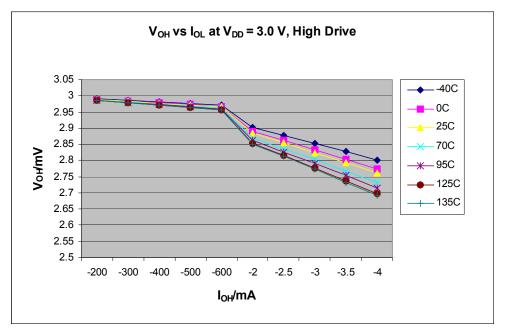

Figure 9. Typical V<sub>OH</sub> vs. I<sub>OH</sub> for High Drive Enabled Pad (V<sub>DD</sub> = 3 V)

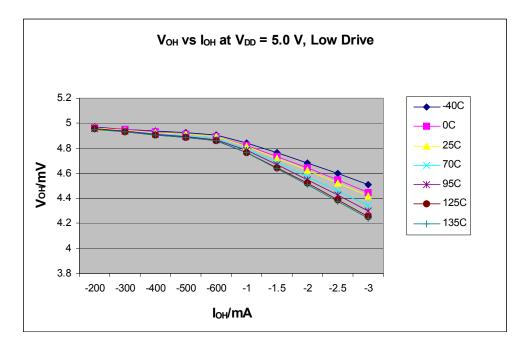

Figure 10. Typical V<sub>OH</sub> vs.  $I_{OH}$  for Low Drive Enabled Pad (V<sub>DD</sub> = 5 V)

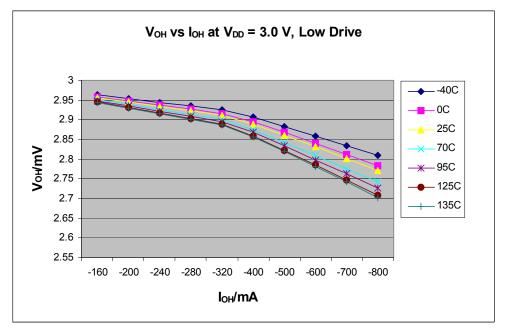

Figure 11. Typical V<sub>OH</sub> vs.  $I_{OH}$  for Low Drive Enabled Pad (V<sub>DD</sub> = 3 V)

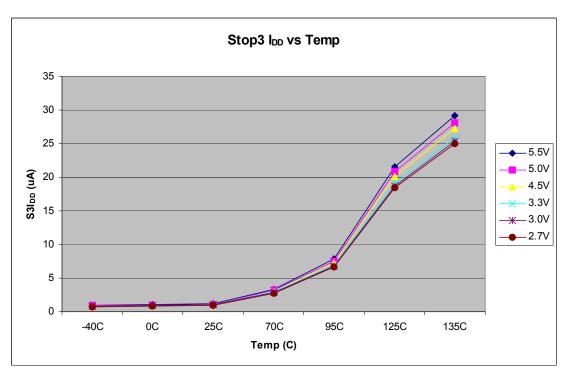

# 3.6 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

| Num | с                             | Parameter                                                          | Symbol                | V <sub>DD</sub><br>(V) | Typical <sup>1</sup> | Max              | Unit                                  | <b>Тетр</b><br><b>(</b> °С)           |

|-----|-------------------------------|--------------------------------------------------------------------|-----------------------|------------------------|----------------------|------------------|---------------------------------------|---------------------------------------|

| 1   | с                             | Run supply current <sup>2</sup> measured at                        | RI <sub>DD</sub>      | 5                      | 2.4                  | 2.72             | mA                                    | -40 to 125                            |

|     | Ĭ                             | (CPU clock = 4 MHz, f <sub>Bus</sub> = 2 MHz)                      | טטייי                 | 3                      | 2.18                 | 2.26             | 110.4                                 | 40 10 120                             |

| 2   | Р                             | Run supply current <sup>2</sup> measured at                        | RI <sub>DD</sub>      | 5                      | 6.35                 | 7.29             | mA                                    | -40 to 125                            |

|     |                               | (CPU clock = 20 MHz, f <sub>Bus</sub> = 10 MHz)                    | טטייי                 | 3                      | 5.79                 | 6.42             |                                       | 10 10 120                             |

| 3   | Р                             | Wait supply current <sup>2</sup> measured at                       | WI <sub>DD</sub>      | 5                      | 1.4                  | 1.56             | mA                                    | -40 to 125                            |

| 0   |                               | f <sub>Bus</sub> = 2 MHz                                           | UUUU                  | 3                      | 1.36                 | 1.53             | 110.4                                 | 40 10 120                             |

| 4   | Р                             | Stop2 mode supply current                                          | 501                   | 5                      | 1.4                  | 19<br>28<br>45.8 | μA                                    | -40 to 85<br>-40 to 105<br>-40 to 125 |

| 4   | + P Stop2 mode supply current | S2I <sub>DD</sub>                                                  | 3                     | 1.3                    | 15<br>22<br>37.2     | μA               | -40 to 85<br>-40 to 105<br>-40 to 125 |                                       |

| 5   | Р                             | Stop3 mode supply current                                          | 621                   | 5                      | 1.61                 | 23<br>43<br>76.1 | μA                                    | -40 to 85<br>-40 to 105<br>-40 to 125 |

| 5   | F                             | Stops mode supply current                                          | S3I <sub>DD</sub>     | 3                      | 1.44                 | 19<br>38<br>66.4 | μA                                    | -40 to 85<br>-40 to 105<br>-40 to 125 |

| 6   | Р                             | RTC adder to stop2 or stop3 <sup>3</sup>                           | ୧୦୦                   | 5                      | 300                  | 500<br>500       | nA                                    | –40 to 85<br>–40 to 125               |

|     |                               |                                                                    | S23I <sub>ddrti</sub> | 3                      | 300                  | 500<br>500       | nA                                    | -40 to 85<br>-40 to 125               |

| 7   | с                             | LVD adder to stop3 (LVDE = LVDSE = 1)                              | 631                   | 5                      | 122                  | 180              | μA                                    | -40 to 125                            |

|     |                               | L V D adder to stops (LV DE = LV DSE = 1)                          | S3I <sub>DDLVD</sub>  | 3                      | 110                  | 160              | μA                                    | -40 to 125                            |

| 8   | с                             | Adder to stop3 for oscillator enabled <sup>4</sup><br>(OSCSTEN =1) | S3I <sub>DDOSC</sub>  | 5,3                    | 5                    | 8                | μA                                    | -40 to 125                            |

### Table 8. Supply Current Characteristics

<sup>1</sup> Typical values are based on characterization data at 25 °C unless otherwise stated. See Figure 12 through Figure 13 for typical curves across voltage/temperature.

<sup>2</sup> All modules except ADC active, ICS configured for FBE, and does not include any dc loads on port pins.

<sup>3</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 220  $\mu$ A at 5 V with f<sub>Bus</sub> = 1 MHz.

<sup>4</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768 kHz crystal and low power mode (HGO = 0).

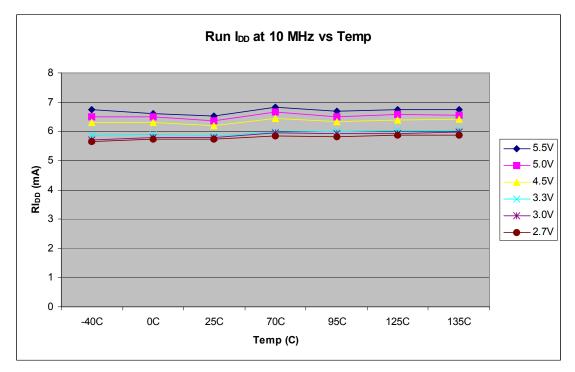

Figure 12. Typical Run I<sub>DD</sub> Curves

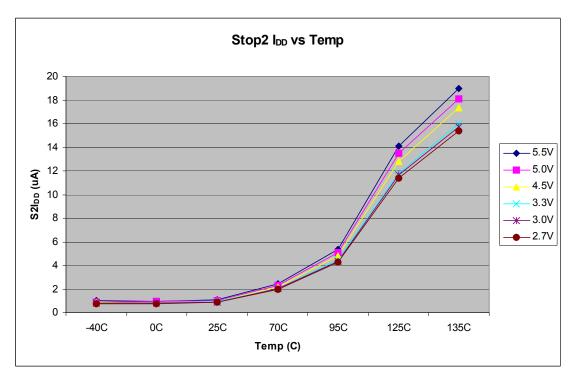

Figure 13. Typical Stop2 I<sub>DD</sub> Curves

Figure 14. Typical Stop3 I<sub>DD</sub> Curves

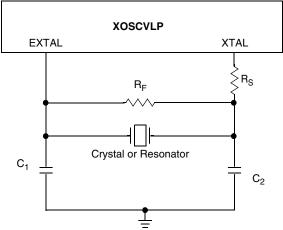

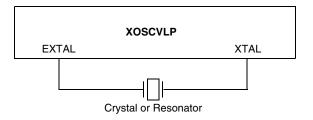

# 3.7 External Oscillator (XOSC) Characteristics

| Num | С | Characteristic                                                                                                                                                                                            | Symbol                                                       | Min.         | Typical <sup>1</sup>      | Max.            | Unit              |

|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------|---------------------------|-----------------|-------------------|

| 1   | С | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)<br>Low range (RANGE = 0)<br>High range (RANGE = 1), high gain (HGO = 1) <sup>2</sup><br>High range (RANGE = 1), low power (HGO = 0) <sup>2</sup> | f <sub>lo</sub><br>f <sub>hi-hgo</sub><br>f <sub>hi-lp</sub> | 32<br>1<br>1 |                           | 38.4<br>16<br>8 | kHz<br>MHz<br>MHz |

| 2   | _ | Load capacitors                                                                                                                                                                                           | C <sub>1,</sub> C <sub>2</sub>                               |              | crystal or<br>turer's rec |                 |                   |

| 3   | _ | Feedback resistor<br>Low range (32 kHz to 100 kHz)<br>High range (1 MHz to 16 MHz)                                                                                                                        | R <sub>F</sub>                                               | _            | 10<br>1                   | _               | MΩ                |

| 4   |   | Series resistor<br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0)                                                     | Rs                                                           |              | 0<br>100<br>0             |                 | kΩ                |

| 4   |   | High range, high gain (RANGE = 1, HGO = 1)<br>≥ 8 MHz<br>4 MHz<br>1 MHz                                                                                                                                   |                                                              |              | 0<br>0<br>0               | 0<br>10<br>20   | N32               |

| Num | С | Characteristic                                                                                                                                                                                                                                   | Symbol                                          | Min.           | Typical <sup>1</sup>  | Max.     | Unit       |

|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------|-----------------------|----------|------------|

| 5   | т | Crystal start-up time <sup>3</sup><br>Low range, low gain (RANGE = 0, HGO = 0)<br>Low range, high gain (RANGE = 0, HGO = 1)<br>High range, low gain (RANGE = 1, HGO = 0) <sup>4</sup><br>High range, high gain (RANGE = 1, HGO = 1) <sup>4</sup> | t<br>CSTL-LP<br>ÇSTH-HGO<br>CSTH-LP<br>CSTH-HGO | <br> <br> <br> | 200<br>400<br>5<br>15 |          | ms         |

| 6   | Т | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1)<br>FEE or FBE mode <sup>2</sup><br>FBELP mode                                                                                                                                         | f <sub>extal</sub>                              | 0.03125<br>0   |                       | 20<br>20 | MHz<br>MHz |

Table 9. Oscillator electrical specifications (Temperature Range = -40 to 125°C Ambient)

$^1\,$  Typical column was characterized at 5.0 V, 25  $^\circ C$  or is recommended value.

<sup>2</sup> The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications. This data will vary based upon the crystal manufacturer and board design. The crystal should be characterized by the crystal manufacturer.

<sup>4</sup> 4 MHz crystal.

Figure 15. Typical Crystal or Resonator Circuit: High Range and Low Range/High Gain

Figure 16. Typical Crystal or Resonator Circuit: Low Range/Low Power

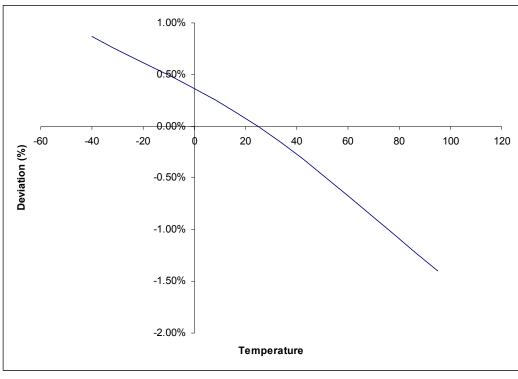

Figure 17. Deviation of DCO Output from Trimmed Frequency (20 MHz, 3.0 V)

# 3.9 ADC Characteristics

| Characteristic              | Conditions                                                          | Symb              | Min               | Typ <sup>1</sup> | Мах               | Unit | Comment            |

|-----------------------------|---------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|------|--------------------|

| Supply voltage              | Absolute                                                            | V <sub>DDA</sub>  | 2.7               | _                | 5.5               | V    |                    |

| Supply voltage              | Delta to $V_{DD} (V_{DD} - V_{DDA})^2$                              | $\Delta V_{DDA}$  | -100              | 0                | 100               | mV   |                    |

| Ground voltage              | Delta to $V_{SS} (V_{SS} - V_{SSA})^2$                              | $\Delta V_{SSA}$  | -100              | 0                | 100               | mV   |                    |

| Input voltage               |                                                                     | V <sub>ADIN</sub> | V <sub>REFL</sub> | —                | V <sub>REFH</sub> | V    |                    |

| Input capacitance           |                                                                     | C <sub>ADIN</sub> | _                 | 4.5              | 5.5               | pF   |                    |

| Input resistance            |                                                                     | R <sub>ADIN</sub> | _                 | 3                | 5                 | kΩ   |                    |

| Analog source<br>resistance | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   |                   |                  | 5<br>10           | kΩ   | External to<br>MCU |

|                             | 8-bit mode (all valid f <sub>ADCK</sub> )                           |                   |                   | —                | 10                |      |                    |

| ADC conversion              | High speed (ADLPC = 0)                                              | f <sub>ADCK</sub> | 0.4               | —                | 8.0               | MHz  |                    |

| clock frequency             | Low power (ADLPC = 1)                                               | ADCK              | 0.4               |                  | 4.0               |      |                    |

Table 11. 10-Bit ADC Operating Conditions

| Table 12. To-Dit ADO Onaracteristics (V <sub>REFH</sub> – V <sub>DDA</sub> , V <sub>REFL</sub> – V <sub>SSA</sub> ) (continued) |                           |          |                     |      |                  |      |                  |                                            |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|---------------------|------|------------------|------|------------------|--------------------------------------------|

| Characteristic                                                                                                                  | Conditions                | С        | Symb                | Min  | Typ <sup>1</sup> | Max  | Unit             | Comment                                    |

| ADC                                                                                                                             | High Speed (ADLPC = 0)    | <b>_</b> |                     | 2    | 3.3              | 5    |                  | t <sub>ADACK</sub> =                       |

| Asynchronous<br>Clock Source                                                                                                    | Low Power (ADLPC = 1)     | D        | f <sub>ADACK</sub>  | 1.25 | 2                | 3.3  | MHz              | 1/f <sub>ADACK</sub>                       |

| Conversion<br>Time (Including                                                                                                   | Short Sample (ADLSMP = 0) | D        | t <sub>ADC</sub>    | _    | 20               | _    | ADCK             | See SE8                                    |

| sample time)                                                                                                                    | Long Sample (ADLSMP = 1)  |          |                     |      | 40               |      | cycles           | reference                                  |

| Sample Time                                                                                                                     | Short Sample (ADLSMP = 0) | D        | t <sub>ADS</sub>    | _    | 3.5              | _    | ADCK<br>cycles   | manual for<br>conversion<br>time variances |

|                                                                                                                                 | Long Sample (ADLSMP = 1)  |          |                     | _    | 23.5             | _    | Cycles           |                                            |

| Temp Sensor                                                                                                                     | –40°C– 25°C               | D        | ~                   |      | 3.266            |      | mV/°C            |                                            |

| Slope                                                                                                                           | 25°C– 125°C               | D        | m                   | _    | 3.638            | _    | mv/ C            |                                            |

| Temp Sensor<br>Voltage                                                                                                          | 25°C                      | D        | V <sub>TEMP25</sub> | _    | 1.396            | _    | mV               |                                            |

| Characteristics                                                                                                                 | for 28-pin packages only  |          |                     |      |                  |      |                  |                                            |

| Total                                                                                                                           | 10-bit mode               | Ρ        | _                   |      | ±1               | ±2.5 | 1.003            | Includes                                   |

| Unadjusted<br>Error                                                                                                             | 8-bit mode                | Ρ        | E <sub>TUE</sub>    | -    | ±0.5             | ±1.0 | LSB <sup>3</sup> | quantization                               |

| Differential                                                                                                                    | 10-bit mode <sup>2</sup>  | Ρ        |                     | _    | ±0.5             | ±1.0 | LSB <sup>3</sup> |                                            |

| Non-Linearity                                                                                                                   | 8-bit mode <sup>3</sup>   | Ρ        | DNL                 |      | ±0.3             | ±0.5 | LSB              |                                            |

| Integral                                                                                                                        | 10-bit mode               | Т        | INL                 |      | ±0.5             | ±1.0 | LSB <sup>3</sup> |                                            |

| Non-Linearity                                                                                                                   | 8-bit mode                | Т        |                     | _    | ±0.3             | ±0.5 | LOD              |                                            |

| Zero-Scale                                                                                                                      | 10-bit mode               | Ρ        | E                   | _    | ±0.5             | ±1.5 | LSB <sup>3</sup> | V <sub>ADIN</sub> = V <sub>SSA</sub>       |

| Error                                                                                                                           | 8-bit mode                | Ρ        | E <sub>ZS</sub>     | _    | ±0.5             | ±0.5 | LOD              | VADIN = VSSA                               |

| Full-Scale                                                                                                                      | 10-bit mode               | Т        | <b>E</b> .          | _    | ±0.5             | ±1   | LSB <sup>3</sup> | V – V                                      |

| Error                                                                                                                           | 8-bit mode                | Т        | E <sub>FS</sub>     | _    | ±0.5             | ±0.5 | LOD              | $V_{ADIN} = V_{DDA}$                       |

| Quantization                                                                                                                    | 10-bit mode               | D        | Eq                  |      | —                | ±0.5 | LSB <sup>3</sup> |                                            |

| Error                                                                                                                           | 8-bit mode                | D        | LQ                  |      | —                | ±0.5 | LOD              |                                            |

| Input Leakage                                                                                                                   | 10-bit mode               | D        | E <sub>IL</sub>     |      | ±0.2             | ±2.5 | LSB <sup>3</sup> | Pad leakage <sup>4</sup> *                 |

| Error                                                                                                                           | 8-bit mode                | D        |                     | _    | ±0.1             | ±1   | LOD              | R <sub>AS</sub>                            |

| Characteristics                                                                                                                 | for 16-pin package only   |          |                     |      |                  |      |                  |                                            |

| Total                                                                                                                           | 10-bit mode               | Ρ        | F                   |      | ±1.5             | ±3.5 | 1003             | Includes                                   |

| Unadjusted<br>Error                                                                                                             | 8-bit mode                | Ρ        | E <sub>TUE</sub>    | _    | ±0.7             | ±1.5 | LSB <sup>3</sup> | quantization                               |

### Table 12. 10-Bit ADC Characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ ) (continued)

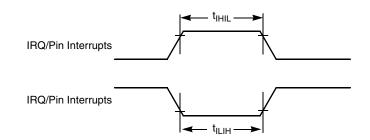

Figure 20. IRQ/Pin Interrupt Timing

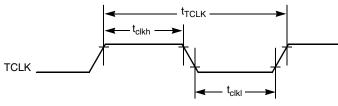

## 3.10.2 TPM/MTIM Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Num | С | Rating                    | Symbol              | Min | Max                 | Unit             |

|-----|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1   | D | External clock frequency  | f <sub>TPMext</sub> | DC  | f <sub>Bus</sub> /4 | MHz              |

| 2   | D | External clock period     | t <sub>TPMext</sub> | 4   | —                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

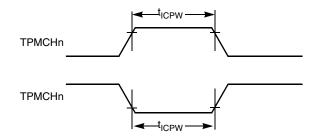

| 5   | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 |                     | t <sub>cyc</sub> |

Table 14. TPM Input Timing

Figure 21. Timer External Clock

Figure 22. Timer Input Capture Pulse

Ordering Information

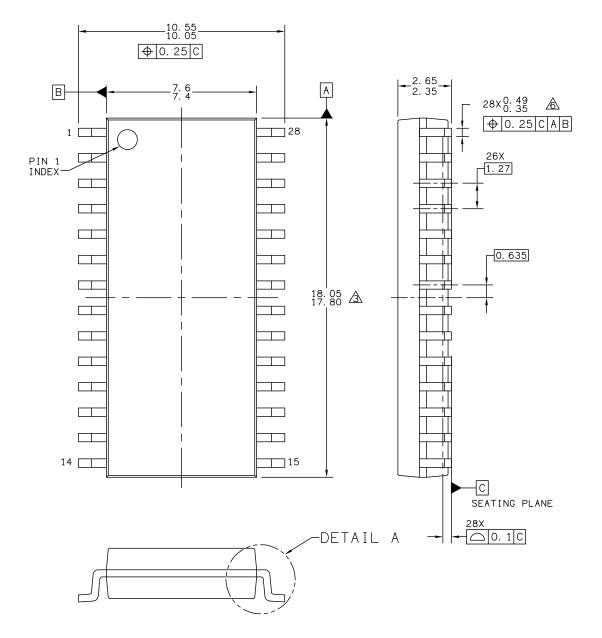

# 4.1 Package Information

| Pin Count | Package Type                      | Abbreviation | Designator | Case No. | Document No. |

|-----------|-----------------------------------|--------------|------------|----------|--------------|

| 28        | Plastic Dual In-line Pin          | PDIP         | RL         | 710      | 98ASB42390B  |

| 28        | Small Outline Integrated Circuit  | SOIC         | WL         | 751F     | 98ASB42345B  |

| 16        | Thin Shrink Small Outline Package | TSSOP        | TG         | 948F     | 98ASH70247A  |

Table 16. Package Descriptions

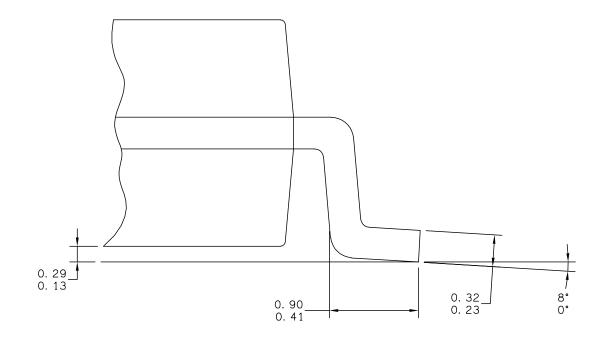

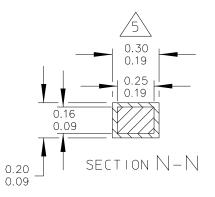

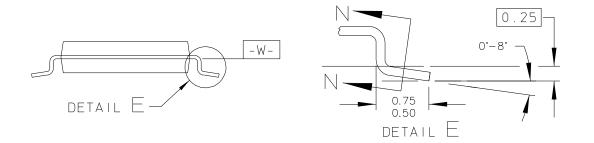

# 4.2 Mechanical Drawings

The following pages are mechanical drawings for the packages described in Table 16.

**Ordering Information**

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION N    | PRINT VERSION NOT TO SCALE |  |  |

|---------------------------------------------------------|--------------------|--------------------|----------------------------|--|--|

| TITLE: SOIC, WIDE BOD                                   | DOCUMENT           | NO: 98ASB42345B    | REV: G                     |  |  |

| 28 LEAD                                                 | ,                  | BER: 751F-05       | 10 MAR 2005                |  |  |

| CASEOUTLINE                                             | STANDARD           | STANDARD: MS-013AE |                            |  |  |

**Ordering Information**

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA                | LOUTLINE    | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------------|-------------|----------------------------|-------------|

| TITLE: SOIC, WIDE BOD                                   | DOCUMENT NO: 98ASB42345B |             | REV: G                     |             |

| 28 LEAD<br>CASEOUTLINE                                  |                          | CASE NUMBER | R: 751F-05                 | 10 MAR 2005 |

|                                                         |                          | STANDARD:   | MS-013AE                   |             |

NOTES:

- POSITIONAL TOLERANCE OF LEADS, SHALL BE WITHIN 0.25 MM (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- $\boxed{3}$  dimension does not include mold flash.

- 4. 710-01 OBSOLETE, NEW STD 710-02.

- 5. CONTROLLING DIMENSION: INCH

|            | IN                                                                 | СН    | MILI                | IMETER                              |                     | INCH        |             | MIL | MILLIMETER |  |

|------------|--------------------------------------------------------------------|-------|---------------------|-------------------------------------|---------------------|-------------|-------------|-----|------------|--|

| DIM        | MIN                                                                | MAX   | MIN                 | MAX                                 | DIM                 | MIN         | MAX         | MIN | МАХ        |  |

| А          | 1.435                                                              | 1.465 | 36.45               | 37.21                               |                     |             |             |     |            |  |

| В          | 0.540                                                              | 0.560 | 13.72               | 14.22                               |                     |             |             |     |            |  |

| С          | 0.155                                                              | 0.200 | 3.94                | 5.08                                |                     |             |             |     |            |  |

| D          | 0.014                                                              | 0.022 | 0.36                | 0.56                                |                     |             |             |     |            |  |

| F          | 0.040                                                              | 0.060 | 1.02                | 1.52                                |                     |             |             |     |            |  |

| G          | 0.100                                                              | BSC   | 2.54 BSC            |                                     |                     |             |             |     |            |  |

| Н          | 0.065                                                              | 0.085 | 1.65                | 2.16                                |                     |             |             |     |            |  |

| J          | 0.008                                                              | 0.015 | 0.20                | 0.38                                |                     |             |             |     |            |  |

| К          | 0.115                                                              | 0.135 | 2.92                | 3.43                                |                     |             |             |     |            |  |

| L          | L 0.600 BSC 15.24                                                  |       | 24 BSC              |                                     |                     |             |             |     |            |  |

| М          | 0*                                                                 | 15°   | 0°                  | 15°                                 |                     |             |             |     |            |  |

| N          | 0.020                                                              | 0.040 | 0.51                | 1.02                                |                     |             |             |     |            |  |

|            |                                                                    |       |                     |                                     |                     |             |             |     |            |  |

| © FI       | © FREESCALE SEMICONDUCTOR, INC. MECHANICAL<br>ALL RIGHTS RESERVED. |       |                     | AL OUTLINE PRINT VERSION NOT TO SCA |                     |             | IT TO SCALE |     |            |  |

| TITLE      | TITLE:                                                             |       |                     | DOCUMENT NO: 98ASB42390B            |                     |             | RE∨: D      |     |            |  |

| 28 LD PDIP |                                                                    |       | CASE NUMBER: 710-02 |                                     |                     | 24 MAY 2005 |             |     |            |  |

|            |                                                                    |       |                     |                                     | STANDARD: NON-JEDEC |             |             |     |            |  |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | Mechanical outline |              | PRINT VERSION NOT TO SCALE |  |  |

|---------------------------------------------------------|--------------------|--------------|----------------------------|--|--|

| TITLE:                                                  | DOCUMENT NE        | 98ASH70247A  | RE∨: B                     |  |  |

| 16 LD TSSOP, PITCH 0.                                   | CASE NUMBER        | 948F-01      | 19 MAY 2005                |  |  |

|                                                         | 0.01111            | STANDARD: JE | DEC                        |  |  |