#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed8MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.5KB (1K × 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 × 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)Purchase URLhttps://www.e-xfl.com/product-detail/microchip-technology/pic12f519-i-mc |                            |                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitSpeed8MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                          | Product Status             | Active                                                                   |

| Speed8MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                        | Core Processor             | PIC                                                                      |

| Connectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                 | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-DFN (2x3)                                                                                                                                                                                                        | Speed                      | 8MHz                                                                     |

| Number of I/O5Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                 | Connectivity               | -                                                                        |

| Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                               | Peripherals                | POR, WDT                                                                 |

| Program Memory TypeFLASHEEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                 | Number of I/O              | 5                                                                        |

| EEPROM Size-RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                         | Program Memory Size        | 1.5KB (1K x 12)                                                          |

| RAM Size41 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                                     | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                                                   | EEPROM Size                | -                                                                        |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                                                                                      | RAM Size                   | 41 x 8                                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                                                                                                      | Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VFDFN Exposed PadSupplier Device Package8-DFN (2x3)                                                                                                                                                                                                                                                                                                                                                             | Data Converters            | -                                                                        |

| Mounting Type     Surface Mount       Package / Case     8-VFDFN Exposed Pad       Supplier Device Package     8-DFN (2x3)                                                                                                                                                                                                                                                                                                                                                                      | Oscillator Type            | Internal                                                                 |

| Package / Case     8-VFDFN Exposed Pad       Supplier Device Package     8-DFN (2x3)                                                                                                                                                                                                                                                                                                                                                                                                            | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Supplier Device Package 8-DFN (2x3)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic12f519-i-mc                                                                                                                                                                                                                                                                                                                                                                                                           | Supplier Device Package    | 8-DFN (2x3)                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f519-i-mc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# PIC12F519

NOTES:

# PIC12F519

NOTES:

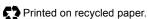

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

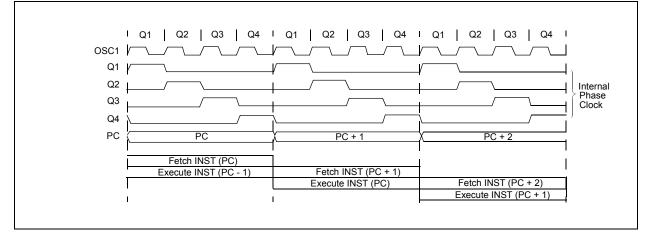

# 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

| Addr               | Name     | Bit 7                                | Bit 6          | Bit 5         | Bit 4         | Bit 3            | Bit 2     | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset |

|--------------------|----------|--------------------------------------|----------------|---------------|---------------|------------------|-----------|-----------|-----------|-------------------------------|

| N/A                | TRISGPIO | —                                    | —              | TRISGPI05     | TRISGPI04     | TRISGPI03        | TRISGPI02 | TRISGPI01 | TRISGPI00 | 11 1111                       |

| N/A                | OPTION   | Contains C                           | ontrol Bits to | Configure Tin | ner0 and Time | 0/WDT Presca     | ller      |           | •         | 1111 1111                     |

| 00h                | INDF     | Uses Conte                           | ents of FSR    | to Address Da | ta Memory (no | t a physical reg | jister)   |           |           | xxxx xxxx                     |

| 01h                | TMR0     | Timer0 Mo                            | dule Registe   | r             |               |                  |           |           |           | xxxx xxxx                     |

| 02h <sup>(1)</sup> | PCL      | Low Order 8 bits of PC               |                |               |               |                  | 1111 1111 |           |           |                               |

| 03h                | STATUS   | GPWUF                                | —              | PA0           | TO            | PD               | Z         | DC        | С         | 0-01 1xxx                     |

| 04h                | FSR      | Indirect Data Memory Address Pointer |                |               |               |                  | 110x xxxx |           |           |                               |

| 05h                | OSCCAL   | CAL6                                 | CAL5           | CAL4          | CAL3          | CAL2             | CAL1      | CAL0      | —         | 1111 111-                     |

| 06h                | GPIO     | —                                    | —              | GP5           | GP4           | GP3              | GP2       | GP1       | GP0       | xx xxxx                       |

| 21h                | EECON    | —                                    | —              | _             | FREE          | WRERR            | WREN      | WR        | RD        | 0 x000                        |

| 25h                | EEDATA   | EEDATA7                              | EEDATA6        | EEDATA5       | EEDATA4       | EEDATA3          | EEDATA2   | EEDATA1   | EEDATA0   | xxxx xxxx                     |

| 26h                | EEADR    | —                                    | -              | EEADR5        | EEADR4        | EEADR3           | EEADR2    | EEADR1    | EEADR0    | xx xxxx                       |

**TABLE 4-1:** SPECIAL FUNCTION REGISTER SUMMARY

Legend: Note 1

x = unknown, u = unchanged, – = unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused The upper byte of the Program Counter is not directly accessible. See **Section 4.6 "Program Counter"** for an explanation of how to access these bits. 1:

# 4.3 STATUS register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see **Section 9.0 "Instruction Set Summary"**.

# REGISTER 4-1: STATUS: STATUS REGISTER

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                  | R-1 | R-1                           | R/W-x                   | R/W-x            | R/W-x  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|-------------------------------|-------------------------|------------------|--------|--|

| GPWUF         |                                                                                                                                                                                                                                                                                                                                                                                                                                | PA0                                    | TO  | PD                            | Z                       | DC               | С      |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |     |                               |                         |                  | bit 0  |  |

| <u>.</u>      |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |     |                               |                         |                  |        |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | .,  | 11 11.2                       |                         | (0)              |        |  |

| R = Readable  |                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable b                         | It  | •                             | emented bit, read       |                  |        |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                       |     | '0' = Bit is c                | leared                  | x = Bit is unkno | own    |  |

| bit 7         | <b>GPWUF</b> : Wake-up From Sleep on Pin Change bit<br>1 = Reset due to wake-up from Sleep on pin change<br>0 = After power-up or other Reset                                                                                                                                                                                                                                                                                  |                                        |     |                               |                         |                  |        |  |

| bit 6         | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                     | ted: Read as '0'                       |     |                               |                         |                  |        |  |

| bit 5         | <b>PA0</b> : Program<br>1 = Page 1 (0<br>0 = Page 0 (2                                                                                                                                                                                                                                                                                                                                                                         |                                        | bit |                               |                         |                  |        |  |

| bit 4         | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                                                                                |                                        |     |                               |                         |                  |        |  |

| bit 3         | <b>PD</b> : Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                     |                                        |     |                               |                         |                  |        |  |

| bit 2         | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                                                                                                                                                                    |                                        |     |                               |                         |                  |        |  |

| bit 1         | <ul> <li>DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)</li> <li>ADDWF:</li> <li>1 = A carry from the 4th low-order bit of the result occurred</li> <li>0 = A carry from the 4th low-order bit of the result did not occur</li> <li>SUBWF:</li> <li>1 = A borrow from the 4th low-order bit of the result did not occur</li> <li>0 = A borrow from the 4th low-order bit of the result did not occur</li> </ul> |                                        |     |                               |                         |                  |        |  |

| bit 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                | ow bit (for ADDWF<br>SU<br>ccurred 1 : |     | RRF, RLF instr<br>d not occur | uctions)<br>RRF or RLF: | o or MSb, respec | tively |  |

# 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the <code>OPTION</code> instruction, the contents of the W register will be transferred to the <code>OPTION</code> register. A Reset sets the <code>OPTION<7:0></code> bits.

| Note: | If the T0SC bit is set to '1', it will override |

|-------|-------------------------------------------------|

|       | the TRIS function on the T0CKI pin.             |

### **REGISTER 4-2: OPTION: OPTION REGISTER**

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | TOCS | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

| Legend:       |                                                                                                                                                                                     |                                                                             |                                                                           |                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|

| R = Readable  | e bit W = V                                                                                                                                                                         | Writable bit                                                                | х                                                                         | = Bit is unknown    |

| -n = Value at | POR '1' =                                                                                                                                                                           | Bit is set                                                                  | '(                                                                        | 0' = Bit is cleared |

| bit 7         | bit 7 <b>GPWU:</b> Enable Wake-up On Pin Change 1 = Disabled                                                                                                                        |                                                                             |                                                                           |                     |

| bit 6         | 0 = Enabled<br>GPPU: Enable Wea                                                                                                                                                     | k Dull upp bit                                                              |                                                                           |                     |

| DIL O         | 1 = Disabled<br>0 = Enabled                                                                                                                                                         | ik Full-ups bit                                                             |                                                                           |                     |

| bit 5         | <b>TOCS:</b> Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                                         |                                                                             |                                                                           |                     |

| bit 4         | <ul> <li>TOSE: Timer0 Source Edge Select bit</li> <li>1 = Increment on high-to-low transition on T0CKI pin</li> <li>0 = Increment on low-to-high transition on T0CKI pin</li> </ul> |                                                                             |                                                                           |                     |

| bit 3         | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler assigned to the WDT</li> <li>0 = Prescaler assigned to Timer0</li> </ul>                                              |                                                                             |                                                                           |                     |

| bit 2-0       | PS<2:0>: Prescaler                                                                                                                                                                  |                                                                             |                                                                           |                     |

|               | Bit Value                                                                                                                                                                           | Timer0 Rate                                                                 | WDT Rate                                                                  |                     |

|               | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                                                | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |                     |

### 8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

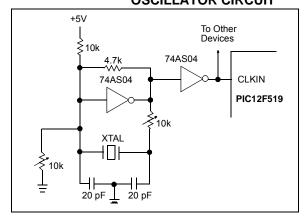

Figure 8-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 8-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

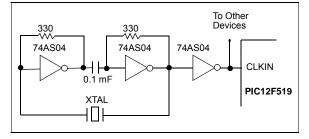

Figure 8-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The  $330\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 8-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

# 8.2.4 EXTERNAL RC OSCILLATOR

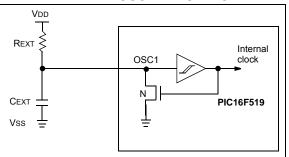

For timing insensitive applications, the RC circuit option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-5 shows how the R/C combination is connected to the PIC12F519 device. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. It is recommended keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), it is recommended using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance. See Figure 11-1 and Figure 11-2.

## FIGURE 8-5:

#### EXTERNAL RC OSCILLATOR MODE

### 8.2.5 INTERNAL 4/8 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4/8 MHz (nominal) system clock at VDD = 3.5V and 25°C, (see **Section 11.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always non-code protected, regardless of the code-protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the

## TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                    | STATUS Addr: 03h |

|------------------------------------|------------------|

| Power-on Reset                     | 0-01 1xxx        |

| MCLR Reset during normal operation | 0-0u uuuu        |

| MCLR Reset during Sleep            | 0-01 Ouuu        |

| WDT Reset during Sleep             | 0-00 Ouuu        |

| WDT Reset normal operation         | 0-00 uuuu        |

| Wake-up from Sleep on pin change   | 1-01 Ouuu        |

**Legend:** u = unchanged, x = unknown

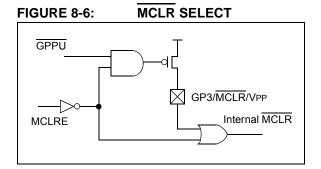

# 8.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 8-6.

# 8.4 Power-on Reset (POR)

The PIC12F519 device incorporates an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as GP3, in which case, an internal weak pull-up resistor is implemented using a transistor (refer to Table 11-4 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See **Section 11.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 8-7.

The Power-on Reset circuit and the Device Reset Timer (see **Section 8.5 "Device Reset Timer (DRT)**") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms or 1 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where MCLR is held low is shown in Figure 8-8. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of Reset TDRT after MCLR goes high.

In Figure 8-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3). The VDD is stable before the Start-up timer times out and there is no problem in getting a proper Reset. However, Figure 8-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-9).

| Note: | When the devices start normal operation (exit the Reset condition), device operat- |  |  |  |

|-------|------------------------------------------------------------------------------------|--|--|--|

|       | ing parameters (voltage, frequency, tem-                                           |  |  |  |

|       | perature, etc.) must be met to ensure                                              |  |  |  |

|       | operation. If these conditions are not met,                                        |  |  |  |

|       | the device must be held in Reset until the                                         |  |  |  |

|       | operating conditions are met.                                                      |  |  |  |

For additional information, refer to Application Note AN522, "*Power-Up Considerations*" (DS00522)

## 8.9 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program and data memory can be read out for verification purposes.

The first 64 locations and the last location (OSCCAL) can be read, regardless of the setting of the program memory's code protection bit. If the code protect bit specific to the FLASH data memory is programmed, then none of the contents of this memory region can be verified externally.

# 8.10 ID Locations

Four memory locations are designated as ID locations where users can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations. The upper bits should be programmed as 0s.

# 8.11 In-Circuit Serial Programming™

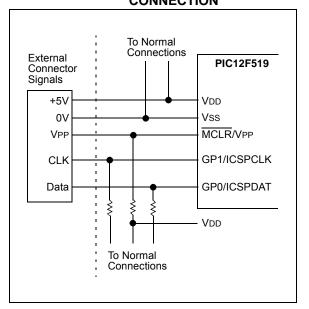

The PIC12F519 device can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows users to manufacture boards with unprogrammed PIC12F519 device and then program the PIC12F519 device just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The PIC12F519 device is placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the  $\overline{MCLR}$  (VPP) pin from VIL to VIHH (see programming specification). The GP1 pin becomes the programming clock, and the GP0 pin becomes the programming data. Both GP1 and GP0 pins are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the *"PIC12F519 Memory Programming Specification,"* (DS41316).

A typical In-Circuit Serial Programming connection is shown in Figure 8-12.

#### FIGURE 8-12: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                   |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is'0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is cleared.                                |

| ANDLW            | AND literal with W                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                             |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                                                |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |  |  |  |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is '0',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                     |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                             |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                            |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                       |  |  |

| Status Affected: | None                                                                                                                                                                                          |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.                                                                                                                      |  |  |

|                  | If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |

# PIC12F519

Status Affected:

Description:

Ζ

register.

The contents of the W register are XOR'ed with the eight-bit literal 'k'.

The result is placed in the W

| TRIS             | Load TRIS Register                          | XORWF            | Exclusive OR W with f                                                                                       |  |

|------------------|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] TRIS f                     | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                  |  |

| Operands:        | f = 6                                       | Operands:        | $0 \le f \le 31$                                                                                            |  |

| Operation:       | (W) $\rightarrow$ TRIS register f           | -                | d ∈ [0,1]                                                                                                   |  |

| Status Affected: | None                                        | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                          |  |

| Description:     | TRIS register 'f' (f = 6 or 7) is           | Status Affected: | Z                                                                                                           |  |

|                  | loaded with the contents of the W register. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W |  |

| XORLW            | Exclusive OR literal with W                 |                  | register. If 'd' is '1', the result is stored back in register 'f'.                                         |  |

| Syntax:          | [ <i>label</i> ] XORLW k                    |                  | Ű                                                                                                           |  |

| Operands:        | $0 \le k \le 255$                           |                  |                                                                                                             |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$               |                  |                                                                                                             |  |

# 10.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 10.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 10.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 10.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

# 11.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                         | 40°C to +125°C                     |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                                     | 0 to +6.5V                         |

| Voltage on MCLR with respect to Vss                                                                                    | 0 to +13.5V                        |

| Voltage on all other pins with respect to Vss                                                                          | 0.3V to (VDD + 0.3V)               |

| Total power dissipation <sup>(1)</sup>                                                                                 | 700 mW                             |

| Max. current out of Vss pin                                                                                            | 200 mA                             |

| Max. current into Vod pin                                                                                              | 150 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                           | ±20 mA                             |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                         | ±20 mA                             |

| Max. output current sunk by any I/O pin                                                                                | 25 mA                              |

| Max. output current sourced by any I/O pin                                                                             | 25 mA                              |

| Max. output current sourced by I/O port                                                                                | 75 mA                              |

| Max. output current sunk by I/O port                                                                                   | 75 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$ | VOH) x IOH} + $\Sigma$ (VOL x IOL) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

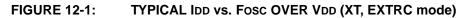

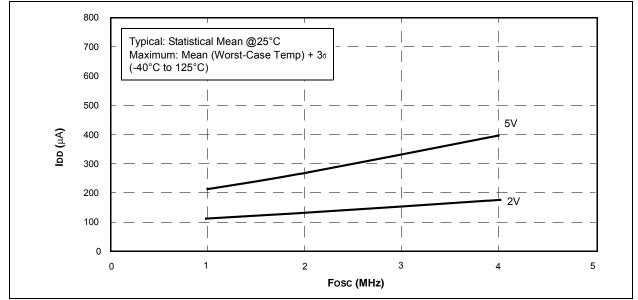

# 12.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

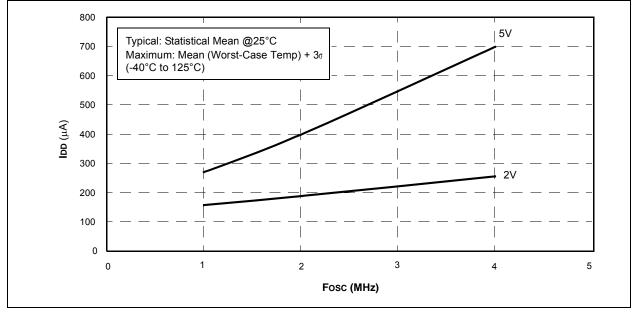

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

# **13.0 PACKAGING INFORMATION**

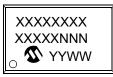

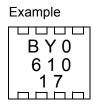

# 13.1 Package Marking Information

# 8-Lead PDIP

8-Lead SOIC (3.90 mm)

8-Lead MSOP

8-Lead 2x3 DFN\*

Example

# Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                          | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | In the event the full Microchip part number cannot be marked on one line, it be carried over to the next line, thus limiting the number of availa characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

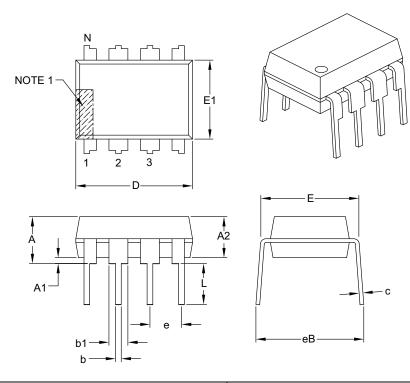

# 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          | INCHES |      |  |

|----------------------------|------------------|----------|--------|------|--|

| Dimensio                   | Dimension Limits |          | NOM    | MAX  |  |

| Number of Pins             | 8                |          |        |      |  |

| Pitch                      | е                | .100 BSC |        |      |  |

| Top to Seating Plane       | Α                | -        | -      | .210 |  |

| Molded Package Thickness   | A2               | .115     | .130   | .195 |  |

| Base to Seating Plane      | A1               | .015     | -      | _    |  |

| Shoulder to Shoulder Width | Е                | .290     | .310   | .325 |  |

| Molded Package Width       | E1               | .240     | .250   | .280 |  |

| Overall Length             | D                | .348     | .365   | .400 |  |

| Tip to Seating Plane       | L                | .115     | .130   | .150 |  |

| Lead Thickness             | С                | .008     | .010   | .015 |  |

| Upper Lead Width           | b1               | .040     | .060   | .070 |  |

| Lower Lead Width           | b                | .014     | .018   | .022 |  |

| Overall Row Spacing §      | eB               | _        | -      | .430 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

For the most current package drawings, please see the Microchip Packaging Specification located at

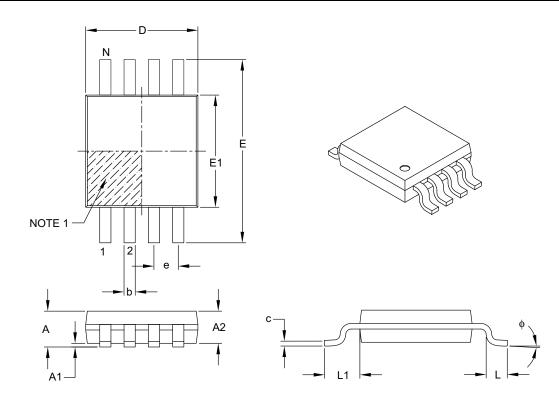

## 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

http://www.microchip.com/packaging

|                          | MILLIMETERS      |                |      |      |

|--------------------------|------------------|----------------|------|------|

| Dimens                   | Dimension Limits |                | NOM  | MAX  |

| Number of Pins           | Ν                | 8              |      |      |

| Pitch                    | е                | 0.65 BSC       |      |      |

| Overall Height           | Α                | 1.10           |      |      |

| Molded Package Thickness | A2               | 0.75           | 0.85 | 0.95 |

| Standoff                 | A1               | 0.00           | -    | 0.15 |

| Overall Width            | E                | 4.90 BSC       |      |      |

| Molded Package Width     | E1               | 3.00 BSC       |      |      |

| Overall Length           | D                | 3.00 BSC       |      |      |

| Foot Length              | L                | 0.40 0.60 0.80 |      |      |

| Footprint                | L1               | 0.95 REF       |      |      |

| Foot Angle               | ф                | 0° – 8°        |      | 8°   |

| Lead Thickness           | С                | 0.08 – 0.23    |      |      |

| Lead Width               | b                | 0.22 – 0.40    |      |      |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

# APPENDIX A: REVISION HISTORY

#### Revision A (May 2007)

Original release of this document.

#### **Revision B (September 2008)**

Added DC and AC Characteristics graphs; Updated Electrical Characteristics section; Updated Package Drawings and made general edits.

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 **China - Shanghai** Tel: 86-21-5407-5533

Fax: 86-21-5407-5066 China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

# ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/02/08