Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 41 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f519-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

NOTES:

## 2.0 PIC12F519 DEVICE VARIETIES

When placing orders, please use the PIC12F519 Product Identification System at the back of this data sheet to specify the correct part number. A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section.

#### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

NOTES:

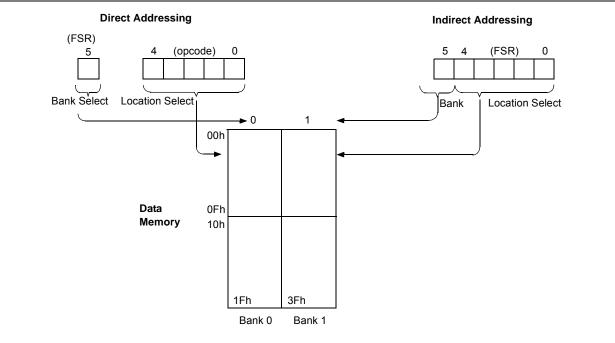

## 4.8 Indirect Data Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

The FSR is an 8-bit wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

FSR<5> is used to select between banks (0 = Bank 0, 1 = Bank 1).

FSR<7:6> are unimplemented and read as '11'.

#### EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTESC | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4 | <pre>;initialize pointer ;to RAM ;clear INDF ;register ;inc pointer ;all done?</pre> |

|----------|-----------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------|

|          | GOTO                                    | NEXT                                  | ;NO, clear next                                                                      |

| CONTINUE |                                         |                                       |                                                                                      |

|          | :                                       |                                       | ;YES, continue                                                                       |

|          | :                                       |                                       |                                                                                      |

|          |                                         |                                       |                                                                                      |

#### FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

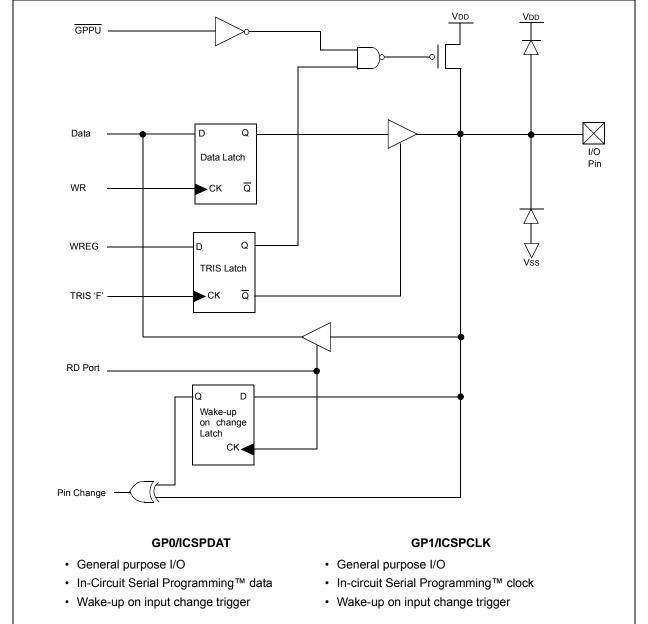

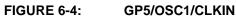

### 6.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 6-1. All port pins, except GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRISGPIO must be cleared (= 0). For use as an input, the corresponding TRISGPIO bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

#### 7.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see **Section 8.6 "Watch-dog Timer (WDT)"**). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |  |  |

|-------|-----------------------------------------|--|--|

|       | Timer0 module or the WDT, but not both. |  |  |

|       | Thus, a prescaler assignment for the    |  |  |

|       | Timer0 module means that there is no    |  |  |

|       | prescaler for the WDT and vice versa.   |  |  |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

#### 7.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

## EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| CLRWDT |             | ;Clear WDT                |

|--------|-------------|---------------------------|

| CLRF   | TMR0        | ;Clear TMR0 and Prescaler |

| MOVLW  | b'00xx1111' |                           |

| OPTION |             |                           |

|        |             |                           |

| CLRWDT |             | ;PS<2:0> are 000 or 001   |

| MOVLW  | b'00xx1xxx' | ;Set Postscaler to        |

| OPTION |             | ;desired WDT rate         |

|        |             |                           |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 7-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT            | ;Clear WDT and      |

|-------------------|---------------------|

|                   | ;prescaler          |

| MOVLW b'xxxx0xxx' | ;Select TMR0, new   |

|                   | ;prescale value and |

|                   | ;clock source       |

| OPTION            |                     |

| 1                 |                     |

#### 8.9 Program Verification/Code Protection

If the code protection bits have not been programmed, the on-chip program and data memory can be read out for verification purposes.

The first 64 locations and the last location (OSCCAL) can be read, regardless of the setting of the program memory's code protection bit. If the code protect bit specific to the FLASH data memory is programmed, then none of the contents of this memory region can be verified externally.

#### 8.10 ID Locations

Four memory locations are designated as ID locations where users can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations. The upper bits should be programmed as 0s.

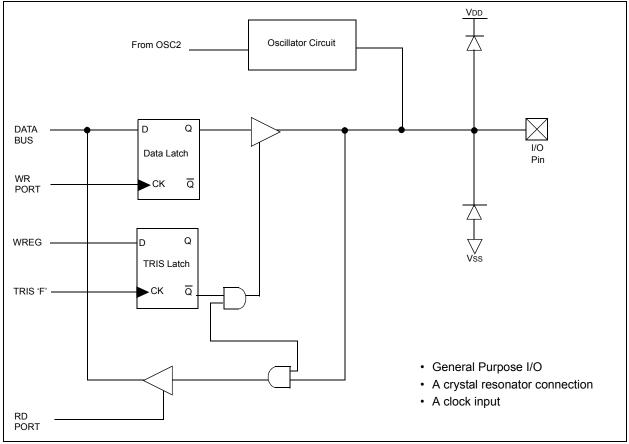

#### 8.11 In-Circuit Serial Programming™

The PIC12F519 device can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows users to manufacture boards with unprogrammed PIC12F519 device and then program the PIC12F519 device just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The PIC12F519 device is placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the  $\overline{MCLR}$  (VPP) pin from VIL to VIHH (see programming specification). The GP1 pin becomes the programming clock, and the GP0 pin becomes the programming data. Both GP1 and GP0 pins are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the *"PIC12F519 Memory Programming Specification,"* (DS41316).

A typical In-Circuit Serial Programming connection is shown in Figure 8-12.

#### FIGURE 8-12: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 9.0 INSTRUCTION SET SUMMARY

The PIC12F519 instruction set is highly orthogonal and is comprised of three basic categories.

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

Each PIC12F519 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 9-1, while the various opcode fields are summarized in Table 9-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

#### TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                                |

| W             | Working register (accumulator)                                                                                                                                                      |

| b             | Bit address within an 8-bit file register                                                                                                                                           |

| k             | Literal field, constant data or label                                                                                                                                               |

| x             | Don't care location (= $0$ or $1$ )<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                          |

| TOS           | Top-of-Stack                                                                                                                                                                        |

| PC            | Program Counter                                                                                                                                                                     |

| WDT           | Watchdog Timer counter                                                                                                                                                              |

| TO            | Time-out bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                      |

| dest          | Destination, either the W register or the specified register file location                                                                                                          |

| []            | Options                                                                                                                                                                             |

| ( )           | Contents                                                                                                                                                                            |

| $\rightarrow$ | Assigned to                                                                                                                                                                         |

| < >           | Register bit field                                                                                                                                                                  |

| E             | In the set of                                                                                                                                                                       |

| italics       | User defined term (font is courier)                                                                                                                                                 |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file                                                                    | e register | operatio | ons                  |     |

|---------------------------------------------------------------------------------------|------------|----------|----------------------|-----|

| 11                                                                                    | 65         | 4        |                      | 0   |

| OPCODE                                                                                | d          | f        | (FILE #)             |     |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address |            |          |                      |     |

| Bit-oriented file                                                                     | egister o  | peration | IS                   |     |

| 11                                                                                    | 87         | 54       |                      | 0   |

| OPCODE                                                                                | b (B       | IT #)    | f (FILE #)           |     |

| f = 5-bit file<br>Literal and contr                                                   | 0          |          | серt Goтo)           |     |

| 11                                                                                    | 8          | 7        |                      | 0   |

| OPCODE                                                                                |            |          | k (literal)          |     |

| k = 8-bit immediate value                                                             |            |          |                      |     |

| Literal and contr                                                                     | ol operati | ons – G  | ото i <b>nstruct</b> | ion |

| 11                                                                                    | 9          | 8        |                      | 0   |

| OPCODE k (literal)                                                                    |            |          |                      |     |

| k = 9-bit im                                                                          | mediate va | alue     |                      |     |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                   |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is'0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is cleared.                                |

| ANDLW            | AND literal with W                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                             |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                                                |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |  |  |  |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is '0',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                            |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.                                                                                                                      |

|                  | If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |

Status Affected:

Description:

Ζ

register.

The contents of the W register are XOR'ed with the eight-bit literal 'k'.

The result is placed in the W

| TRIS                                        | Load TRIS Register                | XORWF            | Exclusive OR W with f                                                                                       |  |

|---------------------------------------------|-----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                     | [ <i>label</i> ] TRIS f           | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                  |  |

| Operands:                                   | f = 6                             | Operands:        | $0 \le f \le 31$                                                                                            |  |

| Operation:                                  | (W) $\rightarrow$ TRIS register f | -                | d ∈ [0,1]                                                                                                   |  |

| Status Affected:                            | None                              | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                          |  |

| Description:                                | TRIS register 'f' (f = 6 or 7) is | Status Affected: | Z                                                                                                           |  |

| loaded with the contents of the W register. |                                   | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W |  |

| XORLW                                       | XORLW Exclusive OR literal with W |                  | register. If 'd' is '1', the result is stored back in register 'f'.                                         |  |

| Syntax:                                     | [ <i>label</i> ] XORLW k          |                  | Ű                                                                                                           |  |

| Operands:                                   | $0 \le k \le 255$                 |                  |                                                                                                             |  |

| Operation:                                  | (W) .XOR. $k \rightarrow (W)$     |                  |                                                                                                             |  |

## 11.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                         | 40°C to +125°C                     |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                                     | 0 to +6.5V                         |

| Voltage on MCLR with respect to Vss                                                                                    | 0 to +13.5V                        |

| Voltage on all other pins with respect to Vss                                                                          | 0.3V to (VDD + 0.3V)               |

| Total power dissipation <sup>(1)</sup>                                                                                 | 700 mW                             |

| Max. current out of Vss pin                                                                                            | 200 mA                             |

| Max. current into Vod pin                                                                                              | 150 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                           | ±20 mA                             |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                         | ±20 mA                             |

| Max. output current sunk by any I/O pin                                                                                | 25 mA                              |

| Max. output current sourced by any I/O pin                                                                             | 25 mA                              |

| Max. output current sourced by I/O port                                                                                | 75 mA                              |

| Max. output current sunk by I/O port                                                                                   | 75 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$ | VOH) x IOH} + $\Sigma$ (VOL x IOL) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

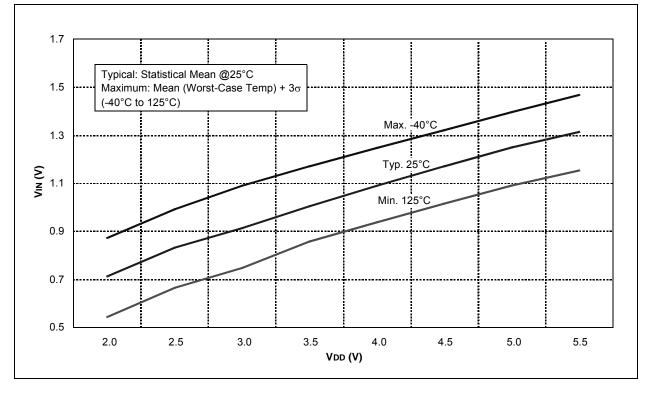

#### **TABLE 11-3:** DC CHARACTERISTICS: PIC12F519 (Industrial, Extended)

| DC CHARACTERISTICS |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |      |          |       |                                                                          |

|--------------------|------|------------------------------------------------------|--------------------|------|----------|-------|--------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                       | Min.               | Typ† | Max.     | Units | Conditions                                                               |

|                    | VIL  | Input Low Voltage                                    |                    | •    |          |       |                                                                          |

|                    |      | I/O ports                                            |                    |      |          |       |                                                                          |

| D030               |      | with TTL buffer                                      | Vss                | —    | 0.8      | V     | For all $4.5 \le VDD \le 5.5V$                                           |

| D030A              |      |                                                      | Vss                | —    | 0.15 VDD | V     | Otherwise                                                                |

| D031               |      | with Schmitt Trigger buffer                          | Vss                | —    | 0.15 VDD | V     |                                                                          |

| D032               |      | MCLR, TOCKI                                          | Vss                | —    | 0.15 VDD | V     |                                                                          |

| D033               |      | OSC1 (EXTRC mode)                                    | Vss                | _    | 0.15 VDD | V     | (Note 1)                                                                 |

| D033A              |      | OSC1 (XT and LP modes)                               | Vss                | _    | 0.3      | V     |                                                                          |

|                    | Vih  | Input High Voltage                                   |                    |      |          |       | 1                                                                        |

|                    |      | I/O ports                                            |                    | —    |          |       |                                                                          |

| D040               |      | with TTL buffer                                      | 2.0                | _    | Vdd      | V     | $4.5 \leq V \text{DD} \leq 5.5 \text{V}$                                 |

| D040A              |      |                                                      | 0.25 VDD<br>+ 0.8V | -    | Vdd      | V     | Otherwise                                                                |

| D041               |      | with Schmitt Trigger buffer                          | 0.85 VDD           | —    | Vdd      | V     | For entire VDD range                                                     |

| D042               |      | MCLR, TOCKI                                          | 0.85 VDD           | —    | Vdd      | V     |                                                                          |

| D042A              |      | OSC1 (EXTRC mode)                                    | 0.85 VDD           | —    | Vdd      | V     | (Note 1)                                                                 |

| D043               |      | OSC1 (XT and LP modes)                               | 1.6                | —    | Vdd      | V     |                                                                          |

| D070               | IPUR | I/O PORT weak pull-up current <sup>(5)</sup>         | 50                 | 250  | 400      | μA    | VDD = 5V, VPIN = VSS                                                     |

|                    | lı∟  | Input Leakage Current <sup>(2), (3)</sup>            |                    |      |          |       |                                                                          |

| D060               |      | I/O ports                                            | —                  | -    | ±1       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}, \ \text{Pin at high-impedance}$ |

| D061               |      | GP3/MCLR <sup>(4)</sup>                              | —                  | ±0.7 | ±5       | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                 |

| D063               |      | OSC1                                                 | —                  | —    | ±5       | μA    | $Vss \leq V\text{PIN} \leq V\text{DD},  XT$ and LP osc configuration     |

|                    |      | Output Low Voltage                                   |                    |      |          |       |                                                                          |

| D080               |      | I/O ports                                            | —                  | -    | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V, -40°C to +85°C                                 |

| D080A              |      |                                                      | —                  | —    | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V, -40°C to +125°C                                |

|                    |      | Output High Voltage                                  |                    |      |          |       |                                                                          |

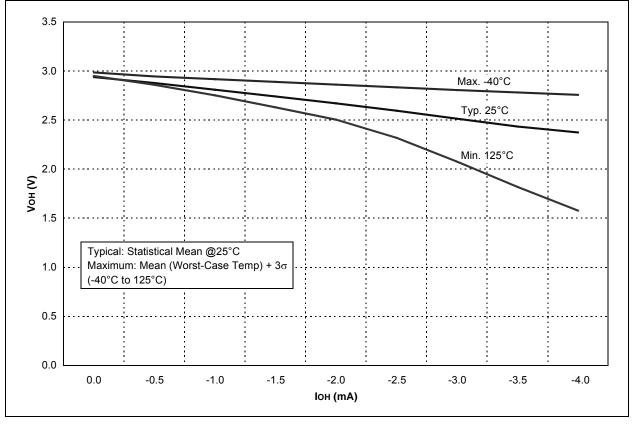

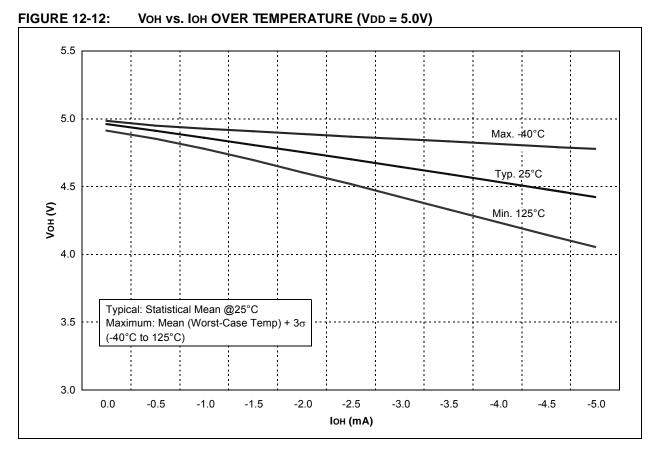

| D090               |      | I/O ports <sup>(3)</sup>                             | VDD - 0.7          | -    | —        | V     | IOH = -3.0 mA, VDD = 4.5V, -40°C to +85°C                                |

| D090A              |      |                                                      | VDD - 0.7          | —    | —        | V     | IOH = -2.5 mA, VDD = 4.5V, $-40^{\circ}$ C to $+125^{\circ}$ C           |

|                    |      | Capacitive Loading Specs on Output                   | t Pins             |      |          |       |                                                                          |

| D101               |      | All I/O pins                                         |                    | _    | 50       | pF    |                                                                          |

|                    |      | Flash Data Memory                                    |                    |      |          |       |                                                                          |

| D120               | ED   | Byte endurance                                       | 100K               | 1M   | —        | E/W   | $-40^\circ C \le T_A \le +85^\circ C$                                    |

| D120A              | ED   | Byte endurance                                       | 10K                | 100K | —        | E/W   | $+85^{\circ}C \leq T_A \leq +125^{\circ}C$                               |

| D121               | Vdrw | VDD for read/write                                   | VMIN               | _    | 5.5      | V     |                                                                          |

t

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12F519 be driven Note 1:

2: ing conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

This specification applies to GP3/MCLR configured as GP3 with internal pull-up disabled. 4:

This specification applies to all weak pull-up devices, including the weak pull-up found on GP3/MCLR. The current value listed will be the 5: same whether or not the pin is configured as GP3 with pull-up enabled or MCLR.

| VDD (Volts) | Temperature<br>(°C) | Min. | Тур. | Max. | Units |  |

|-------------|---------------------|------|------|------|-------|--|

| GP0/GP1     |                     |      |      |      |       |  |

| 2.0         | -40                 | 73K  | 105K | 186K | Ω     |  |

|             | 25                  | 73K  | 113K | 187K | Ω     |  |

|             | 85                  | 82K  | 123K | 190K | Ω     |  |

|             | 125                 | 86K  | 132K | 190K | Ω     |  |

| 5.5         | -40                 | 15K  | 21K  | 33K  | Ω     |  |

|             | 25                  | 15K  | 22K  | 34K  | Ω     |  |

|             | 85                  | 19K  | 26K  | 35K  | Ω     |  |

|             | 125                 | 23K  | 29K  | 35K  | Ω     |  |

| GP3         |                     |      |      |      |       |  |

| 2.0         | -40                 | 63K  | 81K  | 96K  | Ω     |  |

|             | 25                  | 77K  | 93K  | 116K | Ω     |  |

|             | 85                  | 82K  | 96K  | 116K | Ω     |  |

|             | 125                 | 86K  | 100K | 119K | Ω     |  |

| 5.5         | -40                 | 16K  | 20K  | 22K  | Ω     |  |

|             | 25                  | 16K  | 21K  | 23K  | Ω     |  |

|             | 85                  | 24K  | 25K  | 28K  | Ω     |  |

|             | 125                 | 26K  | 27K  | 29K  | Ω     |  |

#### TABLE 11-4: PULL-UP RESISTOR RANGES

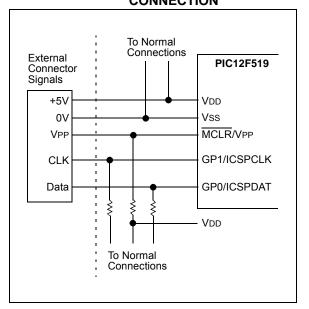

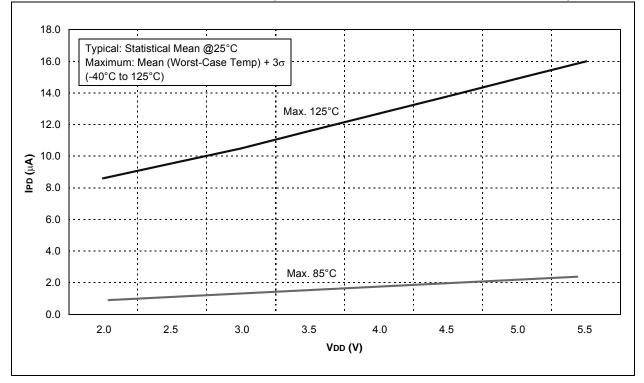

FIGURE 12-4: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

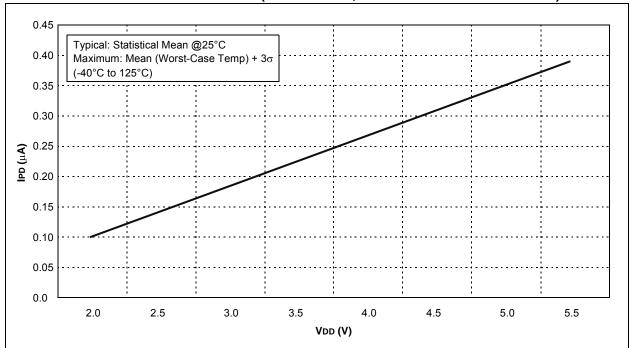

FIGURE 12-5: MAXIMUM IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

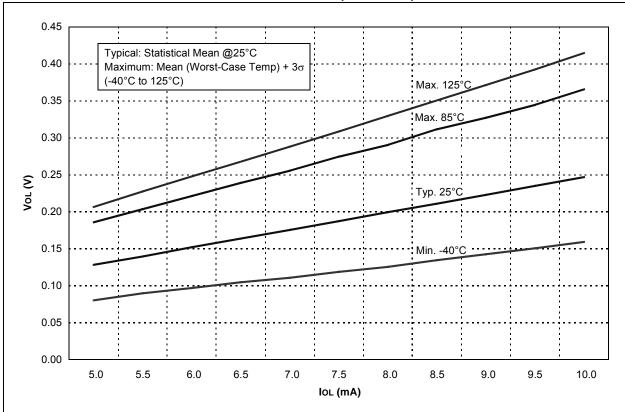

#### FIGURE 12-10: Vol vs. IoL OVER TEMPERATURE (VDD = 5.0V)

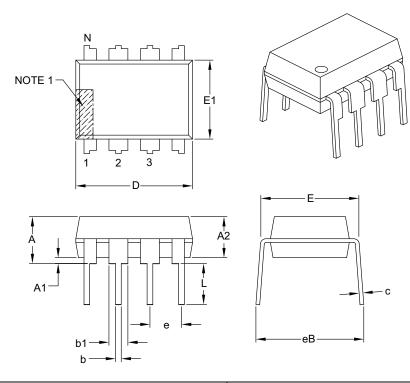

### 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |      |  |

|----------------------------|----------|------|----------|------|--|

| Dimensio                   | n Limits | MIN  | NOM      | MAX  |  |

| Number of Pins             | Ν        |      | 8        |      |  |

| Pitch                      | е        |      | .100 BSC |      |  |

| Top to Seating Plane       | Α        | -    | -        | .210 |  |

| Molded Package Thickness   | A2       | .115 | .130     | .195 |  |

| Base to Seating Plane      | A1       | .015 | -        | -    |  |

| Shoulder to Shoulder Width | Е        | .290 | .310     | .325 |  |

| Molded Package Width       | E1       | .240 | .250     | .280 |  |

| Overall Length             | D        | .348 | .365     | .400 |  |

| Tip to Seating Plane       | L        | .115 | .130     | .150 |  |

| Lead Thickness             | С        | .008 | .010     | .015 |  |

| Upper Lead Width           | b1       | .040 | .060     | .070 |  |

| Lower Lead Width           | b        | .014 | .018     | .022 |  |

| Overall Row Spacing §      | eB       | _    | -        | .430 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | x <u>xx xxx</u>                                                                                                                    | Examples:                                                                                                                                                   |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature Package Pattern<br>Range                                                                                               | <ul> <li>a) PIC12F519-I/P = Industrial temp., PDIP package (Pb-free)</li> <li>b) PIC12F519T-I/SN = Tape and Reel, Industrial temp., SOIC package</li> </ul> |

| Device:               | PIC12F519<br>PIC12F519T (Tape and Reel)                                                                                            | <ul> <li>c) PIC12F519 - E/MS 303 = Extended temp.,<br/>MSOP package, QTP pattern #303</li> </ul>                                                            |

| Temperature<br>Range: | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                          |                                                                                                                                                             |

| Package:              | MC = 8L DFN 2x3 (DUAL Flatpack No-Leads)<br>MS = MSOP (Pb-free)<br>P = 300 mil PDIP (Pb-free)<br>SN = 3.90 mm SOIC, 8-LD (Pb-free) |                                                                                                                                                             |

| Pattern:              | Special Requirements                                                                                                               |                                                                                                                                                             |

| Note: Tape<br>MSC     | and Reel available for only the following packages: SOIC, DFN and PP.                                                              |                                                                                                                                                             |