Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 41 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                    |

| Supplier Device Package    | 8-MSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f519t-i-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0    | General Description                         | . 5 |

|--------|---------------------------------------------|-----|

| 2.0    | PIC12F519 Device Varieties                  | . 7 |

| 3.0    | Architectural Overview                      | 9   |

| 4.0    | Memory Organization                         | 13  |

| 5.0    | Flash Data Memory                           |     |

| 6.0    | I/O Port                                    | 23  |

| 7.0    | Timer0 Module and TMR0 Register             | 31  |

| 8.0    | Special Features Of The CPU                 | 37  |

| 9.0    | Instruction Set Summary                     | 49  |

| 10.0   | Instruction Set Summary                     | 57  |

| 11.0   | Electrical Characteristics                  | 61  |

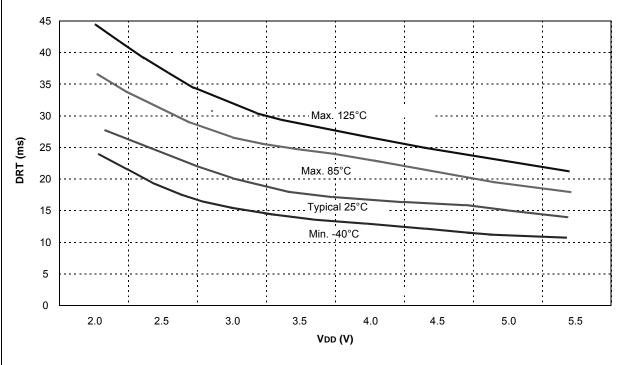

| 12.0   | DC and AC Characteristics Graphs and Charts | 73  |

| 13.0   | Packaging Information                       | 83  |

| Index  |                                             |     |

| The Mi | crochip Web Site                            | 91  |

| Custon | ner Change Notification Service             | 91  |

| Custon | ner Support                                 | 91  |

| Reade  | r Response                                  | 92  |

|        | t Identification System                     |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

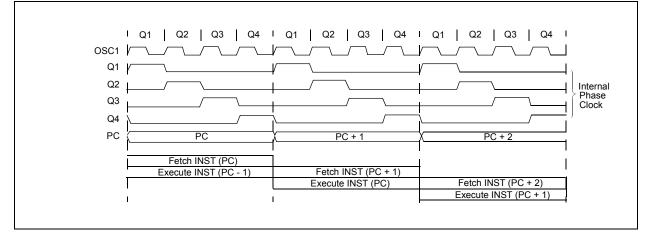

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

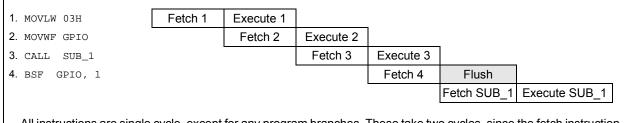

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

#### 4.3 STATUS register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see **Section 9.0 "Instruction Set Summary"**.

#### REGISTER 4-1: STATUS: STATUS REGISTER

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                       | R-1            | R-1                           | R/W-x                   | R/W-x            | R/W-x  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|-------------------------------|-------------------------|------------------|--------|

| GPWUF         |                                                                                                                                                                                                                                                                                                                                                                                                                                | PA0                                                         | TO             | PD                            | Z                       | DC               | С      |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |                |                               |                         |                  | bit 0  |

| <u> </u>      |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |                |                               |                         |                  |        |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | .,             | 11 11.2                       |                         | (0)              |        |

| R = Readable  |                                                                                                                                                                                                                                                                                                                                                                                                                                | W = Writable b                                              | It             | •                             | emented bit, read       |                  |        |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                            |                | '0' = Bit is c                | leared                  | x = Bit is unkno | own    |

| bit 7         | 1 = Reset du                                                                                                                                                                                                                                                                                                                                                                                                                   | ke-up From Sleep<br>e to wake-up fron<br>⁄er-up or other Re | n Sleep on pir | -                             |                         |                  |        |

| bit 6         | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                     | ted: Read as '0'                                            |                |                               |                         |                  |        |

| bit 5         | <b>PA0</b> : Program<br>1 = Page 1 (0<br>0 = Page 0 (2                                                                                                                                                                                                                                                                                                                                                                         |                                                             | bit            |                               |                         |                  |        |

| bit 4         | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                                                                                |                                                             |                |                               |                         |                  |        |

| bit 3         | <b>PD</b> : Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                                                                                                                                                                     |                                                             |                |                               |                         |                  |        |

| bit 2         | <b>Z</b> : Zero bit<br>1 = The result of an arithmetic or logic operation is zero<br>0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                                                                                                            |                                                             |                |                               |                         |                  |        |

| bit 1         | <ul> <li>DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)</li> <li>ADDWF:</li> <li>1 = A carry from the 4th low-order bit of the result occurred</li> <li>0 = A carry from the 4th low-order bit of the result did not occur</li> <li>SUBWF:</li> <li>1 = A borrow from the 4th low-order bit of the result did not occur</li> <li>0 = A borrow from the 4th low-order bit of the result did not occur</li> </ul> |                                                             |                |                               |                         |                  |        |

| bit 0         |                                                                                                                                                                                                                                                                                                                                                                                                                                | ow bit (for ADDWF<br>SU<br>ccurred 1 :                      |                | RRF, RLF instr<br>d not occur | uctions)<br>RRF or RLF: | o or MSb, respec | tively |

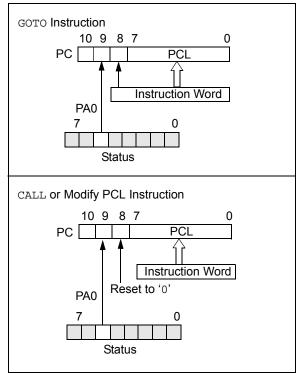

#### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits <8:0> of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STA-TUS register provides page information to bit 9 of the PC (Figure 4-3).

For a CALL instruction, or any instruction where the PCL is the destination, bits <7:0> of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-3).

Instructions where the PCL is the destination, or modify PCL instructions, include <code>MOVWF PCL</code>, <code>ADDWF PCL</code> and <code>BSF PCL</code>, <code>5</code>.

| Note: | Because PC<8> is cleared in the CALL       |

|-------|--------------------------------------------|

|       | instruction or any modify PCL instruction, |

|       | all subroutine calls or computed jumps are |

|       | limited to the first 256 locations of any  |

|       | program memory page (512 words long).      |

#### FIGURE 4-3: LOADING OF PC BRANCH INSTRUCTIONS

#### 4.6.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is pre-selected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

## 4.7 Stack

The PIC12F519 device has a two-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of Stack 1 into Stack 2 and then PUSH the current PC value, incremented by one, into Stack Level 1. If more than two sequential CALLs are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of Stack Level 1 into the PC and then copy Stack Level 2 contents into Stack Level 1. If more than two sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

| Note 1: | There are no Status bits to indicate stack overflows or stack underflow conditions. |

|---------|-------------------------------------------------------------------------------------|

| 2:      | There are no instruction mnemonics                                                  |

|         | called PUSH or POP. These are actions                                               |

and RETLW instructions.

that occur from the execution of the CALL

© 2008 Microchip Technology Inc.

#### REGISTER 6-1: GPIO: GPIO REGISTER

| U-0                                | U-0                        | R/W-x           | R/W-x              | R/W-x              | R/W-x            | R/W-x | R/W-x |

|------------------------------------|----------------------------|-----------------|--------------------|--------------------|------------------|-------|-------|

| _                                  | _                          | GP5             | GP4                | GP3                | GP2              | GP1   | GP0   |

| bit 7                              |                            |                 |                    |                    |                  |       | bit 0 |

|                                    |                            |                 |                    |                    |                  |       |       |

| Legend:                            |                            |                 |                    |                    |                  |       |       |

| R = Readable bit W = Writable bit  |                            | t               | U = Unimpleme      | ented bit, read as | '0'              |       |       |

| -n = Value at POR '1' = Bit is set |                            |                 | '0' = Bit is clear | red                | x = Bit is unkno | wn    |       |

|                                    |                            |                 |                    |                    |                  |       |       |

| bit 7-6                            | Unimplement                | ed: Read as '0' |                    |                    |                  |       |       |

| bit 5-0                            | <b>GP&lt;5:0&gt;</b> : GPI | O I/O Pin bits  |                    |                    |                  |       |       |

1 = GPIO pin is >VIH min.

0 = GPIO pin is <VIL max.

#### REGISTER 6-2: TRISGPIO: TRI-STATE GPIO REGISTER

| U-0   | U-0 | W-1       | W-1       | W-1       | W-1       | W-1       | W-1       |

|-------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| _     | _   | TRISGPI05 | TRISGPIO4 | TRISGPIO3 | TRISGPIO2 | TRISGPIO1 | TRISGPI00 |

| bit 7 |     |           |           | •         |           |           | bit 0     |

|       |     |           |           |           |           |           |           |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 TRISGPIO<5:0>: GPIO Tri-State Control bits

1 = GPIO pin configured as an input (tri-stated)

0 = GPIO pin configured as an output

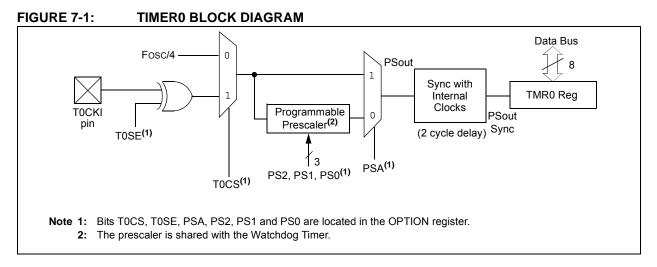

### 7.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.1 "Using Timer0 with an External Clock".

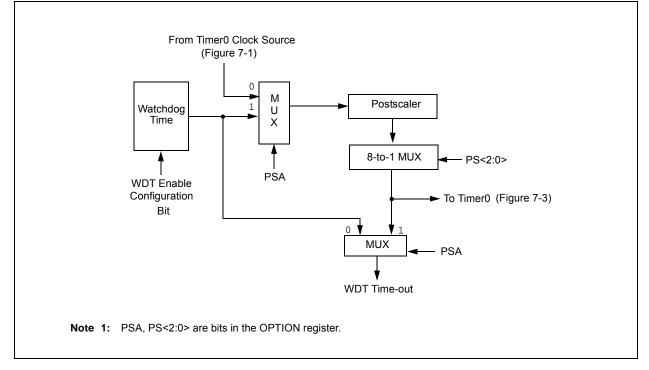

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 7.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 7-1.

The Timer0 contained in the CPU core follows the standard baseline definition.

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| Program<br>Counter)    | ( PC – 1         | Y PC             | Y PC + 1    | PC + 2      | PC + 3      | ( PC + 4    | ( PC + 5 )  | ( PC + 6 )                 |

|------------------------|------------------|------------------|-------------|-------------|-------------|-------------|-------------|----------------------------|

| nstruction<br>Fetch    | 1                | MOVWF TMR0       | MOVF TMR0,W |                            |

| Timer0                 | (то)             | Τ0 + 1 χ         | T0 + 2      |             | NTO X       | χ           | NT0 + 1     | NT0 + 2                    |

| nstruction<br>executed | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | Write TMR0  | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0<br>reads NT0 + 2 |

#### 7.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see **Section 8.6 "Watch-dog Timer (WDT)"**). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |

|-------|-----------------------------------------|

|       | Timer0 module or the WDT, but not both. |

|       | Thus, a prescaler assignment for the    |

|       | Timer0 module means that there is no    |

|       | prescaler for the WDT and vice versa.   |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

#### 7.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| CLRWDT |             | ;Clear WDT                |

|--------|-------------|---------------------------|

| CLRF   | TMR0        | ;Clear TMR0 and Prescaler |

| MOVLW  | b'00xx1111' |                           |

| OPTION |             |                           |

|        |             |                           |

| CLRWDT |             | ;PS<2:0> are 000 or 001   |

| MOVLW  | b'00xx1xxx' | ;Set Postscaler to        |

| OPTION |             | ;desired WDT rate         |

|        |             |                           |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 7-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT            | ;Clear WDT and      |

|-------------------|---------------------|

|                   | ;prescaler          |

| MOVLW b'xxxx0xxx' | ;Select TMR0, new   |

|                   | ;prescale value and |

|                   | ;clock source       |

| OPTION            |                     |

| 1                 |                     |

PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the       |

|-------|----------------------------------------------|

|       | pre-programmed internal calibration value    |

|       | for the internal oscillator. The calibration |

|       | value must be read prior to erasing the      |

|       | part so it can be reprogrammed correctly     |

|       | later.                                       |

For the PIC12F519 device, only bits <7:1> of OSCCAL are used for calibration. See Register 4-3 for more information.

| Note: | The bit 0 of the OSCCAL register is    | 3 |

|-------|----------------------------------------|---|

|       | unimplemented and should be written as | 3 |

|       | '0' when modifying OSCCAL fo           | r |

|       | compatibility with future devices.     |   |

#### 8.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Time-out Reset during normal operation

- WDT Time-out Reset during Sleep

- Wake-up from Sleep on pin change

Some registers are not reset in any way, and they are unknown on Power-on Reset (POR) and unchanged in any other Reset. Most other registers <u>are reset</u> to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They <u>are not affected by a WDT Reset</u> during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 8-3 for a full description of Reset states of all registers.

| Register | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |  |

|----------|---------|--------------------------|----------------------------------------------------|--|

| W        | _       | qqqq qqq0 <sup>(1)</sup> | qqqq qqq0 <sup>(1)</sup>                           |  |

| INDF     | 00h     | XXXX XXXX                | uuuu uuuu                                          |  |

| TMR0     | 01h     | xxxx xxxx                | uuuu uuuu                                          |  |

| PCL      | 02h     | 1111 1111                | 1111 1111                                          |  |

| STATUS   | 03h     | 0-01 1xxx                | q-0q quuu <b>(2), (3)</b>                          |  |

| FSR      | 04h     | 110x xxxx                | 11uu uuuu                                          |  |

| OSCCAL   | 05h     | 1111 111-                | uuuu uuu-                                          |  |

| PORTB    | 06h     | xx xxxx                  | uu uuuu                                            |  |

| OPTION   | —       | 1111 1111                | 1111 1111                                          |  |

| TRIS     | —       | 11 1111                  | 11 1111                                            |  |

| EECON    | 21h     | 0 x000                   | 0 q000                                             |  |

| EEDATA   | 25h     | XXXX XXXX                | սսսս սսսս                                          |  |

| EEADR    | 26h     | xx xxxx                  | uu uuuu                                            |  |

#### TABLE 8-3:RESET CONDITIONS FOR REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:1> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 8-4 for Reset value for specific conditions.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

#### FIGURE 8-11: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 8-6: SUMMARY OF REGISTER ASSOCIATED WITH THE WATCHDOG TIMER

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------|

| OPTION | GPWU  | GPPU  | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                 |

Legend: Shaded boxes = Not used by Watchdog Timer.

### 8.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and (GPWUF) bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) Reset.

# TABLE 8-7:TO/PD/(GPWUF) STATUSAFTER RESET

| GPWUF | то | PD | Reset Caused By                  |

|-------|----|----|----------------------------------|

| 0     | 0  | 0  | WDT wake-up from Sleep           |

| 0     | 0  | u  | WDT time-out (not from Sleep)    |

| 0     | 1  | 0  | MCLR wake-up from Sleep          |

| 0     | 1  | 1  | Power-up                         |

| 0     | u  | u  | MCLR not during Sleep            |

| 1     | 1  | 0  | Wake-up from Sleep on pin change |

**Legend:** u = unchanged

Note 1: The TO, PD and GPWUF bits maintain their status (u) until a Reset occurs. A low-pulse on the MCLR input does not change the TO, PD and GPWUF Status bits.

### 8.8 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

#### 8.8.1 SLEEP

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

| Note: | A Reset generated by a WDT time-out |

|-------|-------------------------------------|

|       | does not drive the MCLR pin low.    |

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the GP3/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

#### 8.8.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 5. An external Reset input on GP3/MCLR/VPP pin, when configured as MCLR.

- 6. A Watchdog Timer Time-out Reset (if WDT was enabled).

- 7. A change on input pin GP0, GP1 and GP3 when wake-up on change is enabled.

These events cause a device Reset. The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and GPWUF bits can be used to determine the cause of device Reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in Sleep at pins GP0, GP1 and GP3 (since the last file or bit operation on GPIO port).

Note: Caution: Right before entering Sleep, read the input pins. When in Sleep, wake up occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before re-entering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

| IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in register<br>'f'. |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |

| Operands:        | $0 \leq f \leq 31$                             |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                       |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' = 1 is useful as a<br>test of a file register, since status<br>flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                 |

| Operands:        | $0 \le k \le 255$                                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                                      |

| Status Affected: | None                                                                                                     |

| Description:     | The eight-bit literal 'k' is loaded<br>into the W register. The "don't<br>cares" will assembled as '0's. |

| OPTION           | Load OPTION Register                                              |

|------------------|-------------------------------------------------------------------|

| Syntax:          | [label] Option                                                    |

| Operands:        | None                                                              |

| Operation:       | $(W) \rightarrow Option$                                          |

| Status Affected: | None                                                              |

| Description:     | The content of the W register is loaded into the OPTION register. |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| SLEEP            | Enter SLEEP Mode                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                      |

| Operands:        | None                                                                                                                                               |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \ prescaler; \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow PD \end{array}$          |

| Status Affected: | TO, PD, GPWUF                                                                                                                                      |

| Description:     | Time-out Status bit $(\overline{TO})$ is set. The Power-down Status bit $(\overline{PD})$ is cleared.                                              |

|                  | GPWUF is unaffected.                                                                                                                               |

|                  | The WDT and its prescaler are<br>cleared.                                                                                                          |

|                  | The processor is put into Sleep<br>mode with the oscillator stopped.<br>See Section 8.8 "Power-down<br>Mode (Sleep)" on Sleep for more<br>details. |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                             |

| Operation:       | See description below                                                                                                                                                                                                  |

| Status Affected: | С                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is stored back in reg-<br>ister 'f'. |

| SUBWF            | Subtract W from f                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                          |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract (two's complement<br>method) the W register from regis-<br>ter 'f'. If 'd' is '0', the result is stored<br>in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                            |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

|                  | C register 'f'                                                                                                                                                                                                        |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                         |

| Operation:       | (f<3:0>) → (dest<7:4>);<br>(f<7:4>) → (dest<3:0>)                                                                                                                  |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is placed in register 'f'. |

#### 10.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 10.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 and PIC24 families of microcontrollers and the dsPIC30 and dsPIC33 family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 10.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 10.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- · MPLAB IDE compatibility

#### 10.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### **11.3 AC Characteristics**

#### TABLE 11-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                               |        |        |     |                       |  |

|--------------------|-------|------------------------------------------------------|-----------------------------------------------|--------|--------|-----|-----------------------|--|

| Param<br>No.       | Sym.  | Characteristic                                       | Min. Typ <sup>(1)</sup> Max. Units Conditions |        |        |     |                       |  |

| 1A                 | Fosc  | External CLKIN Frequency <sup>(2)</sup>              | DC                                            | —      | 4      | MHz | XT Oscillator mode    |  |

|                    |       |                                                      | DC                                            | _      | 200    | kHz | LP Oscillator mode    |  |

|                    |       | Oscillator Frequency <sup>(2)</sup>                  | DC                                            | _      | 4      | MHz | EXTRC Oscillator mode |  |

|                    |       |                                                      | 0.1                                           | —      | 4      | MHz | XT Oscillator mode    |  |

|                    |       |                                                      | DC                                            | —      | 200    | kHz | LP Oscillator mode    |  |

| 1                  | Tosc  | External CLKIN Period <sup>(2)</sup>                 | 250                                           | —      | —      | ns  | XT Oscillator mode    |  |

|                    |       |                                                      | 5                                             | —      | —      | μS  | LP Oscillator mode    |  |

|                    |       | Oscillator Period <sup>(2)</sup>                     | 250                                           | —      | _      | ns  | EXTRC Oscillator mode |  |

|                    |       |                                                      | 250                                           | —      | 10,000 | ns  | XT Oscillator mode    |  |

|                    |       |                                                      | 5                                             | —      |        | μS  | LP Oscillator mode    |  |

| 2                  | Тсү   | Instruction Cycle Time                               | 200                                           | 4/Fosc | DC     | ns  |                       |  |

| 3                  | TosL, | Clock in (OSC1) Low or High                          | 50*                                           | —      | _      | ns  | XT Oscillator         |  |

|                    | TosH  | Time                                                 | 2*                                            | —      | —      | μS  | LP Oscillator         |  |

| 4                  | TosR, | Clock in (OSC1) Rise or Fall                         | —                                             | _      | 25*    | ns  | XT Oscillator         |  |

| TosF Time          |       | Time                                                 | —                                             | —      | 50*    | ns  | LP Oscillator         |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

\*

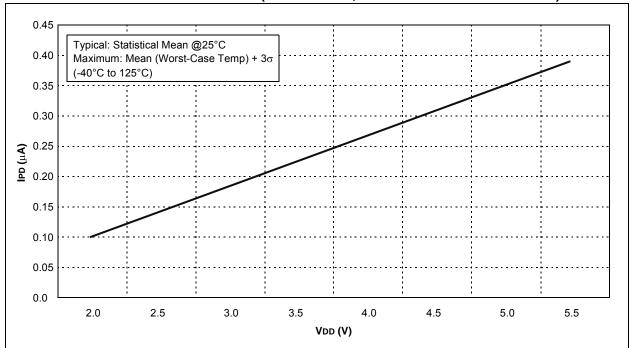

FIGURE 12-4: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

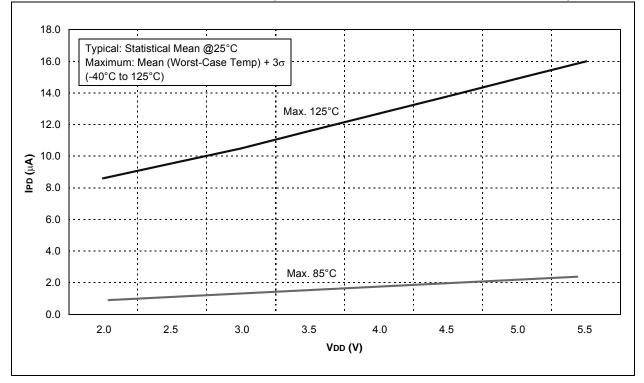

FIGURE 12-5: MAXIMUM IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

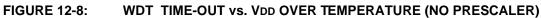

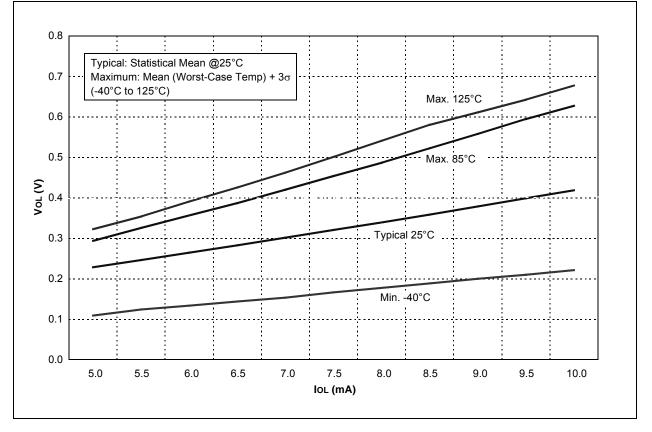

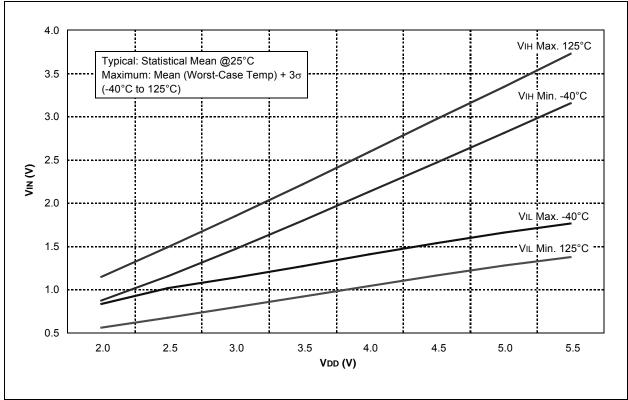

### FIGURE 12-14: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD

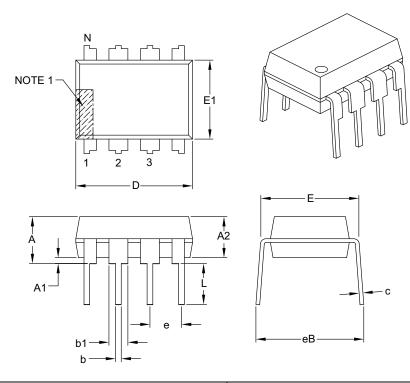

### 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |      |

|----------------------------|----------|------|----------|------|

| Dimensio                   | n Limits | MIN  | NOM      | MAX  |

| Number of Pins             | Ν        |      | 8        |      |

| Pitch                      | е        |      | .100 BSC |      |

| Top to Seating Plane       | Α        | -    | -        | .210 |

| Molded Package Thickness   | A2       | .115 | .130     | .195 |

| Base to Seating Plane      | A1       | .015 | -        | -    |

| Shoulder to Shoulder Width | Е        | .290 | .310     | .325 |

| Molded Package Width       | E1       | .240 | .250     | .280 |

| Overall Length             | D        | .348 | .365     | .400 |

| Tip to Seating Plane       | L        | .115 | .130     | .150 |

| Lead Thickness             | С        | .008 | .010     | .015 |

| Upper Lead Width           | b1       | .040 | .060     | .070 |

| Lower Lead Width           | b        | .014 | .018     | .022 |

| Overall Row Spacing §      | eB       | _    | -        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

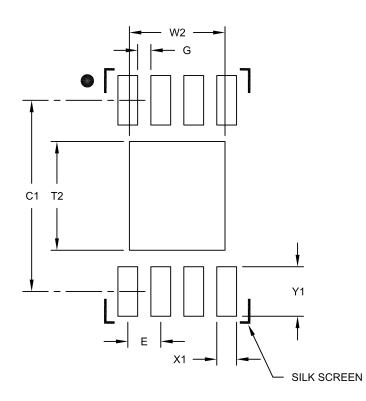

### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### **RECOMMENDED LAND PATTERN**

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | Е  | E 0.50 BSC  |      |      |

| Optional Center Pad Width  | W2 |             |      | 1.45 |

| Optional Center Pad Length | T2 |             |      | 1.75 |

| Contact Pad Spacing        | C1 |             | 2.90 |      |

| Contact Pad Width (X8)     | X1 |             |      | 0.30 |

| Contact Pad Length (X8)    | Y1 |             |      | 0.75 |

| Distance Between Pads      | G  | 0.20        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2123A

#### T Ti

| Timer0<br>Timer0 (TMR0) Module<br>TMR0 with External Clock<br>Timing Diagrams and Specifications<br>Timing Parameter Symbology and Load Conditions<br>TRIS Registers | 33<br>67<br>67 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| w                                                                                                                                                                    |                |

| Wake-up from Sleep                                                                                                                                                   | 47             |

| Watchdog Timer (WDT)                                                                                                                                                 | . 37, 45       |

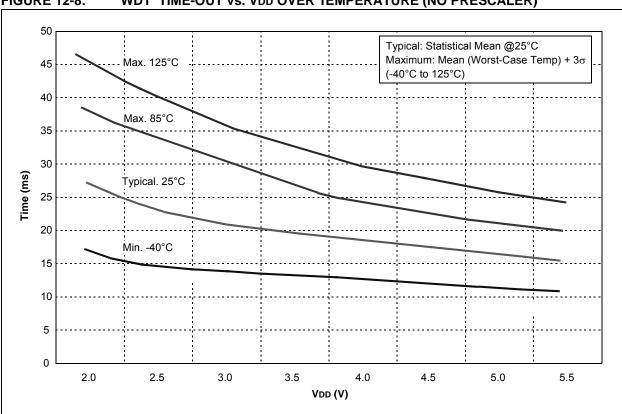

| Period                                                                                                                                                               | 45             |

| Programming Considerations                                                                                                                                           | 45             |

| WWW Address                                                                                                                                                          |                |

| WWW, On-Line Support                                                                                                                                                 | 3              |

| Z                                                                                                                                                                    |                |

| Zero bit                                                                                                                                                             | 9              |