Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                            |

|---------------------------------|----------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                   |

| Programmable Type               | In System Programmable                                                     |

| Delay Time tpd(1) Max           | 5 ns                                                                       |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                  |

| Number of Logic Elements/Blocks | 24                                                                         |

| Number of Macrocells            | 768                                                                        |

| Number of Gates                 | -                                                                          |

| Number of I/O                   | 304                                                                        |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                            |

| Mounting Type                   | Surface Mount                                                              |

| Package / Case                  | 484-BBGA                                                                   |

| Supplier Device Package         | 484-FPBGA (23x23)                                                          |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc5768vg-5f484c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

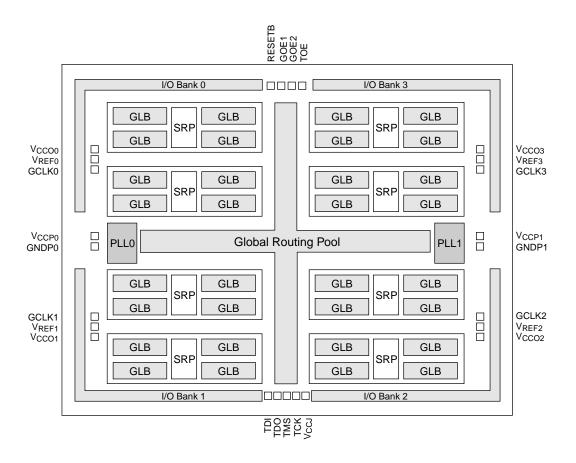

Figure 1. Functional Block Diagram

#### Overview

The ispMACH 5000VG devices consist of multiple SuperWIDE 68-input, 32-macrocell Generic Logic Blocks (GLBs) interconnected by a tiered routing system. Figure 1 shows the functional block diagram of the ispMACH 5000VG. Groups of four GLBs, referred to as segments, are interconnected via a Segment Routing Pool (SRP). Segments are interconnected via the Global Routing Pool (GRP.) Together the GLBs and the routing pools allow designers to create large designs in a single device without compromising performance.

Each GLB has 68 inputs coming from the SRP and contains 163 product terms. These product terms form groups of five product term clusters, which feed the PT sharing array or the macrocell directly. The ispMACH 5000VG allows up to 160 product terms to be connected to a single macrocell via the product term expanders and PT Sharing Array.

The macrocell is designed to provide flexible clocking and control functionality with the capability to select between global, product term and block-level resources. The outputs of the macrocells are fed back into the switch matrices and, if required, the sysIO cell.

All I/Os in the ispMACH 5000VG family are sysIOs, which are split into four banks. Each bank has a separate I/O power supply and reference voltage. The sysIO cells allow operation with a wide range of today's emerging interface standards. Within a bank, inputs can be set to a variety of standards, providing the reference voltage requirements of the chosen standards are compatible. Within a bank, the outputs can be set to differing standards, providing the I/O power supply voltage and the reference voltage requirements of the chosen standard are compatible. Support for this wide range of standards allows designers to achieve significantly higher board-level performance compared to the more traditional LVCMOS standards.

The ispMACH5000VG devices also contain sysCLOCK Phase Locked Loops (PLLs) that provide designers with increased clocking flexibility. The PLLs can be used to synthesize new clocks for use on-chip or elsewhere within the system. They can also be used to deskew clocks, again both at the chip and system levels. A variable delay line capability further improves this and allows designers to retard or advance the clock in order to tune set-up and clock-to-out times for optimal results. The ispMACH 5000VG Family Selection Guide (Table 1) details the key attributes and packages for the ispMACH 5000VG devices.

### ispMACH 5000VG Architecture

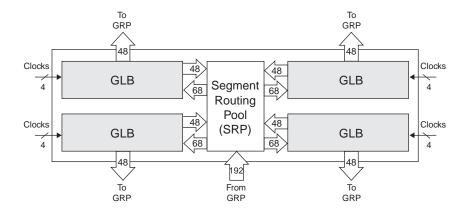

The ispMACH 5000VG Family of In-System Programmable High Density Logic Devices is based on segments containing four Generic Logic Blocks (GLBs) and a hierarchical routing pool (GRP) structure interconnecting the segments. A segment routing pool (SRP) connects each GLB in a segment allowing the maximum flexibility and speed.

Outputs from the GLBs drive the Segment Routing Pool (SRP) and the Global Routing Pool (GRP). Enhanced switching resources are provided to allow signals in the Segment Routing Pool to drive any or all the GLBs in the segment. Optimal switching is provided to allow all signals in the Global Routing Pool to be routed to any or all SRPs. This mechanism allows fast, efficient connections across the entire device.

#### Segment

Each segment contains four GLBs and a segment routing pool (SRP). Each GLB has 32 internal feedback outputs and 16 external feedback outputs, for a total of 48 outputs from each GLB feeding the SRP. The SRP contains up to 384 signals, 48 from each GLB and 192 from the GRP, with full routing capability. This routing scheme maximizes the flexibility and speed of the device without sacrificing the routing.

Figure 2. Segment

#### **Generic Logic Block**

Each GLB contains 32 macrocells and a fully populated, programmable AND-array with 160 logic product terms and three control product terms. The GLB has 68 inputs from the Segment Routing Pool, which are available in both true and complement form for every product term. The three control product terms are used for shared reset, clock and output enable functions. Figure 3 shows the structure of the GLB from the macrocell perspective. This is referred to as a macrocell slice. There are 32 macrocell slices per GLB.

#### **AND-Array**

The programmable AND-Array consists of 68 inputs and 163 output product terms. The 68 inputs from the SRP are used to form 136 lines in the AND-Array (true and complement of the inputs). Each line in the array can be connected to any of the 163 output product terms via a wired AND. Each of the 160 logic product terms feed the Dual-OR Array with the remaining three control product terms feeding the Shared PT Clock, Shared PT Reset and Shared PT OE. Every set of five product terms from the 160 logic product terms forms a product term cluster start-

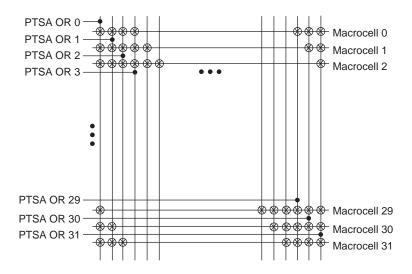

#### **Product Term Sharing Array**

The Product Term Sharing Array (PTSA) consists of 32 inputs from the Dual-OR Array (Expandable PTSA OR) and 32 outputs directly to the macrocells. Each output is the OR term of any combination of the seven Expandable PTSA OR terms connected to that output. Every Nth macrocell is connected to N-3, N-2, N-1, N, N+1, N+2 and N+3 PTSA OR terms via a programmable connection. This wraps around the logic, Macrocell 0 gets its logic from 29, 30, 31, 0, 1, 2, 3. The Expandable PTSA OR used in conjunction with the PTSA allows wide functions to be implemented easily and efficiently. Without using the Expandable PTSA OR capability, the greatest number of product terms that can be included in a single function with one pass of delay is 35. Figure 6 shows the graphical representation of the PTSA.

Figure 6. Product Term Sharing Array

#### Macrocell

The 32 registered macrocells in the GLB are driven by the 32 outputs from the PTSA or the PTSA bypass. Each macrocell contains a programmable XOR gate, a programmable register/latch flip-flop and the necessary clocks and control logic to allow combinatorial or registered operation.

The macrocells each have two outputs, which can be fed to the SRP, GRP and I/O cell. This dual or concurrent output capability from the macrocell gives efficient use of the hardware resources. One output can be a registered function for example, while the other output can be an unrelated combinatorial function. A direct register input from the I/O cell facilitates efficient use of the macrocell to construct high-speed input registers.

Macrocell registers can be clocked from one of several global or product term clocks available on the device. A global and product term clock enable is also provided, eliminating the need to gate the clock to the macrocell registers directly. Reset and preset for the macrocell register is provided from both global and product term signals. The macrocell register can be programmed to operate as a D-type register or a D-type latch. Figure 7 is a graphical representation of the ispMACH 5000VG macrocell.

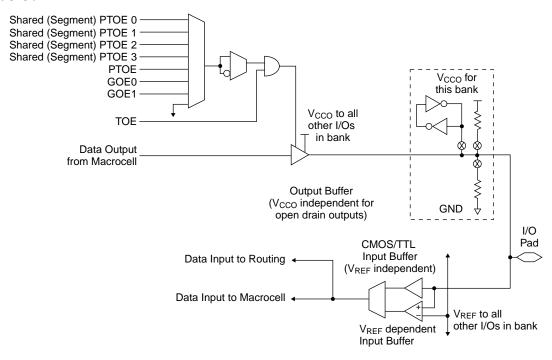

Figure 8. I/O Cell

#### sysIO Capability

The ispMACH 5000VG devices are divided into four sysIO banks, where each bank is capable of supporting 14 different I/O standards. Each sysIO bank has its own I/O supply voltage ( $V_{CCO}$ ) and reference voltage ( $V_{REF}$ ) resources allowing each bank complete independence from the others. Each I/O within a bank is individually configurable based on the  $V_{CCO}$  and  $V_{REF}$  settings. Table 2 lists the sysIO standards with the typical values for  $V_{CCO}$ ,  $V_{REF}$  and  $V_{TT}$ .

Table 2. ispMACH 5000VG Supported I/O Standards

| sysIO Standard                    | V <sub>cco</sub> | V <sub>REF</sub> | V <sub>TT</sub> |

|-----------------------------------|------------------|------------------|-----------------|

| LVTTL                             | 3.3V             | N/A              | N/A             |

| LVCMOS-3.3                        | 3.3V             | N/A              | N/A             |

| LVCMOS-2.5                        | 2.5V             | N/A              | N/A             |

| LVCMOS-1.8                        | 1.8V             | N/A              | N/A             |

| PCI 3.3                           | 3.3V             | N/A              | N/A             |

| PCI-X                             | 3.3V             | N/A              | N/A             |

| AGP-1X                            | 3.3V             | N/A              | N/A             |

| SSTL3, Class I & II               | 3.3V             | 1.5V             | 1.5V            |

| SSTL2, Class I & II               | 2.5V             | 1.25V            | 1.25V           |

| CTT 3.3                           | 3.3V             | 1.5V             | 1.5V            |

| CTT 2.5                           | 2.5V             | 1.25V            | 1.25V           |

| HSTL, Class I                     | 1.5V             | 0.75V            | 0.75V           |

| HSTL, Class III                   | 1.5V             | 0.9V             | 1.5V            |

| GTL+                              | N/A              | 1.0V             | 1.5V            |

| LVPECL, Differential <sup>1</sup> | N/A              | N/A              | N/A             |

| LVDS <sup>1</sup>                 | N/A              | N/A              | N/A             |

<sup>1.</sup> LVDS and LVPECL are only supported on the dedicated clock pins.

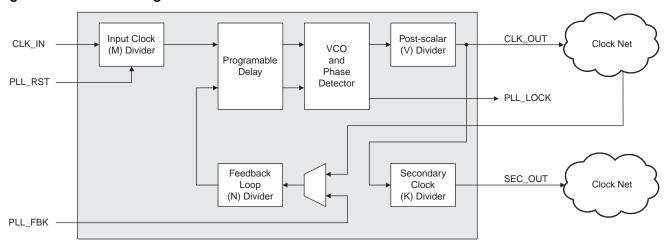

#### sysCLOCK PLL

The sysCLOCK PLL circuitry consists of Phase-Lock Loops (PLLs) and the various dividers, reset and feedback signals associated with the PLLs. This feature gives the user the ability to synthesize clock frequencies and generate multiple clock signals for routing within the device. Furthermore, it can generate clock signals that are deskewed either at the board level or the device level.

The ispMACH 5000VG devices provide two PLL circuits. PLL0 receives its clock inputs from GCLK 0 and provides outputs to CLK 0 (CLK 1 when using the secondary clock). PLL1 operates with signals from GCLK 3 and CLK 3 (CLK 2 when using the secondary clock). The PLL outputs (CLK\_OUT) are routed via a dedicated net to a dedicated pad. Further the buffers at these dedicated pads are regular I/O buffers that can select either the I/O macrocell or the CLK\_OUT (CLK\_OUT0/CLK\_OUT1) signal. The CLK\_OUT nets are not routed through the GRP. Additionally, there are two sets of signals used for external control. Each PLL has a set of PLL\_RST, PLL\_FBK and PLL\_LOCK signals. Figure 10 shows the ispMACH 5000VG PLL block diagram.

Figure 10. PLL Block Diagram

In order to facilitate the multiply and divide capabilities of the PLL, each PLL has dividers associated with it: M, N and K. The M divider is used to divide the clock signal, while the N divider is used to multiply the clock signal. The K divider is only used when a secondary clock output is needed. This divider divides the primary clock output and feeds to a separate global clock net. The V divider is used to provide lower frequency output clocks, while maintaining a stable, high frequency output from the PLL's VCO circuit.

The PLL also has a delay feature that allows the output clock to be advanced or delayed to improve set-up and clock-to-out times for better performance. This operates by inserting delay on the input or feedback lines in 0.5ns increments from 0 to 3.5ns. For more information on the PLL, please refer to Technical Note TN1003: *ispMACH 5000VG PLL Usage Guidelines*.

## **Power Management**

The ispMACH 5000VG devices provide unique power management controls. The devices have two power settings, high power and low power, on a per node basis. Low power consumption is approximately 50% of high power consumption with a timing delay adder (tLP) to the routing delay of the low power node. Each node can be configured as either high power or low power. However, care should be taken when sharing product terms between nodes with different power settings.

The ispMACH 5000VG devices also have a power-off feature for unused product terms. By default, any product term that is not used is configured as such. This allows the device to operate at minimal power consumption without affecting the timing of the design. For more information on power management, please refer to Technical Note TN1002: *Power Estimation in ispMACH 5000VG Devices*.

### **IEEE 1149.1-Compliant Boundary Scan Testability**

All ispMACH 5000VG devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port has its own supply voltage and can operate with LVCMOS3.3, 2.5 and 1.8V standards.

### sysIO Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispMACH 5000VG family of devices allows this by offering the user the ability to quickly configure the physical nature of the sysIO cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM<sup>TM</sup> System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

### **IEEE 1532-Compliant In-System Programming**

In-system programming of devices provides a number of significant benefits including rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispMACH 5000VG devices provide In-System Programming (ISP<sup>TM</sup>) capability through their Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains compliant to the IEEE 1532 standard. By using IEEE 1532 as the communication interface through which ISP is achieved, customers get the benefit of a standard, well-defined interface.

The ispMACH 5000VG devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispMACH 5000VG devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispMACH 5000VG devices during the testing of a circuit board.

## **Security Bit**

A programmable security bit is provided on the ispMACH 5000VG devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit prevents readback of the programmed pattern by a device programmer, securing proprietary design from competitors. The security bit also prevents programming and verification. The entire device must be erased in order to erase the security bit.

## **Hot Socketing**

The ispMACH 5000VG devices are well suited for those applications that require hot socketing capability. Hot socketing a device requires that the device, when powered down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of the powered-down device be minimal on active signals.

## **Density Migration**

The ispMACH 5000 family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

## **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                         | Parameter                                                                                                                                  | Condition                                      |                 | Min                      | Тур | Max                      | Units |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|--------------------------|-----|--------------------------|-------|

| I <sub>IL</sub> , I <sub>IH</sub> <sup>1</sup> | Input or I/O Leakage Current                                                                                                               | $0V \le V_{IN} \le V_{IH} (MAX)$               |                 | _                        | _   | +/-10                    | μΑ    |

|                                                |                                                                                                                                            |                                                | $V_{CCO} = 3.3$ | -30                      | _   | -150                     | μΑ    |

| I <sub>PU</sub> <sup>2</sup>                   | I/O Weak Pull-up Resistor Current                                                                                                          | $0 \le V_{IN} \le 0.7 V_{CCO}$ $V_{CCO} =$     |                 | -20                      | _   | -150                     | μΑ    |

|                                                |                                                                                                                                            |                                                | $V_{CCO} = 1.8$ | -10                      | _   | -150                     | μΑ    |

| $I_{PD}^2$                                     | I/O Weak Pull-down Resistor Current                                                                                                        | $V_{IL}(MAX) \le V_{IN} \le V_{IH}(MAX)$       |                 | 30                       | _   | 150                      | μΑ    |

| I <sub>BHLS</sub> <sup>2</sup>                 | Bus Hold Low Sustaining Current                                                                                                            | $V_{IN} = V_{IL} (MAX)$                        |                 | 30                       | _   | _                        | μΑ    |

|                                                |                                                                                                                                            |                                                | $V_{CCO} = 3.3$ | -30                      | _   | _                        | μΑ    |

| I <sub>BHHS</sub> <sup>2</sup>                 | $ S ^2$ Bus Hold High Sustaining Current $ V_{IN} = 0.7 V_{CCO} $                                                                          | $V_{CCO} = 2.5$                                | -20             | _                        | _   | μΑ                       |       |

|                                                |                                                                                                                                            |                                                | $V_{CCO} = 1.8$ | -10                      | _   | _                        | μΑ    |

| I <sub>BHLO</sub> <sup>2</sup>                 | Bus Hold Low Overdrive Current                                                                                                             | $0V \le V_{IN} \le V_{IH} (MAX)$               |                 |                          | _   | 150                      | μΑ    |

| I <sub>BHHO</sub> <sup>2</sup>                 | Bus Hold High Overdrive Current                                                                                                            | $0V \le V_{IN} \le V_{IH} (MAX)$               |                 | _                        | _   | -150                     | μΑ    |

| I <sub>CC</sub> <sup>3, 4, 5</sup>             | Operating Power Supply Current                                                                                                             | V <sub>CC</sub> = 3.3V                         |                 | _                        | 380 | _                        | mA    |

| V <sub>BHT</sub>                               | Bus Hold Trip Points                                                                                                                       |                                                |                 | V <sub>IL</sub><br>(MAX) | _   | V <sub>IH</sub><br>(MIN) | V     |

| C <sub>1</sub>                                 | I/O Capacitance <sup>3</sup>                                                                                                               | $V_{CC} = 3.3V$ , $V_{IO} = 0$ to $V_{IH}$ (M/ | AX)             |                          | 10  |                          | pf    |

| 01                                             | 1/O Capacitarice                                                                                                                           | V <sub>CCO</sub> = 3.3V, 2.5, 1.8, 1.5         |                 |                          | 10  |                          | Pi    |

| C                                              | $V_{CC} = 3.3V$ , $V_{IO} = 0$ to $V_{IH}$ (MAX)                                                                                           |                                                |                 | 10                       |     | nf                       |       |

| C <sub>2</sub>                                 | Clock Capacitance <sup>3</sup>                                                                                                             | V <sub>CCO</sub> = 3.3V, 2.5, 1.8, 1.5         |                 |                          | 10  | _                        | pf    |

| C                                              | Global Input Capacitance <sup>3</sup> $ \frac{V_{CC} = 3.3V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}}{V_{CCO} = 3.3V, 2.5, 1.8, 1.5} $ |                                                | AX)             |                          | 10  |                          | nf    |

| C <sub>3</sub>                                 |                                                                                                                                            |                                                |                 |                          | 10  | _                        | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

<sup>2.</sup> Only available for LVCMOS and LVTTL standards.

<sup>3.</sup>  $T_A = 25^{\circ}C$ , f = 1.0MHz.

<sup>4.</sup> Device configured with 16-bit counters.

<sup>5.</sup>  $I_{\text{CC}}$  varies with specific device configuration and operating frequency.

## ispMACH 51024VG External Switching Characteristics

#### **Over Recommended Operating Conditions**

|                               |                                                                                     | -     | 5    | -7    | <b>'</b> 5 | -1    | 0    | -12   |      |       |

|-------------------------------|-------------------------------------------------------------------------------------|-------|------|-------|------------|-------|------|-------|------|-------|

| Parameter                     | Description <sup>1,2,3</sup>                                                        | Min   | Max  | Min   | Max        | Min   | Max  | Min   | Max  | Units |

| t <sub>PD</sub>               | Data propagation delay, 5-PT bypass                                                 | _     | 5.0  | _     | 7.5        | _     | 10.0 | _     | 12.0 | ns    |

| t <sub>PD_PTSA</sub>          | Data propagation delay, intrasegment path                                           | _     | 6.0  | _     | 9.0        | _     | 11.5 | _     | 13.5 | ns    |

| t <sub>PD_GLOBAL</sub>        | Data propagation delay, intersegment path                                           | _     | 6.5  | _     | 9.75       | _     | 13.0 | _     | 16.0 | ns    |

| t <sub>S</sub>                | GLB register setup time before clock, 5-PT bypass                                   | 3.0   | _    | 5.0   | _          | 7.5   | _    | 9.3   | _    | ns    |

| t <sub>S_PTSA</sub>           | GLB register setup time before clock                                                | 3.0   | _    | 6.0   | _          | 8.5   | _    | 10.0  | _    | ns    |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                           | 2.8   | _    | 3.0   | _          | 4.0   | _    | 5.0   | _    | ns    |

| t <sub>H</sub>                | GLB register hold time before clock, 5-PT bypass                                    | 0.0   | _    | 0.0   | _          | 0.0   | _    | 0.0   | _    | ns    |

| t <sub>H_PTSA</sub>           | GLB register hold time before clock                                                 | 0.0   | _    | 0.0   | _          | 0.0   | _    | 0.0   | _    | ns    |

| t <sub>HIR</sub>              | GLB register hold time before clock, input reg. path                                | 0.0   | _    | 0.0   | _          | 0.0   | _    | 0.0   | _    | ns    |

| t <sub>CO</sub>               | GLB register clock-to-output delay                                                  | _     | 4.4  | _     | 5.0        | _     | 6.0  | _     | 7.0  | ns    |

| t <sub>R</sub>                | External reset pin to output delay                                                  | _     | 6.5  | _     | 9.0        | _     | 10.0 | _     | 10.9 | ns    |

| t <sub>RW</sub>               | External reset pulse duration                                                       | 4.0   | _    | 6.0   | _          | 8.0   | _    | 9.5   | _    | ns    |

| t <sub>LPTOE/DIS</sub>        | Input to output local product term output enable/disable                            | _     | 7.0  | _     | 9.75       | _     | 11.5 | _     | 13.4 | ns    |

| t <sub>SPTOE/DIS</sub>        | Input to output segment product term output enable/disable                          | _     | 8.0  | _     | 11.25      | _     | 17.5 | _     | 20.4 | ns    |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                            | _     | 6.2  | _     | 7.5        | _     | 8.85 | _     | 10.0 | ns    |

| t <sub>CW</sub>               | Global clock width, high or low                                                     | 1.6   | _    | 2.75  | _          | 3.6   | _    | 4.3   | _    | ns    |

| t <sub>GW</sub>               | Global gate width low (for low transparent) or high (for high transparent)          | 1.8   | _    | 2.75  | _          | 3.6   | _    | 4.3   | _    | ns    |

| t <sub>WIR</sub>              | Input register clock width, high or low                                             | 1.8   | _    | 2.75  | _          | 3.6   | _    | 4.3   | _    | ns    |

| <b>+</b> .                    | Clock-to-out skew, block level                                                      | _     | 0.25 | _     | 0.35       | _     | 0.45 | _     | 0.55 | ns    |

| <sup>T</sup> SKEW             | Clock-to-out skew, segment level                                                    | _     | 0.4  | _     | 0.5        | _     | 0.6  | _     | 0.7  | ns    |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                              | 178.6 | _    | 117.0 | _          | 87.0  | _    | 73.0  | _    | MHz   |

| f <sub>MAX</sub> (Ext.)       | Clock frequency with external feedback, 1/ (t <sub>S_PTSA</sub> + t <sub>CO</sub> ) | 135.1 | _    | 90.9  | _          | 69.0  | _    | 58.8  | _    | MHz   |

| f <sub>MAX</sub> (Tog.)       | Clock frequency max Toggle                                                          | 312.5 | _    | 181.0 | _          | 138.0 | _    | 116.0 | _    | MHz   |

Timing v.1.10

<sup>1.</sup> Timing numbers are based on default LVCMOS 3.3 I/O Buffers. Use timing adjusters provided to calculate timing for other standards.

<sup>2.</sup> Measured using standard switching circuit, assuming segment and global routing loading of 1, worst case PTSA loading and 1 output switching.

<sup>3.</sup> Pulse widths and clock widths less than minimum will cause unknown behavior.

<sup>4.</sup> Standard 16-bit counter using SRP feedback.

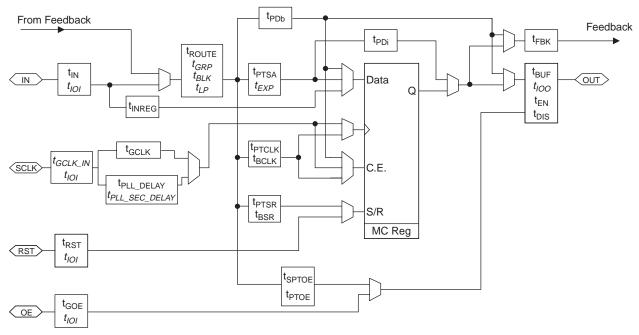

## **Timing Model**

The task of determining the timing through the ispMACH 5000VG family, like any CPLD, is relatively simple. The timing model provided in Figure 11 shows the specific delay paths. Once the implementation of a given function is determined either conceptually or from the software report file, the delay path of the function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model for a particular design. Note that the internal timing parameters are given for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device. For more information on the timing model and usage, please refer to Technical Note TN1001: *ispMACH 5000VG Timing Model Design and Usage Guidelines*.

Figure 11. ispMACH 5000VG Timing Model

Italicized items are optional delay adders

## ispMACH 5768VG Internal Timing Parameters (Continued)

#### **Over Recommended Operating Conditions**

|                    |                              | -   | 5    | -7  | 75   | -1  | 0    | -1  | 12   |       |

|--------------------|------------------------------|-----|------|-----|------|-----|------|-----|------|-------|

| Parameter          | Description                  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Units |

| t <sub>BSR</sub>   | Block PT Set/Reset Delay     | _   | 2.00 | _   | 3.00 | _   | 4.00 | _   | 4.80 | ns    |

| t <sub>PTSR</sub>  | Macrocell PT Set/Reset Delay | _   | 2.00 | _   | 3.00 | _   | 4.00 | _   | 4.80 | ns    |

| t <sub>SPTOE</sub> | Segment PT OE Delay          | _   | 2.40 | _   | 3.60 | _   | 7.75 | _   | 9.10 | ns    |

| t <sub>PTOE</sub>  | Macrocell PT OE Delay        | _   | 1.40 | _   | 2.10 | _   | 1.75 | _   | 2.10 | ns    |

Notes:

Timing v.1.20

## ispMACH 51024VG Internal Timing Parameters

#### **Over Recommended Operating Conditions**

|                            |                                                  | -        | 5    | -7   | 75   | -1   | 10   | -1   | 12   |       |

|----------------------------|--------------------------------------------------|----------|------|------|------|------|------|------|------|-------|

| Parameter                  | Description                                      | Min      | Max  | Min  | Max  | Min  | Max  | Min  | Max  | Units |

| In/Out Delays              |                                                  |          |      |      |      |      |      |      |      |       |

| t <sub>IN</sub>            | Input Buffer Delay                               | _        | 0.65 | —    | 0.95 | _    | 1.25 | _    | 1.40 | ns    |

| t <sub>GCLK_IN</sub>       | Global Clock Input Buffer Delay                  | _        | 0.65 | _    | 0.95 | _    | 1.25 | _    | 1.40 | ns    |

| t <sub>GOE</sub>           | Global OE Pin Delay                              | _        | 4.05 | _    | 5.00 | _    | 6.00 | _    | 7.00 | ns    |

| t <sub>BUF</sub>           | Delay through Output Buffer                      | _        | 1.15 | _    | 1.50 | _    | 1.75 | _    | 1.90 | ns    |

| t <sub>EN</sub>            | Output Enable Time                               | _        | 2.15 | _    | 2.50 | _    | 2.85 | _    | 3.00 | ns    |

| t <sub>DIS</sub>           | Output Disable Time                              | _        | 2.15 | _    | 2.50 | _    | 2.85 | _    | 3.00 | ns    |

| t <sub>RSTb</sub>          | Global RESETbar Pin Delay                        | _        | 4.60 | _    | 6.50 | _    | 7.00 | _    | 7.50 | ns    |

| Routing Delays             |                                                  | •        | •    |      | •    | •    | •    | •    | •    |       |

| t <sub>ROUTE</sub>         | Delay through SRP                                | _        | 2.80 | —    | 4.20 | _    | 5.65 | _    | 6.90 | ns    |

| t <sub>PTSA</sub>          | Product Term Sharing Array Delay                 | _        | 0.40 | _    | 1.85 | _    | 2.35 | _    | 2.50 | ns    |

| t <sub>PDB</sub>           | 5-PT Bypass Propagation Delay                    | _        | 0.40 | _    | 0.85 | _    | 1.35 | _    | 1.80 | ns    |

| t <sub>PDi</sub>           | Macrocell Propagation Delay                      | _        | 1.00 | _    | 0.50 | _    | 0.50 | _    | 0.80 | ns    |

| t <sub>INREG</sub>         | Input Buffer to Macrocell Register Delay         | _        | 3.00 | _    | 3.05 | _    | 3.50 | _    | 4.40 | ns    |

| t <sub>FBK</sub>           | Internal Feedback Delay                          | <b>—</b> | 0.00 | _    | 0.00 | _    | 0.00 | _    | 0.00 | ns    |

| t <sub>GCLK</sub>          | Global Clock Tree Delay                          | _        | 0.85 | _    | 0.70 | _    | 0.55 | _    | 0.65 | ns    |

| t <sub>PLL_DELAY</sub>     | Programmable PLL Delay Increment                 | _        | 0.50 | _    | 0.50 | _    | 0.50 | _    | 0.50 | ns    |

| t <sub>PLL_SEC_DELAY</sub> | Additional Delay When Using Secondary PLL Output | _        | 0.60 | _    | 0.60 | _    | 0.60 | _    | 0.60 | ns    |

| t <sub>GRP</sub>           | Global Routing Pool Delay                        | _        | 1.50 | _    | 2.25 | _    | 3.00 | _    | 4.00 | ns    |

| Register/Latch             | Delays                                           |          |      |      |      |      |      |      |      | '     |

| t <sub>S</sub>             | D-Register Setup Time                            | 0.65     | _    | 0.65 | _    | 1.05 | _    | 1.25 | _    | ns    |

| t <sub>S_PT</sub>          | D-Register Setup Time with PT Clock              | 0.65     | _    | 0.65 | _    | 1.05 | _    | 1.25 | _    | ns    |

| t <sub>H</sub>             | D-Register Hold Time                             | 0.00     | _    | 0.00 | _    | 0.00 | _    | 0.00 | _    | ns    |

| t <sub>ST</sub>            | T-Register Setup Time                            | 1.15     | _    | 1.15 | _    | 1.55 | _    | 1.75 | _    | ns    |

| t <sub>ST_PT</sub>         | T-Register Setup Time with PT Clock              | 1.15     | _    | 1.15 | _    | 1.55 | _    | 1.75 | _    | ns    |

| t <sub>HT</sub>            | T-Register Hold Time                             | 0.00     | _    | 0.00 | _    | 0.00 | _    | 0.00 | _    | ns    |

| t <sub>COi</sub>           | Register Clock to Output/Feedback MUX Time       | _        | 1.75 | _    | 1.85 | _    | 2.45 | _    | 3.05 | ns    |

<sup>1.</sup> Internal Timing Parameters are not tested and are for reference only. Refer to Timing Model in this data sheet for further details.

<sup>2.</sup> t<sub>PLL\_DELAY</sub> is the unit increment by which the clock signal can be incremented. The PLL can adjust the clock signal by up to 3.5ns in either direction in units of 0.5ns for each step.

# ispMACH 51024VG Internal Timing Parameters (Continued)

#### **Over Recommended Operating Conditions**

|                    |                                                                    | -    | 5    | -7   | <b>7</b> 5 | -1   | 10   | -1   | 2    |       |

|--------------------|--------------------------------------------------------------------|------|------|------|------------|------|------|------|------|-------|

| Parameter          | Description                                                        | Min  | Max  | Min  | Max        | Min  | Max  | Min  | Max  | Units |

| t <sub>CES</sub>   | Clock Enable Setup Time                                            | 2.60 | _    | 3.90 | _          | 5.05 | _    | 5.95 | _    | ns    |

| t <sub>CEH</sub>   | Clock Enable Hold Time                                             | 0.60 | _    | 0.90 | _          | 1.20 | _    | 1.45 | _    | ns    |

| t <sub>SL</sub>    | Latch Setup Time                                                   | 2.80 | _    | 4.20 | _          | 5.50 | _    | 6.60 | _    | ns    |

| t <sub>SL_PT</sub> | Latch Setup Time with PT Clock                                     | 2.80 | _    | 4.20 | _          | 5.50 | _    | 6.60 | _    | ns    |

| t <sub>HL</sub>    | Latch Hold Time                                                    | 0.00 | _    | 0.00 | _          | 0.00 | _    | 0.00 | _    | ns    |

| t <sub>GOi</sub>   | Latch Gate to Output/Feedback MUX Time                             | _    | 1.75 | _    | 2.50       | _    | 3.50 | _    | 4.50 | ns    |

| t <sub>PDLi</sub>  | Propagation Delay through Transparent Latch to Output/Feedback MUX | _    | 2.40 | _    | 3.50       | _    | 4.00 | _    | 4.50 | ns    |

| t <sub>SRi</sub>   | Asynchronous Reset or Set to Output/Feedback MUX Delay             | _    | 0.75 | _    | 1.00       | _    | 1.25 | _    | 1.50 | ns    |

| t <sub>SRR</sub>   | Asynchronous Reset or Set Recovery Delay                           | _    | 1.00 | _    | 1.50       | _    | 2.00 | _    | 2.50 | ns    |

| Control Delays     | 3                                                                  | •    |      | ,    |            |      |      |      |      |       |

| t <sub>BCLK</sub>  | GLB PT Clock Delay                                                 | _    | 3.10 | _    | 4.65       | _    | 6.00 | _    | 7.00 | ns    |

| t <sub>PTCLK</sub> | Macrocell PT Clock Delay                                           | _    | 3.00 | _    | 4.50       | _    | 6.00 | _    | 7.00 | ns    |

| t <sub>BSR</sub>   | Block PT Set/Reset Delay                                           | _    | 2.00 | _    | 3.00       | _    | 4.00 |      | 4.80 | ns    |

| t <sub>PTSR</sub>  | Macrocell PT Set/Reset Delay                                       | _    | 2.00 | _    | 3.00       | _    | 4.00 |      | 4.80 | ns    |

| t <sub>SPTOE</sub> | Segment PT OE Delay                                                | _    | 2.40 | _    | 3.60       | _    | 7.75 |      | 9.10 | ns    |

| t <sub>PTOE</sub>  | Macrocell PT OE Delay                                              | _    | 1.40 | _    | 2.10       | _    | 1.75 | _    | 2.10 | ns    |

Notes:

Timing v.1.10

<sup>1.</sup> Internal Timing Parameters are not tested and are for reference only. Refer to Timing Model in this data sheet for further details.

<sup>2.</sup> t<sub>PLL\_DELAY</sub> is the unit increment by which the clock signal can be incremented. The PLL can adjust the clock signal by up to 3.5ns in either direction in units of 0.5ns for each step.

## sysCLOCK PLL Timing

### Over Recommended Operating Conditions<sup>1</sup>

| Symbol                   | Parameter                                                  | Conditions                                                | Min      | Max      | Units |

|--------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------|----------|-------|

| $t_R, t_F$               | Input clock, rise and fall time                            | 20% to 80%                                                | _        | 3.0      | ns    |

| t <sub>INSTB</sub>       | Input clock stability, period jitter (peak) <sup>1</sup>   | _                                                         | _        | +/- 200  | ps    |

| t <sub>PWH</sub>         | Input clock, high time                                     | _                                                         | 1.6      | _        | ns    |

| t <sub>PWL</sub>         | Input clock, low time                                      | _                                                         | 1.6      | _        | ns    |

| f <sub>MDIVIN</sub>      | M Divider input, frequency range                           | _                                                         | 5        | 180      | MHz   |

| f <sub>MDIVOUT</sub>     | M Divider output, frequency range                          | _                                                         | 5        | 180      | MHz   |

| f <sub>VDIVIN</sub>      | V Divider input, frequency range                           | _                                                         | 60       | 200      | MHz   |

| f <sub>VDIVOUT</sub>     | V Divider output, frequency range                          | _                                                         | 5        | 180      | MHz   |

| toutduty                 | Output clock, duty cycle                                   | _                                                         | 40       | 60       | %     |

| •                        | Output clock, cycle to cycle jitter (peak)                 | Clean Reference,<br>5MHz ≤ f <sub>MDIVOUT</sub> < 80MHz   | _        | +/- 200  | ps    |

| t <sub>JIT(CC)</sub>     | Output clock, cycle to cycle jitter (peak)                 | Clean Reference,<br>80MHz ≤ f <sub>MDIVOUT</sub> ≤ 180MHz | _        | +/- 100  | ps    |

|                          | Output clock, accumulated phase jitter (peak) <sup>2</sup> | Clean Reference,<br>5MHz ≤ f <sub>MDIVOUT</sub> < 80MHz   | _        | +/- 200  | ps    |

| t <sub>JIT(φ)</sub>      | Output clock, accumulated phase jitter (peak)              | Clean Reference,<br>80MHz ≤ f <sub>MDIVOUT</sub> ≤ 180MHz | _        | +/- 100  | ps    |

| t <sub>CLK_OUT_DLY</sub> | Input clock to CLK_OUT delay                               | Internal feedback                                         | _        | 1        | ns    |

| $t_{\phi}$               | Input clock to external feedback delta                     | External feedback                                         | _        | 500      | ps    |

| t <sub>LOCK</sub>        | Time to acquire phase lock after input stable              | _                                                         | _        | 30       | μS    |

| t <sub>PLL_DELAY</sub>   | Delay increment                                            | _                                                         | +/- 0.35 | +/- 0.65 | ns    |

| t <sub>RANGE</sub>       | Total output delay range                                   | _                                                         | +/- 2.45 | +/- 4.55 | ns    |

| t <sub>PLL_RSTR</sub>    | Reset recovery time of the M-divider                       | _                                                         | 11.0     | _        | ns    |

| t <sub>PLL_RSTW</sub>    | Minimum reset pulse width                                  | _                                                         | 6.0      | _        | ns    |

<sup>1.</sup> This condition assures that the output phase jitter  $(t_{J|T(\phi)})$  will remain within specification. 2. Accumulated jitter measured over 10,000 waveform samples.

# **Boundary Scan Timing Specifications**

| Symbol               | Parameter                                                      | Min. | Max. | Units |

|----------------------|----------------------------------------------------------------|------|------|-------|

| t <sub>BTCP</sub>    | TCK [BSCAN test] clock cycle                                   | 40   | _    | ns    |

| t <sub>BTCH</sub>    | TCK [BSCAN test] pulse width high                              | 20   | _    | ns    |

| t <sub>BTCL</sub>    | TCK [BSCAN test] pulse width low                               | 20   | _    | ns    |

| t <sub>BTSU</sub>    | TCK [BSCAN test] setup time                                    | 8    | _    | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN test] hold time                                     | 10   | _    | ns    |

| t <sub>BRF</sub>     | TCK [BSCAN test] rise and fall time                            | 50   | _    | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output           | _    | 10   | ns    |

| t <sub>BTOZ</sub>    | TAP controller falling edge of clock to data output disable    | _    | 10   | ns    |

| t <sub>BTVO</sub>    | TAP controller falling edge of clock to data output enable     | _    | 10   | ns    |

| t <sub>BVTCPSU</sub> | BSCAN test Capture register setup time                         | 8    | _    | ns    |

| t <sub>BTCPH</sub>   | BSCAN test Capture register hold time                          | 10   | _    | ns    |

| t <sub>BTUCO</sub>   | BSCAN test Update reg, falling edge of clock to valid output   | _    | 25   | ns    |

| t <sub>BTUOZ</sub>   | BSCAN test Update reg, falling edge of clock to output disable | _    | 25   | ns    |

| t <sub>BTUOV</sub>   | BSCAN test Update reg, falling edge of clock to output enable  | _    | 25   | ns    |

| Bank<br>No. | Signal         | 256<br>fpBGA | 484<br>fpBGA |

|-------------|----------------|--------------|--------------|

| 3           | 4B-24          | G11          | M19          |

| 3           | 4B-26          | F11          | M21          |

| 3           | 4B-28          | F10          | L19          |

| 3           | 4B-30/CLK_OUT1 | B11          | L20          |

| 3           | GNDIO3         | GND          | GND          |

| 3           | 4A-30          | NC           | M17          |

| 3           | 4A-28          | NC           | M22          |

| 3           | 4A-26          | NC           | K20          |

| 3           | 4A-24          | NC           | L18          |

| 3           | 4A-22          | NC           | L21          |

| 3           | 4A-20          | NC           | K19          |

| 3           | 4A-18          | NC           | L22          |

| 3           | 4A-16          | NC           | K17          |

| 3           | 4A-14          | E13          | K22          |

| 3           | 4A-12          | B12          | L17          |

| 3           | GNDIO3         | GND          | GND          |

| 3           | 4A-10          | E15          | K21          |

| 3           | 4A-8           | D15          | K18          |

| 3           | 4A-6           | NC           | J17          |

| 3           | 4A-4           | NC           | J19          |

| 3           | 4A-2           | D16          | J22          |

| 3           | 4A-0           | E12          | J21          |

| 3           | 5B-0           | NC           | H19          |

| 3           | 5B-2           | NC           | H20          |

| 3           | 5B-4           | NC           | H17          |

| 3           | 5B-6           | NC           | H18          |

| 3           | 5B-8           | NC           | H22          |

| 3           | 5B-10          | NC           | H21          |

| 3           | GNDIO3         | GND          | GND          |

| 3           | 5B-12          | NC           | G20          |

| 3           | 5B-14          | NC           | G22          |

| 3           | 5B-16          | NC           | G17          |

| 3           | 5B-18          | NC           | G21          |

| 3           | 5B-20          | NC           | F19          |

| 3           | 5B-22          | NC           | F20          |

| 3           | 5B-24          | A16          | F22          |

| 3           | 5B-26          | B15          | E22          |

| 3           | 5B-28          | A15          | E19          |

| 3           | 5B-30          | D13          | E20          |

| 3           | 5A-30          | B14          | D22          |

| 3           | 5A-28          | B16          | D21          |

| 3           | GNDIO3         | GND          | GND          |

| 3           | 5A-26          | C16          | D20          |

| Bank<br>No. | Signal      | 256<br>fpBGA | 484<br>fpBGA |

|-------------|-------------|--------------|--------------|

| 3           | 5A-24       | C15          | C22          |

| 3           | 5A-22       | D14          | C18          |

| 3           | 5A-20       | A14          | C19          |

| 3           | 5A-18       | C13          | D17          |

| 3           | 5A-16       | B13          | C21          |

| 3           | 5A-14       | NC           | NC           |

| 3           | 5A-12       | NC           | NC           |

| 3           | GNDIO3      | GND          | GND          |

| 3           | 5A-10       | NC           | NC           |

| 3           | 5A-8        | NC           | NC           |

| 3           | 5A-6        | NC           | B22          |

| 3           | 5A-4        | NC           | D18          |

| 3           | 5A-2        | NC           | B20          |

| 3           | 5A-0        | NC           | F17          |

| 3           | 5D-0        | NC           | B19          |

| 3           | 5D-2        | NC           | C17          |

| 3           | GNDIO3      | GND          | GND          |

| 3           | 5D-4        | NC           | A21          |

| 3           | 5D-6        | NC           | D15          |

| 3           | 5D-8        | NC           | A20          |

| 3           | 5D-10       | NC           | C16          |

| 3           | 5D-12       | NC           | A19          |

| 3           | 5D-14       | NC           | F16          |

| 3           | 5D-16       | NC           | B16          |

| 3           | 5D-18       | NC           | D14          |

| 3           | 5D-20       | NC           | A18          |

| 3           | 5D-22       | A13          | F15          |

| 3           | 5D-24       | A12          | A17          |

| 3           | 5D-26       | A11          | B15          |

| 3           | GNDIO3      | GND          | GND          |

| 3           | 5D-28       | A10          | A16          |

| 3           | 5D-30       | C11          | F14          |

| 3           | 5C-0        | A9           | C15          |

| 3           | 5C-2        | D12          | D13          |

| 3           | 5C-4        | D11          | E15          |

| 3           | 5C-6        | B10          | F13          |

| 3           | 5C-8        | В9           | B14          |

| 3           | 5C-10       | E11          | E13          |

| 3           | 5C-12/VREF3 | A8           | A15          |

| 3           | 5C-14       | D10          | D12          |

| 3           | 5C-16       | E10          | A14          |

| 3           | 5C-18       | A7           | B13          |

| 3           | GNDIO3      | GND          | GND          |

| Bank<br>No. | Signal         | 484<br>fpBGA | 676<br>fpBGA |

|-------------|----------------|--------------|--------------|

| 0           | 1A-30          | K5           | МЗ           |

| 0           | GNDIO0         | GND          | GND          |

| 0           | 1B-30/CLK_OUT0 | N1           | M2           |

| 0           | 1B-28          | M2           | M1           |

| 0           | 1B-26          | P1           | N6           |

| 0           | 1B-24          | L4           | N5           |

| 0           | 1B-22          | N2           | N4           |

| 0           | 1B-20          | МЗ           | N3           |

| 0           | 1B-18          | L5           | N2           |

| 0           | 1B-16          | R1           | N1           |

| 0           | 1B-14          | P2           | P6           |

| 0           | 1B-12          | N3           | P4           |

| 0           | GNDIO0         | GND          | GND          |

| 0           | 1B-10          | M6           | P3           |

| 0           | 1B-8           | M5           | P2           |

| 0           | 1B-6/PLL_RST0  | M4           | P1           |

| 0           | 1B-4/PLL_FBK0  | N4           | R4           |

| 0           | 1B-2           | N6           | R3           |

| 0           | 1B-0           | N5           | R2           |

| 1           | 2B-0           | NC           | R1           |

| 1           | 2B-2           | NC           | T1           |

| 1           | 2B-4           | NC           | T3           |

| 1           | 2B-6           | NC           | T2           |

| 1           | 2B-8           | NC           | U1           |

| 1           | 2B-10          | NC           | U2           |

| 1           | GNDIO1         | GND          | GND          |

| 1           | 2B-12          | NC           | U3           |

| 1           | 2B-14          | NC           | U4           |

| 1           | 2B-16          | NC           | V1           |

| 1           | 2B-18          | NC           | V2           |

| 1           | 2B-20          | NC           | V3           |

| 1           | 2B-22          | NC           | V4           |

| 1           | 2B-24          | NC           | W1           |

| 1           | 2B-26          | NC           | V6           |

| 1           | 2B-28          | NC           | W2           |

| 1           | 2B-30          | NC           | W3           |

| 1           | GNDIO1         | GND          | GND          |

| 1           | 2A-30          | NC           | Y1           |

| 1           | 2A-28          | NC           | W5           |

| 1           | 2A-26          | NC           | Y2           |

| 1           | 2A-24          | NC           | Y3           |

| 1           | 2A-22          | NC           | AA1          |

| 1           | 2A-20          | NC           | Y4           |

| Bank<br>No. | Signal | 484<br>fpBGA | 676<br>fpBGA |

|-------------|--------|--------------|--------------|

| 1           | 2A-18  | NC           | AA2          |

| 1           | 2A-16  | NC           | AA3          |

| 1           | 2A-14  | NC           | AB1          |

| 1           | 2A-12  | NC           | AB2          |

| 1           | GNDIO1 | GND          | GND          |

| 1           | 2A-10  | NC           | AA5          |

| 1           | 2A-8   | NC           | AB3          |

| 1           | 2A-6   | NC           | AC1          |

| 1           | 2A-4   | NC           | AB4          |

| 1           | 2A-2   | NC           | AC2          |

| 1           | 2A-0   | NC           | AD1          |

| 1           | 3B-0   | R5           | AC3          |

| 1           | 3B-2   | T2           | AD2          |

| 1           | 3B-4   | T5           | AE1          |

| 1           | 3B-6   | T3           | AD3          |

| 1           | 3B-8   | U1           | AE2          |

| 1           | 3B-10  | U4           | AC5          |

| 1           | GNDIO1 | GND          | GND          |

| 1           | 3B-12  | V1           | AF1          |

| 1           | 3B-14  | U3           | AD4          |

| 1           | 3B-16  | V5           | AE3          |

| 1           | 3B-18  | V2           | AC6          |

| 1           | 3B-20  | W1           | AF2          |

| 1           | 3B-22  | V3           | AG1          |

| 1           | 3B-24  | W2           | AF3          |

| 1           | 3B-26  | Y1           | AG2          |

| 1           | 3B-28  | Y2           | AH1          |

| 1           | 3B-30  | W3           | AE5          |

| 1           | 3A-30  | AA3          | AF4          |

| 1           | 3A-28  | W4           | AG3          |

| 1           | GNDIO1 | GND          | GND          |

| 1           | 3A-26  | W5           | AE6          |

| 1           | 3A-24  | Y4           | AH2          |

| 1           | 3A-22  | T6           | AJ1          |

| 1           | 3A-20  | Y5           | AG4          |

| 1           | 3A-18  | U6           | AF6          |

| 1           | 3A-16  | AA4          | AG5          |

| 1           | 3A-14  | NC           | AH4          |

| 1           | 3A-12  | NC           | AJ3          |

| 1           | GNDIO1 | GND          | GND          |

| 1           | 3A-10  | NC           | AK2          |

| 1           | 3A-8   | NC           | AE8          |

| 1           | 3A-6   | W6           | AH5          |

| Bank<br>No. | Signal      | 484<br>fpBGA | 676<br>fpBGA   |

|-------------|-------------|--------------|----------------|

| 1           | 3A-4        | V4           | AJ4            |

| 1           | 3A-2        | U7           | AK3            |

| 1           | 3A-0        | AB2          | AK4            |

| 1           | 3D-0        | V7           | AJ5            |

| 1           | 3D-2        | AA5          | AH6            |

| 1           | GNDIO1      | GND          | GND            |

| 1           | 3D-4        | AB3          | AF8            |

| 1           | 3D-6        | Y6           | AG7            |

| 1           | 3D-8        | AB4          | AK5            |

| 1           | 3D-10       | Y7           | AJ6            |

| 1           | 3D-12       | AB5          | AH7            |

| 1           | 3D-14       | V8           | AK6            |

| 1           | 3D-16       | AA7          | AJ7            |

| 1           | 3D-18       | Y8           | AH8            |

| 1           | 3D-20       | AB6          | AG9            |

| 1           | 3D-22       | W8           | AK7            |

| 1           | 3D-24       | AA8          | AF10           |

| 1           | 3D-26       | Y10          | AJ8            |

| 1           | GNDIO1      | GND          | GND            |

| 1           | 3D-28       | U8           | AH9            |

| 1           | 3D-30       | AB7          | AK8            |

| 1           | 3C-0        | U9           | AJ9            |

| 1           | 3C-2        | AA9          | AH10           |

| 1           | 3C-4        | W9           | AK9            |

| 1           | 3C-6        | AB8          | AG11           |

| 1           | 3C-8        | U10          | AJ10           |

| 1           | 3C-10       | AB9          | AF12           |

| 1           | 3C-12       | V11          | AH11           |

| 1           | 3C-14/VREF1 | AA10         | AK10           |

| 1           | 3C-16       | V10          | AJ11           |

| 1           | 3C-18       | AB10         | AK11           |

| 1           | GNDIO1      | GND          | GND            |

| 1           | 3C-20       | W10          | AH12           |

| 1           | 3C-22       | W11          | AJ12           |

| 1           | 3C-24       | U11          | AK12           |

| 1           | 3C-26       | AA11         | AH13           |

| 1           | 3C-28       | V12          | AJ13           |

| 1           | 3C-30       | AB11         | AK13           |

| 2           | 4C-30       | W12          | AK18           |

| 2           | 4C-28       | Y11          | AK19           |

| 2           | 4C-26       | Y12          | AJ19           |

| 2           | 4C-24       | AB12         | AH19           |

| 2           | 4C-22       | U12          | AK20           |

|             | <u> </u>    |              | _ · <b>_ ·</b> |

| Bank<br>No. | Signal      | 484<br>fpBGA | 676<br>fpBGA |

|-------------|-------------|--------------|--------------|

| 2           | 4C-20       | AA12         | AJ20         |

| 2           | GNDIO2      | GND          | GND          |

| 2           | 4C-18       | Y13          | AK21         |

| 2           | 4C-16       | AB13         | AH20         |

| 2           | 4C-14       | W13          | AF19         |

| 2           | 4C-12/VREF2 | AA13         | AJ21         |

| 2           | 4C-10       | U13          | AG20         |

| 2           | 4C-8        | AB14         | AK22         |

| 2           | 4C-6        | V13          | AH21         |

| 2           | 4C-4        | AA14         | AJ22         |

| 2           | 4C-2        | U14          | AK23         |

| 2           | 4C-0        | AB15         | AH22         |

| 2           | 4D-30       | Y15          | AJ23         |

| 2           | 4D-28       | AB16         | AK24         |

| 2           | GNDIO2      | GND          | GND          |

| 2           | 4D-26       | AA15         | AF21         |

| 2           | 4D-24       | W14          | AG22         |

| 2           | 4D-22       | AB17         | AH23         |

| 2           | 4D-20       | Y16          | AJ24         |

| 2           | 4D-18       | AA16         | AK25         |

| 2           | 4D-16       | Y17          | AH24         |

| 2           | 4D-14       | AB18         | AJ25         |

| 2           | 4D-12       | V15          | AK26         |

| 2           | 4D-10       | AB19         | AJ26         |

| 2           | 4D-8        | W15          | AH25         |

| 2           | 4D-6        | AB20         | AG24         |

| 2           | 4D-4        | AA18         | AF23         |

| 2           | GNDIO2      | GND          | GND          |

| 2           | 4D-2        | U15          | AK27         |

| 2           | 4D-0        | W17          | AK28         |

| 2           | 4A-0        | U16          | AJ27         |

| 2           | 4A-2        | AA19         | AH26         |

| 2           | 4A-4        | V16          | AE23         |

| 2           | 4A-6        | AB21         | AK29         |

| 2           | 4A-8        | NC           | AJ28         |

| 2           | 4A-10       | NC           | AH27         |

| 2           | GNDIO2      | GND          | GND          |

| 2           | 4A-12       | NC           | AG26         |

| 2           | 4A-14       | NC           | AF25         |

| 2           | 4A-16       | Y18          | AJ29         |

| 2           | 4A-18       | W18          | AG27         |

| 2           | 4A-20       | AA20         | AJ30         |

| 2           | 4A-22       | W19          | AH29         |

| Bank<br>No. | Signal | 484<br>fpBGA | 676<br>fpBGA |

|-------------|--------|--------------|--------------|

| 2           | 4A-24  | Y19          | AE25         |

| 2           | 4A-26  | V19          | AG28         |

| 2           | GNDIO2 | GND          | GND          |

| 2           | 4A-28  | Y21          | AF27         |

| 2           | 4A-30  | W20          | AE26         |

| 2           | 4B-30  | AA22         | AH30         |

| 2           | 4B-28  | W21          | AG29         |

| 2           | 4B-26  | Y22          | AF28         |

| 2           | 4B-24  | V20          | AG30         |

| 2           | 4B-22  | V21          | AF29         |

| 2           | 4B-20  | W22          | AC25         |

| 2           | 4B-18  | V18          | AE28         |

| 2           | 4B-16  | U20          | AF30         |

| 2           | 4B-14  | V22          | AD27         |

| 2           | 4B-12  | U19          | AE29         |

| 2           | GNDIO2 | GND          | GND          |

| 2           | 4B-10  | U17          | AC26         |

| 2           | 4B-8   | U22          | AD28         |

| 2           | 4B-6   | T20          | AE30         |

| 2           | 4B-4   | T21          | AD29         |

| 2           | 4B-2   | T17          | AC28         |

| 2           | 4B-0   | R20          | AD30         |

| 2           | 5A-0   | NC           | AC29         |

| 2           | 5A-2   | NC           | AB27         |

| 2           | 5A-4   | NC           | AC30         |

| 2           | 5A-6   | NC           | AB28         |

| 2           | 5A-8   | NC           | AA26         |

| 2           | 5A-10  | NC           | AB29         |

| 2           | GNDIO2 | GND          | GND          |

| 2           | 5A-12  | NC           | AB30         |

| 2           | 5A-14  | NC           | AA28         |

| 2           | 5A-16  | NC           | AA29         |

| 2           | 5A-18  | NC           | AA30         |

| 2           | 5A-20  | NC           | Y27          |

| 2           | 5A-22  | NC           | Y28          |

| 2           | 5A-24  | NC           | Y29          |

| 2           | 5A-26  | NC           | W26          |

| 2           | 5A-28  | NC           | Y30          |

| 2           | 5A-30  | NC           | W28          |

| 2           | GNDIO2 | GND          | GND          |

| 2           | 5B-30  | NC           | W29          |

| 2           | 5B-28  | NC           | W30          |

| 2           | 5B-26  | NC           | V25          |

| Bank<br>No. | Signal         | 484<br>fpBGA | 676<br>fpBGA |  |  |  |

|-------------|----------------|--------------|--------------|--|--|--|

| 2           | 5B-24          | NC           | V26          |  |  |  |

| 2           | 5B-22          | NC           | V27          |  |  |  |

| 2           | 5B-20          | NC           | V28          |  |  |  |

| 2           | 5B-18          | NC           | V29          |  |  |  |

| 2           | 5B-16          | NC           | V30          |  |  |  |

| 2           | 5B-14          | NC           | U25          |  |  |  |

| 2           | 5B-12          | NC           | U27          |  |  |  |

| 2           | GNDIO2         | GND          | GND          |  |  |  |

| 2           | 5B-10          | NC           | U28          |  |  |  |

| 2           | 5B-8           | NC           | U29          |  |  |  |

| 2           | 5B-6           | NC           | U30          |  |  |  |

| 2           | 5B-4           | NC           | T27          |  |  |  |

| 2           | 5B-2           | NC           | T28          |  |  |  |

| 2           | 5B-0           | NC           | T29          |  |  |  |

| 3           | 6B-0           | R21          | T30          |  |  |  |

| 3           | 6B-2           | T22          | R29          |  |  |  |

| 3           | 6B4/PLL_FBK1   | P21          | R27          |  |  |  |

| 3           | 6B6/PLL_RST1   | N20          | R28          |  |  |  |

| 3           | 6B-8           | R22          | R30          |  |  |  |

| 3           | 6B-10          | N21          | P30          |  |  |  |

| 3           | GNDIO3         | GND          | GND          |  |  |  |

| 3           | 6B-12          | M18          | P29          |  |  |  |

| 3           | 6B-14          | N19          | P28          |  |  |  |

| 3           | 6B-16          | P22          | P27          |  |  |  |

| 3           | 6B-18          | M20          | N30          |  |  |  |

| 3           | 6B-20          | N22          | N29          |  |  |  |

| 3           | 6B-22          | N17          | N28          |  |  |  |

| 3           | 6B-24          | M19          | N27          |  |  |  |

| 3           | 6B-26          | M21          | N25          |  |  |  |

| 3           | 6B-28          | L19          | M30          |  |  |  |

| 3           | 6B-30/CLK_OUT1 | L20          | M29          |  |  |  |

| 3           | GNDIO3         | GND          | GND          |  |  |  |

| 3           | 6A-30          | M17          | M28          |  |  |  |

| 3           | 6A-28          | M22          | L30          |  |  |  |

| 3           | 6A-26          | K20          | M26          |  |  |  |

| 3           | 6A-24          | L18          | L29          |  |  |  |

| 3           | 6A-22          | L21          | L28          |  |  |  |

| 3           | 6A-20          | K19          | L27          |  |  |  |

| 3           | 6A-18          | L22          | K30          |  |  |  |

| 3           | 6A-16          | K17          | K29          |  |  |  |

| 3           | 6A-14          | K22          | K28          |  |  |  |

| 3           | 6A-12          | L17          | J30          |  |  |  |

| 3           | GNDIO3         | GND          | GND          |  |  |  |

|             |        | <u> </u>     |              |  |  |  |

|-------------|--------|--------------|--------------|--|--|--|

| Bank<br>No. | Signal | 484<br>fpBGA | 676<br>fpBGA |  |  |  |

| 3           | 6A-10  | K21          | J29          |  |  |  |

| 3           | 6A-8   | K18          | K26          |  |  |  |

| 3           | 6A-6   | J17          | J28          |  |  |  |

| 3           | 6A-4   | J19          | H30          |  |  |  |

| 3           | 6A-2   | J22          | J27          |  |  |  |

| 3           | 6A-0   | J21          | H29          |  |  |  |

| 3           | 7B-0   | H19          | G30          |  |  |  |

| 3           | 7B-2   | H20          | H28          |  |  |  |

| 3           | 7B-4   | H17          | G29          |  |  |  |

| 3           | 7B-6   | H18          | F30          |  |  |  |

| 3           | 7B-8   | H22          | G28          |  |  |  |

| 3           | 7B-10  | H21          | H26          |  |  |  |

| 3           | GNDIO3 | GND          | GND          |  |  |  |

| 3           | 7B-12  | G20          | F29          |  |  |  |

| 3           | 7B-14  | G22          | G27          |  |  |  |

| 3           | 7B-16  | G17          | E30          |  |  |  |

| 3           | 7B-18  | G21          | F28          |  |  |  |

| 3           | 7B-20  | F19          | H25          |  |  |  |

| 3           | 7B-22  | F20          | E29          |  |  |  |

| 3           | 7B-24  | F22          | D30          |  |  |  |

| 3           | 7B-26  | E22          | E28          |  |  |  |

| 3           | 7B-28  | E19          | D29          |  |  |  |

| 3           | 7B-30  | E20          | C30          |  |  |  |

| 3           | 7A-30  | D22          | F26          |  |  |  |

| 3           | 7A-28  | D21          | E27          |  |  |  |

| 3           | GNDIO3 | GND          | GND          |  |  |  |

| 3           | 7A-26  | D20          | D28          |  |  |  |

| 3           | 7A-24  | C22          | F25          |  |  |  |

| 3           | 7A-22  | C18          | C29          |  |  |  |

| 3           | 7A-20  | C19          | B30          |  |  |  |

| 3           | 7A-18  | D17          | D27          |  |  |  |

| 3           | 7A-16  | C21          | E25          |  |  |  |

| 3           | 7A-14  | NC           | D26          |  |  |  |

| 3           | 7A-12  | NC           | C27          |  |  |  |

| 3           | GNDIO3 | GND          | GND          |  |  |  |

| 3           | 7A-10  | NC           | B28          |  |  |  |

| 3           | 7A-8   | NC           | A29          |  |  |  |

| 3           | 7A-6   | B22          | F23          |  |  |  |

| 3           | 7A-4   | D18          | C26          |  |  |  |

| 3           | 7A-2   | B20          | B27          |  |  |  |

| 3           | 7A-0   | F17          | A28          |  |  |  |

| 3           | 7D-0   | B19          | A27          |  |  |  |

| 3           | 7D-2   | C17          | B26          |  |  |  |

| Bank<br>No. | Signal      | 484<br>fpBGA | 676<br>fpBGA |

|-------------|-------------|--------------|--------------|

| 3           | GNDIO3      | GND          | GND          |

| 3           | 7D-4        | A21          | E23          |

| 3           | 7D-6        | D15          | D24          |

| 3           | 7D-8        | A20          | C25          |

| 3           | 7D-10       | C16          | A26          |

| 3           | 7D-12       | A19          | B25          |

| 3           | 7D-14       | F16          | C24          |

| 3           | 7D-16       | B16          | A25          |

| 3           | 7D-18       | D14          | B24          |

| 3           | 7D-20       | A18          | C23          |

| 3           | 7D-22       | F15          | D22          |

| 3           | 7D-24       | A17          | A24          |

| 3           | 7D-26       | B15          | E21          |

| 3           | GNDIO3      | GND          | GND          |

| 3           | 7D-28       | A16          | B23          |

| 3           | 7D-30       | F14          | C22          |

| 3           | 7C-0        | C15          | A23          |

| 3           | 7C-2        | D13          | B22          |

| 3           | 7C-4        | E15          | C21          |

| 3           | 7C-6        | F13          | A22          |

| 3           | 7C-8        | B14          | D20          |

| 3           | 7C-10       | E13          | B21          |

| 3           | 7C-12/VREF3 | A15          | E19          |

| 3           | 7C-14       | D12          | C20          |

| 3           | 7C-16       | A14          | A21          |

| 3           | 7C-18       | B13          | B20          |

| 3           | GNDIO3      | GND          | GND          |

| 3           | 7C-20       | A13          | A20          |

| 3           | 7C-22       | B12          | C19          |

| 3           | 7C-24       | C13          | B19          |

| 3           | 7C-26       | A12          | A19          |

| 3           | 7C-28       | C12          | B18          |

| 3           | 7C-30       | A11          | A18          |

| _           | GCLK0       | P6           | R5           |

| _           | GCLK1       | R6           | T6           |

| _           | GCLK2       | P17          | R25          |

| _           | GCLK3       | P19          | P26          |

| _           | GOE0        | R18          | T26          |