## Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | 8052                                                                |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 12.58MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 34                                                                  |

| Program Memory Size        | 62KB (62K x 8)                                                      |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | 4K x 8                                                              |

| RAM Size                   | 2.25K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                         |

| Data Converters            | A/D 10x24b; D/A 1x12b, 2x16b                                        |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                           |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc845bcpz62-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SPECIFICATIONS<sup>1</sup>

$AV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V,  $DV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V, REFIN(-) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz crystal; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Input buffer on for primary ADC, unless otherwise noted. Core speed = 1.57 MHz (default CD = 3), unless otherwise noted.

| Parameter                                         | Min       | Тур                                     | Max  | Unit              | Test Conditions/Comments                                                                                                   |

|---------------------------------------------------|-----------|-----------------------------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| PRIMARY ADC                                       |           |                                         |      |                   |                                                                                                                            |

| Conversion Rate                                   | 5.4       |                                         | 105  | Hz                | Chop on (ADCMODE.3 = $0$ )                                                                                                 |

|                                                   | 16.06     |                                         | 1365 | Hz                | Chop off (ADCMODE.3 = 1)                                                                                                   |

| No Missing Codes <sup>2</sup>                     | 24        |                                         |      | Bits              | $\leq$ 26.7 Hz update rate with chop enabled                                                                               |

|                                                   | 24        |                                         |      | Bits              | ≤80.3 Hz update rate with chop disabled                                                                                    |

| Resolution (ADuC845/ADuC847)                      | See Table | e 11 and Table 1                        | 5    |                   |                                                                                                                            |

| Resolution (ADuC848)                              | See Table | e 13 and Table 1                        | 7    |                   |                                                                                                                            |

| Output Noise (ADuC845/ADuC847)                    | See Table | e 10 and Table 1                        | 4    | μV (rms)          | Output noise varies with selected update rates, gain range, and chop status.                                               |

| Output Noise (ADuC848)                            | See Table | e 12 and Table 1                        | 6    | μV (rms)          | Output noise varies with selected update rates, gain range, and chop status.                                               |

| Integral Nonlinearity                             |           |                                         | ±15  | ppm of FSR        | 1 LSB <sub>16</sub>                                                                                                        |

| Offset Error <sup>3</sup>                         |           | ±3                                      |      | μV                | Chop on                                                                                                                    |

|                                                   |           |                                         |      |                   | Chop off, offset error is in the order of the noise<br>for the programmed gain and update rate<br>following a calibration. |

| Offset Error Drift vs. Temperature <sup>2</sup>   |           | ±10                                     |      | nV/°C             | Chop on (ADCMODE.3 $=$ 0)                                                                                                  |

|                                                   |           | ±200                                    |      | nV/°C             | Chop off (ADCMODE.3 = 1)                                                                                                   |

| Full-Scale Error <sup>4</sup>                     |           |                                         |      |                   |                                                                                                                            |

| ADuC845/ADuC847                                   |           | ±10                                     |      | μV                | ±20 mV to ±2.56 V                                                                                                          |

| ADuC848                                           |           | ±10                                     |      | μV                | ±20 mV to ±640 mV                                                                                                          |

|                                                   |           | ±0.5                                    |      | LSB <sub>16</sub> | ±1.28 V to ±2.56 V                                                                                                         |

| Gain Error Drift vs. Temperature <sup>4</sup>     |           | ±0.5                                    |      | ppm/°C            |                                                                                                                            |

| Power Supply Rejection                            |           |                                         |      |                   |                                                                                                                            |

|                                                   | 80        |                                         |      | dB                | $AIN = 1 V, \pm 2.56 V, chop enabled$                                                                                      |

|                                                   |           | 113                                     |      | dB                | $AIN = 7.8 \text{ mV}, \pm 20 \text{ mV}, \text{ chop enabled}$                                                            |

|                                                   |           | 80                                      |      | dB                | AIN = 1 V, $\pm 2.56$ V, chop disabled <sup>2</sup>                                                                        |

| PRIMARY ADC ANALOG INPUTS                         |           |                                         |      |                   |                                                                                                                            |

| Differential Input Voltage Ranges <sup>5,6</sup>  |           |                                         |      |                   | Gain = 1 to 128                                                                                                            |

| Bipolar Mode (ADC0CON1.5 = 0)                     |           | $\pm$ 1.024 ×<br>V <sub>REF</sub> /GAIN |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) - REFIN2(-) \text{ (or Int 1.25 } V_{REF})$                           |

| Unipolar Mode (ADC0CON1.5 = 1)                    |           | 0 – 1.024 ×<br>V <sub>REF</sub> /GAIN   |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) - REFIN2(-) \text{ (or Int 1.25 } V_{REF})$                           |

| ADC Range Matching                                |           | ±2                                      |      | μV                | AIN = 18 mV, chop enabled                                                                                                  |

| Common-Mode Rejection DC                          |           |                                         |      |                   | Chop enabled, chop disabled                                                                                                |

| On AIN                                            | 95        |                                         |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   |           | 113                                     |      | dB                | $AIN = 1 V$ , range = $\pm 2.56 V$                                                                                         |

| Common-Mode Rejection<br>50 Hz/60 Hz <sup>2</sup> |           |                                         |      |                   | 50 Hz/60 Hz $\pm$ 1 Hz, 16.6 Hz and 50 Hz update rate, chop enabled, REJ60 enabled                                         |

| On AIN                                            | 95        |                                         |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   | 90        |                                         |      | dB                | AIN = 1 V, range = $\pm 2.56$ V                                                                                            |

## **Data Sheet**

# ADuC845/ADuC847/ADuC848

| Parameter                                         | Min                        | Тур            | Max                       | Unit              | Test Conditions/Comments                                                               |

|---------------------------------------------------|----------------------------|----------------|---------------------------|-------------------|----------------------------------------------------------------------------------------|

| Normal Mode Rejection 50 Hz/60 Hz <sup>2</sup>    |                            |                |                           |                   |                                                                                        |

| On AIN                                            | 75                         |                |                           | dB                | 50 Hz/60 Hz ± 1 Hz, 16.6 Hz Fadc, SF = 52H, chop<br>on, REJ60 on                       |

|                                                   | 100                        |                |                           | dB                | 50 Hz $\pm$ 1 Hz, 16.6 Hz Fadc, SF = 52H, chop on                                      |

|                                                   | 67                         |                |                           | dB                | 50 Hz/60 Hz $\pm$ 1 Hz, 50 Hz Fadc, SF = 52H, chop off, REJ60 on                       |

|                                                   | 100                        |                |                           | dB                | 50 Hz ± 1 Hz, 50 Hz Fadc, SF = 52H, chop off                                           |

| Analog Input Current <sup>2</sup>                 |                            |                | ±1                        | nA                | $T_{MAX} = 85^{\circ}C$ , buffer on                                                    |

|                                                   |                            |                | ±5                        | nA                | T <sub>MAX</sub> = 125°C, buffer on                                                    |

| Analog Input Current Drift                        |                            | ±5             |                           | pA/°C             | T <sub>MAX</sub> = 85°C, buffer on                                                     |

|                                                   |                            | ±15            |                           | pA/°C             | T <sub>MAX</sub> = 125°C, buffer on                                                    |

| Average Input Current                             |                            | ±125           |                           | nA/V              | ±2.56 V range, buffer bypassed                                                         |

| Average Input Current Drift                       |                            | ±2             |                           | pA/V/°C           | Buffer bypassed                                                                        |

| Absolute AIN Voltage Limits <sup>2</sup>          | A <sub>GND</sub> + 0.1     |                | AV <sub>DD</sub> –<br>0.1 | V                 | AIN1 AIN10 and AINCOM with buffer enabled                                              |

| Absolute AIN Voltage Limits <sup>2</sup>          | A <sub>GND</sub> –<br>0.03 |                | AV <sub>DD</sub> + 0.03   | v                 | AIN1 AIN10 and AINCOM with buffer bypassed                                             |

| EXTERNAL REFERENCE INPUTS                         |                            |                |                           |                   |                                                                                        |

| REFIN(+) to REFIN(–) Voltage                      |                            | 2.5            |                           | v                 | REFIN refers to both REFIN and REFIN2                                                  |

| REFIN(+) to REFIN(-) Range <sup>2</sup>           | 1                          |                | AVDD                      | v                 | REFIN refers to both REFIN and REFIN2                                                  |

| Average Reference Input Current                   |                            | ±1             |                           | μA/V              | Both ADCs enabled                                                                      |

| Average Reference Input Current<br>Drift          |                            | ±0.1           |                           | nA/V/°C           |                                                                                        |

| NOXREF Trigger Voltage                            | 0.3                        |                | 0.65                      | v                 | NOXREF (ADCSTAT.4) bit active if $V_{REF} > 0.3$ V, and inactive if $V_{RFF} > 0.65$ V |

| Common-Mode Rejection                             |                            |                |                           |                   |                                                                                        |

| DC Rejection                                      |                            | 125            |                           | dB                | $AIN = 1 V$ , range = $\pm 2.56 V$                                                     |

| 50 Hz/60 Hz Rejection <sup>2</sup>                | 90                         |                |                           | dB                | 50 Hz/60 Hz $\pm$ 1 Hz, AIN = 1 V, range = $\pm$ 2.56 V, SF = 82                       |

| Normal Mode Rejection<br>50 Hz/60 Hz <sup>2</sup> | 75                         |                |                           | dB                | 50 Hz/60 Hz $\pm$ 1 Hz, AIN = 1 V, range = $\pm$ 2.56 V, SF = 52H, chop on, REJ60 on   |

|                                                   | 100                        |                |                           | dB                | 50 Hz $\pm$ 1 Hz, AlN = 1 V, range = $\pm$ 2.56 V,<br>SF = 52H, chop on                |

|                                                   | 67                         |                |                           | dB                | 50 Hz/60 Hz ± 1 Hz, AIN = 1 V, range = ±2.56 V,<br>SF = 52H, chop off, REJ60 on        |

|                                                   | 100                        |                |                           | dB                | 50 Hz $\pm$ 1 Hz, AIN = 1 V, range = $\pm$ 2.56 V,<br>SF = 52H, chop off               |

| AUXILIARY ADC (ADuC845 Only)                      |                            |                |                           |                   |                                                                                        |

| Conversion Rate                                   | 5.4                        |                | 105                       | Hz                | Chop on                                                                                |

|                                                   | 16.06                      |                | 1365                      | Hz                | Chop off                                                                               |

| No Missing Codes <sup>2</sup>                     | 24                         |                |                           | Bits              | ≤26.7 Hz update rate, chop enabled                                                     |

|                                                   | 24                         |                |                           | Bits              | 80.3 Hz update rate, chop disabled                                                     |

| Resolution                                        | See Table                  | 19 and Table 2 | 21                        |                   |                                                                                        |

| Output Noise                                      | See Table                  | 18 and Table 2 | 20                        |                   | Output noise varies with selected update rates.                                        |

| Integral Nonlinearity                             |                            |                | ±15                       | ppm of FSR        | 1 LSB <sub>16</sub>                                                                    |

| Offset Error <sup>3</sup>                         |                            | ±3             |                           | μV                | Chop on                                                                                |

|                                                   |                            | ±0.25          |                           | LSB <sub>16</sub> | Chop off                                                                               |

| Offset Error Drift <sup>2</sup>                   |                            | 10             |                           | nV/°C             | Chop on                                                                                |

|                                                   |                            | 200            |                           | nV/°C             | Chop off                                                                               |

| Full-Scale Error <sup>₄</sup>                     |                            | ±0.5           |                           | LSB <sub>16</sub> |                                                                                        |

| Gain Error Drift <sup>4</sup>                     |                            | ±0.5           |                           | ppm/°C            |                                                                                        |

| Power Supply Rejection                            | 80                         |                |                           | dB                | AIN = 1 V, range = $\pm 2.56$ V, chop enabled                                          |

|                                                   |                            | 80             |                           | dB                | AIN = 1 V, range = $\pm 2.56$ V, chop disabled                                         |

## **Data Sheet**

# ADuC845/ADuC847/ADuC848

| Parameter                                                     | Min  | Тур  | Max             | Unit   | Test Conditions/Comments                                                      |

|---------------------------------------------------------------|------|------|-----------------|--------|-------------------------------------------------------------------------------|

| TRANSDUCER BURNOUT CURRENT<br>SOURCES                         |      |      |                 |        |                                                                               |

| AIN+ Current                                                  |      | -100 |                 | nA     | AIN+ is the selected positive input (AIN4 or AIN6 only) to the primary ADC    |

| AIN– Current                                                  |      | 100  |                 | nA     | AIN– is the selected negative input (AIN5 or AIN7<br>only) to the primary ADC |

| Initial Tolerance at 25°C                                     |      | ±10  |                 | %      |                                                                               |

| Drift                                                         |      | 0.03 |                 | %/°C   |                                                                               |

| EXCITATION CURRENT SOURCES                                    |      |      |                 |        |                                                                               |

| Output Current                                                |      | 200  |                 | μA     | Available from each current source                                            |

| Initial Tolerance at 25°C                                     |      | ±10  |                 | %      |                                                                               |

| Drift                                                         |      | 200  |                 | ppm/°C |                                                                               |

| Initial Current Matching at 25°C                              |      | ±1   |                 | %      | Matching between both current sources                                         |

| Drift Matching                                                |      | 20   |                 | ppm/°C |                                                                               |

| Line Regulation (AV <sub>DD</sub> )                           |      | 1    |                 | μA/V   | $AV_{DD} = 5 V \pm 5\%$                                                       |

| Load Regulation                                               |      | 0.1  |                 | μA/V   |                                                                               |

| Output Compliance <sup>2</sup>                                | AGND |      | $AV_{DD} - 0.6$ | V      |                                                                               |

| POWER SUPPLY MONITOR (PSM)                                    |      |      |                 |        |                                                                               |

| AV <sub>DD</sub> Trip Point Selection Range                   | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                     |

| AV <sub>DD</sub> Trip Point Accuracy                          |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                       |

|                                                               |      |      | ±4.0            | %      | $T_{MAX} = 125^{\circ}C$                                                      |

| DV <sub>DD</sub> Trip Point Selection Range                   | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                     |

| DV <sub>DD</sub> Trip Point Accuracy                          |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                       |

|                                                               |      |      | ±4.0            | %      | $T_{MAX} = 125^{\circ}C$                                                      |

| CRYSTAL OSCILLATOR (XTAL1 AND XTAL2)                          |      |      |                 |        |                                                                               |

| Logic Inputs, XTAL1 Only <sup>2</sup>                         |      |      |                 |        |                                                                               |

| VINL, Input Low Voltage                                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                               |

| VINH, Input Low Voltage                                       | 3.5  |      |                 | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 2.5  |      |                 | V      | $DV_{DD} = 3 V$                                                               |

| XTAL1 Input Capacitance                                       |      | 18   |                 | pF     |                                                                               |

| XTAL2 Output Capacitance                                      |      | 18   |                 | pF     |                                                                               |

| LOGIC INPUTS                                                  |      |      |                 |        |                                                                               |

| All Inputs Except SCLOCK, RESET,<br>and XTAL1 <sup>2</sup>    |      |      |                 |        |                                                                               |

| VINL, Input Low Voltage                                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                               |

| V <sub>INH</sub> , Input Low Voltage<br>SCLOCK and RESET Only | 2.0  |      |                 | V      |                                                                               |

| (Schmidt Triggered Inputs) <sup>2</sup>                       |      |      |                 |        |                                                                               |

| V <sub>T+</sub>                                               | 1.3  |      | 3.0             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 0.95 |      | 2.5             | V      | $DV_{DD} = 3 V$                                                               |

| V <sub>T-</sub>                                               | 0.8  |      | 1.4             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 0.4  |      | 1.1             | V      | $DV_{DD} = 3 V$                                                               |

| $V_{T+} - V_{T-}$                                             | 0.3  |      | 0.85            | V      | $DV_{DD} = 5 V \text{ or } 3 V$                                               |

| Input Currents                                                |      |      |                 |        |                                                                               |

| Port 0, P1.0 to P1.7, EA                                      |      |      | ±10             | μA     | $V_{\text{IN}}=0 \text{ V or } V_{\text{DD}}$                                 |

| RESET                                                         |      |      | ±10             | μA     | $V_{IN} = 0 V, DV_{DD} = 5 V$                                                 |

|                                                               | 35   |      | 105             | μA     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$ , internal pull-down                        |

| Port 2, Port 3                                                |      |      | ±10             | μΑ     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$                                             |

|                                                               | -180 |      | -660            | μΑ     | $V_{IN} = 2 V, DV_{DD} = 5 V$                                                 |

|                                                               | -20  |      | -75             | μΑ     | $V_{IN} = 0.45 \text{ V}, \text{DV}_{DD} = 5 \text{ V}$                       |

| Input Capacitance                                             |      | 10   | -               | pF     | All digital inputs                                                            |

| n | ิล | ta | 1  | 2 | ŀ | 1  | ρ | ρ | t  |

|---|----|----|----|---|---|----|---|---|----|

| ν | α  | ιc | ι. | U | ł | ł, | U | U | μ. |

| Parameter                                                                          | Min     | Тур | Мах  | Unit   | Test Conditions/Comments                                                                          |

|------------------------------------------------------------------------------------|---------|-----|------|--------|---------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (ALL DIGITAL<br>OUTPUTS EXCEPT XTAL2)                                |         |     |      |        |                                                                                                   |

| V <sub>OH</sub> , Output High Voltage <sup>2</sup>                                 | 2.4     |     |      | V      | $DV_{DD} = 5 V$ , $I_{SOURCE} = 80 \mu A$                                                         |

|                                                                                    | 2.4     |     |      | V      | $DV_{DD} = 3 V$ , $I_{SOURCE} = 20 \mu A$                                                         |

| Vol, Output Low Voltage                                                            |         |     | 0.4  | V      | Isink = 8 mA, SCLOCK, SDATA                                                                       |

| . 2                                                                                |         |     | 0.4  | V      | I <sub>SINK</sub> = 1.6 mA on P0, P1, P2                                                          |

| Floating State Leakage Current <sup>2</sup>                                        |         |     | ±10  | μA     |                                                                                                   |

| Floating State Output Capacitance                                                  |         | 10  |      | pF     |                                                                                                   |

| START-UP TIME                                                                      |         |     |      |        |                                                                                                   |

| At Power-On                                                                        |         | 600 |      | ms     |                                                                                                   |

| After Ext RESET in Normal Mode                                                     |         | 3   |      | ms     |                                                                                                   |

| After WDT RESET in Normal Mode                                                     |         | 2   |      | ms     | Controlled via WDCON SFR                                                                          |

| From Power-Down Mode                                                               |         |     |      |        |                                                                                                   |

| Oscillator Running                                                                 |         |     |      |        | PLLCON.7 = 0                                                                                      |

| Wake-Up with $\frac{2}{100}$ Interrupt                                             |         | 20  |      | μs     |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 20  |      | μs     |                                                                                                   |

| Wake-Up with TIC Interrupt                                                         |         | 20  |      | μs     |                                                                                                   |

| Oscillator Powered Down                                                            |         |     |      | P      | PLLCON.7 = 1                                                                                      |

| Wake-Up with INTO Interrupt                                                        |         | 30  |      | μs     |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 30  |      | μs     |                                                                                                   |

| FLASH/EE MEMORY RELIABILITY<br>CHARACTERISTICS                                     |         |     |      |        |                                                                                                   |

| Endurance <sup>9</sup>                                                             | 100,000 |     |      | Cycles |                                                                                                   |

| Data Retention <sup>10</sup>                                                       | 100,000 |     |      | Years  |                                                                                                   |

| POWER REQUIREMENTS                                                                 |         |     |      |        |                                                                                                   |

| Power Supply Voltages                                                              |         |     |      |        |                                                                                                   |

| AV <sub>DD</sub> 3 V Nominal                                                       | 2.7     |     | 3.6  | v      |                                                                                                   |

| AV <sub>DD</sub> 5 V Nominal                                                       | 4.75    |     | 5.25 | v      |                                                                                                   |

| $DV_{DD}$ 3 V Nominal                                                              | 2.7     |     | 3.6  | v      |                                                                                                   |

| $DV_{DD}$ 5 V Nominal                                                              | 4.75    |     | 5.25 | v      |                                                                                                   |

| 5 V Power Consumption                                                              | 1.7 5   |     | 5.25 | •      | $4.75 \text{ V} < \text{DV}_{\text{DD}} < 5.25 \text{ V}, \text{AV}_{\text{DD}} = 5.25 \text{ V}$ |

| Normal Mode <sup>11, 12</sup>                                                      |         |     |      |        | 4.75 V < D V 00 < 3.25 V, TV 00 = 5.25 V                                                          |

|                                                                                    |         |     | 10   | mA     | Core clock = 1.57 MHz                                                                             |

|                                                                                    |         | 25  | 31   | mA     | Core clock = $12.58$ MHz                                                                          |

| AV <sub>DD</sub> Current                                                           |         | 25  | 180  | μA     |                                                                                                   |

| Power-Down Mode <sup>11, 12</sup>                                                  |         |     |      | P      |                                                                                                   |

| DV <sub>DD</sub> Current                                                           |         | 40  | 53   | μA     | T <sub>MAX</sub> = 85°C; OSC on; TIC on                                                           |

|                                                                                    |         | 50  |      | μΑ     | $T_{MAX} = 125$ °C; OSC on; TIC on                                                                |

|                                                                                    |         | 20  | 33   | μΑ     | $T_{MAX} = 85^{\circ}C; OSC off$                                                                  |

|                                                                                    |         | 30  | 55   | μΑ     | $T_{MAX} = 125$ °C; OSC off                                                                       |

| AV <sub>DD</sub> Current                                                           |         | 50  | 1    | μΑ     | $T_{MAX} = 85^{\circ}C; OSC on or off$                                                            |

|                                                                                    |         |     | 3    | μΑ     | $T_{MAX} = 125$ °C; OSC on or off                                                                 |

| Typical Additional Peripheral<br>Currents (Al <sub>DD</sub> and Dl <sub>DD</sub> ) |         |     | 5    | μπ     | $5 \text{ V V}_{\text{DD}}, \text{CD} = 3$                                                        |

| Primary ADC                                                                        |         | 1   |      | mA     |                                                                                                   |

| Auxiliary ADC (ADuC845 Only)                                                       |         | 0.5 |      | mA     |                                                                                                   |

| Power Supply Monitor                                                               |         | 30  |      | μA     |                                                                                                   |

| DAC                                                                                |         | 60  |      | μΑ     | DACH/L = 000H                                                                                     |

| Dual Excitation Current Sources                                                    |         | 200 |      | μA     | 200 $\mu$ A each. Can be combined to give 400 $\mu$ A on a single output.                         |

| ALE Off                                                                            |         | -20 |      | μA     | PCON.4 = 1 (see Table 6)                                                                          |

| WDT                                                                                |         | 10  |      | μΑ     |                                                                                                   |

| Pin                   | No.                   |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------|------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP               | 56-LFCSP              | Mnemonic               | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9                     | 9                     | P1.4/AIN5              |                   | On power-on default, P1.4/AIN5 is configured as the AIN5 analog input.<br>AIN5 can be used as a pseudo differential input when used with AINCOM or as<br>the positive input of a fully differential pair when used with AIN6.                                                                                                                                                                                                                       |

|                       |                       |                        |                   | P1.0 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                              |

| 10                    | 10                    | P1.5/AIN6              | 1                 | On power-on default, P1.5/AIN6 is configured as the AIN6 analog input.<br>AIN6 can be used as a pseudo differential input when used with AINCOM or as<br>the negative input of a fully differential pair when used with AIN5.                                                                                                                                                                                                                       |

|                       |                       |                        |                   | P1.1 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                              |

| 11                    | 11                    | P1.6/AIN7/IEXC1        | I/O               | On power-on default, P1.6/AIN7 is configured as the AIN7 analog input.                                                                                                                                                                                                                                                                                                                                                                              |

|                       |                       |                        |                   | AIN7 can be used as a pseudo differential input when used with AINCOM or as<br>the positive input of a fully differential pair when used with AIN8. One or both<br>current sources can also be configured at this pin.                                                                                                                                                                                                                              |

|                       |                       |                        |                   | P1.6 has no digital output driver. It can, however, function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                    |

| 12                    | 12                    | P1.7/AIN8/IEXC2        | I/O               | On power-on default, P1.7/AIN8 is configured as the AIN8 analog input.                                                                                                                                                                                                                                                                                                                                                                              |

|                       |                       |                        |                   | AIN8 can be used as a pseudo differential input when used with AINCOM or as<br>the negative input of a fully differential pair when used with AIN7. One or<br>both current sources can also be configured at this pin.                                                                                                                                                                                                                              |

|                       |                       |                        |                   | P1.7 has no digital output driver. It can, however, function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                    |

| 13                    | 13                    | AINCOM/DAC             | I/O               | All analog inputs can be referred to this pin, provided that a relevant pseudo differential input mode is selected. This pin also functions as an alternative pin out for the DAC.                                                                                                                                                                                                                                                                  |

| 14                    | 14                    | DAC                    | 0                 | The voltage output from the DAC, if enabled, appears at this pin.                                                                                                                                                                                                                                                                                                                                                                                   |

| Not<br>applicable     | 15                    | AIN9                   | I                 | AIN9 can be used as a pseudo differential analog input when used with<br>AINCOM or as the positive input of a fully differential pair when used with<br>AIN10 (LFCSP version only).                                                                                                                                                                                                                                                                 |

| Not<br>applicable     | 16                    | AIN10                  | I                 | AIN10 can be used as a pseudo differential analog input when used with<br>AINCOM or as the negative input of a fully differential pair when used with<br>AIN9 (LFCSP version only).                                                                                                                                                                                                                                                                 |

| 15                    | 17                    | RESET                  | I                 | Reset Input. A high level on this pin for 16 core clock cycles while the oscillator is running resets the device. This pin has an internal weak pull-down and a Schmitt trigger input stage.                                                                                                                                                                                                                                                        |

| 16 to 19,<br>22 to 25 | 18 to 21,<br>24 to 27 | P3.0 to P3.7           | I/O               | P3.0 to P3.7 are bidirectional port pins with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. When driving a 0-to-1 output transition, a strong pull-up is active for one core clock period of the instruction cycle. |

| 1.0                   | 10                    |                        |                   | Port 3 pins also have the various secondary functions described in this table.                                                                                                                                                                                                                                                                                                                                                                      |

| 16<br>17              | 18<br>19              | P3.0/RxD<br>P3.1/TxD   |                   | Receiver Data for UART Serial Port.<br>Transmitter Data for UART Serial Port.                                                                                                                                                                                                                                                                                                                                                                       |

| 17<br>18              | 19<br>20              | P3.1/TXD<br>P3.2/INTO  |                   | External Interrupt 0. This pin can also be used as a gate control input to Timer 0.                                                                                                                                                                                                                                                                                                                                                                 |

| 18<br>19              | 20                    | P3.2/INT0<br>P3.3/INT1 |                   | External Interrupt 0. This pin can also be used as a gate control input to Timer 0.<br>External Interrupt 1. This pin can also be used as a gate control input to Timer 1.                                                                                                                                                                                                                                                                          |

| 19<br>22              | 21                    | P3.3/INTT<br>P3.4/T0   |                   | Timer/Counter 0 External Input.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22                    | 24<br>25              | P3.4/10<br>P3.5/T1     |                   | Timer/Counter 0 External Input.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23<br>24              | 25                    | P3.6/WR                |                   | External Data Memory Write Strobe. This pin latches the data byte from Port 0 into an external data memory.                                                                                                                                                                                                                                                                                                                                         |

| 25                    | 27                    | P3.7/RD                |                   | External Data Memory Read Strobe. This pin enables the data from an external data memory to Port 0.                                                                                                                                                                                                                                                                                                                                                 |

| Pin                   | No.                   |              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-----------------------|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP               | 56-LFCSP              | Mnemonic     | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 43 to 46,<br>49 to 52 | 46 to 49,<br>52 to 55 | P0.0 to P0.7 | Ι/Ο               | These pins are part of Port 0, which is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float, and, in that state, can be used as high impedance inputs. An external pull-up resistor is required on P0 outputs to force a valid logic high level externally. Port 0 is also the multiplexed low-order address and data bus during accesses to external data memory. In this application, Port 0 uses strong internal pull-ups when emitting 1s. |

|                       | EP                    | EPAD         |                   | Exposed Pad. For the LFCSP, the exposed paddle must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                              |

$^{1}$  I = input, S = supply, I/O means input/output, and O = output.

### Notes on the ADCMODE Register

Any change to the MD bits immediately resets both ADCs (auxiliary ADC only applicable to the ADuC845). A write to the MD2–MD0 bits with no change in contents is also treated as a reset. (See the exception to this in the third note of this section.)

If ADC1CON1 and ADC1CON2 are written when ADC0EN = 1, or if ADC0EN is changed from 0 to 1, both ADCs are also immediately reset. In other words, the primary ADC is given priority over the auxiliary ADC and any change requested on the primary ADC is immediately responded to. Only applicable to the ADuC845.

On the other hand, if ADC1CON is written to or if ADC1EN is changed from 0 to 1, only the auxiliary ADC is reset. For example, if the primary ADC is continuously converting when the auxiliary ADC change or enable occurs, the primary ADC continues undisturbed. Rather than allow the auxiliary ADC to operate with a phase difference from the primary ADC, the auxiliary ADC falls into step with the outputs of the primary ADC. The result is that the first conversion time for the auxiliary ADC is delayed by up to three outputs while the auxiliary ADC update rate is synchronized to the primary ADC. Only applicable to ADuC845. If the ADC1CON write occurs after the primary ADC has completed its operation, the auxiliary ADC can respond immediately without having to fall into step with the primary ADCs output cycle. If the devices are powered down via the PD bit in the PCON register, the current ADCMODE bits are preserved, that is, they are not reset to default state. Upon a subsequent resumption of normal operating mode, the ADCs restarts the selected operation defined by the ADCMODE register.

Once ADCMODE has been written with a calibration mode, the RDY0/1 (ADuC845 only) bits (ADCSTAT) are reset and the calibration commences. On completion, the appropriate calibration registers are written, the relevant bits in ADCSTAT are written, and the MD2–MD0 bits are reset to 000B to indicate that the ADC is back in power-down mode.

Any calibration request of the auxiliary ADC while the temperature sensor is selected fails to complete. Although the RDY1 bit is set at the end of the calibration cycle, no update of the calibration SFRs takes place, and the ERR1 bit is set. ADuC845 only.

Calibrations performed at maximum SF (see Table 28) value (slowest ADC throughput rate) help to ensure optimum calibration.

The duration of a calibration cycle is 2/Fadc for chop-on mode and 4/Fadc for chop-off mode.

## SF (ADC SINC FILTER CONTROL REGISTER)

The SF register is used to configure the decimation factor for the ADC, and therefore, has a direct influence on the ADC throughput rate.

| SFR Address:      | D4H |

|-------------------|-----|

| Power-On Default: | 45H |

| Bit Addressable:  | No  |

#### Table 28. Sinc Filter SFR Bit Designations

| SF.7 | SF.6 | SF.5 | SF.4 | SF.3 | SF.2 | SF.1 | SF.0 |

|------|------|------|------|------|------|------|------|

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    |

The bits in this register set the decimation factor of the ADC. This has a direct bearing on the throughput rate of the ADC along with the chop setting. The equations used to determine the ADC throughput rate are

Fadc (Chop On) =  $\frac{1}{3 \times 8 \times SFword} \times 32.768 \text{ kHz}$

where SFword is in decimal.

Fadc (Chop Off) =

$$\frac{1}{8 \times SFword} \times 32.768 \text{ kHz}$$

where SFword is in decimal.

#### Table 29. SF SFR Bit Examples Chop Enabled (ADCMODE.3 = 0)

| Chop Enabled (AL |                  |           |           |              |  |  |  |  |  |

|------------------|------------------|-----------|-----------|--------------|--|--|--|--|--|

| SF (Decimal)     | SF (Hexadecimal) | Fadc (Hz) | Tadc (ms) | Tsettle (ms) |  |  |  |  |  |

| 13 <sup>1</sup>  | 0D               | 105.3     | 9.52      | 19.04        |  |  |  |  |  |

| 69               | 45               | 19.79     | 50.53     | 101.1        |  |  |  |  |  |

| 82               | 52               | 16.65     | 60.06     | 120.1        |  |  |  |  |  |

| 255              | FF               | 5.35      | 186.77    | 373.54       |  |  |  |  |  |

#### Chop Disabled (ADCMODE.3 = 1)

| SF (Decimal) | SF (Hexadecimal) | Fadc (Hz) | Tadc (ms) | Tsettle (ms) |

|--------------|------------------|-----------|-----------|--------------|

| 3            | 03               | 1365.3    | 0.73      | 2.2          |

| 69           | 45               | 59.36     | 16.84     | 50.52        |

| 82           | 52               | 49.95     | 20.02     | 60.06        |

| 255          | FF               | 16.06     | 62.25     | 186.8        |

<sup>1</sup> With chop enabled, if an SF word smaller than 13 is written to this SF register, the filter automatically defaults to 13.

During ADC calibration, the user-programmed value of SF word is used. The SF word does not default to the maximum setting (255) as it did on previous MicroConverter<sup>®</sup> products. However, for optimum calibration results, it is recommended that the maximum SF word be set.

## ICON (EXCITATION CURRENT SOURCES CONTROL REGISTER)

The ICON register is used to configure the current sources and the burnout detection source.

| SFR Address:      | D5H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

#### Table 30. Excitation Current Source SFR Bit Designations

| Bit No. | Name   | Description                                                                                                                                                                                     |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       |        | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 6       | ICON.6 | Burnout Current Enable Bit.                                                                                                                                                                     |

|         |        | When set, this bit enables the sensor burnout current sources on primary ADC channels AIN5/AIN6 or AIN7/AIN8. Not available on any other ADC input pins or on the auxiliary ADC (ADuC845 only). |

| 5       | ICON.5 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 4       | ICON.4 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 3       | ICON.3 | IEXC2 Pin Select. 0 selects AIN8, 1 selects AIN7                                                                                                                                                |

| 2       | ICON.2 | IEXC1 Pin Select. 0 selects AIN7, 1 selects AIN8                                                                                                                                                |

| 1       | ICON.1 | IEXC2 Enable Bit (0 = disable).                                                                                                                                                                 |

| 0       | ICON.0 | IEXC1 Enable Bit (0 = disable).                                                                                                                                                                 |

A write to the ICON register has an immediate effect but does not reset the ADCs. Therefore, if a current source is changed while an ADC is already converting, the user must wait until the third or fourth output at least (depending on the status of the chop mode) to see a fully settled new output.

Both IEXC1 and IEXC2 can be configured to operate on the same output pin thereby increasing the current source capability to 400 µA.

## NONVOLATILE FLASH/EE MEMORY OVERVIEW

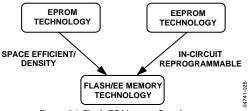

The ADuC845/ADuC847/ADuC848 incorporate Flash/EE memory technology on-chip to provide the user with nonvolatile, in-circuit reprogrammable code and data memory space.

Like EEPROM, flash memory can be programmed in-system at the byte level, although it must first be erased, in page blocks. Thus, flash memory is often and more correctly referred to as Flash/EE memory.

Figure 26. Flash/EE Memory Development

Overall, Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. The Flash/EE memory technology allows the user to update program code space incircuit, without needing to replace onetime programmable (OTP) devices at remote operating nodes.

### Flash/EE Memory on the ADuC845, ADuC847, ADuC848

The ADuC845/ADuC847/ADuC848 provide two arrays of Flash/EE memory for user applications—up to 62 kbytes of Flash/EE program space and 4 kbytes of Flash/EE data memory space. Also, 8-kbyte and 32-kbyte program memory options are available. All examples and references in this datasheet use the 62-kbyte option; however, similar protocols and procedures are applicable to the 32-kbyte and 8-kbyte options unless otherwise noted, provided that the difference in memory size is taken into account.

The 62 kbytes Flash/EE code space are provided on-chip to facilitate code execution without any external discrete ROM device requirements. The program memory can be programmed in-circuit, using the serial download mode provided, using conventional third party memory programmers, or via any user-defined protocol in user download (ULOAD) mode.

The 4-kbyte Flash/EE data memory space can be used as a general-purpose, nonvolatile scratchpad area. User access to this area is via a group of seven SFRs. This space can be programmed at a byte level, although it must first be erased in 4-byte pages.

All the following sections use the 62-kbyte program space as an example when referring to program and ULOAD mode. For the 64-kbyte part, the ULOAD area takes up the top 6 kbytes of the program space, that is, from 56 kbytes to 62 kbytes. For the 32-kbyte part, the ULOAD space moves to the top 8 kbytes of the on-chip program memory, that is., from 24 kbytes to 32 kbytes.

No ULOAD mode is available on the 8-kbyte part since the bootload area on the 8-kbyte part is 8 kbytes long, so no usable user program space remains. The kernel still resides in the protected area from 62 kbytes to 64 kbytes.

### Flash/EE Memory Reliability

The Flash/EE program and data memory arrays on the ADuC845/ADuC847/ADuC848 are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. In real terms, a single endurance cycle is composed of four independent, sequential events:

- 1. Initial page erase sequence

- 2. Read/verify sequence

- 3. Byte program sequence

- 4. Second read/verify sequence

In reliability qualification, every byte in both the program and data Flash/EE memory is cycled from 00H to FFH until a first fail is recorded, signifying the endurance limit of the on-chip Flash/EE memory.

As indicated in the Specifications table, the ADuC845/ADuC847/ ADuC848 Flash/EE memory endurance qualification has been carried out in accordance with JEDEC Specification A117 over the industrial temperature range of – 40°C, +25°C, +85°C, and +125°C. (The LFCSP package is qualified to +85°C only.) The results allow the specification of a minimum endurance figure over supply and temperature of 100,000 cycles, with an endurance figure of 700,000 cycles being typical of operation at 25°C.

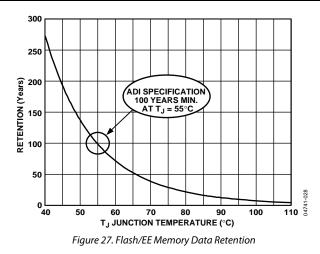

Retention is the ability of the Flash/EE memory to retain its programmed data over time. Again, the devices have been qualified in accordance with the formal JEDEC Retention Lifetime Specification (A117) at a specific junction temperature ( $T_1 = 55^{\circ}$ C). As part of this qualification procedure, the Flash/EE memory is cycled to its specified endurance limit described previously, before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its full specified retention lifetime every time the Flash/EE memory is reprogrammed. It should also be noted that retention lifetime, based on an activation energy of 0.6 eV, derates with  $T_1$  as shown in Figure 27.

## FLASH/EE PROGRAM MEMORY

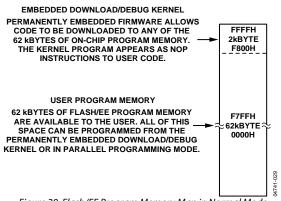

The ADuC845/ADuC847/ADuC848 contain a 64-kbyte array of Flash/EE program memory. The lower 62 kbytes of this program memory are available to the user for program storage or as additional NV data memory.

The upper 2 kbytes of this Flash/EE program memory array contain permanently embedded firmware, allowing in-circuit serial download, serial debug, and nonintrusive single-pin emulation. These 2 kbytes of embedded firmware also contain a power-on configuration routine that downloads factory calibrated coefficients to the various calibrated peripherals such as ADC, temperature sensor, current sources, band gap, and references.

These 2 kbytes of embedded firmware are hidden from the user code. Attempts to read this space read 0s; therefore, the embedded firmware appears as NOP instructions to user code.

In normal operating mode (power-on default), the 62 kbytes of user Flash/EE program memory appear as a single block. This block is used to store the user code as shown in Figure 28.

Figure 28. Flash/EE Program Memory Map in Normal Mode

In normal mode, the 62 kbytes of Flash/EE program memory can be programmed by serial downloading and by parallel programming.

## ADuC845/ADuC847/ADuC848

#### Serial Downloading (In-Circuit Programming)

The ADuC845/ADuC847/ADuC848 facilitate code download via the standard UART serial port. The devices enter serial download mode after a reset or a power cycle if the  $\overline{\text{PSEN}}$  pin is pulled low through an external 1 k $\Omega$  resistor. Once in serial download mode, the hidden embedded download kernel executes. This allows the user to download code to the full 62 kbytes of Flash/EE program memory while the device is in circuit in its target application hardware.

A PC serial download executable (WSD.EXE) is provided as part of the ADuC845/ADuC847/ADuC848 Quick Start development system. The AN-1074 Application Note fully describes the serial download protocol that is used by the embedded download kernel.

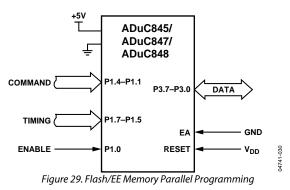

#### Parallel Programming

The parallel programming mode is fully compatible with conventional third-party flash or EEPROM device programmers. A block diagram of the external pin configuration required to support parallel programming is shown in Figure 29. In this mode, Ports 0 and 2 operate as the external address bus interface, P3 operates as the external data bus interface, and P1.0 operates as the write enable strobe. P1.1, P1.2, P1.3, and P1.4 are used as general configuration ports that configure the device for various program and erase operations during parallel programming.

The command words that are assigned to P1.1, P1.2, P1.3, and P1.4 are described in Table 31.

|         | Port     | 1 Pins |      |                                                 |

|---------|----------|--------|------|-------------------------------------------------|

| P1.4    | P1.3     | P1.2   | P1.1 | Programming Mode                                |

| 0       | 0        | 0      | 0    | Erase Flash/EE Program, Data, and Security Mode |

| 1       | 0        | 1      | 0    | Program Code Byte                               |

| 0       | 0        | 1      | 0    | Program Data Byte                               |

| 1       | 0        | 1      | 1    | Read Code Byte                                  |

| 0       | 0        | 1      | 1    | Read Data Byte                                  |

| 1       | 1        | 0      | 0    | Program Security Modes                          |

| 1       | 1        | 0      | 1    | Read/Verify Security Modes                      |

| All oth | ner code | 25     |      | Redundant                                       |

## USING FLASH/EE DATA MEMORY

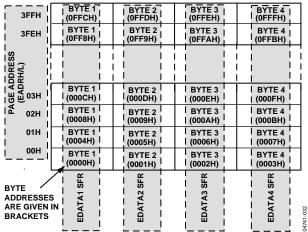

The 4 kbytes of Flash/EE data memory are configured as 1024 pages, each of 4 bytes. As with the other ADuC845/ADuC847/ ADuC848 peripherals, the interface to this memory space is via a group of registers mapped in the SFR space. A group of four data registers (EDATA1–4) holds the 4 bytes of data at each page. The page is addressed via the EADRH and EADRL registers. Finally, ECON is an 8-bit control register that can be written to with one of nine Flash/EE memory access commands to trigger various read, write, erase, and verify functions. A block diagram of the SFR interface to the Flash/EE data memory array is shown in Figure 32.

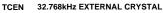

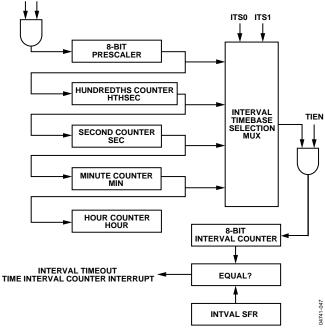

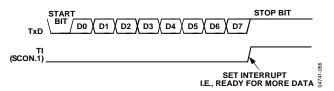

#### ECON—Flash/EE Memory Control SFR