## Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | 8052                                                                |

| Core Size                  | 8-Bit                                                               |

| Speed                      | 12.58MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 34                                                                  |

| Program Memory Size        | 62KB (62K x 8)                                                      |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | 4K x 8                                                              |

| RAM Size                   | 2.25K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                       |

| Data Converters            | A/D 10x24b; D/A 1x12b, 2x16b                                        |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                           |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc847bcpz62-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Revision History                             |

| Specifications                               |

| Abosolute Maximum Ratings 10                 |

| ESD Caution10                                |

| Pin Configurations and Function Descriptions |

| General Description                          |

| 8052 Instruction Set                         |

| Timer Operation                              |

| ALE                                          |

| External Memory Access                       |

| Complete SFR Map19                           |

| Functional Description                       |

| 8051 Instruction Set 20                      |

| Memory Organization                          |

| Special Function Registers (SFRs)            |

| ADC Circuit Information26                    |

| Auxiliary ADC (ADuC845 Only)                 |

| Reference Inputs                             |

| Burnout Current Sources                      |

| Reference Detect Circuit                     |

| Sinc Filter Register (SF)                    |

| $\Sigma$ - $\Delta$ Modulator                |

| Digital Filter                               |

| ADC Chopping                                 |

| Calibration                                  |

| Programmable Gain Amplifier                  |

| Bipolar/Unipolar Configuration35             |

| Data Output Coding                           |

| Excitation Currents                          |

|   | ADC Power-On                                       |

|---|----------------------------------------------------|

| Т | ypical Performance Characteristics                 |

| F | unctional Description                              |

|   | ADC SFR Interface                                  |

|   | ADCSTAT (ADC Status Register) 40                   |

|   | ADCMODE (ADC Mode Register)                        |

|   | ADC0CON1 (Primary ADC Control Register) 43         |

|   | ADC0CON2 (Primary ADC Channel Select Register) 44  |

|   | SF (ADC Sinc Filter Control Register) 46           |

|   | ICON (Excitation Current Sources Control Register) |

|   | Nonvolatile Flash/EE Memory Overview               |

|   | Flash/EE Program Memory 49                         |

|   | User Download Mode (ULOAD) 50                      |

|   | Using Flash/EE Data Memory51                       |

|   | Flash/EE Memory Timing                             |

|   | DAC Circuit Information                            |

|   | Pulse-Width Modulator (PWM)55                      |

|   | On-Chip PLL (PLLCON)                               |

|   | I <sup>2</sup> C Serial Interface                  |

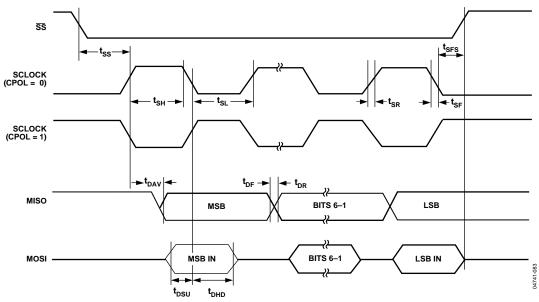

|   | SPI Serial Interface                               |

|   | Using the SPI Interface                            |

|   | Dual Data Pointers                                 |

|   | Power Supply Monitor                               |

|   | Watchdog Timer                                     |

|   | Time Interval Counter (TIC)                        |

|   | 8052-Compatible On-Chip Peripherals                |

|   | Timers/Counters                                    |

|   | UART Serial Interface                              |

|   | Interrupt System                                   |

|   | Interrupt Priority                                 |

|   | Interrupt Vectors                                  |

## **Data Sheet**

| H | Iardware Design Considerations             | .89 |

|---|--------------------------------------------|-----|

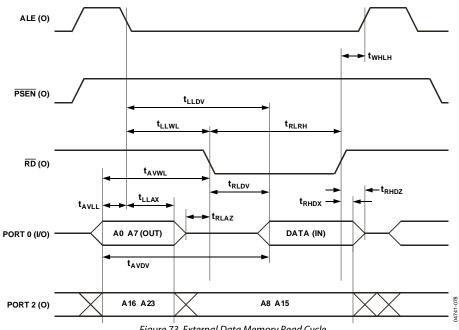

|   | External Memory Interface                  | .89 |

|   | Power Supplies                             | .89 |

|   | Power-On Reset Operation                   | .90 |

|   | Power Consumption                          | .90 |

|   | Power-Saving Modes                         | .90 |

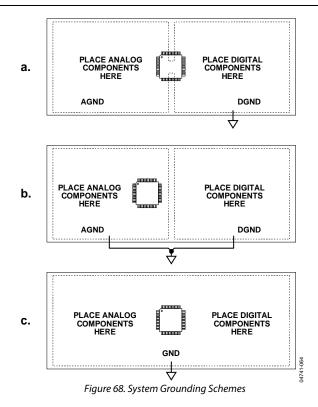

|   | Grounding and Board Layout Recommendations | .91 |

## **REVISION HISTORY**

### 5/2016—Rev. C to Rev. D

| Changed uC004 to AN-1074   | . Throughout |

|----------------------------|--------------|

| Updated Outline Dimensions |              |

| Changes to Ordering Guide  |              |

#### 12/2012-Rev. B to Rev. C

| Changes to Figure 3 and Table 3                                     | 11  |

|---------------------------------------------------------------------|-----|

| Changes to Burnout Current Sources Section                          | 32  |

| Change to ADCMODE (ADC Mode Register) Section                       | 42  |

| Changes to Mode 4 (Dual NRZ 16-Bit $\Sigma$ - $\Delta$ DAC) Section | 58  |

| Change to Hardware Slave Mode Section                               | 63  |

| Updated Outline Dimensions                                          | 104 |

| Changes to Ordering Guide                                           |     |

|                                                                     |     |

## 2/2005—Rev. A to Rev. B

| Changes to Figure 1                                     | 1  |

|---------------------------------------------------------|----|

| Changes to the Burnout Current Sources Section          | 32 |

| Changes to the Excitation Currents Section              | 36 |

| Changes to Table 30                                     | 47 |

| Changes to the Flash/EE Memory on the ADuC845, ADuC847, |    |

| ADuC848 Section                                         | 48 |

| Changes to Figure 39                                    | 57 |

| Changes to On-Chip PLL (PLLCON) Section                 | 60 |

| Added 3 V Part Section Heading                          | 88 |

| Added 5 V Part Section                                  | 88 |

| Changes to Figure 70                                    | 91 |

| Changes to Figure 71                                    | 93 |

|                                                         |    |

# ADuC845/ADuC847/ADuC848

| Other Hardware Considerations      |    |

|------------------------------------|----|

| QuickStart Development System      | 96 |

| QuickStart-PLUS Development System | 96 |

|                                    |    |

| Timing Specifications              | 97 |

| Timing Specifications              |    |

## 6/2004—Rev. 0 to Rev. A

| Changes to Figure 517                                   |

|---------------------------------------------------------|

| Changes to Figure 6                                     |

| Changes to Figure 719                                   |

| Changes to Table 5                                      |

| Changes to Table 24                                     |

| Changes to Table 25                                     |

| Changes to Table 26                                     |

| Changes to Table 27                                     |

| Changes to User Download Mode Section                   |

| Added Figure 51 and Renumbered Subsequent Figures       |

| Edits to the DACH/DACL Data Registers Section           |

| Changes to Table 34                                     |

| Added SPIDAT: SPI Data Register Section                 |

| Changes to Table 42                                     |

| Changes to Table 43                                     |

| Changes to Table 44                                     |

| Changes to Table 45                                     |

| Changes to Table 50                                     |

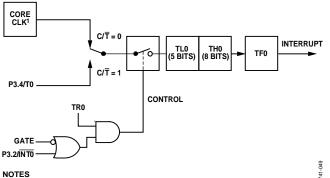

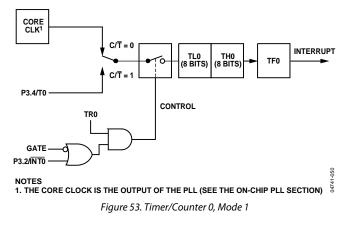

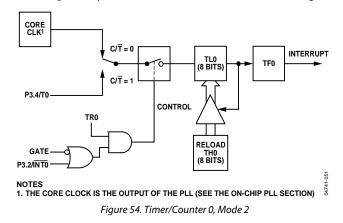

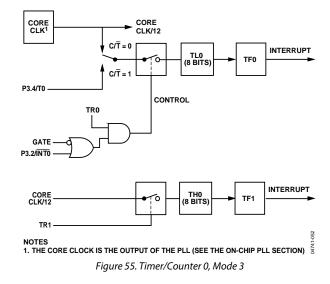

| Changes to Timer/Counter 0 and 1 Data Registers Section |

| Changes to Table 54                                     |

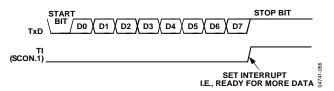

| Added the SBUF—UART Serial Port Data Register Section80 |

| Addition to the Timer 3 Generated Baud Rates Section    |

| Added Table 57 and Renumbered Subsequent Tables         |

| Changes to Table 61                                     |

|                                                         |

4/2004—Revision 0: Initial Version

| n | ิล | ta | 1  | 2 | ŀ | 1  | ρ | ρ | t  |

|---|----|----|----|---|---|----|---|---|----|

| ν | α  | LC | ι. | U | ł | ł, | U | U | μ. |

| Parameter                                                                          | Min     | Тур | Мах  | Unit   | Test Conditions/Comments                                                                          |

|------------------------------------------------------------------------------------|---------|-----|------|--------|---------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (ALL DIGITAL<br>OUTPUTS EXCEPT XTAL2)                                |         |     |      |        |                                                                                                   |

| V <sub>OH</sub> , Output High Voltage <sup>2</sup>                                 | 2.4     |     |      | V      | $DV_{DD} = 5 V$ , $I_{SOURCE} = 80 \mu A$                                                         |

|                                                                                    | 2.4     |     |      | V      | $DV_{DD} = 3 V$ , $I_{SOURCE} = 20 \mu A$                                                         |

| Vol, Output Low Voltage                                                            |         |     | 0.4  | V      | Isink = 8 mA, SCLOCK, SDATA                                                                       |

| . 2                                                                                |         |     | 0.4  | V      | I <sub>SINK</sub> = 1.6 mA on P0, P1, P2                                                          |

| Floating State Leakage Current <sup>2</sup>                                        |         |     | ±10  | μA     |                                                                                                   |

| Floating State Output Capacitance                                                  |         | 10  |      | pF     |                                                                                                   |

| START-UP TIME                                                                      |         |     |      |        |                                                                                                   |

| At Power-On                                                                        |         | 600 |      | ms     |                                                                                                   |

| After Ext RESET in Normal Mode                                                     |         | 3   |      | ms     |                                                                                                   |

| After WDT RESET in Normal Mode                                                     |         | 2   |      | ms     | Controlled via WDCON SFR                                                                          |

| From Power-Down Mode                                                               |         |     |      |        |                                                                                                   |

| Oscillator Running                                                                 |         |     |      |        | PLLCON.7 = 0                                                                                      |

| Wake-Up with $\frac{2}{100}$ Interrupt                                             |         | 20  |      | μs     |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 20  |      | μs     |                                                                                                   |

| Wake-Up with TIC Interrupt                                                         |         | 20  |      | μs     |                                                                                                   |

| Oscillator Powered Down                                                            |         |     |      | P      | PLLCON.7 = 1                                                                                      |

| Wake-Up with INTO Interrupt                                                        |         | 30  |      | μs     |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 30  |      | μs     |                                                                                                   |

| FLASH/EE MEMORY RELIABILITY<br>CHARACTERISTICS                                     |         |     |      |        |                                                                                                   |

| Endurance <sup>9</sup>                                                             | 100,000 |     |      | Cycles |                                                                                                   |

| Data Retention <sup>10</sup>                                                       | 100,000 |     |      | Years  |                                                                                                   |

| POWER REQUIREMENTS                                                                 |         |     |      |        |                                                                                                   |

| Power Supply Voltages                                                              |         |     |      |        |                                                                                                   |

| AV <sub>DD</sub> 3 V Nominal                                                       | 2.7     |     | 3.6  | v      |                                                                                                   |

| AV <sub>DD</sub> 5 V Nominal                                                       | 4.75    |     | 5.25 | v      |                                                                                                   |

| $DV_{DD}$ 3 V Nominal                                                              | 2.7     |     | 3.6  | v      |                                                                                                   |

| $DV_{DD}$ 5 V Nominal                                                              | 4.75    |     | 5.25 | v      |                                                                                                   |

| 5 V Power Consumption                                                              | 1.7 5   |     | 5.25 | •      | $4.75 \text{ V} < \text{DV}_{\text{DD}} < 5.25 \text{ V}, \text{AV}_{\text{DD}} = 5.25 \text{ V}$ |

| Normal Mode <sup>11, 12</sup>                                                      |         |     |      |        | 4.75 V < D V 00 < 3.25 V, TV 00 = 5.25 V                                                          |

|                                                                                    |         |     | 10   | mA     | Core clock = 1.57 MHz                                                                             |

|                                                                                    |         | 25  | 31   | mA     | Core clock = $12.58$ MHz                                                                          |

| AV <sub>DD</sub> Current                                                           |         | 25  | 180  | μA     |                                                                                                   |

| Power-Down Mode <sup>11, 12</sup>                                                  |         |     |      | P      |                                                                                                   |

| DV <sub>DD</sub> Current                                                           |         | 40  | 53   | μA     | T <sub>MAX</sub> = 85°C; OSC on; TIC on                                                           |

|                                                                                    |         | 50  |      | μΑ     | $T_{MAX} = 125$ °C; OSC on; TIC on                                                                |

|                                                                                    |         | 20  | 33   | μΑ     | $T_{MAX} = 85^{\circ}C; OSC off$                                                                  |

|                                                                                    |         | 30  | 55   | μΑ     | $T_{MAX} = 125$ °C; OSC off                                                                       |

| AV <sub>DD</sub> Current                                                           |         | 50  | 1    | μΑ     | $T_{MAX} = 85^{\circ}C; OSC on or off$                                                            |

|                                                                                    |         |     | 3    | μΑ     | $T_{MAX} = 125$ °C; OSC on or off                                                                 |

| Typical Additional Peripheral<br>Currents (Al <sub>DD</sub> and Dl <sub>DD</sub> ) |         |     | 5    | μπ     | $5 \text{ V V}_{\text{DD}}, \text{CD} = 3$                                                        |

| Primary ADC                                                                        |         | 1   |      | mA     |                                                                                                   |

| Auxiliary ADC (ADuC845 Only)                                                       |         | 0.5 |      | mA     |                                                                                                   |

| Power Supply Monitor                                                               |         | 30  |      | μΑ     |                                                                                                   |

| DAC                                                                                |         | 60  |      | μΑ     | DACH/L = 000H                                                                                     |

| Dual Excitation Current Sources                                                    |         | 200 |      | μA     | 200 $\mu$ A each. Can be combined to give 400 $\mu$ A on a single output.                         |

| ALE Off                                                                            |         | -20 |      | μA     | PCON.4 = 1 (see Table 6)                                                                          |

| WDT                                                                                |         | 10  |      | μΑ     |                                                                                                   |

## **Data Sheet**

## ADuC845/ADuC847/ADuC848

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments                                                                       |

|-----------------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------|

| PWM                               |     |     |     |      |                                                                                                |

| –Fxtal                            |     | 3   |     | μA   |                                                                                                |

| –Fvco                             |     | 0.5 |     | mA   |                                                                                                |

| TIC                               |     | 1   |     | μA   |                                                                                                |

| 3 V Power Consumption             |     |     |     |      | $2.7 \text{ V} < \text{DV}_{\text{DD}} < 3.6 \text{ V}, \text{AV}_{\text{DD}} = 3.6 \text{ V}$ |

| Normal Mode <sup>11, 12</sup>     |     |     |     |      |                                                                                                |

| DV <sub>DD</sub> Current          |     |     | 4.8 | mA   | Core clock = 1.57 MHz                                                                          |

|                                   |     | 9   | 11  | mA   | Core clock = $6.29$ MHz (CD = 1)                                                               |

| AV <sub>DD</sub> Current          |     |     | 180 | μA   | ADC not enabled                                                                                |

| Power-Down Mode <sup>11, 12</sup> |     |     |     |      |                                                                                                |

| DV <sub>DD</sub> Current          |     | 20  | 26  | μA   | T <sub>MAX</sub> = 85°C; OSC on; TIC on                                                        |

|                                   |     | 29  |     | μA   | T <sub>MAX</sub> = 125°C; OSC on; TIC on                                                       |

|                                   |     | 14  | 20  | μA   | T <sub>MAX</sub> = 85°C; OSC off                                                               |

|                                   |     | 21  |     | μA   | $T_{MAX} = 125^{\circ}C; OSC off$                                                              |

| AV <sub>DD</sub> Current          |     |     | 1   | μA   | $T_{MAX} = 85^{\circ}C$ ; OSC on or off                                                        |

|                                   |     |     | 3   | μA   | $T_{MAX} = 125^{\circ}C$ ; OSC on or off                                                       |

<sup>1</sup> Temperature range is for ADuC845BS; for the ADuC847BS and ADuC848BS (MQFP package), the range is –40°C to +125°C. Temperature range for ADuC845BCP, ADuC847BCP, and ADuC848BCP (LFCSP package) is –40°C to +85°C.

<sup>2</sup> These numbers are not production tested but are guaranteed by design and/or characterization data on production release.

<sup>3</sup> System zero-scale calibration can remove this error.

<sup>4</sup> Gain error drift is a span drift. To calculate full-scale error drift, add the offset error drift to the gain error drift times the full-scale input.

<sup>5</sup> In general terms, the bipolar input voltage range to the primary ADC is given by the ADC range =  $\pm (V_{REF} 2^{RN})/1.25$ , where:

$V_{REF} = REFIN(+)$  to REFIN(-) voltage and  $V_{REF} = 1.25$  V when internal ADC  $V_{REF}$  is selected. RN = decimal equivalent of RN2, RN1, RN0. For example, if  $V_{REF} = 2.5$  V and RN2, RN1, RN0 = 1, 1, 0, respectively, then the ADC range = ±1.28 V. In unipolar mode, the effective range is 0 V to 1.28 V in this example.

<sup>6</sup> 1.25 V is used as the reference voltage to the ADC when internal V<sub>REF</sub> is selected via XREF0/XREF1 or AXREF bits in ADC0CON2 and ADC1CON, respectively. (AXREF is available only on the ADuC845.)

<sup>7</sup> In bipolar mode, the auxiliary ADC can be driven only to a minimum of AGND – 30 mV as indicated by the auxiliary ADC absolute AIN voltage limits. The bipolar range is still – V<sub>REF</sub> to +V<sub>REF</sub>.

<sup>8</sup> DAC linearity and ac specifications are calculated using a reduced code range of 48 to 4095, 0 V to V<sub>REF</sub>, reduced code range of 100 to 3950, 0 V to V<sub>DD</sub>.

<sup>9</sup> Endurance is qualified to 100 kcycle per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, +85°C, and +125°C. Typical endurance at 25°C is 700 kcycles.

<sup>10</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature.

<sup>11</sup> Power supply current consumption is measured in normal mode following the power-on sequence, and in power-down modes under the following conditions: Normal mode: reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, core executing internal software loop. Power-down mode: reset = 0.4 V, all P0 pins and P1.2 to P1.7 pins = 0.4 V. All other digital I/O pins are open circuit, core Clk changed via CD bits in PLLCON, PCON.1 = 1, core

execution suspended in power-down mode, OSC turned on or off via OSC\_PD bit (PLLCON.7) in PLLCON SFR.

<sup>12</sup> DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

#### **General Notes about Specifications**

- DAC gain error is a measure of the span error of the DAC.

- The ADuC845BCP, ADuC847BCP, and ADuC848BCP (LFCSP package) have been qualified and tested with the base of the LFCSP package floating. The base of the LFCSP package should be soldered to the board, but left floating electrically, to ensure good mechanical stability.

- Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and Flash/EE data memory.

## ADC CIRCUIT INFORMATION

The ADuC845 incorporates two 10-channel (8-channel on the MQFP package) 24-bit  $\Sigma$ - $\Delta$  ADCs, while the ADuC847 and ADuC848 each incorporate a single 10-channel (8-channel on the MQFP package) 24-bit and 16-bit  $\Sigma$ - $\Delta$  ADC.

Each device also includes an on-chip programmable gain amplifier and configurable buffering (neither is available on the auxiliary ADC on the ADuC845). The devices also incorporate digital filtering intended for measuring wide dynamic range and low frequency signals such as those in weigh-scale, strain-gage, pressure transducer, or temperature measurement applications.

The ADuC845/ADuC847/ADuC848 can be configured as four or five (MQFP/LFCSP package) fully-differential input channels or as eight or ten (MQFP/LFCSP package) pseudo differential input channels referenced to AINCOM. The ADC on each device (primary only on the ADuC845) can be fully buffered internally, and can be programmed for one of eight input ranges from  $\pm 20$  mV to  $\pm 2.56$  V (V<sub>REF</sub> × 1.024). Buffering the input channel means that the device can handle significant source impedances on the selected analog input and that RC filtering (for noise rejection or RFI reduction) can be placed on the analog inputs. If the ADC is used with internal buffering disabled (ADC0CON1.7 = 1, ADC0CON1.6 = 0), these unbuffered inputs provide a dynamic load to the driving source. Therefore, resistor/capacitor combinations on the inputs can cause dc gain errors, depending on the output impedance of the source that is driving the ADC inputs.

Table 8 and Table 9 show the allowable external resistance/ capacitance values for unbuffered mode such that no gain error at the 16-bit and 20-bit levels, respectively, is introduced. When used with internal buffering enabled, it is recommended that a capacitor (10 nF to 100 nF) be placed on the input to the ADC (usually as part of an antialiasing filter) to aid in noise performance.

The input channels are intended to convert signals directly from sensors without the need for external signal conditioning. With internal buffering disabled (relevant bits set/cleared in ADC0CON1), external buffering might be required.

When the internal buffer is enabled, it might be necessary to offset the negative input channel by +100 mV and to offset the positive channel by -100 mV if the reference range is AV<sub>DD</sub>. This accounts for the restricted common-mode input range in the buffer. Some circuits, for example, bridge circuits, are inherently suitable to use without having to offset where the output voltage is balanced around V<sub>REF</sub>/2 and is not sufficiently large to encroach on the supply rails. Internal buffering is not available on the auxiliary ADC (ADuC845 only). The auxiliary ADC (ADuC845 only) is fixed at a gain range of ±2.50 V.

The ADCs use a  $\Sigma$ - $\Delta$  conversion technique to realize up to 24 bits on the ADuC845 and the ADuC847, and up to 16 bits on the ADuC848 of no missing codes performance (20 Hz update rate, chop enabled). The  $\Sigma$ - $\Delta$  modulator converts the sampled input signal into a digital pulse train whose duty cycle contains the digital information. A sinc<sup>3</sup> programmable low-pass filter (see Table 28) is then used to decimate the modulator output data stream to give a valid data conversion result at programmable output rates. The signal chain has two modes of operation, chop enabled and chop disabled. The CHOP bit in the ADCMODE register enables or disables the chopping scheme.

#### Table 8. Maximum Resistance for No 16-Bit Gain Error (Unbuffered Mode)

|       | External Capacitance |         |         |        |         |         |  |  |  |  |

|-------|----------------------|---------|---------|--------|---------|---------|--|--|--|--|

| Gain  | 0 pF                 | 50 pF   | 100 pF  | 500 pF | 1000 pF | 5000 pF |  |  |  |  |

| 1     | 111.3 kΩ             | 27.8 kΩ | 16.7 kΩ | 4.5 kΩ | 2.58 kΩ | 700 Ω   |  |  |  |  |

| 2     | 53.7 kΩ              | 13.5 kΩ | 8.1 kΩ  | 2.2 kΩ | 1.26 kΩ | 360 Ω   |  |  |  |  |

| 4     | 25.4 kΩ              | 6.4 kΩ  | 3.9 kΩ  | 1.0 kΩ | 600 Ω   | 170 Ω   |  |  |  |  |

| 8–128 | 10.7 kΩ              | 2.9 kΩ  | 1.7 kΩ  | 480 Ω  | 270 Ω   | 75 Ω    |  |  |  |  |

#### Table 9. Maximum Resistance for No 20-Bit Gain Error (Unbuffered Mode)

|       | External Capacitance |         |         |        |         |         |  |  |  |  |  |

|-------|----------------------|---------|---------|--------|---------|---------|--|--|--|--|--|

| Gain  | 0 pF                 | 50 pF   | 100 pF  | 500 pF | 1000 pF | 5000 pF |  |  |  |  |  |

| 1     | 84.9 kΩ              | 21.1 kΩ | 12.5 kΩ | 3.2 kΩ | 1.77 kΩ | 440 Ω   |  |  |  |  |  |

| 2     | 42.0 kΩ              | 10.4 kΩ | 6.1 kΩ  | 1.6 kΩ | 880 Ω   | 220 Ω   |  |  |  |  |  |

| 4     | 20.5 kΩ              | 5.0 kΩ  | 2.9 kΩ  | 790 Ω  | 430 Ω   | 110 Ω   |  |  |  |  |  |

| 8–128 | 8.8 kΩ               | 2.3 k Ω | 1.3 k Ω | 370 Ω  | 195 Ω   | 50 Ω    |  |  |  |  |  |

### ADC Noise Performance with Chop Disabled ( $\overline{CHOP} = 1$ )

Table 14 through Table 17 show the output rms noise and output peak-to-peak resolution in bits (rounded to the nearest 0.5 LSB) for some typical output update rates. The numbers are typical and are generated at a differential input voltage of 0 V and a common-mode voltage of 2.5 V. The output update rate is selected via the SF7 to SF0 bits in the SF filter register. Note that the peak-to-peak resolution figures represent the resolution for which there is no code flicker within a 6-sigma limit.

The output noise comes from two sources. The first source is the electrical noise in the semiconductor devices (device noise) used in the implementation of the modulator. The second source is quantization noise, which is added when the analog input is converted to the digital domain. The device noise is at a low level and is independent of frequency. The quantization noise starts at an even lower level but rises rapidly with increasing frequency to become the dominant noise source.

The numbers in the tables are given for the bipolar input ranges. For the unipolar ranges, the rms noise numbers are the same as the bipolar range, but the peak-to-peak resolution is based on half the signal range, which effectively means losing 1 bit of resolution. Typically, the performance of the ADC with chop disabled shows a 0.5 LSB degradation over the performance with chop enabled.

| Table 14. ADuC845 and ADuC847 | ' Typical Output RMS Noise ( | (µV) vs. Input Range and | Update Rate with Chop Disabled |

|-------------------------------|------------------------------|--------------------------|--------------------------------|

|                               |                              |                          |                                |

|         | Data Update Input Range |        |        |        |         |         |         |         |         |

|---------|-------------------------|--------|--------|--------|---------|---------|---------|---------|---------|

| SF Word | Rate (Hz)               | ±20 mV | ±40 mV | ±80 mV | ±160 mV | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |

| 3       | 1365.33                 | 30.64  | 24.5   | 56.18  | 100.47  | 248.39  | 468.65  | 774.36  | 1739.5  |

| 13      | 315.08                  | 2.07   | 1.95   | 2.28   | 3.24    | 8.22    | 13.9    | 20.98   | 49.26   |

| 68      | 59.36                   | 0.85   | 0.79   | 1.01   | 0.99    | 0.79    | 1.29    | 2.3     | 3.7     |

| 82      | 49.95                   | 0.83   | 0.77   | 0.85   | 0.77    | 0.91    | 1.12    | 1.59    | 3.2     |

| 255     | 16.06                   | 0.52   | 0.58   | 0.59   | 0.48    | 0.52    | 0.57    | 1.16    | 1.68    |

Table 15. ADuC845 and ADuC847 Typical Peak-to-Peak Resolution (Bits) vs. Input Range and Update Rate with Chop Disabled

|         | Data Update | Input Range |        |        |         |         |         |         |         |  |

|---------|-------------|-------------|--------|--------|---------|---------|---------|---------|---------|--|

| SF Word | Rate (Hz)   | ±20 mV      | ±40 mV | ±80 mV | ±160 mV | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |  |

| 3       | 1365.33     | 7.5         | 9      | 9      | 9       | 9       | 9       | 9       | 9       |  |

| 13      | 315.08      | 11.5        | 12.5   | 13.5   | 14      | 13.5    | 14      | 14      | 14      |  |

| 68      | 59.36       | 13          | 14     | 14.5   | 15.5    | 17      | 17      | 17.5    | 18      |  |

| 82      | 49.95       | 13          | 14     | 15     | 16      | 16.5    | 17.5    | 18      | 18      |  |

| 255     | 16.06       | 13.5        | 14.5   | 15.5   | 16.5    | 17.5    | 18.5    | 18.5    | 19      |  |

#### Table 16. ADuC848 Typical Output RMS Noise (µV) vs. Input Range and Update Rate with Chop Disabled

|         | Data Update | Input Range |        |        |         |         |         |         |         |  |

|---------|-------------|-------------|--------|--------|---------|---------|---------|---------|---------|--|

| SF Word | Rate (Hz)   | ±20 mV      | ±40 mV | ±80 mV | ±160 mV | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |  |

| 3       | 1365.33     | 30.64       | 24.5   | 56.18  | 100.47  | 248.39  | 468.65  | 774.36  | 1739.5  |  |

| 13      | 315.08      | 2.07        | 1.95   | 2.28   | 3.24    | 8.22    | 13.9    | 20.98   | 49.26   |  |

| 69      | 59.36       | 0.85        | 0.79   | 1.01   | 0.99    | 0.79    | 1.29    | 2.3     | 3.7     |  |

| 82      | 49.95       | 0.83        | 0.77   | 0.85   | 0.77    | 0.91    | 1.12    | 1.59    | 3.2     |  |

| 255     | 16.06       | 0.52        | 0.58   | 0.59   | 0.48    | 0.52    | 0.57    | 1.16    | 1.68    |  |

#### Table 17. ADuC848 Typical Peak-to-Peak Resolution (Bits) vs. Input Range and Update Rate with Chop Disabled

|         | Data Update | Input Range |        |        |         |        |        |         |         |  |

|---------|-------------|-------------|--------|--------|---------|--------|--------|---------|---------|--|

| SF Word | Rate (Hz)   | ±20 mV      | ±40 mV | ±80 mV | ±160 mV | ±320mV | ±640mV | ±1.28 V | ±2.56 V |  |

| 3       | 1365.33     | 7.5         | 9      | 9      | 9       | 9      | 9      | 9       | 9       |  |

| 13      | 315.08      | 11.5        | 12.5   | 13.5   | 14      | 13.5   | 14     | 14      | 14      |  |

| 68      | 59.36       | 13          | 14     | 14.5   | 15.5    | 16     | 16     | 16      | 16      |  |

| 82      | 49.95       | 13          | 14     | 15     | 16      | 16     | 16     | 16      | 16      |  |

| 255     | 16.06       | 13.5        | 14.5   | 15.5   | 16      | 16     | 16     | 16      | 16      |  |

## ADCSTAT (ADC STATUS REGISTER)

This SFR reflects the status of both ADCs including data ready, calibration, and various (ADC-related) error and warning conditions including REFIN± reference detect and conversion overflow/underflow flags.

| SFR Address:      | D8H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | Yes |

| Bit No. | Name   | Description                                                                                                                                                                                                                                    |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | RDY0   | Ready Bit for the Primary ADC.                                                                                                                                                                                                                 |

|         |        | Set by hardware on completion of conversion or calibration.                                                                                                                                                                                    |

|         |        | Cleared directly by the user, or indirectly by a write to the mode bits, to start calibration. The primary ADC is inhibited from writing further results to its data or calibration registers until the RDY0 bit is cleared.                   |

| 6       | RDY1   | Ready Bit for Auxiliary (ADuC845 only) ADC.                                                                                                                                                                                                    |

|         |        | Same definition as RDY0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                                              |

| 5       | CAL    | Calibration Status Bit.                                                                                                                                                                                                                        |

|         |        | Set by hardware on completion of calibration.                                                                                                                                                                                                  |

|         |        | Cleared indirectly by a write to the mode bits to start another ADC conversion or calibration.                                                                                                                                                 |

|         |        | Note that calibration with the temperature sensor selected (auxiliary ADC on the ADuC845 only) fails to complete.                                                                                                                              |

| 4       | NOXREF | No External Reference Bit (only active if primary or auxiliary (ADuC845 only) ADC is active).                                                                                                                                                  |

|         |        | Set to indicate that one or both of the REFIN pins is floating or the applied voltage is below a specified threshold. When set, conversion results are clamped to all 1s. Only detects invalid REFIN±, does not check REFIN±.                  |

|         |        | Cleared to indicate valid V <sub>REF</sub> .                                                                                                                                                                                                   |

| 3       | ERRO   | Primary ADC Error Bit.                                                                                                                                                                                                                         |

|         |        | Set by hardware to indicate that the result written to the primary ADC data registers has been clamped to all 0s or all 1s. After a calibration, this bit also flags error conditions that caused the calibration registers not to be written. |

|         |        | Cleared by a write to the mode bits to initiate a conversion or calibration.                                                                                                                                                                   |

| 2       | ERR1   | Auxiliary ADC Error Bit. Same definition as ERR0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                     |

| 1       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

| 0       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

#### Table 23. ADCSTAT SFR Bit Designation

## ADCMODE (ADC MODE REGISTER)

Used to control the operational mode of both ADCs.

| SFR Address:      | D1H |

|-------------------|-----|

| Power-On Default: | 08H |

| Bit Addressable:  | No  |

### Table 24. ADCMODE SFR Bit Designations

| Bit No. | Name           | Descri                                                                                                                                                                                                                                                                                                                                            | ption              |                      |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7       |                | Not Im                                                                                                                                                                                                                                                                                                                                            | plemer             | nted. Wr             | ite Don't Care.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 6       | REJ60          | Autom                                                                                                                                                                                                                                                                                                                                             | natic 60           | Hz Notc              | h Select Bit.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|         |                | Setting this bit places a notch in the frequency response at 60 Hz, allowing simultaneous 50 Hz and 60 Hz rejection at an SF word of 82 decimal. This 60 Hz notch can be set only if SF $\geq$ 68 decimal, that is, the regula filter notch must be $\leq$ 60 Hz. This second notch is placed at 60 Hz only if the device clock is at 32.768 kHz. |                    |                      |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 5       | ADC0EN         | Primar                                                                                                                                                                                                                                                                                                                                            | y ADC I            | Enable.              |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|         |                | Set by                                                                                                                                                                                                                                                                                                                                            | the use            | er to ena            | ble the primary ADC and place it in the mode selected in MD2–MD0.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|         |                | Cleare                                                                                                                                                                                                                                                                                                                                            | d by the           | e user to            | place the primary ADC into power-down mode.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 4       | ADC1EN         | Auxilia                                                                                                                                                                                                                                                                                                                                           | ry (ADu            | IC845 or             | nly) ADC Enable.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|         | (ADuC845 only) | Set by                                                                                                                                                                                                                                                                                                                                            | the use            | r to ena             | ble the auxiliary (ADuC845 only) ADC and place it in the mode selected in MD2–MD0.                                                                                                                                                                                                                                                                                      |  |  |  |  |

|         |                | Cleare                                                                                                                                                                                                                                                                                                                                            | d by the           | e user to            | place the auxiliary (ADuC845 only) ADC in power-down mode.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 3       | CHOP           | Chop I                                                                                                                                                                                                                                                                                                                                            | Node D             | isable.              |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|         |                | three t<br>1.3 kH                                                                                                                                                                                                                                                                                                                                 | imes hi<br>z ADC u | gher AD<br>Ipdate ra |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|         |                |                                                                                                                                                                                                                                                                                                                                                   |                    |                      | enable chop mode on both the primary and auxiliary (ADuC845 only) ADC.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 2, 1, 0 | MD2, MD1, MD0  |                                                                                                                                                                                                                                                                                                                                                   | •                  |                      | (ADuC845 only) ADC Mode Bits.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|         |                |                                                                                                                                                                                                                                                                                                                                                   |                    |                      | perational mode of the enabled ADC as follows:                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|         |                | MD2                                                                                                                                                                                                                                                                                                                                               | MD1                | MD0                  |                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                 | 0                  | 0                    | ADC Power-Down Mode (Power-On Default).                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                 | 0                  | 1                    | Idle Mode. In idle mode, the ADC filter and modulator are held in a reset state although the modulator clocks are still provided.                                                                                                                                                                                                                                       |  |  |  |  |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                 | 1                  | 0                    | Single Conversion Mode. In single conversion mode, a single conversion is performed<br>on the enabled ADC. Upon completion of a conversion, the ADC data registers<br>(ADC0H/M/L and/or ADC1H/M/L (ADuC845 only)) are updated. The relevant flags in<br>the ADCSTAT SFR are written, and power-down is re-entered with the MD2–MD0<br>accordingly being written to 000. |  |  |  |  |

|         |                |                                                                                                                                                                                                                                                                                                                                                   |                    |                      | Note that ADC0L is not available on the ADuC848.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                 | 1                  | 1                    | Continuous Conversion. In continuous conversion mode, the ADC data registers are regularly updated at the selected update rate (see the Sinc Filter SFR Bit Designations in Table 28).                                                                                                                                                                                  |  |  |  |  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                 | 0                  | 0                    | Internal Zero-Scale Calibration. Internal short automatically connected to the enabled ADC input(s).                                                                                                                                                                                                                                                                    |  |  |  |  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                 | 0                  | 1                    | Internal Full-Scale Calibration. Internal or external REFIN± or REFIN2± $V_{REF}$ (as determined by XREF bits in ADC0CON2 and/or AXREF (ADuC845 only) in ADC1CON (ADuC845 only) is automatically connected to the enabled ADC input(s) for this calibration.                                                                                                            |  |  |  |  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                 | 1                  | 0                    | System Zero-Scale Calibration. User should connect system zero-scale input to the enabled ADC input(s) as selected by CH3–CH0 and ACH3–ACH0 bits in the ADC0CON2 and ADC1CON (ADuC845 only) registers.                                                                                                                                                                  |  |  |  |  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                 | 1                  | 1                    | System Full-Scale Calibration. User should connect system full-scale input to the enabled ADC input(s) as selected by CH3–CH0 and ACH3–ACH0 bits in the ADC0CON2 and ADC1CON (ADuC845 only) registers.                                                                                                                                                                  |  |  |  |  |

## ICON (EXCITATION CURRENT SOURCES CONTROL REGISTER)

The ICON register is used to configure the current sources and the burnout detection source.

| SFR Address:      | D5H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

#### Table 30. Excitation Current Source SFR Bit Designations

| Bit No. | Name   | Description                                                                                                                                                                                     |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       |        | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 6       | ICON.6 | Burnout Current Enable Bit.                                                                                                                                                                     |

|         |        | When set, this bit enables the sensor burnout current sources on primary ADC channels AIN5/AIN6 or AIN7/AIN8. Not available on any other ADC input pins or on the auxiliary ADC (ADuC845 only). |

| 5       | ICON.5 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 4       | ICON.4 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 3       | ICON.3 | IEXC2 Pin Select. 0 selects AIN8, 1 selects AIN7                                                                                                                                                |

| 2       | ICON.2 | IEXC1 Pin Select. 0 selects AIN7, 1 selects AIN8                                                                                                                                                |

| 1       | ICON.1 | IEXC2 Enable Bit (0 = disable).                                                                                                                                                                 |

| 0       | ICON.0 | IEXC1 Enable Bit (0 = disable).                                                                                                                                                                 |

A write to the ICON register has an immediate effect but does not reset the ADCs. Therefore, if a current source is changed while an ADC is already converting, the user must wait until the third or fourth output at least (depending on the status of the chop mode) to see a fully settled new output.

Both IEXC1 and IEXC2 can be configured to operate on the same output pin thereby increasing the current source capability to 400 µA.

## **ON-CHIP PLL (PLLCON)**

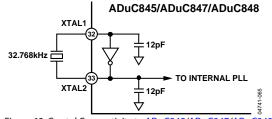

The ADuC845/ADuC847/ADuC848 are intended for use with a 32.768 kHz watch crystal. A PLL locks onto a multiple (384) of this to provide a stable 12.582912 MHz clock for the system. The core can operate at this frequency or at binary submultiples of it to allow power saving when maximum core performance is not required. The default core clock is the PLL clock divided by 8 or 1.572864 MHz. The ADC clocks are also derived from the PLL clock, with the modulator rate being the same as the crystal oscillator frequency. The control register for the PLL is called PLLCON and is described as follows.

The 5 V parts can be set to a maximum core frequency of 12.58 MHz (CD2...0 = 000) while at 3 V, the maximum core clock rate is 6.29 MHz (CD2...0 = 001). The CD bits should not be set to 000b on the 3 V parts.

The 3 V parts are limited to a core clock speed of 6.29 MHz (CD = 1).

#### PLLCON PLL Control Register

| SFR Address:      | D7H |

|-------------------|-----|

| Power-On Default: | 53H |

| Bit Addressable:  | No  |

#### Table 39. PLLCON PLL Control Register

| Bit No. | Name          | Descr                                                                                                                                                                                                                                                                                                                                                                                                                  | iption                                                                                                                                                                         |                 |                                                                               |  |  |

|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------|--|--|

| 7       | OSC_PD        | Oscillator Power-Down Bit.                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                |                 |                                                                               |  |  |

|         |               | If low, the 32 kHz crystal oscillator continues running in power-down mode.                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                |                 |                                                                               |  |  |

|         |               | If high, the 32.768 kHz oscillator is powered down.                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                |                 |                                                                               |  |  |

|         |               | When this bit is low, the seconds counter continues to count in power-down mode and can interrupt t to exit power-down. The oscillator is always enabled in normal mode.                                                                                                                                                                                                                                               |                                                                                                                                                                                |                 |                                                                               |  |  |

| 6       | LOCK          | PLL Lo                                                                                                                                                                                                                                                                                                                                                                                                                 | ock Bit. Thi                                                                                                                                                                   | s is a read-onl | y bit.                                                                        |  |  |

|         |               |                                                                                                                                                                                                                                                                                                                                                                                                                        | Set automatically at power-on to indicate that the PLL loop is correctly tracking the crystal clock. After power-<br>down, this bit can be polled to wait for the PLL to lock. |                 |                                                                               |  |  |

|         |               | Cleared automatically at power-on to indicate that the PLL is not correctly tracking the crystal clock. This might be due to the absence of a crystal clock or an external crystal at power-on. In this mode, the PLL outp can be 12.58 MHz $\pm$ 20%. After the device wakes up from power-down, user code can poll this bit to wait for the PLL to lock. If LOCK = 0, the PLL is not locked.                         |                                                                                                                                                                                |                 |                                                                               |  |  |

| 5       |               | Not In                                                                                                                                                                                                                                                                                                                                                                                                                 | nplemente                                                                                                                                                                      | ed. Write Don'  | t Care.                                                                       |  |  |

| 4       | LTEA          | EA Sta                                                                                                                                                                                                                                                                                                                                                                                                                 | EA Status. Read-only bit. Reading this bit returns the state of the external EA pin latched at reset or power-on.                                                              |                 |                                                                               |  |  |