Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8052                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 12.58MHz                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                   |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | 4K x 8                                                            |

| RAM Size                   | 2.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                     |

| Data Converters            | A/D 10x24b; D/A 1x12b, 2x16b                                      |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 52-QFP                                                            |

| Supplier Device Package    | 52-MQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc847bsz8-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Revision History                             |

| Specifications                               |

| Abosolute Maximum Ratings 10                 |

| ESD Caution10                                |

| Pin Configurations and Function Descriptions |

| General Description                          |

| 8052 Instruction Set                         |

| Timer Operation                              |

| ALE                                          |

| External Memory Access                       |

| Complete SFR Map19                           |

| Functional Description                       |

| 8051 Instruction Set 20                      |

| Memory Organization                          |

| Special Function Registers (SFRs)            |

| ADC Circuit Information26                    |

| Auxiliary ADC (ADuC845 Only)                 |

| Reference Inputs                             |

| Burnout Current Sources                      |

| Reference Detect Circuit                     |

| Sinc Filter Register (SF)                    |

| $\Sigma$ - $\Delta$ Modulator                |

| Digital Filter                               |

| ADC Chopping                                 |

| Calibration                                  |

| Programmable Gain Amplifier                  |

| Bipolar/Unipolar Configuration35             |

| Data Output Coding                           |

| Excitation Currents                          |

|   | ADC Power-On                                       |

|---|----------------------------------------------------|

| Т | ypical Performance Characteristics                 |

| F | unctional Description                              |

|   | ADC SFR Interface                                  |

|   | ADCSTAT (ADC Status Register) 40                   |

|   | ADCMODE (ADC Mode Register)                        |

|   | ADC0CON1 (Primary ADC Control Register) 43         |

|   | ADC0CON2 (Primary ADC Channel Select Register) 44  |

|   | SF (ADC Sinc Filter Control Register) 46           |

|   | ICON (Excitation Current Sources Control Register) |

|   | Nonvolatile Flash/EE Memory Overview               |

|   | Flash/EE Program Memory 49                         |

|   | User Download Mode (ULOAD) 50                      |

|   | Using Flash/EE Data Memory51                       |

|   | Flash/EE Memory Timing                             |

|   | DAC Circuit Information                            |

|   | Pulse-Width Modulator (PWM)55                      |

|   | On-Chip PLL (PLLCON)                               |

|   | I <sup>2</sup> C Serial Interface                  |

|   | SPI Serial Interface                               |

|   | Using the SPI Interface                            |

|   | Dual Data Pointers                                 |

|   | Power Supply Monitor                               |

|   | Watchdog Timer                                     |

|   | Time Interval Counter (TIC)                        |

|   | 8052-Compatible On-Chip Peripherals                |

|   | Timers/Counters                                    |

|   | UART Serial Interface                              |

|   | Interrupt System                                   |

|   | Interrupt Priority                                 |

|   | Interrupt Vectors                                  |

|  | D | a | ta | S | h | e | e | t |

|--|---|---|----|---|---|---|---|---|

|--|---|---|----|---|---|---|---|---|

| Parameter                                             | Min                        | Тур                | Max                     | Unit      | Test Conditions/Comments                                           |

|-------------------------------------------------------|----------------------------|--------------------|-------------------------|-----------|--------------------------------------------------------------------|

| AUXILIARY ADC ANALOG INPUTS                           |                            |                    |                         |           |                                                                    |

| (ADuC845 ONLY)                                        |                            |                    |                         |           |                                                                    |

| Differential Input Voltage Ranges <sup>5, 6</sup>     |                            |                    |                         |           |                                                                    |

| Bipolar Mode (ADC1CON.5 = 0)                          |                            | $\pm V_{REF}$      |                         | V         | $REFIN = REFIN(+) - REFIN(-) \text{ (or Int 1.25 } V_{REF})$       |

| Unipolar Mode (ADC1CON.5 = 1)                         |                            | $0 - V_{REF}$      |                         | V         | $REFIN = REFIN(+) - REFIN(-)$ (or Int 1.25 $V_{REF}$ )             |

| Average Analog Input Current                          |                            | 125                |                         | nA/V      |                                                                    |

| Analog Input Current Drift                            |                            | ±2                 | A) / .                  | pA/V/°C   |                                                                    |

| Absolute AIN/AINCOM Voltage<br>Limits <sup>2, 7</sup> | A <sub>GND</sub> –<br>0.03 |                    | AV <sub>DD</sub> + 0.03 | V         |                                                                    |

| Normal Mode Rejection 50 Hz/60 Hz <sup>2</sup>        |                            |                    |                         |           |                                                                    |

| On AIN and REFIN                                      | 75                         |                    |                         | dB        | 50 Hz/60 Hz ± 1 Hz, 16.6 Hz Fadc, SF = 52H, chop<br>on, REJ60 on   |

|                                                       | 100                        |                    |                         | dB        | $50 \text{ Hz} \pm 1 \text{ Hz}$ , 16.6 Hz Fadc, SF = 52H, chop on |

|                                                       | 67                         |                    |                         | dB        | 50 Hz/60 Hz $\pm$ 1 Hz, 50 Hz Fadc, SF = 52H, chop off, REJ60 on   |

|                                                       | 100                        |                    |                         | dB        | 50 Hz $\pm$ 1 Hz, 50 Hz Fadc, SF = 52H, chop off                   |

| ADC SYSTEM CALIBRATION                                |                            |                    |                         |           |                                                                    |

| Full-Scale Calibration Limit                          |                            |                    | $+1.05 \times FS$       | V         |                                                                    |

| Zero-Scale Calibration Limit                          | $-1.05 \times FS$          |                    |                         | V         |                                                                    |

| Input Span                                            | $0.8 \times FS$            |                    | 2.1 × FS                | V         |                                                                    |

| DAC                                                   |                            |                    |                         |           |                                                                    |

| Voltage Range                                         |                            | $0-V_{\text{REF}}$ |                         | V         | DACCON.2 = 0                                                       |

|                                                       |                            | $0 - AV_{DD}$      |                         | V         | DACCON.2 = 1                                                       |

| Resistive Load                                        |                            | 10                 |                         | kΩ        | From DAC output to AGND                                            |

| Capactive Load                                        |                            | 100                |                         | pF        | From DAC output to AGND                                            |

| Output Impedance                                      |                            | 0.5                |                         | Ω         |                                                                    |

| Isink                                                 |                            | 50                 |                         | μΑ        |                                                                    |

| DC Specifications <sup>8</sup>                        | 4.0                        |                    |                         |           |                                                                    |

| Resolution                                            | 12                         |                    |                         | Bits      |                                                                    |

| Relative Accuracy                                     |                            | ±3                 | 1                       | LSB       |                                                                    |

| Differential Nonlinearity                             |                            |                    | -1                      | LSB       | Guaranteed 12-bit monotonic                                        |

| Offset Error                                          |                            |                    | ±50                     | mV        | AV/                                                                |

| Gain Error                                            |                            | . 1                | ±1                      | %         | AV <sub>DD</sub> range                                             |

| AC Specifications <sup>2,8</sup>                      |                            | ±1                 |                         | %         | V <sub>REF</sub> range                                             |

| Voltage Output Settling Time                          |                            | 15                 |                         |           | Settling time to 1 LSB of final value                              |

| Digital-to-Analog Glitch Energy                       |                            | 10                 |                         | μs<br>nVs | 1 LSB change at major carry                                        |

| INTERNAL REFERENCE                                    |                            | 10                 |                         | 1105      |                                                                    |

| ADC Reference                                         |                            |                    |                         |           | Chop enabled                                                       |

| Reference Voltage                                     | 1.25 – 1%                  | 1.25               | 1.25 + 1%               | v         | Initial tolerance @ $25^{\circ}$ C, V <sub>DD</sub> = 5 V          |

| Power Supply Rejection                                | 1.23 1/0                   | 45                 | ריד <b>ביי</b> ו 170    | dB        |                                                                    |

| Reference Tempco                                      |                            | 100                |                         | ppm/°C    |                                                                    |

| DAC Reference                                         |                            |                    |                         | PP''' C   |                                                                    |

| Reference Voltage                                     | 2.5 – 1%                   | 2.5                | 2.5 + 1%                | ±1% V     | Initial tolerance @ 25°C, $V_{DD} = 5 V$                           |

| Power Supply Rejection                                |                            | 50                 |                         | dB        |                                                                    |

| Reference Tempco                                      |                            | ±100               |                         | ppm/°C    |                                                                    |

| TEMPERATURE SENSOR<br>(ADuC845 ONLY)                  |                            | -                  |                         |           |                                                                    |

| Accuracy                                              |                            | ±2                 |                         | °C        |                                                                    |

| Thermal Impedance                                     |                            | 90                 |                         | °C/W      | MQFP                                                               |

|                                                       |                            | 52                 |                         | °C/W      | LFCSP                                                              |

P2.7/PWMCLK (A15/A23) P2.5/PWM0 (A13/A21) P2.6/PWM1 (A14/A22) P2.3/SS/T2 (A11/A19) P2.4/T2EX (A12/A20) P2.2/MISO (A10/A18) P2.0/SCLK (A8/A16) P2.1/MOSI (A9/A17) P1.2/AIN3/REFIN2+ P1.3/AIN4/REFIN2-P1.7/AIN8/IEXC2 P1.6/AIN7/IEXC1 P3.1 (TxD) P0.2 (AD2) P0.3 (AD3) P0.4 (AD4) P0.5 (AD5) P0.7 (AD7) P3.2 (<u>INTO</u>) P3.3 (<u>INT1</u>) P0.0 (AD0) P0.1 (AD1) P0.6 (AD6) P3.6 (<u>WR</u>) P3.7 (<u>RD</u>) P1.4/AIN5 P1.5/AIN6 P3.0 (RxD) P1.1/AIN2 P3.4 (T0) P3.5 (T1) P1.0/AIN 46 (47) 484952535455 323333404142 1319202124252627 66) 1 @3 ⊚ 00-(12) <u>30</u>31 AIN1 ADuC845 8 AIN2 o-~ AIN3 12-BIT ADC CONTROL DAC VOLTAGE PRIMARY ADC BUF (14) DAC CONTROL AIN4 BUF PG/ OUTPUT DAG 24-BIT AND Σ- $\Delta$  ADC AIN5 AIN MUX 8 o AIN6 (10 DUAL AIN7 (11 16-BIT Σ-Δ DAC ADC CONTROL (40) PWM0 AUXILIARY ADC PWM AIN8 (12) мих **24-BIT** Σ**-**Δ **ADC** CONTRO AND CALIBRATION DUAL 16-BIT PWM AIN9 (15 (41) PWM1 AIN10 (16 AINCOM/DAC (13 62 kBYTES PROGRAM/ BAND GAP REFERENCE 2304 BYTES USER RAM (24) TO FLASH/EE 16-BIT SINGLE-(25) Т1 TEMP SENSOR COUNTER CYCLE 4 kBYTES DATA/ FLASH/EE WATCHDOG 33 Т2 TIMER 8052 REFIN+ (8) 39) V<sub>REF</sub> DETECT T2EX MCU CORE REFIN-POWER SUPPLY 2 × DATA POINTERS 11-BIT STACK POINTER MONITOR 20 INTO PLL WITH PROG. CLOCK DIVIDER **200**μ**A** 8 **200**μ**A** 21) INT1 DOWNLOADER DEBUGGER WAKE-UP/ CURRENT SOURCE IEXC1 ( RTC TIMER IEXC2 SINGLE-PIN EMULATOR MIX UART SERIAL PORT SPI SERIAL UART I<sup>2</sup>C SERIAL POR INTERFACE TIMER INTERFACE OSC ŧ 5)6) 2236 23(37)(38)(50) 18 19 44)(43) (45 4 (51 30 32 28 DV<sub>DD</sub> PSEN EA SCLK MISO SDATA AV<sub>DD</sub> SCLK XTAL1 XTAL2 AGND DGND RXD Ť SS MOSI RESET

NOTES 1. THE PIN NUMBERS REFER TO THE LFCSP PACKAGE ONLY.

Figure 4. Detailed Block Diagram of the ADuC845

04741-004

| Mnemonic                  | Description                              | Bytes | Cycles <sup>1</sup> |

|---------------------------|------------------------------------------|-------|---------------------|

| SJMP rel                  | Short jump (relative address)            | 2     | 3                   |

| JC rel                    | Jump on carry = 1                        | 2     | 3                   |

| JNC rel                   | Jump on carry = 0                        | 2     | 3                   |

| JZ rel                    | Jump on accumulator = 0                  | 2     | 3                   |

| JNZ rel                   | Jump on accumulator ! = 0                | 2     | 3                   |

| DJNZ Rn,rel               | Decrement register, JNZ relative         | 2     | 3                   |

| LJMP                      | Long jump unconditional                  | 3     | 4                   |

| LCALL <sup>3</sup> addr16 | Long jump to subroutine                  | 3     | 4                   |

| JB bit,rel                | Jump on direct bit = 1                   | 3     | 4                   |

| JNB bit,rel               | Jump on direct bit = 0                   | 3     | 4                   |

| JBC bit,rel               | Jump on direct bit = 1 and clear         | 3     | 4                   |

| CJNE A,dir,rel            | Compare A, direct JNE relative           | 3     | 4                   |

| CJNE A,#data,rel          | Compare A, immediate JNE relative        | 3     | 4                   |

| CJNE Rn,#data,rel         | Compare register, immediate JNE relative | 3     | 4                   |

| CJNE @Ri,#data,rel        | Compare indirect, immediate JNE relative | 3     | 4                   |

| DJNZ dir,rel              | Decrement direct byte, JNZ relative      | 3     | 4                   |

| Miscellaneous             |                                          |       |                     |

| NOP                       | No operation                             | 1     | 1                   |

<sup>1</sup> One cycle is one clock.

<sup>2</sup> MOVX instructions are four cycles when they have 0 wait state. Cycles of MOVX instructions are 4 + *n* cycles when they have *n* wait states as programmed via EWAIT. <sup>3</sup> LCALL instructions are three cycles when the LCALL instruction comes from an interrupt.

#### **MEMORY ORGANIZATION**

The ADuC845, ADuC847, and ADuC848 contain four memory blocks:

- 62 kbytes/32 kbytes/8 kbytes of on-chip Flash/EE program memory

- 4 kbytes of on-chip Flash/EE data memory

- 256 bytes of general-purpose RAM

- 2 kbytes of internal XRAM

#### Flash/EE Program Memory

The devices provide up to 62 kbytes of Flash/EE program memory to run user code. All further references to Flash/EE program memory assume the 62-kbyte option.

When EA is pulled high externally during a power cycle or a hardware reset, the devices default to code execution from their internal 62 kbytes of Flash/EE program memory. The devices do not support the rollover from internal code space to external code space. No external code space is available on the devices. Permanently embedded firmware allows code to be serially downloaded to the 62 kbytes of internal code space via the UART serial port while the device is in-circuit. No external hardware is required.

During run time, 56 kbytes of the 62-kbyte program memory can be reprogrammed. This means that the code space can be upgraded in the field by using a user-defined protocol running on the devices, or it can be used as a data memory. For details, see the Nonvolatile Flash/EE Memory Overview section.

#### Flash/EE Data Memory

The user has 4 kbytes of Flash/EE data memory available that can be accessed indirectly by using a group of registers mapped into the special function register (SFR) space. For details, see the Nonvolatile Flash/EE Memory Overview section.

#### **General-Purpose RAM**

The general-purpose RAM is divided into two separate memories, the upper and the lower 128 bytes of RAM. The lower 128 bytes of RAM can be accessed through direct or indirect addressing. The upper 128 bytes of RAM can be accessed only through indirect addressing because it shares the same address space as the SFR space, which must be accessed through direct addressing.

The lower 128 bytes of internal data memory are mapped as shown in Figure 8. The lowest 32 bytes are grouped into four banks of eight registers addressed as R0 to R7. The next 16 bytes (128 bits), locations 20H to 2FH above the register banks, form a block of directly addressable bit locations at Bit Addresses 00H to 7FH. The stack can be located anywhere in the internal memory address space, and the stack depth can be expanded up to 2048 bytes.

Reset initializes the stack pointer to location 07H. Any call or push pre-increments the SP before loading the stack. Therefore, loading the stack starts from location 08H, which is also the first register (R0) of Register Bank 1. Thus, if one is going to use more than one register bank, the stack pointer should be initialized to an area of RAM not used for data storage.

#### Power Control Register (PCON)

The PCON SFR contains bits for power-saving options and general-purpose status flags as listed in Table 6.

| SFR Address:      | 87H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

#### Table 6. PCON SFR Bit Designations

| Bit No. | Name          | Description                                                                                                                                                     |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | SMOD          | Double UART Baud Rate.                                                                                                                                          |

|         |               | 0 = Normal, 1 = Double Baud Rate.                                                                                                                               |

| 6       | SERIPD        | Serial Power-Down Interrupt Enable. If this<br>bit is set, a serial interrupt from either SPI<br>or I <sup>2</sup> C can terminate the power-down<br>mode.      |

| 5       | <b>INTOPD</b> | INT0 Power-Down Interrupt Enable.                                                                                                                               |

|         |               | If this bit is set, either a level ( $\overline{IT0} = 0$ ) or a negative-going transition ( $\overline{IT0} = 1$ ) on the INT0 pin terminates power-down mode. |

| 4       | ALEOFF        | If set to 1, the ALE output is disabled.                                                                                                                        |

| 3       | GF1           | General-Purpose Flag Bit.                                                                                                                                       |

| 2       | GF0           | General-Purpose Flag Bit.                                                                                                                                       |

| 1       | PD            | Power-Down Mode Enable. If set to 1, the device enters power-down mode.                                                                                         |

| 0       |               | Not Implemented. Write Don't Care.                                                                                                                              |

# ADuC845/ADuC847/ADuC848 Configuration Register (CFG845/CFG847/CFG848)

The CFG845/CFG847/CFG848 SFR contains the bits necessary to configure the internal XRAM and the extended SP. By default, it configures the user into 8051 mode, that is, extended SP, and the internal XRAM are disabled. When using in a program, use the device name only, that is, CFG845, CFG847, or CFG848.

| SFR Address:      | AFH |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

| Table 7. CFG845/CFG847/CFG848 SFR Bit Designations |

|----------------------------------------------------|

|----------------------------------------------------|

| Bit No. | Name   | Description                                                                                                                                   |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | EXSP   | Extended SP Enable.                                                                                                                           |

|         |        | If this bit is set to 1, the stack rolls over from SPH/SP = 00FFH to 0100H.                                                                   |

|         |        | If this bit is cleared to 0, SPH SFR is<br>disabled and the stack rolls over from<br>SP = FFH to SP = 00H.                                    |

| 6       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 5       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 4       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 3       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 2       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 1       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 0       | XRAMEN | If this bit is set to 1, the internal XRAM is<br>mapped into the lower 2 kbytes of the<br>external address space.                             |

|         |        | If this bit is cleared to 0, the internal XRAM<br>is accessible and up to 16 MB of external<br>data memory become available. See<br>Figure 8. |

#### AUXILIARY ADC (ADUC845 ONLY)

Table 18. ADuC845 Typical Output RMS Noise (μV) vs. Update Rate with Chop Enabled

| SF Word | Data Update Rate (Hz) | μV    |

|---------|-----------------------|-------|

| 13      | 105.03                | 17.46 |

| 23      | 59.36                 | 3.13  |

| 27      | 50.56                 | 4.56  |

| 69      | 19.79                 | 2.66  |

| 255     | 5.35                  | 1.13  |

|         |                       |       |

# Table 19. ADuC845 Typical Peak-to-Peak Resolution (Bits)vs. Update Rate1 with Chop Enabled

| 1       | 1 1                   |      |  |  |  |  |  |

|---------|-----------------------|------|--|--|--|--|--|

| SF Word | Data Update Rate (Hz) | Bits |  |  |  |  |  |

| 13      | 105.03                | 15.5 |  |  |  |  |  |

| 23      | 59.36                 | 18   |  |  |  |  |  |

| 27      | 50.56                 | 17.5 |  |  |  |  |  |

| 69      | 19.79                 | 18   |  |  |  |  |  |

| 255     | 5.35                  | 19.5 |  |  |  |  |  |

<sup>1</sup> ADC converting in bipolar mode.

# Table 20. ADuC845 Typical Output RMS Noise ( $\mu$ V) vs. Update Rate with Chop Disabled

| SF Word | Data Update Rate (Hz) | μV      |

|---------|-----------------------|---------|

| 3       | 1365.33               | 1386.58 |

| 13      | 315.08                | 34.94   |

| 66      | 62.06                 | 3.2     |

| 69      | 59.36                 | 3.19    |

| 81      | 50.57                 | 3.14    |

| 255     | 16.06                 | 1.71    |

| Table 21. ADuC845 Peak-to-Peak Resolution (Bits) vs. |

|------------------------------------------------------|

| Update Rate with Chop Disabled                       |

| SF Word | Data Update Rate (Hz) | Bits |

|---------|-----------------------|------|

| 3       | 1365.33               | 9    |

| 13      | 315.08                | 14.5 |

| 66      | 62.06                 | 18   |

| 69      | 59.36                 | 18   |

| 81      | 50.57                 | 18   |

| 255     | 16.06                 | 19   |

#### **REFERENCE INPUTS**

The ADuC845/ADuC847/ADuC848 each have two separate differential reference inputs, REFIN± and REFIN2±. While both references are available for use with the primary ADC, only REFIN± is available for the auxiliary ADC (ADuC845 only). The common-mode range for these differential references is from AGND to AV<sub>DD</sub>. The nominal external reference voltage is

2.5 V, with the primary and auxiliary (ADuC845 only) reference select bits configured from the ADC0CON2 and ADC1CON (ADuC845 only), respectively.

When an external reference voltage is used, the primary ADC sees this internally as a 2.56 V reference ( $V_{REF} \times 1.024$ ). Therefore, any calculations of LSB size should account for this. For instance, with a 2.5 V external reference connected and using a gain of 1 on a unipolar range (2.56 V), the LSB size is ( $2.56/2^{24}$ ) = 152.6 nV (if using the 24-bit ADC on the ADuC845 or ADuC847). If a bipolar gain of 4 is used (±640 mV), the LSB size is (±640 mV)/2<sup>24</sup>) = 76.3 nV (again using the 24-bit ADC on the ADuC845 or ADuC845 or ADuC847).

The ADuC845/ADuC847/ADuC848 can also be configured to use the on-chip band gap reference via the XREF0/1 bits in the ADC0CON2 SFR (for primary ADC) or the AXREF bit in ADC1CON (for auxiliary ADC (ADuC845 only)). In this mode of operation, the ADC sees the internal reference of 1.25 V, thereby halving all the input ranges. A consequence of using the internal band gap reference is a noticeable degradation in peakto-peak resolution. For this reason, operation with an external reference is recommended.

In applications where the excitation (voltage or current) for the transducer on the analog input also drives the reference inputs for the device, the effect of any low frequency noise in the excitation source is removed because the application is ratiometric. If the devices are not used in a ratiometric configuration, use a low noise reference. Recommended reference voltage sources for the ADuC845/ADuC847/ADuC848 include the ADR421, REF43, and REF192.

The reference inputs provide a high impedance, dynamic load to external connections. Because the impedance of each reference input is dynamic, resistor/capacitor combinations on these pins can cause dc gain errors, depending on the output impedance of the source that is driving the reference inputs. Reference voltage sources, such as those mentioned above, for example, the ADR421, typically have low output impedances, and, therefore, decoupling capacitors on the REFIN± or REFIN2± inputs would be recommended (typically 0.1  $\mu$ F). Deriving the reference voltage from an external resistor configuration means that the reference input sees a significant external source impedance. External decoupling of the REFIN± and/or REFIN2± inputs is not recommended in this type of configuration.

#### **BURNOUT CURRENT SOURCES**

The primary ADC on the ADuC845 and the ADC on the ADuC847 and ADuC848 incorporate two 100 nA constant current generators that are used to detect a failure in a connected sensor. One sources current from the  $AV_{DD}$  to AIN(+), and one sinks current from AIN(-) to AGND. These currents are only configurable for use on AIN5/AIN6 and/or AIN7/AIN8 in differential mode only, from the ICON.6 bit in the ICON SFR

#### DATA OUTPUT CODING

When the primary ADC is configured for unipolar operation, the output coding is natural (straight) binary with a zero differential input voltage resulting in a code of 000...000, a midscale voltage resulting in a code of 100...000, and a full-scale voltage resulting in a code of 111...111. The output code for any analog input voltage on the main ADC can be represented as follows:

$Code - (AIN \times GAIN \times 2^{N})/(1.024 \times V_{REF})$

where:

AIN is the analog input voltage.

*GAIN* is the PGA gain setting, that is, 1 on the 2.56 V range and 128 on the 20 mV range, and N = 24 (16 on the ADuC848).

The output code for any analog input voltage on the auxiliary ADC can be represented as follows:

$Code = (AIN \times 2^{N})/(V_{REF})$

with the same definitions as used for the primary ADC above.

When the primary ADC is configured for bipolar operation, the coding is offset binary with negative full-scale voltage resulting in a code of 000...000, a zero differential voltage resulting in a code of 800...000, and a positive full-scale voltage resulting in a code of 111...111. The output from the primary ADC for any analog input voltage can be represented as follows:

$Code = 2^{N-1} [(AIN \times GAIN)/(1.024 \times V_{REF}) + 1]$

where:

AIN is the analog input voltage.

*GAIN* is the PGA gain, that is, 1 on the  $\pm 2.56$  V range and 128 on the  $\pm 20$  mV range. N = 24 (16 on the ADuC848).

The output from the auxiliary ADC in bipolar mode can be represented as follows:

$Code = 2^{N-1} [(AIN/V_{REF}) + 1]$

#### **EXCITATION CURRENTS**

The ADuC845/ADuC847/ADuC848 contain two matched, software-configurable 200  $\mu$ A current sources. Both source current from AV<sub>DD</sub>, which is directed to either or both of the IEXC1 (Pin 11 whose alternate functions are P1.6/AIN7) or IEXC2 (Pin 12, whose alternate functions are P1.7/AIN8) pins on the device. These currents are controlled via the lower four bits in the ICON register (Table 30). These bits not only enable the current sources but also allow the configuration of the currents such that 200  $\mu$ A can be sourced individually from both pins or can be combined to give a 400  $\mu$ A source from one or the other of the outputs. These sources can be used to excite external resistive bridge or RTD sensors (see Figure 71).

#### **ADC POWER-ON**

The ADC typically takes 0.5 ms to power up from an initial start-up sequence or following a power-down event.

#### Notes on the ADCMODE Register

Any change to the MD bits immediately resets both ADCs (auxiliary ADC only applicable to the ADuC845). A write to the MD2–MD0 bits with no change in contents is also treated as a reset. (See the exception to this in the third note of this section.)

If ADC1CON1 and ADC1CON2 are written when ADC0EN = 1, or if ADC0EN is changed from 0 to 1, both ADCs are also immediately reset. In other words, the primary ADC is given priority over the auxiliary ADC and any change requested on the primary ADC is immediately responded to. Only applicable to the ADuC845.

On the other hand, if ADC1CON is written to or if ADC1EN is changed from 0 to 1, only the auxiliary ADC is reset. For example, if the primary ADC is continuously converting when the auxiliary ADC change or enable occurs, the primary ADC continues undisturbed. Rather than allow the auxiliary ADC to operate with a phase difference from the primary ADC, the auxiliary ADC falls into step with the outputs of the primary ADC. The result is that the first conversion time for the auxiliary ADC is delayed by up to three outputs while the auxiliary ADC update rate is synchronized to the primary ADC. Only applicable to ADuC845. If the ADC1CON write occurs after the primary ADC has completed its operation, the auxiliary ADC can respond immediately without having to fall into step with the primary ADCs output cycle. If the devices are powered down via the PD bit in the PCON register, the current ADCMODE bits are preserved, that is, they are not reset to default state. Upon a subsequent resumption of normal operating mode, the ADCs restarts the selected operation defined by the ADCMODE register.

Once ADCMODE has been written with a calibration mode, the RDY0/1 (ADuC845 only) bits (ADCSTAT) are reset and the calibration commences. On completion, the appropriate calibration registers are written, the relevant bits in ADCSTAT are written, and the MD2–MD0 bits are reset to 000B to indicate that the ADC is back in power-down mode.

Any calibration request of the auxiliary ADC while the temperature sensor is selected fails to complete. Although the RDY1 bit is set at the end of the calibration cycle, no update of the calibration SFRs takes place, and the ERR1 bit is set. ADuC845 only.

Calibrations performed at maximum SF (see Table 28) value (slowest ADC throughput rate) help to ensure optimum calibration.

The duration of a calibration cycle is 2/Fadc for chop-on mode and 4/Fadc for chop-off mode.

### ADC0CON1 (PRIMARY ADC CONTROL REGISTER)

ADC0CON1 is used to configure the primary ADC for buffer, unipolar, or bipolar coding, and ADC range configuration.

| SFR Address:      | D2H |

|-------------------|-----|

| Power-On Default: | 07H |

| Bit Addressable:  | No  |

#### Table 25. ADC0CON1 SFR Bit Designations

| Bit No. | Name          | Descr                              | iption      |              |                                                                        |

|---------|---------------|------------------------------------|-------------|--------------|------------------------------------------------------------------------|

| 7,6     | BUF1, BUF0    | Buffer Configuration Bits.         |             |              |                                                                        |

|         |               | BUF1                               | <b>BUF0</b> |              | Buffer Configuration                                                   |

|         |               | 0                                  | 0           |              | ADC0+ and ADC0- are buffered                                           |

|         |               | 0                                  | 1           |              | Reserved                                                               |

|         |               | 1                                  | 0           |              | Buffer Bypass                                                          |

|         |               | 1                                  | 1           |              | Reserved                                                               |

| 5       | UNI           | Prima                              | ry ADC Ur   | nipolar Bit. |                                                                        |

|         |               | Set by                             | the user    | to enable u  | nipolar coding; zero differential input results in 000000H output.     |

|         |               | Cleare                             | d by the    | user to enab | ble bipolar coding; zero differential input results in 800000H output. |

| 4       |               | Not Implemented. Write Don't Care. |             |              |                                                                        |

| 3       |               | Not In                             | nplement    | ed. Write Do | on't Care.                                                             |

| 2, 1, 0 | RN2, RN1, RN0 | Prima                              | ry ADC Ra   | ange Bits. W | ritten by the user to select the primary ADC input range as follows:   |

|         |               | RN2                                | RN1         | RN0          | Selected primary ADC input range ( $V_{REF} = 2.5 V$ )                 |

|         |               | 0                                  | 0           | 0            | ±20 mV (0 mV to 20 mV in unipolar mode)                                |

|         |               | 0                                  | 0           | 1            | ±40 mV (0 mV to 40 mV in unipolar mode)                                |

|         |               | 0                                  | 1           | 0            | ±80 mV (0 mV to 80 mV in unipolar mode)                                |

|         |               | 0                                  | 1           | 1            | ±160 mV (0 mV to 160 mV in unipolar mode)                              |

|         |               | 1                                  | 0           | 0            | ±320 mV (0 mV to 320 mV in unipolar mode)                              |

|         |               | 1                                  | 0           | 1            | ±640 mV (0 mV to 640 mV in unipolar mode)                              |

|         |               | 1                                  | 1           | 0            | ±1.28 V (0 V to 1.28 V in unipolar mode)                               |

|         |               | 1                                  | 1           | 1            | ±2.56 V (0 V to 2.56 V in unipolar mode)                               |

#### ICON (EXCITATION CURRENT SOURCES CONTROL REGISTER)

The ICON register is used to configure the current sources and the burnout detection source.

| SFR Address:      | D5H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

#### Table 30. Excitation Current Source SFR Bit Designations

| Bit No. | Name   | Description                                                                                                                                                                                     |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       |        | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 6       | ICON.6 | Burnout Current Enable Bit.                                                                                                                                                                     |

|         |        | When set, this bit enables the sensor burnout current sources on primary ADC channels AIN5/AIN6 or AIN7/AIN8. Not available on any other ADC input pins or on the auxiliary ADC (ADuC845 only). |

| 5       | ICON.5 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 4       | ICON.4 | Not Implemented. Write Don't Care.                                                                                                                                                              |

| 3       | ICON.3 | IEXC2 Pin Select. 0 selects AIN8, 1 selects AIN7                                                                                                                                                |

| 2       | ICON.2 | IEXC1 Pin Select. 0 selects AIN7, 1 selects AIN8                                                                                                                                                |

| 1       | ICON.1 | IEXC2 Enable Bit (0 = disable).                                                                                                                                                                 |

| 0       | ICON.0 | IEXC1 Enable Bit (0 = disable).                                                                                                                                                                 |

A write to the ICON register has an immediate effect but does not reset the ADCs. Therefore, if a current source is changed while an ADC is already converting, the user must wait until the third or fourth output at least (depending on the status of the chop mode) to see a fully settled new output.

Both IEXC1 and IEXC2 can be configured to operate on the same output pin thereby increasing the current source capability to 400 µA.

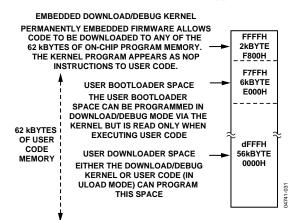

#### **USER DOWNLOAD MODE (ULOAD)**

Figure 28 shows that it is possible to use the 62 kbytes of Flash/EE program memory available to the user as one single block of memory. In this mode, all the Flash/EE memory is read-only to user code.

However, most of the Flash/EE program memory can also be written to during run time simply by entering ULOAD mode. In ULOAD mode, the lower 56 kbytes of program memory can be erased and reprogrammed by the user software as shown in Figure 30. ULOAD mode can be used to upgrade the code in the field via any user-defined download protocol. By configuring the SPI port on the ADuC845/ADuC847/ADuC848 as a slave, it is possible to completely reprogram the 56 kbytes of Flash/EE program memory in under 5 s (see the AN-1074 Application Note).

Alternatively, ULOAD mode can be used to save data to the 56 kbytes of Flash/EE memory. This can be extremely useful in data logging applications where the devices can provide up to 60 kbytes of data memory on-chip (4 kbytes of dedicated Flash/EE data memory also exist).

The upper 6 kbytes of the 62 kbytes of Flash/EE program memory (8 kbytes on the 32-kbyte parts) are programmable only via serial download or parallel programming. This means that this space appears as read-only to user code; therefore, it cannot be accidentally erased or reprogrammed by erroneous code execution, making it very suitable to use the 6 kbytes as a bootloader. A bootload enable option exists in the Windows<sup>®</sup> serial downloader (WSD) to "Always RUN from E000H after Reset." If using a bootloader, this option is recommended to ensure that the bootloader always executes correct code after reset.

Programming the Flash/EE program memory via ULOAD mode is described in the Flash/EE Memory Control SFR section of ECON and also in the AN-1074 Application Note.

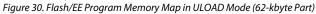

The 32-kbyte memory parts have the user bootload space starting at 6000H. The memory mapping is shown in Figure 31.

Figure 31. Flash/EE Program Memory Map in ULOAD Mode (32-kbyte Part)

ULOAD mode is not available on the 8-kbyte Flash/EE program memory parts.

#### Flash/EE Program Memory Security

The ADuC845/ADuC847/ADuC848 facilitate three modes of Flash/EE program memory security: the lock, secure, and serial safe modes. These modes can be independently activated, restricting access to the internal code space. They can be enabled as part of serial download protocol, as described in the AN-1074 Application Note, or via parallel programming.

#### Lock Mode

This mode locks the code memory, disabling parallel programming of the program memory. However, reading the memory in parallel mode and reading the memory via a MOVC command from external memory are still allowed. This mode is deactivated by initiating an ERASE CODE AND DATA command in serial download or parallel programming modes.

#### Secure Mode

This mode locks the code memory, disabling parallel programming of the program memory. Reading/verifying the memory in parallel mode and reading the internal memory via a MOVC command from external memory are also disabled. This mode is deactivated by initiating an ERASE CODE AND DATA command in serial download or parallel programming modes.

#### Serial Safe Mode

This mode disables serial download capability on the device. If serial safe mode is activated and an attempt is made to reset the device into serial download mode, that is, RESET asserted (pulled high) and de-asserted (pulled low) with PSEN low, the device interprets the serial download reset as a normal reset only. It therefore does not enter serial download mode, but executes only a normal reset sequence. Serial safe mode can be disabled only by initiating an ERASE CODE AND DATA command in parallel programming mode.

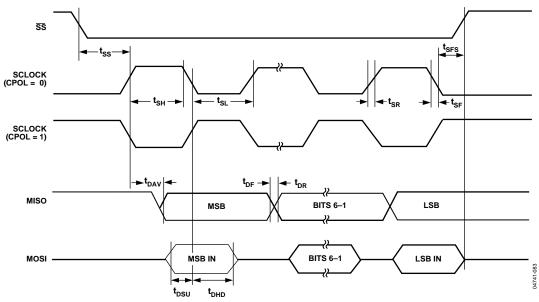

#### **USING THE SPI INTERFACE**

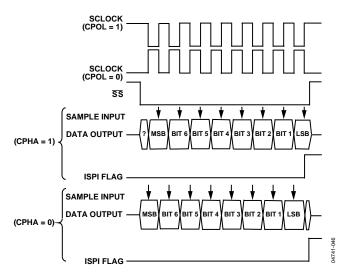

Depending on the configuration of the bits in the SPICON SFR shown in Table 41, the SPI interface transmits or receives data in a number of possible modes. Figure 46 shows all possible ADuC845/ADuC847/ADuC848 SPI configurations and the timing relationships and synchronization among the signals involved. Also shown in this figure is the SPI interrupt bit (ISPI) and how it is triggered at the end of each byte-wide communication.

Figure 46. SPI Timing, All Modes

#### SPI Interface—Master Mode

In master mode, the SCLOCK pin is always an output and generates a burst of eight clocks whenever user code writes to the SPIDAT register. The SCLOCK bit rate is determined by SPR0 and SPR1 in SPICON. Also note that the  $\overline{SS}$  pin is not used in master mode. If the devices need to assert the  $\overline{SS}$  pin on an external slave device, use a port digital output pin.

In master mode, a byte transmission or reception is initiated by a byte write to SPIDAT. The hardware automatically generates eight clock periods via the SCLOCK pin, and the data is transmitted via MOSI. With each SCLOCK period, a data bit is also sampled via MISO. After eight clocks, the transmitted byte is completely transmitted (via MOSI), and the input byte (if required) is waiting in the input shift register (after being received via MISO). The ISPI flag is set automatically, and an interrupt occurs if enabled. The value in the input shift register is latched into SPIDAT.

#### SPI Interface—Slave Mode

In slave mode, the SCLOCK is an input. The  $\overline{SS}$  pin must also be driven low externally during the byte communication. Transmission is also initiated by a write to SPIDAT. In slave mode, a data bit is transmitted via MISO, and a data bit is received via MOSI through each input SCLOCK period. After eight clocks, the transmitted byte is completely transmitted, and the input byte is waiting in the input shift register. The ISPI flag is set automatically, and an interrupt occurs, if enabled. The value in the shift register is latched into SPIDAT only when the transmission/reception of a byte has been completed. The end of transmission occurs after the eighth clock has been received if CPHA = 1, or when  $\overline{SS}$  returns high if CPHA = 0.

#### Mode 3 (9-Bit UART with Variable Baud Rate)

Mode 3 is selected by setting both SM0 and SM1. In this mode, the 8051 UART serial port operates in 9-bit mode with a variable baud rate determined by either Timer 1 or Timer 2. The operation of the 9-bit UART is the same as for Mode 2, but the baud rate can be varied as for Mode 1.

In all four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 when RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1.

#### **UART Serial Port Baud Rate Generation**

#### Mode 0 Baud Rate Generation

The baud rate in Mode 0 is fixed:

Mode 0 Baud Rate =

$$\left(\frac{CoreClockFrequency}{12}\right)$$

#### Mode 2 Baud Rate Generation

The baud rate in Mode 2 depends on the value of the SMOD bit in the PCON SFR. If SMOD = 0, the baud rate is 1/32 of the core clock. If SMOD = 1, the baud rate is 1/16 of the core clock:

*Mode 2 Baud Rate* =  $\frac{2^{SMOD}}{32} \times Core Clock Frequency$

#### Modes 1 and 3 Baud Rate Generation

The baud rates in Modes 1 and 3 are determined by the overflow rate in Timer 1 or Timer 2, or in both (one for transmit and the other for receive).

#### **Timer 1 Generated Baud Rates**

When Timer 1 is used as the baud rate generator, the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD as follows:

*Modes 1 and 3 Baud Rate* =  $\frac{2^{SMOD}}{32} \times Timer 1$  *Overflow Rate*

The Timer 1 interrupt should be disabled in this application. The timer itself can be configured for either timer or counter operation, and in any of its three running modes. In the most typical application, it is configured for timer operation in autoreload mode (high nibble of TMOD = 0010 binary). In that case, the baud rate is given by the formula

Modes 1 and 3 Baud Rate =

$$\frac{2^{SMOD}}{32} \times \frac{CoreClockFrequency}{(256-TH1)}$$

#### Timer 2 Generated Baud Rates

Baud rates can also be generated by using Timer 2. Using Timer 2 is similar to using Timer 1 in that the timer must overflow 16 times before a bit is transmitted or received. Because Timer 2 has a 16-bit autoreload mode, a wider range of baud rates is possible.

Modes 1 and 3 Baud Rate =

$$\frac{1}{16}$$

× Timer 2 Overflow Rate

Therefore, when Timer 2 is used to generate baud rates, the timer increments every two clock cycles rather than every core machine cycle as before. It increments six times faster than Timer 1, and, therefore, baud rates six times faster are possible. Because Timer 2 has 16-bit autoreload capability, very low baud rates are still possible.

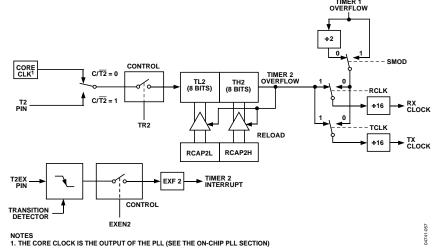

Timer 2 is selected as the baud rate generator by setting the TCLK and/or RCLK in T2CON. The baud rates for transmit and receive can be simultaneously different. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode as shown in Figure 60.

In this case, the baud rate is given by the formula

$Modes \ 1 \ and \ 3 \ Baud \ Rate =$  $Core \ Clock \ Frequency$  $(16 \times [65536 - (RCAP \ 2H : RCAP \ 2L)])$

Figure 60. Timer 2, UART Baud Rates

### **Data Sheet**

| Table 57. Common Baud Rates Using Timer 3 with a 12.58 MHz PLL Clock |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| Ideal Baud   | CD | DIV | T3CON | T3FD | % Error |  |

|--------------|----|-----|-------|------|---------|--|

| 230400       | 0  | 1   | 81H   | 2DH  | 0.18    |  |

|              |    |     |       |      |         |  |

| 115200       | 0  | 2   | 82H   | 2DH  | 0.18    |  |

| 115200       | 1  | 1   | 81H   | 2DH  | 0.18    |  |

| 57600        | 0  | 3   | 83H   | 2DH  | 0.18    |  |

| 57600        | 1  | 2   | 82H   | 2DH  | 0.18    |  |

| 57600        | 2  | 1   | 81H   | 2DH  | 0.18    |  |

|              |    |     |       |      |         |  |

| 38400        | 0  | 4   | 84H   | 12H  | 0.12    |  |

| 38400        | 1  | 3   | 83H   | 12H  | 0.12    |  |

| 38400        | 2  | 2   | 82H   | 12H  | 0.12    |  |

| 38400        | 3  | 1   | 81H   | 12H  | 0.12    |  |

|              |    |     |       |      |         |  |

| 19200        | 0  | 5   | 85H   | 12H  | 0.12    |  |

| 19200        | 1  | 4   | 84H   | 12H  | 0.12    |  |

| 19200        | 2  | 3   | 83H   | 12H  | 0.12    |  |

| 19200        | 3  | 2   | 82H   | 12H  | 0.12    |  |

| 19200        | 4  | 1   | 81H   | 12H  | 0.12    |  |

| 9600         | 0  | 6   | 86H   | 12H  | 0.12    |  |

|              | 1  | 6   |       |      | 0.12    |  |

| 9600<br>9600 |    | 5   | 85H   | 12H  | 0.12    |  |

|              | 2  | 4   | 84H   | 12H  |         |  |

| 9600         | 3  | 3   | 83H   | 12H  | 0.12    |  |

| 9600         | 4  | 2   | 82H   | 12H  | 0.12    |  |

| 9600         | 5  | 1   | 81H   | 12H  | 0.12    |  |

# ADuC845/ADuC847/ADuC848

#### **INTERRUPT SYSTEM**

The ADuC845/ADuC847/ADuC848 provide nine interrupt sources with two priority levels. The control and configuration of the interrupt system is carried out through three interrupt-related SFRs:

| er |

|----|

|    |

- IP Interrupt Priority Register

- IEIP2 Secondary Interrupt Enable Register

#### IE—Interrupt Enable Register

SFR Address:A8HPower-On Default:00HBit Addressable:Yes

#### Table 58. IE SFR Bit Designations

| Bit No. | Name | Description                                                    |

|---------|------|----------------------------------------------------------------|

| 7       | EA   | Set by the user to enable all interrupt sources.               |

|         |      | Cleared by the user to disable all interrupt sources.          |

| 6       | EADC | Set by the user to enable the ADC interrupt.                   |

|         |      | Cleared by the user to disable the ADC interrupt.              |

| 5       | ET2  | Set by the user to enable the Timer 2 interrupt.               |

|         |      | Cleared by the user to disable the Timer 2 interrupt.          |

| 4       | ES   | Set by the user to enable the UART serial port interrupt.      |

|         |      | Cleared by the user to disable the UART serial port interrupt. |

| 3       | ET1  | Set by the user to enable the Timer 1 interrupt.               |

|         |      | Cleared by the user to disable the Timer 1 interrupt.          |

| 2       | EX1  | Set by the user to enable External Interrupt 1 (INT0).         |

|         |      | Cleared by the user to disable External Interrupt 1 (INTO).    |

| 1       | ET0  | Set by the user to enable the Timer 0 interrupt.               |

|         |      | Cleared by the user to disable the Timer 0 interrupt.          |

| 0       | EX0  | Set by the user to enable External Interrupt 0 (INT0).         |

|         |      | Cleared by the user to disable External Interrupt 0 (INTO).    |

#### **IP**—Interrupt Priority Register

SFR Address:B8HPower-On Default:00HBit Addressable:Yes

#### Table 59. IP SFR Bit Designations

| Bit No. | Name | Description                                                            |  |

|---------|------|------------------------------------------------------------------------|--|

| 7       |      | Not Implemented. Write Don't Care.                                     |  |

| 6       | PADC | ADC Interrupt Priority $(1 = High; 0 = Low)$ .                         |  |

| 5       | PT2  | Timer 2 Interrupt Priority (1 = High; 0 = Low).                        |  |

| 4       | PS   | UART Serial Port Interrupt Priority (1 = High; 0 = Low).               |  |

| 3       | PT1  | Timer 1 Interrupt Priority (1 = High; 0 = Low).                        |  |

| 2       | PX1  | $\overline{INTO}$ (External Interrupt 1) priority (1 = High; 0 = Low). |  |

| 1       | PT0  | Timer 0 Interrupt Priority (1 = High; 0 = Low).                        |  |

| 0       | PX0  | $\overline{INT0}$ (External Interrupt 0) Priority (1 = High; 0 = Low). |  |

### HARDWARE DESIGN CONSIDERATIONS

This section outlines some of the key hardware design considerations that must be addressed when integrating the ADuC845/ADuC847/ADuC848 into any hardware system.

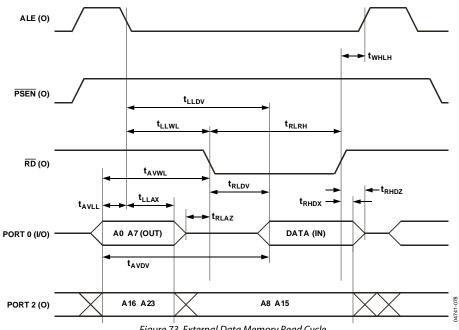

#### **EXTERNAL MEMORY INTERFACE**

In addition to their internal program and data memories, the devices can access up to 16 Mbytes of external data memory (SRAM). No external program memory access is available.

To begin executing code, tie the  $\overline{\text{EA}}$  (external access) pin high. When  $\overline{\text{EA}}$  is high (pulled up to V<sub>DD</sub>—see Figure 70), user program execution starts at Address 0 in the internal 62-kbyte Flash/EE code space. When executing from internal code space, accesses to the program space above F7FFH (62 kbytes) are read as NOP instructions.

Note that a second very important function of the  $\overline{EA}$  pin is described in the Single-Pin Emulation Mode section under the Other Hardware Considerations section.

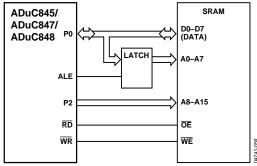

Figure 62 shows a hardware configuration for accessing up to 64 kbytes of external data memory. This interface is standard to any 8051-compatible MCU.

Figure 62. External Data Memory Interface (64-kbyte Address Space)

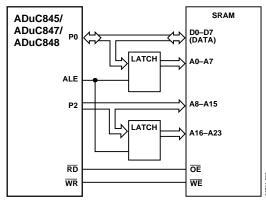

If access to more than 64 kbytes of RAM is desired, a feature unique to the MicroConverter allows addressing up to 16 Mbytes of external RAM simply by adding another latch as shown in Figure 63.

Figure 63. External Data Memory Interface (16-Mbtye Address Space)

In either implementation, Port 0 (P0) serves as a multiplexed address/data bus. It emits the low byte of the data pointer (DPL) as an address, which is latched by ALE prior to data being placed on the bus by the devices (write operation) or the external data memory (read operation). Port 2 (P2) provides the data pointer page byte (DPP) to be latched by ALE, followed by the data pointer high byte (DPH). If no latch is connected to P2, DPP is ignored by the SRAM, and the 8051 standard of 64-kbyte external data memory access is maintained.

The following example shows the code used to write data to external data memory.

MOV DPP, #10h ;Set addr to 100000h MOV DPH, #00h MOV DPL, #00h MOV A, #'B' ;Write Char 'B' (42h) MOVX @DPTR,A ;Move to DPP:DPH:DPL addr

#### **POWER SUPPLIES**

The operational power supply voltage range of the device is 2.7 V to 5.25 V. Although the guaranteed data sheet specifications are given only for power supplies within 2.7 V to 3.6 V and 4.75 V to 5.25 V ( $\pm$ 5% of the nominal 5 V level), the chip functions equally well at any power supply level between 2.7 V and 5.25 V.

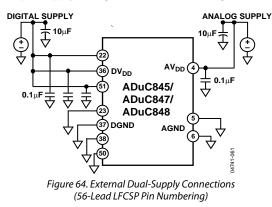

Separate analog and digital power supply pins (AV<sub>DD</sub> and DV<sub>DD</sub>, respectively) allow AV<sub>DD</sub> to be kept relatively free of the noisy digital signals often present on a system DV<sub>DD</sub> line. In this mode, the device can also operate with split supplies, that is, using different voltage supply levels for each supply. For example, the system can be designed to operate with a DV<sub>DD</sub> voltage level of 3 V and the AV<sub>DD</sub> level can be at 5 V, or vice versa, if required. A typical split-supply configuration is shown in Figure 64.

As an alternative to providing two separate power supplies,  $AV_{DD}$  can be kept quiet by placing a small series resistor and/or ferrite bead between it and  $DV_{DD}$ , and then decoupling  $AV_{DD}$  separately to ground. An example of this configuration is shown in Figure 65. In this configuration, other analog circuitry (such

| Yable 65. EXTERNAL DATA MEMORY READ CYCLE Parameter |

|-----------------------------------------------------|

|-----------------------------------------------------|

|                   |                                                   | 12.58 MHz Core Clock |     | 6.29 | 6.29 MHz Core Clock |      |

|-------------------|---------------------------------------------------|----------------------|-----|------|---------------------|------|

|                   |                                                   | Min                  | Max | Min  | Max                 | Unit |

| t <sub>RLRH</sub> | RD Pulse Width                                    | 60                   |     | 125  |                     | ns   |

| t <sub>AVLL</sub> | Address Valid After ALE Low                       | 60                   |     | 120  |                     | ns   |

| t <sub>LLAX</sub> | Address Hold After ALE Low                        | 145                  |     | 290  |                     | ns   |

| t <sub>RLDV</sub> | RD Low to Valid Data In                           |                      | 48  |      | 100                 | ns   |

| trhdx             | Data and Address Hold After RD                    | 0                    |     | 0    |                     | ns   |

| trhdz             | Data Float After RD                               |                      | 150 |      | 625                 | ns   |

| tLLDV             | ALE Low to Valid Data In                          |                      | 170 |      | 350                 | ns   |

| t <sub>AVDV</sub> | Address to Valid Data In                          |                      | 230 |      | 470                 | ns   |

| t <sub>LLWL</sub> | ALE Low to $\overline{RD}$ or $\overline{WR}$ Low | 130                  |     | 255  |                     | ns   |

| tavwl             | Address Valid to RD or WR Low                     | 190                  |     | 375  |                     | ns   |

| t <sub>RLAZ</sub> | RD Low to Address Float                           |                      | 15  |      | 35                  | ns   |

| t <sub>WHLH</sub> | RD or WR High to ALE High                         | 60                   |     | 120  |                     | ns   |

Figure 7<sup>'</sup>3. External Data Memory Read Cycle

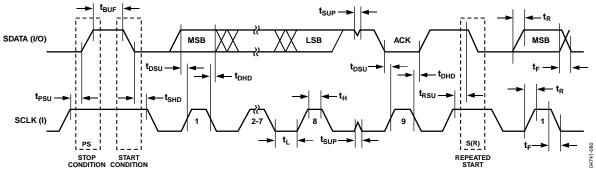

Figure 75. I<sup>2</sup>C-Compatible Interface Timing

#### Table 70. SPI SLAVE MODE TIMING (CPHA = 1) Parameter

|                  |                                          | Min | Тур | Max | Unit |

|------------------|------------------------------------------|-----|-----|-----|------|

| tss              | SS to SCLOCK Edge                        | 0   |     |     | ns   |

| t <sub>sL</sub>  | SCLOCK Low Pulse Width                   |     | 330 |     | ns   |

| t <sub>sн</sub>  | SCLOCK High Pulse Width                  |     | 330 |     | ns   |

| t <sub>DAV</sub> | Data Output Valid After SCLOCK Edge      |     |     | 50  | ns   |

| t <sub>DSU</sub> | Data Input Setup Time Before SCLOCK Edge | 100 |     |     | ns   |

| <b>t</b> DHD     | Data Input Hold Time After SCLOCK Edge   | 100 |     |     | ns   |

| t <sub>DF</sub>  | Data Output Fall Time                    |     | 10  | 25  | ns   |

| t <sub>DR</sub>  | Data Output Rise Time                    |     | 10  | 25  | ns   |

| t <sub>sr</sub>  | SCLOCK Rise Time                         |     | 10  | 25  | ns   |

| t <sub>SF</sub>  | SCLOCK Fall Time                         |     | 10  | 25  | ns   |

| t <sub>SFS</sub> | SS High After SCLOCK Edge                | 0   |     |     | ns   |

Figure 78. SPI Slave Mode Timing (CHPA = 1)

#### **ORDERING GUIDE**

| Model <sup>1, 2, 3</sup> | Temperature Range | Package Description                     | Package Option |

|--------------------------|-------------------|-----------------------------------------|----------------|

| ADuC845BSZ62-5           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 5 V  | S-52-2         |

| ADuC845BSZ62-5-RL        | –40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 5 V  | S-52-2         |

| ADuC845BSZ62-3           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 3 V  | S-52-2         |

| ADuC845BSZ8-5            | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 5 V   | S-52-2         |

| ADuC845BSZ8-5-RL         | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 5 V   | S-52-2         |

| ADuC845BSZ8-3            | –40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 3 V   | S-52-2         |

| ADuC845BCPZ62-5          | –40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 5 V | CP-56-11       |

| ADuC845BCPZ62-3          | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 3 V | CP-56-11       |

| ADuC845BCPZ8-5           | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 5 V  | CP-56-11       |

| ADuC845BCPZ8-3           | –40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 3 V  | CP-56-11       |

| ADuC847BSZ62-5           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 5 V  | S-52-2         |

| ADuC847BSZ62-3           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 3 V  | S-52-2         |

| ADuC847BSZ32-5           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 32-kbyte, 5 V  | S-52-2         |

| ADuC847BSZ32-3           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 32-kbyte, 3 V  | S-52-2         |

| ADuC847BSZ8-5            | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 5 V   | S-52-2         |

| ADuC847BSZ8-3            | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 3 V   | S-52-2         |

| ADuC847BCPZ62-5          | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 5 V | CP-56-11       |

| ADuC847BCPZ62-3          | –40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 3 V | CP-56-11       |

| ADuC847BCPZ8-5           | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 5 V  | CP-56-11       |

| ADuC847BCPZ8-3           | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 3 V  | CP-56-11       |

| ADuC848BSZ62-5           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 5 V  | S-52-2         |

| ADuC848BSZ62-3           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 62-kbyte, 3 V  | S-52-2         |

| ADuC848BSZ32-5           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 32-kbyte, 5 V  | S-52-2         |

| ADuC848BSZ32-3           | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 32-kbyte, 3 V  | S-52-2         |

| ADuC848BSZ8-5            | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 5 V   | S-52-2         |

| ADuC848BSZ8-3            | -40°C to +125°C   | 52-Lead MQFP, Lead Free, 8-kbyte, 3 V   | S-52-2         |

| ADuC848BCPZ62-5          | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 5 V | CP-56-11       |

| ADuC848BCPZ62-3          | –40°C to +85°C    | 56-Lead LFCSP, Lead Free, 62-kbyte, 3 V | CP-56-11       |

| ADuC848BCPZ8-5           | -40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 5 V  | CP-56-11       |

| ADuC848BCPZ8-3           | –40°C to +85°C    | 56-Lead LFCSP, Lead Free, 8-kbyte, 3 V  | CP-56-11       |

| EVAL-ADuC845QSZ          |                   | QuickStart Development System           |                |

| EVAL-ADuC845QSPZ         |                   | QuickStart-PLUS Development System      |                |

| EVAL-ADuC847QSZ          |                   | QuickStart Development System           |                |

| EVAL-ADUC-CABLE1Z        |                   | ADuC Serial Downloader Cable for UART   |                |

$^{1}$  The -3 and -5 in the Model column indicate the  $\mathsf{DV}_{\mathsf{DD}}$  operating voltage.

$^{2}$  Z = RoHS Compliant Part.  $^{3}$  The QuickStart Plus system can only be ordered directly from Accutron. It can be purchased from the website http://www.accutron.com.