#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                             |

|----------------------------|--------------------------------------------------------------------|

| Core Processor             | 8052                                                               |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 12.58MHz                                                           |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                    |

| Number of I/O              | 34                                                                 |

| Program Memory Size        | 8KB (8K x 8)                                                       |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | 4K x 8                                                             |

| RAM Size                   | 2.25K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                      |

| Data Converters            | A/D 10x16b; D/A 1x12b, 2x16b                                       |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                          |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc848bcpz8-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Data Sheet**

# ADuC845/ADuC847/ADuC848

| Parameter                                                     | Min  | Тур  | Max             | Unit   | Test Conditions/Comments                                                      |

|---------------------------------------------------------------|------|------|-----------------|--------|-------------------------------------------------------------------------------|

| TRANSDUCER BURNOUT CURRENT<br>SOURCES                         |      |      |                 |        |                                                                               |

| AIN+ Current                                                  |      | -100 |                 | nA     | AIN+ is the selected positive input (AIN4 or AIN6 only) to the primary ADC    |

| AIN– Current                                                  |      | 100  |                 | nA     | AIN– is the selected negative input (AIN5 or AIN7<br>only) to the primary ADC |

| Initial Tolerance at 25°C                                     |      | ±10  |                 | %      |                                                                               |

| Drift                                                         |      | 0.03 |                 | %/°C   |                                                                               |

| EXCITATION CURRENT SOURCES                                    |      |      |                 |        |                                                                               |

| Output Current                                                |      | 200  |                 | μA     | Available from each current source                                            |

| Initial Tolerance at 25°C                                     |      | ±10  |                 | %      |                                                                               |

| Drift                                                         |      | 200  |                 | ppm/°C |                                                                               |

| Initial Current Matching at 25°C                              |      | ±1   |                 | %      | Matching between both current sources                                         |

| Drift Matching                                                |      | 20   |                 | ppm/°C |                                                                               |

| Line Regulation (AV <sub>DD</sub> )                           |      | 1    |                 | μA/V   | $AV_{DD} = 5 V \pm 5\%$                                                       |

| Load Regulation                                               |      | 0.1  |                 | μA/V   |                                                                               |

| Output Compliance <sup>2</sup>                                | AGND |      | $AV_{DD} - 0.6$ | V      |                                                                               |

| POWER SUPPLY MONITOR (PSM)                                    |      |      |                 |        |                                                                               |

| AV <sub>DD</sub> Trip Point Selection Range                   | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                     |

| AV <sub>DD</sub> Trip Point Accuracy                          |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                       |

|                                                               |      |      | ±4.0            | %      | $T_{MAX} = 125^{\circ}C$                                                      |

| DV <sub>DD</sub> Trip Point Selection Range                   | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                     |

| DV <sub>DD</sub> Trip Point Accuracy                          |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                       |

|                                                               |      |      | ±4.0            | %      | $T_{MAX} = 125^{\circ}C$                                                      |

| CRYSTAL OSCILLATOR (XTAL1 AND XTAL2)                          |      |      |                 |        |                                                                               |

| Logic Inputs, XTAL1 Only <sup>2</sup>                         |      |      |                 |        |                                                                               |

| VINL, Input Low Voltage                                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                               |

| VINH, Input Low Voltage                                       | 3.5  |      |                 | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 2.5  |      |                 | V      | $DV_{DD} = 3 V$                                                               |

| XTAL1 Input Capacitance                                       |      | 18   |                 | pF     |                                                                               |

| XTAL2 Output Capacitance                                      |      | 18   |                 | pF     |                                                                               |

| LOGIC INPUTS                                                  |      |      |                 |        |                                                                               |

| All Inputs Except SCLOCK, RESET,<br>and XTAL1 <sup>2</sup>    |      |      |                 |        |                                                                               |

| VINL, Input Low Voltage                                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                               |

| V <sub>INH</sub> , Input Low Voltage<br>SCLOCK and RESET Only | 2.0  |      |                 | V      |                                                                               |

| (Schmidt Triggered Inputs) <sup>2</sup>                       |      |      |                 |        |                                                                               |

| V <sub>T+</sub>                                               | 1.3  |      | 3.0             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 0.95 |      | 2.5             | V      | $DV_{DD} = 3 V$                                                               |

| V <sub>T-</sub>                                               | 0.8  |      | 1.4             | V      | $DV_{DD} = 5 V$                                                               |

|                                                               | 0.4  |      | 1.1             | V      | $DV_{DD} = 3 V$                                                               |

| $V_{T+} - V_{T-}$                                             | 0.3  |      | 0.85            | V      | $DV_{DD} = 5 V \text{ or } 3 V$                                               |

| Input Currents                                                |      |      |                 |        |                                                                               |

| Port 0, P1.0 to P1.7, EA                                      |      |      | ±10             | μA     | $V_{\text{IN}}=0 \text{ V or } V_{\text{DD}}$                                 |

| RESET                                                         |      |      | ±10             | μA     | $V_{IN} = 0 V, DV_{DD} = 5 V$                                                 |

|                                                               | 35   |      | 105             | μA     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$ , internal pull-down                        |

| Port 2, Port 3                                                |      |      | ±10             | μΑ     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$                                             |

|                                                               | -180 |      | -660            | μΑ     | $V_{IN} = 2 V, DV_{DD} = 5 V$                                                 |

|                                                               | -20  |      | -75             | μΑ     | $V_{IN} = 0.45 \text{ V}, \text{DV}_{DD} = 5 \text{ V}$                       |

| Input Capacitance                                             |      | 10   | -               | pF     | All digital inputs                                                            |

## Data Sheet

## ADuC845/ADuC847/ADuC848

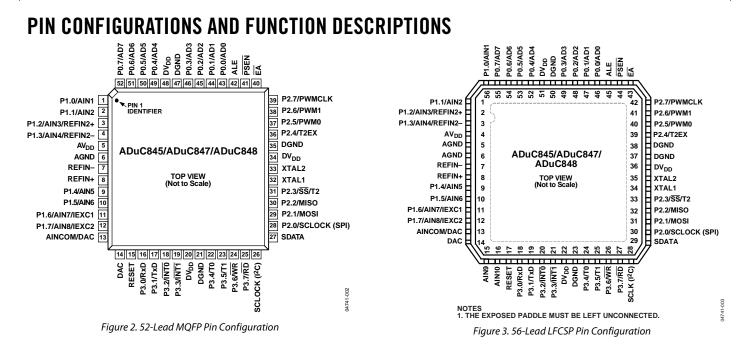

#### **Table 3. Pin Function Descriptions**

| Pin               | No.      |                   |                   |                                                                                                                                                                                                                                                                                      |

|-------------------|----------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP           | 56-LFCSP | Mnemonic          | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                          |

| 1                 | 56       | P1.0/AIN1         | Ι                 | By power-on default, P1.0/AIN1 is configured as the AIN1 analog input.                                                                                                                                                                                                               |

|                   |          |                   |                   | AIN1 can be used as a pseudo differential input when used with AINCOM or as the positive input of a fully differential pair when used with AIN2.                                                                                                                                     |

|                   |          |                   |                   | P1.0 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                               |

| 2                 | 1        | P1.1/AIN2         | 1                 | On power-on default, P1.1/AIN2 is configured as the AIN2 analog input.                                                                                                                                                                                                               |

|                   |          |                   |                   | AIN2 can be used as a pseudo differential input when used with AINCOM or as the negative input of a fully differential pair when used with AIN1.                                                                                                                                     |

|                   |          |                   |                   | P1.1 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                               |

| 3                 | 2        | P1.2/AIN3/REFIN2+ | I                 | On power-on default, P1.2/AIN3 is configured as the AIN3 analog input.                                                                                                                                                                                                               |

|                   |          |                   |                   | AIN3 can be used as a pseudo differential input when used with AINCOM or as the positive input of a fully differential pair when used with AIN4.                                                                                                                                     |

|                   |          |                   |                   | P1.2 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally. This pin also functions as a second external differential reference input, positive terminal. |

| 4                 | 3        | P1.3/AIN4/REFIN2- | I                 | On power-on default, P1.3/AIN4 is configured as the AIN4 analog input.                                                                                                                                                                                                               |

|                   |          |                   |                   | AIN4 can be used as a pseudo differential input when used with AINCOM or as the negative input of a fully differential pair when used with AIN3.                                                                                                                                     |

|                   |          |                   |                   | P1.3 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally. This pin also functions as a second external differential reference input, negative terminal. |

| 5                 | 4        | AV <sub>DD</sub>  | S                 | Analog Supply Voltage.                                                                                                                                                                                                                                                               |

| 6                 | 5        | AGND              | S                 | Analog Ground.                                                                                                                                                                                                                                                                       |

| Not<br>applicable | 6        | AGND              | S                 | A second analog ground is provided with the LFCSP version only.                                                                                                                                                                                                                      |

| 7                 | 7        | REFIN-            | I                 | External Differential Reference Input, Negative Terminal.                                                                                                                                                                                                                            |

| 8                 | 8        | REFIN+            | I                 | External Differential Reference Input, Positive Terminal.                                                                                                                                                                                                                            |

**Data Sheet**

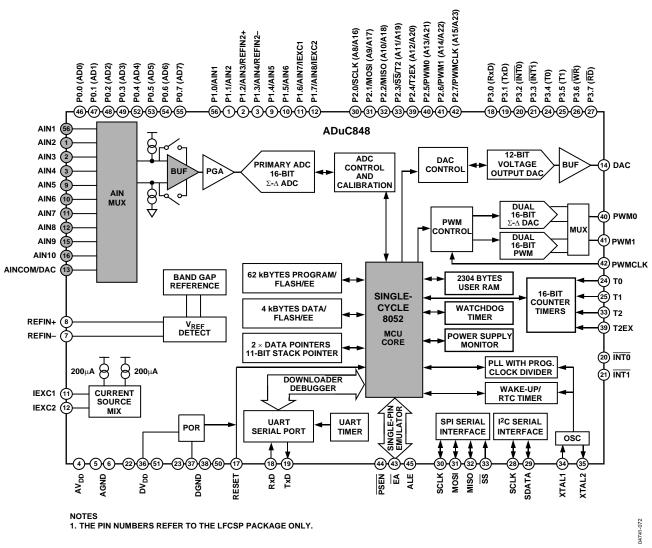

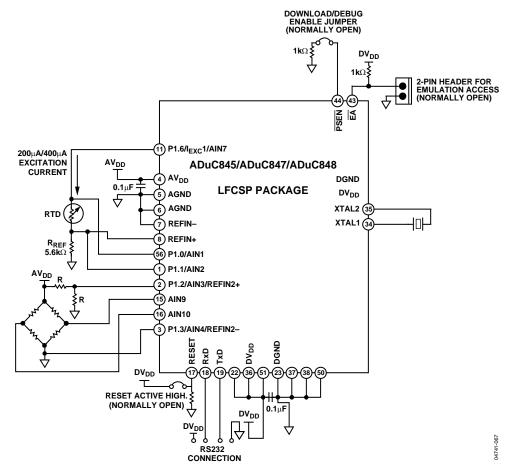

Figure 6. Detailed Block Diagram of the ADuC848

## **8052 INSTRUCTION SET**

Table 4 documents the number of clock cycles required for each instruction. Most instructions are executed in one or two clock cycles resulting in 12.58 MIPs peak performance when operating at PLLCON = 00H.

## TIMER OPERATION

Timers on a standard 8052 increment by one with each machine cycle. On the ADuC845, ADuC847, and ADuC848, one machine cycle is equal to one clock cycle; therefore, the timers increment at the same rate as the core clock.

## ALE

On the ADuC834, the output on the ALE pin is a clock at 1/6th of the core operating frequency. On the ADuC845, ADuC847, and ADuC848, the ALE pin operates as follows. For a single machine cycle instruction, ALE is high for the entire machine cycle. For a two or more machine cycle instruction, ALE is high for the first machine cycle and then low for the remainder of the machine cycles.

## **EXTERNAL MEMORY ACCESS**

The ADuC845, ADuC847, and ADuC848 do not support external program memory access, but the devices can access up to 16 MB (24 address bits) of external data memory. When accessing external RAM, the EWAIT register might need to be programmed to give extra machine cycles to MOVX commands to allow differing external RAM access speeds.

04741-073

## **COMPLETE SFR MAP**

| ISPI WCOL                | SPE           | SPIM<br>FCH 0   | CPOL<br>FBH 0  | CPHA<br>FAH 1  | SPR1<br>F9H 0  | SPR<br>F8H |                   | $\overline{}$ | SPICON<br>F8H 05H | RESERVED                                        | RESERVED                       | DACL                               | DACH                                         | DACCON                                       | RESERVED                        | RESERVED              |

|--------------------------|---------------|-----------------|----------------|----------------|----------------|------------|-------------------|---------------|-------------------|-------------------------------------------------|--------------------------------|------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------------|-----------------------|

| F7H 0 F6H 0              | ) F5H 0       | ) F4H 0         | F3H 0          | F2H 0          | F1H 0          | FOH        | 0 BITS            |               | FOH OOH           | RESERVED                                        | I2CADD1<br>F2H 7FH             | NOT USED                           | RESERVED                                     | RESERVED                                     | RESERVED                        | SPIDAT<br>F7H 00H     |

| MDO MDE<br>EFH 0 EEH 0   | MCO<br>EDH 0  | MDI<br>ECH 0    | I2CM<br>EBH 0  | I2CRS<br>EAH 0 | I2CTX<br>E9H 0 | I2C<br>E8H | BITS              | >             | 12CCON<br>E8H 00H | GN0L <sup>2</sup><br>E9H xxH                    | GN0M <sup>2</sup><br>Eah XXH   | GN0H <sup>2</sup><br>EBH xxH       | GN1L <sup>2</sup><br>ADuC845 ONLY<br>ECH XXH | GN1H <sup>2</sup><br>ADuC845 ONLY<br>EDH XXH | RESERVED                        | RESERVED              |

| E7H 0 E6H 0              | E5H 0         | E4H 0           | E3H 0          | E2H 0          | E1H 0          | E0H        | 0 BITS            | >             | ACC<br>E0H 00H    | OF0L<br>E1H xxH                                 | OF0M<br>E2H xxH                | OF0H<br>E3H xxH                    | OF1L<br>ADuC845 ONLY<br>E4H xxH              | OF1H<br>ADuC845 ONL<br>E5H xxH               | ADC0CON2<br>E6H 00H             | RESERVED              |

| RDY0 RDY1<br>DFH 0 DEH 0 | CAL<br>DDH 0  | NOXREF<br>DCH 0 | ERR0<br>DBH 0  | ERR1<br>DAH 0  | D9H 0          | D8H        | 0 BITS            | }             | ADCSTAT           | ADC0L<br>NOT AVAILABLI<br>ON ADuC848<br>D9H 00H | ADC0M<br>DAH 00H               | ADC0H<br>DBH 00H                   | ADC1M<br>ADuC845 ONLY<br>DCH 00H             | ADC1H<br>ADuC845 ONL<br>DDH 00H              | ADC1L<br>ADuC845 ONL<br>DEH 00H | PSMCON<br>DFH DEH     |

| CY AC<br>D7H 0 D6H 0     | F0<br>D5H 0   | RS1<br>0 D4H 0  | RS0<br>D3H 0   | OV<br>D2H 0    | FI<br>D1H 0    | P<br>D0H   | 0 BITS            | 2             | PSW<br>DOH 00H    | ADCMODE<br>D1H 08H                              | ADC0CON1<br>D2H 07H            | ADC1CON<br>ADuC845 ONLY<br>D3H 00H | SF<br>D4H 45H                                | ICON<br>D5H 00H                              | RESERVED                        | PLLCON<br>D7H 53H     |

| TF2 EXF2<br>CFH 0 CEH 0  | RCLK<br>CDH 0 | TCLK<br>CCH 0   | EXEN2<br>CBH 0 | TR2<br>CAH 0   | СNT2<br>С9Н 0  | CAP<br>C8H | <sup>2</sup> BITS | >             | T2CON<br>C8H 00H  | RESERVED                                        | RCAP2L<br>CAH 00H              | RCAP2H<br>CBH 00H                  | TL2<br>CCH 00H                               | TH2<br>CDH 00H                               | RESERVED                        | RESERVED              |

| PRE3 PRE2<br>C7H 0 C6H 0 | PRE1<br>C5H 0 | PRE0<br>C4H 1   | WDIR<br>C3H 0  | WDS<br>C2H 0   | WDE<br>C1H 0   | WDW<br>COH | VR BITS           | }             | WDCON<br>COH 10H  | RESERVED                                        | CHIPID<br>C2H A0H              | RESERVED                           | RESERVED                                     | RESERVED                                     | EDARL<br>C6H 00H                | EDARH<br>C7H 00H      |

| PADC<br>BFH 0 BEH 0      | PT2<br>BDH 0  | PS<br>BCH 0     | РТ1<br>ВВН 0   | PX1<br>BAH 0   | РТ0<br>В9Н 0   | PX<br>B8H  | D BITS            | $\geq$        | IР<br>IР<br>      | ECON<br>89H 00H                                 | RESERVED                       | RESERVED                           | EDATA1<br>BCH 00H                            | EDATA2<br>BDH 00H                            | EDATA3<br>BEH 00H               | EDATA4<br>BFH 00H     |

| RD WR<br>B7H 1 B6H 1     | T1<br>B5H 1   | T0<br>B4H 1     | INT1<br>B3H 1  | INT0<br>B2H 1  | TxD<br>B1H 1   | RxI<br>B0H | D BITS            | $\geq$        | P3<br>BOH FFH     | PWM0L<br>B1H 00H                                | PWM0H<br>B2H 00H               | PWM1L<br>B3H 00H                   | PWM1H<br>B4H 00H                             | RESERVED                                     | RESERVED                        | SPH<br>87H 00H        |

| EA EADC<br>AFH 0 AEH 0   | ET2<br>ADH 0  | ES<br>ACH 0     | ET1<br>ABH 0   | EX1<br>AAH 0   | ET0<br>A9H 0   | EX<br>A8H  | 0 BITS            | $\geq$        | IE<br>A8H 00H     | IEIP2<br>А9Н А 0Н                               | RESERVED                       | RESERVED                           | RESERVED                                     | RESERVED                                     | PWMCON<br>AEH 00H               | CFG845/7/8<br>AFH 00H |

| A7H 1 A6H 1              | A5H 1         | A4H 1           | A3H 1          | A2H 1          | A1H 1          | A0H        | 1 BITS            |               | P2<br>A0H FFH     | TIMECON<br>A1H 00H                              | HTHSEC <sup>1</sup><br>A2H 00H | SEC <sup>1</sup><br>A3H 00H        | MIN <sup>1</sup><br>A4H 00H                  | HOUR <sup>1</sup><br>A5H 00H                 | INTVAL<br>A6H 00H               | DPCON<br>A7H 00H      |

| SM0 SM1<br>9FH 0 9EH 0   | SM2<br>9DH 0  | REN<br>9CH 0    | ТВ8<br>9ВН 0   | RB8<br>9AH 0   | ТІ<br>99Н 0    | RI<br>98H  | 0 BITS            |               | SCON<br>98H 00H   | SBUF<br>99H 00H                                 | 12CDAT<br>9AH 00H              | 12CADD<br>9BH 55H                  | RESERVED                                     | T3FD<br>9DH 00H                              | T3CON<br>9EH 00H                | EWAIT<br>9FH 00H      |

| 97H 1 96H 1              | 95H 1         | 94H 1           | 93H 1          | 92H 1          | T2EX<br>91H 1  | T2<br>90H  | 1 BITS            | >             | P1<br>90H FFH     | RESERVED                                        | RESERVED                       | RESERVED                           | RESERVED                                     | RESERVED                                     | RESERVED                        | RESERVED              |

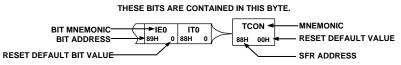

| TF1 TR1<br>8FH 0 8EH 0   | TF0<br>8DH 0  | TR0<br>8CH 0    | IE1<br>8BH 0   | IT1<br>8AH 0   | IE0<br>89Н 0   | IT0<br>88H | BITS              |               | ТСОN<br>88Н 00Н   | ТМОD<br>89Н 00Н                                 | TL0<br>8AH 00H                 | TL1<br>8BH 00H                     | TH0<br>8CH 00H                               | TH1<br>8DH 00H                               | RESERVED                        | RESERVED              |

| 87H 1 86H 1              | 85H 1         | 84H 1           | 83H 1          | 82H 1          | 81H 1          | 80H        | 1 BITS            | $\geq$        | P0<br>80H FFH     | SP<br>81H 07H                                   | DPL<br>82H 00H                 | DPH<br>83H 00H                     | DPP<br>84H 00H                               | RESERVED                                     | RESERVED                        | PCON<br>87H 00H       |

<sup>1</sup> THESE SFRs MAINTAIN THEIR PRE-RESET VALUES AFTER A RESET IF TIMECON.0 = 1. <sup>2</sup> CALIBRATION COEFFICIENTS ARE PRECONFIGURED ON POWER-UP TO FACTORY CALIBRATED VALUES.

SFR MAP KEY:

SFR NOTE: SFRs WHOSE ADDRESSES END IN 0H OR 8H ARE BIT ADDRESSABLE.

Figure 7. Complete SFR Map for the ADuC845, ADuC847, and ADuC848

| Mnemonic                  | Description                              | Bytes | Cycles <sup>1</sup> |

|---------------------------|------------------------------------------|-------|---------------------|

| SJMP rel                  | Short jump (relative address)            | 2     | 3                   |

| JC rel                    | Jump on carry = 1                        | 2     | 3                   |

| JNC rel                   | Jump on carry = 0                        | 2     | 3                   |

| JZ rel                    | Jump on accumulator = 0                  | 2     | 3                   |

| JNZ rel                   | Jump on accumulator ! = 0                | 2     | 3                   |

| DJNZ Rn,rel               | Decrement register, JNZ relative         | 2     | 3                   |

| LJMP                      | Long jump unconditional                  | 3     | 4                   |

| LCALL <sup>3</sup> addr16 | Long jump to subroutine                  | 3     | 4                   |

| JB bit,rel                | Jump on direct bit = 1                   | 3     | 4                   |

| JNB bit,rel               | Jump on direct bit = 0                   | 3     | 4                   |

| JBC bit,rel               | Jump on direct bit = 1 and clear         | 3     | 4                   |

| CJNE A,dir,rel            | Compare A, direct JNE relative           | 3     | 4                   |

| CJNE A,#data,rel          | Compare A, immediate JNE relative        | 3     | 4                   |

| CJNE Rn,#data,rel         | Compare register, immediate JNE relative | 3     | 4                   |

| CJNE @Ri,#data,rel        | Compare indirect, immediate JNE relative | 3     | 4                   |

| DJNZ dir,rel              | Decrement direct byte, JNZ relative      | 3     | 4                   |

| Miscellaneous             |                                          |       |                     |

| NOP                       | No operation                             | 1     | 1                   |

<sup>1</sup> One cycle is one clock.

<sup>2</sup> MOVX instructions are four cycles when they have 0 wait state. Cycles of MOVX instructions are 4 + *n* cycles when they have *n* wait states as programmed via EWAIT. <sup>3</sup> LCALL instructions are three cycles when the LCALL instruction comes from an interrupt.

## **MEMORY ORGANIZATION**

The ADuC845, ADuC847, and ADuC848 contain four memory blocks:

- 62 kbytes/32 kbytes/8 kbytes of on-chip Flash/EE program memory

- 4 kbytes of on-chip Flash/EE data memory

- 256 bytes of general-purpose RAM

- 2 kbytes of internal XRAM

### Flash/EE Program Memory

The devices provide up to 62 kbytes of Flash/EE program memory to run user code. All further references to Flash/EE program memory assume the 62-kbyte option.

When EA is pulled high externally during a power cycle or a hardware reset, the devices default to code execution from their internal 62 kbytes of Flash/EE program memory. The devices do not support the rollover from internal code space to external code space. No external code space is available on the devices. Permanently embedded firmware allows code to be serially downloaded to the 62 kbytes of internal code space via the UART serial port while the device is in-circuit. No external hardware is required.

During run time, 56 kbytes of the 62-kbyte program memory can be reprogrammed. This means that the code space can be upgraded in the field by using a user-defined protocol running on the devices, or it can be used as a data memory. For details, see the Nonvolatile Flash/EE Memory Overview section.

### Flash/EE Data Memory

The user has 4 kbytes of Flash/EE data memory available that can be accessed indirectly by using a group of registers mapped into the special function register (SFR) space. For details, see the Nonvolatile Flash/EE Memory Overview section.

### **General-Purpose RAM**

The general-purpose RAM is divided into two separate memories, the upper and the lower 128 bytes of RAM. The lower 128 bytes of RAM can be accessed through direct or indirect addressing. The upper 128 bytes of RAM can be accessed only through indirect addressing because it shares the same address space as the SFR space, which must be accessed through direct addressing.

The lower 128 bytes of internal data memory are mapped as shown in Figure 8. The lowest 32 bytes are grouped into four banks of eight registers addressed as R0 to R7. The next 16 bytes (128 bits), locations 20H to 2FH above the register banks, form a block of directly addressable bit locations at Bit Addresses 00H to 7FH. The stack can be located anywhere in the internal memory address space, and the stack depth can be expanded up to 2048 bytes.

Reset initializes the stack pointer to location 07H. Any call or push pre-increments the SP before loading the stack. Therefore, loading the stack starts from location 08H, which is also the first register (R0) of Register Bank 1. Thus, if one is going to use more than one register bank, the stack pointer should be initialized to an area of RAM not used for data storage.

## ADC CIRCUIT INFORMATION

The ADuC845 incorporates two 10-channel (8-channel on the MQFP package) 24-bit  $\Sigma$ - $\Delta$  ADCs, while the ADuC847 and ADuC848 each incorporate a single 10-channel (8-channel on the MQFP package) 24-bit and 16-bit  $\Sigma$ - $\Delta$  ADC.

Each device also includes an on-chip programmable gain amplifier and configurable buffering (neither is available on the auxiliary ADC on the ADuC845). The devices also incorporate digital filtering intended for measuring wide dynamic range and low frequency signals such as those in weigh-scale, strain-gage, pressure transducer, or temperature measurement applications.

The ADuC845/ADuC847/ADuC848 can be configured as four or five (MQFP/LFCSP package) fully-differential input channels or as eight or ten (MQFP/LFCSP package) pseudo differential input channels referenced to AINCOM. The ADC on each device (primary only on the ADuC845) can be fully buffered internally, and can be programmed for one of eight input ranges from  $\pm 20$  mV to  $\pm 2.56$  V (V<sub>REF</sub> × 1.024). Buffering the input channel means that the device can handle significant source impedances on the selected analog input and that RC filtering (for noise rejection or RFI reduction) can be placed on the analog inputs. If the ADC is used with internal buffering disabled (ADC0CON1.7 = 1, ADC0CON1.6 = 0), these unbuffered inputs provide a dynamic load to the driving source. Therefore, resistor/capacitor combinations on the inputs can cause dc gain errors, depending on the output impedance of the source that is driving the ADC inputs.

Table 8 and Table 9 show the allowable external resistance/ capacitance values for unbuffered mode such that no gain error at the 16-bit and 20-bit levels, respectively, is introduced. When used with internal buffering enabled, it is recommended that a capacitor (10 nF to 100 nF) be placed on the input to the ADC (usually as part of an antialiasing filter) to aid in noise performance.

The input channels are intended to convert signals directly from sensors without the need for external signal conditioning. With internal buffering disabled (relevant bits set/cleared in ADC0CON1), external buffering might be required.

When the internal buffer is enabled, it might be necessary to offset the negative input channel by +100 mV and to offset the positive channel by -100 mV if the reference range is AV<sub>DD</sub>. This accounts for the restricted common-mode input range in the buffer. Some circuits, for example, bridge circuits, are inherently suitable to use without having to offset where the output voltage is balanced around V<sub>REF</sub>/2 and is not sufficiently large to encroach on the supply rails. Internal buffering is not available on the auxiliary ADC (ADuC845 only). The auxiliary ADC (ADuC845 only) is fixed at a gain range of ±2.50 V.

The ADCs use a  $\Sigma$ - $\Delta$  conversion technique to realize up to 24 bits on the ADuC845 and the ADuC847, and up to 16 bits on the ADuC848 of no missing codes performance (20 Hz update rate, chop enabled). The  $\Sigma$ - $\Delta$  modulator converts the sampled input signal into a digital pulse train whose duty cycle contains the digital information. A sinc<sup>3</sup> programmable low-pass filter (see Table 28) is then used to decimate the modulator output data stream to give a valid data conversion result at programmable output rates. The signal chain has two modes of operation, chop enabled and chop disabled. The CHOP bit in the ADCMODE register enables or disables the chopping scheme.

#### Table 8. Maximum Resistance for No 16-Bit Gain Error (Unbuffered Mode)

|       |          | External Capacitance |         |        |         |         |  |  |  |  |

|-------|----------|----------------------|---------|--------|---------|---------|--|--|--|--|

| Gain  | 0 pF     | 50 pF                | 100 pF  | 500 pF | 1000 pF | 5000 pF |  |  |  |  |

| 1     | 111.3 kΩ | 27.8 kΩ              | 16.7 kΩ | 4.5 kΩ | 2.58 kΩ | 700 Ω   |  |  |  |  |

| 2     | 53.7 kΩ  | 13.5 kΩ              | 8.1 kΩ  | 2.2 kΩ | 1.26 kΩ | 360 Ω   |  |  |  |  |

| 4     | 25.4 kΩ  | 6.4 kΩ               | 3.9 kΩ  | 1.0 kΩ | 600 Ω   | 170 Ω   |  |  |  |  |

| 8–128 | 10.7 kΩ  | 2.9 kΩ               | 1.7 kΩ  | 480 Ω  | 270 Ω   | 75 Ω    |  |  |  |  |

#### Table 9. Maximum Resistance for No 20-Bit Gain Error (Unbuffered Mode)

|       | External Capacitance |         |         |        |         |         |  |  |  |

|-------|----------------------|---------|---------|--------|---------|---------|--|--|--|

| Gain  | 0 pF                 | 50 pF   | 100 pF  | 500 pF | 1000 pF | 5000 pF |  |  |  |

| 1     | 84.9 kΩ              | 21.1 kΩ | 12.5 kΩ | 3.2 kΩ | 1.77 kΩ | 440 Ω   |  |  |  |

| 2     | 42.0 kΩ              | 10.4 kΩ | 6.1 kΩ  | 1.6 kΩ | 880 Ω   | 220 Ω   |  |  |  |

| 4     | 20.5 kΩ              | 5.0 kΩ  | 2.9 kΩ  | 790 Ω  | 430 Ω   | 110 Ω   |  |  |  |

| 8–128 | 8.8 kΩ               | 2.3 k Ω | 1.3 k Ω | 370 Ω  | 195 Ω   | 50 Ω    |  |  |  |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

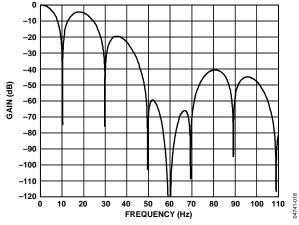

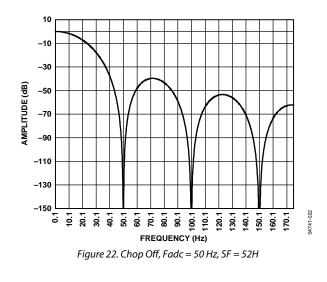

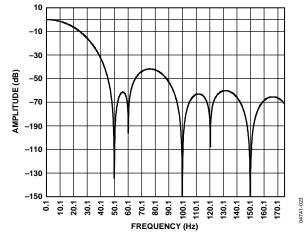

Figure 18. Filter Response, Chop On, SF = 69 Decimal

Figure 19. Filter Response, Chop On, SF = 255 Decimal

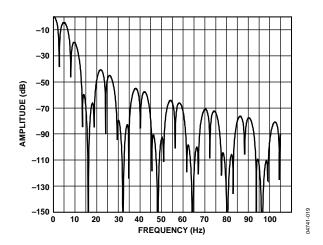

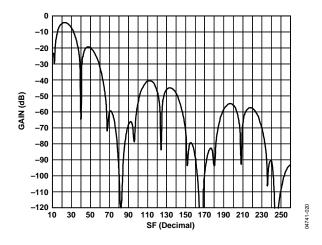

Figure 20. 50 Hz Normal Mode Rejection vs. SF Word, Chop On

Figure 21. 60 Hz Normal Mode Rejection vs. SF, Chop On

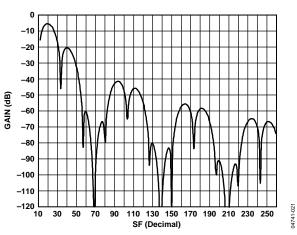

Figure 23. Chop Off, SF = 52H, REJ60 Enabled

## ADCSTAT (ADC STATUS REGISTER)

This SFR reflects the status of both ADCs including data ready, calibration, and various (ADC-related) error and warning conditions including REFIN± reference detect and conversion overflow/underflow flags.

| SFR Address:      | D8H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | Yes |

| Bit No. | Name   | Description                                                                                                                                                                                                                                    |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | RDY0   | Ready Bit for the Primary ADC.                                                                                                                                                                                                                 |

|         |        | Set by hardware on completion of conversion or calibration.                                                                                                                                                                                    |

|         |        | Cleared directly by the user, or indirectly by a write to the mode bits, to start calibration. The primary ADC is inhibited from writing further results to its data or calibration registers until the RDY0 bit is cleared.                   |

| 6       | RDY1   | Ready Bit for Auxiliary (ADuC845 only) ADC.                                                                                                                                                                                                    |

|         |        | Same definition as RDY0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                                              |

| 5       | CAL    | Calibration Status Bit.                                                                                                                                                                                                                        |

|         |        | Set by hardware on completion of calibration.                                                                                                                                                                                                  |

|         |        | Cleared indirectly by a write to the mode bits to start another ADC conversion or calibration.                                                                                                                                                 |

|         |        | Note that calibration with the temperature sensor selected (auxiliary ADC on the ADuC845 only) fails to complete.                                                                                                                              |

| 4       | NOXREF | No External Reference Bit (only active if primary or auxiliary (ADuC845 only) ADC is active).                                                                                                                                                  |

|         |        | Set to indicate that one or both of the REFIN pins is floating or the applied voltage is below a specified threshold. When set, conversion results are clamped to all 1s. Only detects invalid REFIN±, does not check REFIN±.                  |

|         |        | Cleared to indicate valid V <sub>REF</sub> .                                                                                                                                                                                                   |

| 3       | ERRO   | Primary ADC Error Bit.                                                                                                                                                                                                                         |

|         |        | Set by hardware to indicate that the result written to the primary ADC data registers has been clamped to all 0s or all 1s. After a calibration, this bit also flags error conditions that caused the calibration registers not to be written. |

|         |        | Cleared by a write to the mode bits to initiate a conversion or calibration.                                                                                                                                                                   |

| 2       | ERR1   | Auxiliary ADC Error Bit. Same definition as ERR0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                     |

| 1       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

| 0       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

#### Table 23. ADCSTAT SFR Bit Designation

## SF (ADC SINC FILTER CONTROL REGISTER)

The SF register is used to configure the decimation factor for the ADC, and therefore, has a direct influence on the ADC throughput rate.

| SFR Address:      | D4H |

|-------------------|-----|

| Power-On Default: | 45H |

| Bit Addressable:  | No  |

#### Table 28. Sinc Filter SFR Bit Designations

| SF.7 | SF.6 | SF.5 | SF.4 | SF.3 | SF.2 | SF.1 | SF.0 |

|------|------|------|------|------|------|------|------|

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    |

The bits in this register set the decimation factor of the ADC. This has a direct bearing on the throughput rate of the ADC along with the chop setting. The equations used to determine the ADC throughput rate are

Fadc (Chop On) =  $\frac{1}{3 \times 8 \times SFword} \times 32.768 \text{ kHz}$

where SFword is in decimal.

Fadc (Chop Off) =

$$\frac{1}{8 \times SFword} \times 32.768 \text{ kHz}$$

where SFword is in decimal.

#### Table 29. SF SFR Bit Examples Chop Enabled (ADCMODE.3 = 0)

| Chop Enabled (AL | chop Enabled (Abcinobels - 6) |           |           |              |  |  |  |  |  |  |  |

|------------------|-------------------------------|-----------|-----------|--------------|--|--|--|--|--|--|--|

| SF (Decimal)     | SF (Hexadecimal)              | Fadc (Hz) | Tadc (ms) | Tsettle (ms) |  |  |  |  |  |  |  |

| 13 <sup>1</sup>  | 0D                            | 105.3     | 9.52      | 19.04        |  |  |  |  |  |  |  |

| 69               | 45                            | 19.79     | 50.53     | 101.1        |  |  |  |  |  |  |  |

| 82               | 52                            | 16.65     | 60.06     | 120.1        |  |  |  |  |  |  |  |

| 255              | FF                            | 5.35      | 186.77    | 373.54       |  |  |  |  |  |  |  |

### Chop Disabled (ADCMODE.3 = 1)

| SF (Decimal) | SF (Hexadecimal) | Fadc (Hz) | Tadc (ms) | Tsettle (ms) |

|--------------|------------------|-----------|-----------|--------------|

| 3            | 03               | 1365.3    | 0.73      | 2.2          |

| 69           | 45               | 59.36     | 16.84     | 50.52        |

| 82           | 52               | 49.95     | 20.02     | 60.06        |

| 255          | FF               | 16.06     | 62.25     | 186.8        |

<sup>1</sup> With chop enabled, if an SF word smaller than 13 is written to this SF register, the filter automatically defaults to 13.

During ADC calibration, the user-programmed value of SF word is used. The SF word does not default to the maximum setting (255) as it did on previous MicroConverter<sup>®</sup> products. However, for optimum calibration results, it is recommended that the maximum SF word be set.

#### I2CADD-I<sup>2</sup>C Address Register 1

Function:

SFR Address:

Holds one of the I<sup>2</sup>C peripheral addresses for the device. It may be overwritten by user code. The uC001 Application Note describes the format of the I<sup>2</sup>C standard 7-bit address. 9BH

| Power-On Default: | 55H |

|-------------------|-----|

| Bit Addressable:  | No  |

#### I2CADD1-I<sup>2</sup>C Address Register 2

| Function:         | Same as the I2CADD. |

|-------------------|---------------------|

| SFR Address:      | F2H                 |

| Power-On Default: | 7FH                 |

| Bit Addressable:  | No                  |

#### I2CDAT-I<sup>2</sup>C Data Register

Function:The I2CDAT SFR is written to by user code to transmit data, or read by user code to read data just received by<br/>the I²C interface. Accessing I2CDAT automatically clears any pending I²C interrupt and the I2CI bit in the<br/>I2CCON SFR. User code should access I2CDAT only once per interrupt cycle.SFR Address:9AHPower-On Default:00HBit Addressable:No

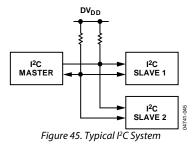

The main features of the MicroConverter I<sup>2</sup>C interface are

- Only two bus lines are required: a serial data line (SDATA) and a serial clock line (SCLOCK).

- An I<sup>2</sup>C master can communicate with multiple slave devices. Because each slave device has a unique 7-bit address, single master/slave relationships can exist at all times even in a multislave environment.

- The ability to respond to two separate addresses when operating in slave mode.

- On-chip filtering rejects <50 ns spikes on the SDATA and the SCLOCK lines to preserve data integrity.

### Software Master Mode

The ADuC845/ADuC847/ADuC848 can be used as an I<sup>2</sup>C master device by configuring the I<sup>2</sup>C peripheral in master mode and writing software to output the data bit-by-bit. This is referred to as a software master. Master mode is enabled by setting the I2CM bit in the I2CCON register.

To transmit data on the SDATA line, MDE must be set to enable the output driver on the SDATA pin. If MDE is set, the SDATA pin is pulled high or low depending on whether the MDO bit is set or cleared. MCO controls the SCLOCK pin and is always configured as an output in master mode. In master mode, the SCLOCK pin is pulled high or low depending on the whether MCO is set or cleared.

To receive data, MDE must be cleared to disable the output driver on SDATA. Software must provide the clocks by toggling the MCO bit and reading the SDATA pin via the MDI bit. If MDE is cleared, MDI can be used to read the SDATA pin. The value of the SDATA pin is latched into MDI on a rising edge of SCLOCK. MDI is set if the SDATA pin is high on the last rising edge of SCLOCK. MDI is cleared if the SDATA pin is low on the last rising edge of SCLOCK.

Software must control MDO, MCO, and MDE appropriately to generate the start condition, slave address, acknowledge bits, data bytes, and stop conditions. These functions are described in the uC001 Application Note.

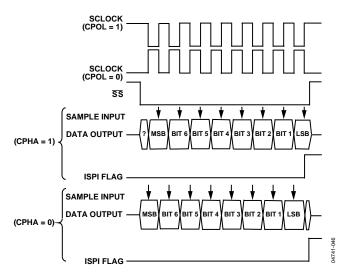

### **USING THE SPI INTERFACE**

Depending on the configuration of the bits in the SPICON SFR shown in Table 41, the SPI interface transmits or receives data in a number of possible modes. Figure 46 shows all possible ADuC845/ADuC847/ADuC848 SPI configurations and the timing relationships and synchronization among the signals involved. Also shown in this figure is the SPI interrupt bit (ISPI) and how it is triggered at the end of each byte-wide communication.

Figure 46. SPI Timing, All Modes

### SPI Interface—Master Mode

In master mode, the SCLOCK pin is always an output and generates a burst of eight clocks whenever user code writes to the SPIDAT register. The SCLOCK bit rate is determined by SPR0 and SPR1 in SPICON. Also note that the  $\overline{SS}$  pin is not used in master mode. If the devices need to assert the  $\overline{SS}$  pin on an external slave device, use a port digital output pin.

In master mode, a byte transmission or reception is initiated by a byte write to SPIDAT. The hardware automatically generates eight clock periods via the SCLOCK pin, and the data is transmitted via MOSI. With each SCLOCK period, a data bit is also sampled via MISO. After eight clocks, the transmitted byte is completely transmitted (via MOSI), and the input byte (if required) is waiting in the input shift register (after being received via MISO). The ISPI flag is set automatically, and an interrupt occurs if enabled. The value in the input shift register is latched into SPIDAT.

### SPI Interface—Slave Mode

In slave mode, the SCLOCK is an input. The  $\overline{SS}$  pin must also be driven low externally during the byte communication. Transmission is also initiated by a write to SPIDAT. In slave mode, a data bit is transmitted via MISO, and a data bit is received via MOSI through each input SCLOCK period. After eight clocks, the transmitted byte is completely transmitted, and the input byte is waiting in the input shift register. The ISPI flag is set automatically, and an interrupt occurs, if enabled. The value in the shift register is latched into SPIDAT only when the transmission/reception of a byte has been completed. The end of transmission occurs after the eighth clock has been received if CPHA = 1, or when  $\overline{SS}$  returns high if CPHA = 0.

#### INTVAL—User Timer Interval Select Register

Function:

User code writes the required time interval to this register. When the 8-bit interval counter is equal to the time interval value loaded in the INTVAL SFR, the TII bit (TIMECON.2) is set and generates an interrupt, if enabled.

SFR Address:A6HPower-On Default:00HBit Addressable:NoValid Value:0 to 255 decimal

#### HTHSEC—Hundredths of Seconds Time Register

| Function:         | This register is incremented in 1/128-second intervals once TCEN in TIMECON is active. The HTHSEC SFR counts from 0 to 127 before rolling over to increment the SEC time register. |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Address:      | A2H                                                                                                                                                                                |

| Power-On Default: | 00H                                                                                                                                                                                |

| Bit Addressable:  | No                                                                                                                                                                                 |

| Valid Value:      | 0 to 127 decimal                                                                                                                                                                   |

|                   |                                                                                                                                                                                    |

#### SEC—Seconds Time Register

| Function:         | This register is incremented in 1-second intervals once TCEN in TIMECON is active. The SEC SFR counts from 0 to 59 before rolling over to increment the MIN time register. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Address:      | A3H                                                                                                                                                                        |

| Power-On Default: | 00H                                                                                                                                                                        |

| Bit Addressable:  | No                                                                                                                                                                         |

| Valid Value:      | 0 to 59 decimal                                                                                                                                                            |

#### MIN-Minutes Time Register

| Function          | This register is incremented in 1-minute intervals once TCEN in TIMECON is active. The MIN SFR counts from 0 to 59 before rolling over to increment the HOUR time register. |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Address:      | A4H                                                                                                                                                                         |

| Power-On Default: | 00H                                                                                                                                                                         |

| Bit Addressable:  | No                                                                                                                                                                          |

| Valid Value:      | 0 to 59 decimal                                                                                                                                                             |

|                   |                                                                                                                                                                             |

#### HOUR-Hours Time Register

| Function:         | This register is incremented in 1-hour intervals once TCEN in TIMECON is active. The HOUR SFR counts from 0 to 23 before rolling over to 0. |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SFR Address:      | A5H                                                                                                                                         |

| Power-On Default: | 00H                                                                                                                                         |

| Bit Addressable:  | No                                                                                                                                          |

| Valid Value:      | 0 to 23 decimal                                                                                                                             |

To enable the TIC as a real-time clock, the HOUR, MIN, SEC, and HTHSEC registers can be loaded with the current time. Once the TCEN bit is high, the TIC starts. To use the TIC as a time interval counter, select the count interval—hundredths of seconds, seconds, minutes, and hours via the ITS0 and ITS1 bits in the TIMECON SFR. Load the count required into the INTVAL SFR.

Note that INTVAL is only an 8-bit register, so user software must take into account any intervals longer than are possible with 8 bits. Therefore, to count an interval of 20 seconds, use the following procedure:

MOV TIMECON, #0D0H ;Enable 24Hour mode, count seconds, Clear TCEN. MOV INTVAL, #14H ;Load INTVAL with required count interval...in this case 14H = 20 MOV TIMECON, #0D3H ;Start TIC counting and enable the 8bit INTVAL counter.

## **8052-COMPATIBLE ON-CHIP PERIPHERALS**

This section gives a brief overview of the various secondary peripheral circuits that are available to the user on-chip. These features are mostly 8052-compatible (with a few additional features) and are controlled via standard 8052 SFR bit definitions.

## Parallel I/O

The ADuC845/ADuC847/ADuC848 use four input/output ports to exchange data with external devices. In addition to performing general-purpose I/O, some are capable of external memory operations, while others are multiplexed with alternate functions for the peripheral functions available on-chip. In general, when a peripheral is enabled, that pin cannot be used as a general-purpose I/O pin.

### Port 0

Port 0 is an 8-bit open-drain bidirectional I/O port that is directly controlled via the Port 0 SFR (80H). Port 0 is also the multiplexed low-order address and data bus during accesses to external data memory.

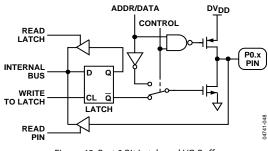

Figure 48 shows a typical bit latch and I/O buffer for a Port 0 pin. The bit latch (one bit in the SFRof the port) is represented as a Type D flip-flop, which clocks in a value from the internal bus in response to a write to latch signal from the CPU. The Q output of the flip-flop is placed on the internal bus in response to a read latch signal from the CPU. The level of the port pin itself is placed on the internal bus in response to a read pin signal from the CPU. Some instructions that read a port activate the read latch signal, and others activate the read pin signal. See the Read-Modify-Write Instructions section for details.

Figure 48. Port 0 Bit Latch and I/O Buffer

As shown in Figure 48, the output drivers of Port 0 pins are switchable to an internal ADDR and ADDR/DATA bus by an internal control signal for use in external memory accesses. During external memory accesses, the P0 SFR has 1s written to it; therefore, all its bit latches become 1. When accessing external memory, the control signal in Figure 48 goes high, enabling push-pull operation of the output pin from the internal address or data bus (ADDR/DATA line). Therefore, no external pullups are required on Port 0 for it to access external memory. In general-purpose I/O port mode, Port 0 pins that have 1s written to them via the Port 0 SFR are configured as open-drain and, therefore, float. In this state, Port 0 pins can be used as high impedance inputs. This is represented in Figure 48 by the NAND gate whose output remains high as long as the control signal is low, thereby disabling the top FET. External pull-up resistors are, therefore, required when Port 0 pins are used as general-purpose outputs. Port 0 pins with 0s written to them drive a logic low output voltage (Vol.) and are capable of sinking 1.6 mA.

### Port 1

Port 1 is also an 8-bit port directly controlled via the P1 SFR (90H). Port 1 digital output capability is not supported on this device. Port 1 pins can be configured as digital inputs or analog inputs. By (power-on) default, these pins are configured as analog inputs, that is, 1 is written to the corresponding Port 1 register bit. To configure any of these pins as digital inputs, the user should write a 0 to these port bits to configure the corresponding pin as a high impedance digital input. These pins also have various secondary functions aside from their analog input capability, as described in Table 46.

Table 46. Port 1 Alternate Functions

| Pin No. | Alternate Function                         |

|---------|--------------------------------------------|

| P1.2    | REFIN2+ (second reference input, postive)  |

| P1.3    | REFIN2– (second reference input, negative) |

| P1.6    | IEXC1 (200 μA excitation current source)   |

| P1.7    | IEXC2 (200 µA excitation current source)   |

Figure 49. Port 1 Bit Latch and I/O Buffer

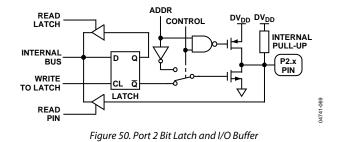

## Port 2

Port 2 is a bidirectional port with internal pull-up resistors directly controlled via the P2 SFR. Port 2 also emits the middleand high-order address bytes during accesses to the 24-bit external data memory space.

In general-purpose I/O port mode, Port 2 pins that have 1s written to them are pulled high by the internal pull-ups as shown in Figure 50 and, in that state, can be used as inputs. As inputs, Port 2 pins pulled externally low source current because of the internal pull-up resistors. Port 2 pins with 0s written to them drive a logic low output voltage (VoL) and are capable of sinking 1.6 mA.

P2.5 and P2.6 can also be used as PWM outputs, while P2.7 can act as an alternate PWM clock source. When selected as the PWM outputs, they overwrite anything written to P2.5 or P2.6.

#### Table 47. Port 2 Alternate Functions

| Pin No. | Alternate Function            |

|---------|-------------------------------|

| P2.0    | SCLOCK for SPI                |

| P2.1    | MOSI for SPI                  |

| P2.2    | MISO for SPI                  |

| P2.3    | SS and T2 clock input         |

| P2.4    | T2EX alternate control for T2 |

| P2.5    | PWM0 output                   |

| P2.6    | PWM1 output                   |

| P2.7    | PWMCLK                        |

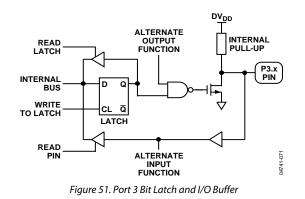

#### Port 3

Port 3 is a bidirectional port with internal pull-ups directly controlled via the P3 SFR (B0H). Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and, in that state, can be used as inputs. As inputs, Port 3 pins pulled externally low source current because of the internal pull-ups.

Port 3 pins with 0s written to them drive a logic low output voltage ( $V_{OL}$ ) and are capable of sinking 4 mA. Port 3 pins also have various secondary functions as described in Table 48. The alternate functions of Port 3 pins can be activated only if the corresponding bit latch in the P3 SFR contains a 1. Otherwise, the port pin remains at 0.

| Table 48. | Port 3 | Alternate | Functions |

|-----------|--------|-----------|-----------|

|-----------|--------|-----------|-----------|

| Pin No. | Alternate Function                                      |

|---------|---------------------------------------------------------|

| P3.0    | RxD (UART input pin, or serial data I/O in Mode 0)      |

| P3.1    | TxD (UART output pin, or serial clock output in Mode 0) |

| P3.2    | INT0 (External Interrupt 0)                             |

| P3.3    | INT1 (External Interrupt 1)                             |

| P3.4    | T0 (Timer/Counter 0 external input)                     |

| P3.5    | T1 (Timer/Counter 1 external input)                     |

| P3.6    | WR (external data memory write strobe)                  |

| P3.7    | RD (external data memory read strobe)                   |

### **Read-Modify-Write Instructions**

Some 8051 instructions read the latch while others read the pin. The instructions that read the latch rather than the pins are the ones that read a value, possibly change it, and rewrite it to the latch. These are called read-modify-write instructions, which are listed in Table 49. When the destination operand is a port or a port bit, these instructions read the latch rather than the pin.

#### Table 49. Read-Modify-Write Instructions

| ·                        |                                                                |  |

|--------------------------|----------------------------------------------------------------|--|

| Instruction              | Description                                                    |  |

| ANL                      | Logical AND, for example, ANL P1, A                            |  |

| ORL                      | Logical OR, for example, ORL P2, A                             |  |

| XRL                      | Logical EX-OR, for example, XRL P3, A                          |  |

| JBC                      | Jump if Bit = 1 and clear bit, for example, JBC<br>P1.1, LABEL |  |

| CPL                      | Complement bit, for example, CPL P3.0                          |  |

| INC                      | Increment, for example, INC P2                                 |  |

| DEC                      | Decrement, for example, DEC P2                                 |  |

| DJNZ                     | Decrement and jump if not zero, for example,<br>DJNZ P3, LABEL |  |

| MOV PX.Y, C <sup>1</sup> | Move Carry to Bit Y of Port X                                  |  |

| CLR PX.Y <sup>1</sup>    | Clear Bit Y of Port X                                          |  |

| SETB PX.Y <sup>1</sup>   | Set Bit Y of Port X                                            |  |

|                          |                                                                |  |

<sup>1</sup>These instructions read the port byte (all 8 bits), modify the addressed bit, and write the new byte back to the latch.

Read-modify-write instructions are directed to the latch rather than to the pin to avoid a possible misinterpretation of the voltage level of a pin. For example, a port pin might be used to drive the base of a transistor. When 1 is written to the bit, the transistor is turned on. If the CPU reads the same port bit at the pin rather than the latch, it reads the base voltage of the transistor and interprets it as Logic 0. Reading the latch rather than the pin returns the correct value of 1.

## **INTERRUPT SYSTEM**

The ADuC845/ADuC847/ADuC848 provide nine interrupt sources with two priority levels. The control and configuration of the interrupt system is carried out through three interrupt-related SFRs:

| er |

|----|

|    |

- IP Interrupt Priority Register

- IEIP2 Secondary Interrupt Enable Register

#### IE—Interrupt Enable Register

SFR Address:A8HPower-On Default:00HBit Addressable:Yes

## Table 58. IE SFR Bit Designations

| Bit No. | Name | Description                                                    |

|---------|------|----------------------------------------------------------------|

| 7       | EA   | Set by the user to enable all interrupt sources.               |

|         |      | Cleared by the user to disable all interrupt sources.          |

| 6       | EADC | Set by the user to enable the ADC interrupt.                   |

|         |      | Cleared by the user to disable the ADC interrupt.              |

| 5       | ET2  | Set by the user to enable the Timer 2 interrupt.               |

|         |      | Cleared by the user to disable the Timer 2 interrupt.          |

| 4       | ES   | Set by the user to enable the UART serial port interrupt.      |

|         |      | Cleared by the user to disable the UART serial port interrupt. |

| 3       | ET1  | Set by the user to enable the Timer 1 interrupt.               |

|         |      | Cleared by the user to disable the Timer 1 interrupt.          |

| 2       | EX1  | Set by the user to enable External Interrupt 1 (INT0).         |

|         |      | Cleared by the user to disable External Interrupt 1 (INTO).    |

| 1       | ET0  | Set by the user to enable the Timer 0 interrupt.               |

|         |      | Cleared by the user to disable the Timer 0 interrupt.          |

| 0       | EX0  | Set by the user to enable External Interrupt 0 (INT0).         |

|         |      | Cleared by the user to disable External Interrupt 0 (INTO).    |

#### **IP**—Interrupt Priority Register

SFR Address:B8HPower-On Default:00HBit Addressable:Yes

### Table 59. IP SFR Bit Designations

| Bit No. | Name | Description                                                            |  |  |

|---------|------|------------------------------------------------------------------------|--|--|

| 7       |      | Not Implemented. Write Don't Care.                                     |  |  |

| 6       | PADC | ADC Interrupt Priority $(1 = High; 0 = Low)$ .                         |  |  |

| 5       | PT2  | Timer 2 Interrupt Priority (1 = High; 0 = Low).                        |  |  |

| 4       | PS   | UART Serial Port Interrupt Priority (1 = High; 0 = Low).               |  |  |

| 3       | PT1  | Timer 1 Interrupt Priority (1 = High; 0 = Low).                        |  |  |

| 2       | PX1  | $\overline{INTO}$ (External Interrupt 1) priority (1 = High; 0 = Low). |  |  |

| 1       | PT0  | Timer 0 Interrupt Priority (1 = High; 0 = Low).                        |  |  |

| 0       | PX0  | $\overline{INT0}$ (External Interrupt 0) Priority (1 = High; 0 = Low). |  |  |

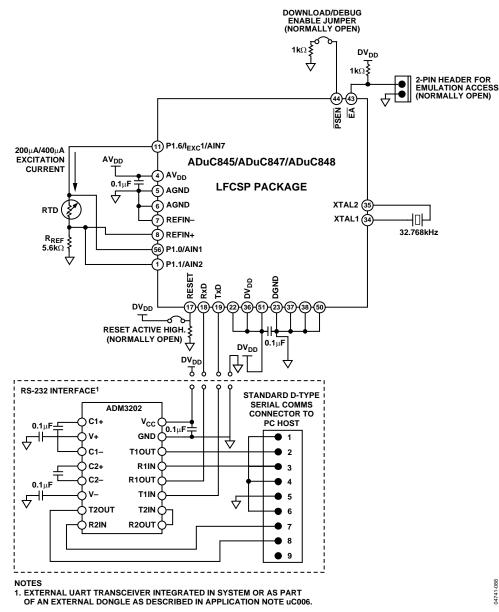

Figure 70. UART Connectivity in Typical System

In addition to the basic UART connections, users also need a way to trigger the chip into download mode. This is accomplished via a 1 k $\Omega$  pull-down resistor that can be jumpered onto the PSEN pin, as shown in Figure 70. To get the devices into download mode, connect this jumper and power-cycle the device (or manually reset the device, if a manual reset button is available), and it is ready to receive a new program serially. With the jumper removed, the device powers on in normal mode (and runs the program) whenever power is cycled or RESET is toggled. Note that PSEN is normally an output and that it is sampled as an input only on the falling edge of RESET, that is, at power-on or upon an external manual reset. Note also that if any external circuitry unintentionally pulls PSEN low during power-on or reset events, it may cause the chip to enter download mode and fail to begin user code execution. To

prevent this, ensure that no external signals are capable of pulling the  $\overrightarrow{\text{PSEN}}$  pin low, except for the external  $\overrightarrow{\text{PSEN}}$  jumper itself or the method of download entry in use during a reset or power-cycle condition.

#### Embedded Serial Port Debugger

From a hardware perspective, entry to serial port debug mode is identical to the serial download entry sequence described previously. In fact, both serial download and serial port debug modes are essentially one mode of operation used in two different ways.

The serial port debugger is fully contained on the device, unlike ROM monitor type debuggers, and, therefore, no external memory is needed to enable in-system debug sessions.

## Single-Pin Emulation Mode

Built into the ADuC845/ADuC847/ADuC848 is a dedicated controller for single-pin in-circuit emulation (ICE). In this mode, emulation access is gained by connection to a single pin, the EA pin. Normally on the 8051 standard, this pin is hardwired either high or low to select execution from internal or external program memory space. Note that external program memory or execution from external program memory is not allowed on the devices. To enable single-pin emulation mode, users need to pull the  $\overline{EA}$  pin high through a 1 k $\Omega$  resistor as shown in Figure 70. The emulator then connects to the 2-pin header also shown in Figure 70. To be compatible with the standard connector that comes with the single-pin emulator available from Accutron Limited (www.accutron.com), use a 2-pin 0.1-inch pitch Friction Lock header from Molex (www.molex.com) such as part number 22-27-2021. Be sure to observe the polarity of this header. As shown in Figure 70, when the Friction Lock tab is at the right, the ground pin should be the lower of the two pins when viewed from the top.

## **Typical System Configuration**

A typical ADuC845/ADuC847/ADuC848 configuration is shown in Figure 70. Figure 70 also includes connections for a typical analog measurement application of the devices, namely an interface to a resistive temperature device (RTD). The arrangement shown is commonly referred to as a 4-wire RTD configuration. Here, the on-chip excitation current sources are enabled to excite the sensor. The excitation current flows directly through the RTD generating a voltage across the RTD proportional to its resistance. This differential voltage is routed directly to one set of the positive and negative inputs of the ADC (AIN1, AIN2, respectively in this case). The same current that excited the RTD also flows through a series resistance,  $R_{REF}$ , generating a ratiometric voltage reference,  $V_{REF}$ . The ratiometric voltage reference ensures that variations in the excitation current do not affect the measurement system since the input voltage from the RTD and reference voltage across  $R_{REF}$  vary ratiometrically with the excitation current. Resistor  $R_{REF}$  must, however, have a low temperature coefficient to avoid errors in the reference voltage overtemperature.  $R_{REF}$  must also be large enough to generate at least a 1 V voltage reference.

The preceding example shows just a single differential ADC connection using a single reference input pair. The ADuC845/ ADuC847/ADuC848 have the capability of connecting to five differential inputs directly or ten single-ended inputs (LFCSP package only) as well as having a second reference input. This arrangement means that different sensors with different reference ranges can be connected to the device with the need for external multiplexing circuitry. This arrangement is shown in Figure 71. The bridge sensor shown can be a load cell or a pressure sensor. The RTD is shown using a reference voltage derived from the  $R_{REF}$  resistor via the REFIN± inputs, and the bridge sensor is shown using a divided down AV<sub>DD</sub> reference via the REFIN2± inputs.

Figure 71. Dual Reference Typical Connectivity

### Table 66. EXTERNAL DATA MEMORY WRITE CYCLE Parameter

|                     |                                                                   | 12.58 MHz Core Clock |     | 6.29 MHz Core Clock |     |      |  |

|---------------------|-------------------------------------------------------------------|----------------------|-----|---------------------|-----|------|--|

|                     |                                                                   | Min                  | Max | Min                 | Max | Unit |  |

| t <sub>wlwH</sub>   | WR Pulse Width                                                    | 65                   |     | 130                 |     | ns   |  |

| t <sub>AVLL</sub>   | Address Valid After ALE Low                                       | 60                   |     | 120                 |     | ns   |  |

| t <sub>LLAX</sub>   | Address Hold After ALE Low                                        | 65                   |     | 135                 |     | ns   |  |