Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8052                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 12.58MHz                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                   |

| Number of I/O              | 34                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | 4K x 8                                                            |

| RAM Size                   | 2.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                       |

| Data Converters            | A/D 10x16b; D/A 1x12b, 2x16b                                      |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 52-QFP                                                            |

| Supplier Device Package    | 52-MQFP (10x10)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc848bsz8-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SPECIFICATIONS<sup>1</sup>

$AV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V,  $DV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V, REFIN(-) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz crystal; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Input buffer on for primary ADC, unless otherwise noted. Core speed = 1.57 MHz (default CD = 3), unless otherwise noted.

| Parameter                                         | Min       | Тур                                     | Max  | Unit              | Test Conditions/Comments                                                                                                   |

|---------------------------------------------------|-----------|-----------------------------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| PRIMARY ADC                                       |           |                                         |      |                   |                                                                                                                            |

| Conversion Rate                                   | 5.4       |                                         | 105  | Hz                | Chop on (ADCMODE.3 = $0$ )                                                                                                 |

|                                                   | 16.06     |                                         | 1365 | Hz                | Chop off (ADCMODE.3 = 1)                                                                                                   |

| No Missing Codes <sup>2</sup>                     | 24        |                                         |      | Bits              | $\leq$ 26.7 Hz update rate with chop enabled                                                                               |

|                                                   | 24        |                                         |      | Bits              | ≤80.3 Hz update rate with chop disabled                                                                                    |

| Resolution (ADuC845/ADuC847)                      | See Table | e 11 and Table 1                        | 5    |                   |                                                                                                                            |

| Resolution (ADuC848)                              | See Table | e 13 and Table 1                        | 7    |                   |                                                                                                                            |

| Output Noise (ADuC845/ADuC847)                    | See Table | e 10 and Table 1                        | 4    | μV (rms)          | Output noise varies with selected update rates, gain range, and chop status.                                               |

| Output Noise (ADuC848)                            | See Table | e 12 and Table 1                        | 6    | μV (rms)          | Output noise varies with selected update rates, gain range, and chop status.                                               |

| Integral Nonlinearity                             |           |                                         | ±15  | ppm of FSR        | 1 LSB <sub>16</sub>                                                                                                        |

| Offset Error <sup>3</sup>                         |           | ±3                                      |      | μV                | Chop on                                                                                                                    |

|                                                   |           |                                         |      |                   | Chop off, offset error is in the order of the noise<br>for the programmed gain and update rate<br>following a calibration. |

| Offset Error Drift vs. Temperature <sup>2</sup>   |           | ±10                                     |      | nV/°C             | Chop on (ADCMODE.3 $=$ 0)                                                                                                  |

|                                                   |           | ±200                                    |      | nV/°C             | Chop off (ADCMODE.3 = 1)                                                                                                   |

| Full-Scale Error <sup>4</sup>                     |           |                                         |      |                   |                                                                                                                            |

| ADuC845/ADuC847                                   |           | ±10                                     |      | μV                | ±20 mV to ±2.56 V                                                                                                          |

| ADuC848                                           |           | ±10                                     |      | μV                | ±20 mV to ±640 mV                                                                                                          |

|                                                   |           | ±0.5                                    |      | LSB <sub>16</sub> | ±1.28 V to ±2.56 V                                                                                                         |

| Gain Error Drift vs. Temperature <sup>4</sup>     |           | ±0.5                                    |      | ppm/°C            |                                                                                                                            |

| Power Supply Rejection                            |           |                                         |      |                   |                                                                                                                            |

|                                                   | 80        |                                         |      | dB                | $AIN = 1 V, \pm 2.56 V, chop enabled$                                                                                      |

|                                                   |           | 113                                     |      | dB                | $AIN = 7.8 \text{ mV}, \pm 20 \text{ mV}, \text{ chop enabled}$                                                            |

|                                                   |           | 80                                      |      | dB                | AIN = 1 V, $\pm 2.56$ V, chop disabled <sup>2</sup>                                                                        |

| PRIMARY ADC ANALOG INPUTS                         |           |                                         |      |                   |                                                                                                                            |

| Differential Input Voltage Ranges <sup>5,6</sup>  |           |                                         |      |                   | Gain = 1 to 128                                                                                                            |

| Bipolar Mode (ADC0CON1.5 = 0)                     |           | $\pm$ 1.024 ×<br>V <sub>REF</sub> /GAIN |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) - REFIN2(-) \text{ (or Int 1.25 } V_{REF})$                           |

| Unipolar Mode (ADC0CON1.5 = 1)                    |           | 0 – 1.024 ×<br>V <sub>REF</sub> /GAIN   |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) - REFIN2(-) \text{ (or Int 1.25 } V_{REF})$                           |

| ADC Range Matching                                |           | ±2                                      |      | μV                | AIN = 18 mV, chop enabled                                                                                                  |

| Common-Mode Rejection DC                          |           |                                         |      |                   | Chop enabled, chop disabled                                                                                                |

| On AIN                                            | 95        |                                         |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   |           | 113                                     |      | dB                | $AIN = 1 V$ , range = $\pm 2.56 V$                                                                                         |

| Common-Mode Rejection<br>50 Hz/60 Hz <sup>2</sup> |           |                                         |      |                   | 50 Hz/60 Hz $\pm$ 1 Hz, 16.6 Hz and 50 Hz update rate, chop enabled, REJ60 enabled                                         |

| On AIN                                            | 95        |                                         |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   | 90        |                                         |      | dB                | AIN = 1 V, range = $\pm 2.56$ V                                                                                            |

## **ABOSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

### Table 2.

| Parameter                                 | Rating                             |

|-------------------------------------------|------------------------------------|

| AV <sub>DD</sub> to AGND                  | –0.3 V to +7 V                     |

| AV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| DV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| DV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| AGND to DGND <sup>1</sup>                 | –0.3 V to +0.3 V                   |

| AV <sub>DD</sub> to DV <sub>DD</sub>      | –2 V to +5 V                       |

| Analog Input Voltage to AGND <sup>2</sup> | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| Reference Input Voltage to AGND           | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| AIN/REFIN Current (Indefinite)            | 30 mA                              |

| Digital Input Voltage to DGND             | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Digital Output Voltage to DGND            | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Operating Temperature Range               | -40°C to +125°C                    |

| Storage Temperature Range                 | –65°C to +150°C                    |

| Junction Temperature                      | 150°C                              |

| $\theta_{JA}$ Thermal Impedance (MQFP)    | 90°C/W                             |

| θ <sub>JA</sub> Thermal Impedance (LFCSP) | 52°C/W                             |

| Lead Temperature, Soldering               |                                    |

| Vapor Phase (60 sec)                      | 215°C                              |

| Infrared (15 sec)                         | 220°C                              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> AGND and DGND are shorted internally on the ADuC845, ADuC847, and ADuC848.

<sup>2</sup> Applies to the P1.0 to P1.7 pins operating in analog or digital input modes.

| Pin                   | No.                   |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------|------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP               | 56-LFCSP              | Mnemonic               | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9                     | 9                     | P1.4/AIN5              |                   | On power-on default, P1.4/AIN5 is configured as the AIN5 analog input.<br>AIN5 can be used as a pseudo differential input when used with AINCOM or as<br>the positive input of a fully differential pair when used with AIN6.                                                                                                                                                                                                                       |

|                       |                       |                        |                   | P1.0 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                              |

| 10                    | 10                    | P1.5/AIN6              | 1                 | On power-on default, P1.5/AIN6 is configured as the AIN6 analog input.<br>AIN6 can be used as a pseudo differential input when used with AINCOM or as<br>the negative input of a fully differential pair when used with AIN5.                                                                                                                                                                                                                       |

|                       |                       |                        |                   | P1.1 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                              |

| 11                    | 11                    | P1.6/AIN7/IEXC1        | I/O               | On power-on default, P1.6/AIN7 is configured as the AIN7 analog input.                                                                                                                                                                                                                                                                                                                                                                              |

|                       |                       |                        |                   | AIN7 can be used as a pseudo differential input when used with AINCOM or as<br>the positive input of a fully differential pair when used with AIN8. One or both<br>current sources can also be configured at this pin.                                                                                                                                                                                                                              |

|                       |                       |                        |                   | P1.6 has no digital output driver. It can, however, function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                    |

| 12                    | 12                    | P1.7/AIN8/IEXC2        | I/O               | On power-on default, P1.7/AIN8 is configured as the AIN8 analog input.                                                                                                                                                                                                                                                                                                                                                                              |

|                       |                       |                        |                   | AIN8 can be used as a pseudo differential input when used with AINCOM or as<br>the negative input of a fully differential pair when used with AIN7. One or<br>both current sources can also be configured at this pin.                                                                                                                                                                                                                              |

|                       |                       |                        |                   | P1.7 has no digital output driver. It can, however, function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                                                                                                                                                                                    |

| 13                    | 13                    | AINCOM/DAC             | I/O               | All analog inputs can be referred to this pin, provided that a relevant pseudo differential input mode is selected. This pin also functions as an alternative pin out for the DAC.                                                                                                                                                                                                                                                                  |

| 14                    | 14                    | DAC                    | 0                 | The voltage output from the DAC, if enabled, appears at this pin.                                                                                                                                                                                                                                                                                                                                                                                   |

| Not<br>applicable     | 15                    | AIN9                   | I                 | AIN9 can be used as a pseudo differential analog input when used with<br>AINCOM or as the positive input of a fully differential pair when used with<br>AIN10 (LFCSP version only).                                                                                                                                                                                                                                                                 |

| Not<br>applicable     | 16                    | AIN10                  | I                 | AIN10 can be used as a pseudo differential analog input when used with AINCOM or as the negative input of a fully differential pair when used with AIN9 (LFCSP version only).                                                                                                                                                                                                                                                                       |

| 15                    | 17                    | RESET                  | I                 | Reset Input. A high level on this pin for 16 core clock cycles while the oscillator is running resets the device. This pin has an internal weak pull-down and a Schmitt trigger input stage.                                                                                                                                                                                                                                                        |

| 16 to 19,<br>22 to 25 | 18 to 21,<br>24 to 27 | P3.0 to P3.7           | I/O               | P3.0 to P3.7 are bidirectional port pins with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. When driving a 0-to-1 output transition, a strong pull-up is active for one core clock period of the instruction cycle. |

| 1.0                   | 10                    |                        |                   | Port 3 pins also have the various secondary functions described in this table.                                                                                                                                                                                                                                                                                                                                                                      |

| 16<br>17              | 18<br>19              | P3.0/RxD<br>P3.1/TxD   |                   | Receiver Data for UART Serial Port.<br>Transmitter Data for UART Serial Port.                                                                                                                                                                                                                                                                                                                                                                       |

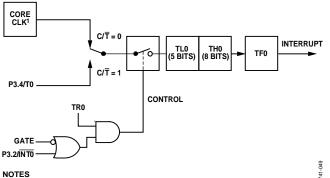

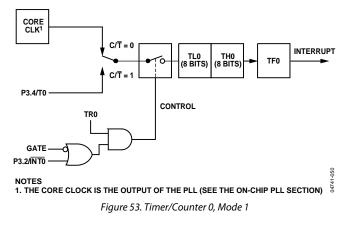

| 17<br>18              | 19<br>20              | P3.1/TXD<br>P3.2/INTO  |                   | External Interrupt 0. This pin can also be used as a gate control input to Timer 0.                                                                                                                                                                                                                                                                                                                                                                 |

| 18<br>19              | 20                    | P3.2/INT0<br>P3.3/INT1 |                   | External Interrupt 0. This pin can also be used as a gate control input to Timer 0.<br>External Interrupt 1. This pin can also be used as a gate control input to Timer 1.                                                                                                                                                                                                                                                                          |

| 19<br>22              | 21                    | P3.3/INTT<br>P3.4/T0   |                   | Timer/Counter 0 External Input.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22                    | 24<br>25              | P3.4/10<br>P3.5/T1     |                   | Timer/Counter 0 External Input.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23<br>24              | 25                    | P3.6/WR                |                   | External Data Memory Write Strobe. This pin latches the data byte from Port 0 into an external data memory.                                                                                                                                                                                                                                                                                                                                         |

| 25                    | 27                    | P3.7/RD                |                   | External Data Memory Read Strobe. This pin enables the data from an external data memory to Port 0.                                                                                                                                                                                                                                                                                                                                                 |

### Power Control Register (PCON)

The PCON SFR contains bits for power-saving options and general-purpose status flags as listed in Table 6.

| SFR Address:      | 87H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

### Table 6. PCON SFR Bit Designations

| Bit No. | Name          | Description                                                                                                                                                     |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | SMOD          | Double UART Baud Rate.                                                                                                                                          |

|         |               | 0 = Normal, 1 = Double Baud Rate.                                                                                                                               |

| 6       | SERIPD        | Serial Power-Down Interrupt Enable. If this<br>bit is set, a serial interrupt from either SPI<br>or I <sup>2</sup> C can terminate the power-down<br>mode.      |

| 5       | <b>INTOPD</b> | INT0 Power-Down Interrupt Enable.                                                                                                                               |

|         |               | If this bit is set, either a level ( $\overline{IT0} = 0$ ) or a negative-going transition ( $\overline{IT0} = 1$ ) on the INT0 pin terminates power-down mode. |

| 4       | ALEOFF        | If set to 1, the ALE output is disabled.                                                                                                                        |

| 3       | GF1           | General-Purpose Flag Bit.                                                                                                                                       |

| 2       | GF0           | General-Purpose Flag Bit.                                                                                                                                       |

| 1       | PD            | Power-Down Mode Enable. If set to 1, the device enters power-down mode.                                                                                         |

| 0       |               | Not Implemented. Write Don't Care.                                                                                                                              |

# ADuC845/ADuC847/ADuC848 Configuration Register (CFG845/CFG847/CFG848)

The CFG845/CFG847/CFG848 SFR contains the bits necessary to configure the internal XRAM and the extended SP. By default, it configures the user into 8051 mode, that is, extended SP, and the internal XRAM are disabled. When using in a program, use the device name only, that is, CFG845, CFG847, or CFG848.

| SFR Address:      | AFH |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | No  |

| Table 7. CFG845/CFG847/CFG848 SFR Bit Designations |

|----------------------------------------------------|

|----------------------------------------------------|

| Bit No. | Name   | Description                                                                                                                                   |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | EXSP   | Extended SP Enable.                                                                                                                           |

|         |        | If this bit is set to 1, the stack rolls over from SPH/SP = 00FFH to 0100H.                                                                   |

|         |        | If this bit is cleared to 0, SPH SFR is<br>disabled and the stack rolls over from<br>SP = FFH to SP = 00H.                                    |

| 6       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 5       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 4       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 3       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 2       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 1       |        | Not Implemented. Write Don't Care.                                                                                                            |

| 0       | XRAMEN | If this bit is set to 1, the internal XRAM is<br>mapped into the lower 2 kbytes of the<br>external address space.                             |

|         |        | If this bit is cleared to 0, the internal XRAM<br>is accessible and up to 16 MB of external<br>data memory become available. See<br>Figure 8. |

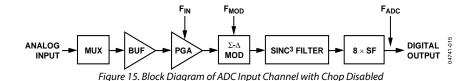

### Signal Chain Overview with Chop Disabled (CHOP = 1)

With  $\overline{\text{CHOP}} = 1$ , chop is disabled and the available output rates vary from 16.06 Hz to 1.365 kHz. The range of applicable SF words is from 3 to 255. When switching between channels with chop disabled, the channel throughput rate is higher than when chop is enabled. The drawback with chop disabled is that the drift performance is degraded and offset calibration is required following a gain range change or significant temperature change. A block diagram of the ADC input channel with chop disabled is shown in Figure 15.

The signal chain includes a multiplex or buffer, PGA,  $\Sigma$ - $\Delta$  modulator, and digital filter. The modulator bit stream is applied to a Sinc<sup>3</sup> filter. Programming the Sinc<sup>3</sup> decimation factor is restricted to an 8-bit register SF; the actual decimation factor is the register value times 8. The decimated output rate from the Sinc<sup>3</sup> filter (and the ADC conversion rate) is therefore

$$f_{ADC} = \frac{1}{8 \times SF} \times f_{MOD}$$

where:

$f_{ADC}$  is the ADC conversion rate.

*SF* is the decimal equivalent of the word loaded to the filter register, valid range is from 3 to 255.

$f_{MOD}$  is the modulator sampling rate of 32.768 kHz.

The settling time to a step input is governed by the digital filter. A synchronized step change requires a settling time of three times the programmed update rate; a channel change can be treated as a synchronized step change. This is one conversion longer than the case for chop enabled. However, because the ADC throughput is three times faster with chop disabled than it is with chop enabled, the actual time to a settled ADC output is significantly less also. This means that following a synchronized step change, the ADC requires three conversions (note: data is not output following a synchronized ADC change until data has settled) before the result accurately reflects the new input voltage.

$$t_{SETTLE} = \frac{3}{f_{ADC}} = 3 \times t_{ADC}$$

An unsynchronized step change requires four conversions to accurately reflect the new analog input at its output. Note that with an unsynchronized change the ADC continues to output data and so the user must take unsettled outputs into account. Again, this is one conversion longer than with chop enabled, but because the ADC throughput with chop disabled is faster than with chop enabled, the actual time taken to obtain a settled ADC output is less.

The allowable range for SF is 3 to 255 with a default of 69 (45H). The corresponding conversion rates, rms, and peak-to-peak noise performances are shown in Table 14, Table 15, Table 16, and Table 17. Note that the conversion time increases by 0.244 ms for each increment in SF.

### AUXILIARY ADC (ADUC845 ONLY)

Table 18. ADuC845 Typical Output RMS Noise (μV) vs. Update Rate with Chop Enabled

| SF Word | Data Update Rate (Hz) | μV    |

|---------|-----------------------|-------|

| 13      | 105.03                | 17.46 |

| 23      | 59.36                 | 3.13  |

| 27      | 50.56                 | 4.56  |

| 69      | 19.79                 | 2.66  |

| 255     | 5.35                  | 1.13  |

|         |                       |       |

# Table 19. ADuC845 Typical Peak-to-Peak Resolution (Bits)vs. Update Rate1 with Chop Enabled

| SF Word | Data Update Rate (Hz) | Bits |  |  |

|---------|-----------------------|------|--|--|

| 13      | 105.03                | 15.5 |  |  |

| 23      | 59.36                 | 18   |  |  |

| 27      | 50.56                 | 17.5 |  |  |

| 69      | 19.79                 | 18   |  |  |

| 255     | 5.35                  | 19.5 |  |  |

<sup>1</sup> ADC converting in bipolar mode.

# Table 20. ADuC845 Typical Output RMS Noise ( $\mu$ V) vs. Update Rate with Chop Disabled

| SF Word | Data Update Rate (Hz) | μV      |

|---------|-----------------------|---------|

| 3       | 1365.33               | 1386.58 |

| 13      | 315.08                | 34.94   |

| 66      | 62.06                 | 3.2     |

| 69      | 59.36                 | 3.19    |

| 81      | 50.57                 | 3.14    |

| 255     | 16.06                 | 1.71    |

| Table 21. ADuC845 Peak-to-Peak Resolution (Bits) vs. |

|------------------------------------------------------|

| Update Rate with Chop Disabled                       |

| SF Word | Data Update Rate (Hz) | Bits |

|---------|-----------------------|------|

| 3       | 1365.33               | 9    |

| 13      | 315.08                | 14.5 |

| 66      | 62.06                 | 18   |

| 69      | 59.36                 | 18   |

| 81      | 50.57                 | 18   |

| 255     | 16.06                 | 19   |

### **REFERENCE INPUTS**

The ADuC845/ADuC847/ADuC848 each have two separate differential reference inputs, REFIN± and REFIN2±. While both references are available for use with the primary ADC, only REFIN± is available for the auxiliary ADC (ADuC845 only). The common-mode range for these differential references is from AGND to AV<sub>DD</sub>. The nominal external reference voltage is

2.5 V, with the primary and auxiliary (ADuC845 only) reference select bits configured from the ADC0CON2 and ADC1CON (ADuC845 only), respectively.

When an external reference voltage is used, the primary ADC sees this internally as a 2.56 V reference ( $V_{REF} \times 1.024$ ). Therefore, any calculations of LSB size should account for this. For instance, with a 2.5 V external reference connected and using a gain of 1 on a unipolar range (2.56 V), the LSB size is ( $2.56/2^{24}$ ) = 152.6 nV (if using the 24-bit ADC on the ADuC845 or ADuC847). If a bipolar gain of 4 is used (±640 mV), the LSB size is (±640 mV)/2<sup>24</sup>) = 76.3 nV (again using the 24-bit ADC on the ADuC845 or ADuC845 or ADuC847).

The ADuC845/ADuC847/ADuC848 can also be configured to use the on-chip band gap reference via the XREF0/1 bits in the ADC0CON2 SFR (for primary ADC) or the AXREF bit in ADC1CON (for auxiliary ADC (ADuC845 only)). In this mode of operation, the ADC sees the internal reference of 1.25 V, thereby halving all the input ranges. A consequence of using the internal band gap reference is a noticeable degradation in peakto-peak resolution. For this reason, operation with an external reference is recommended.

In applications where the excitation (voltage or current) for the transducer on the analog input also drives the reference inputs for the device, the effect of any low frequency noise in the excitation source is removed because the application is ratiometric. If the devices are not used in a ratiometric configuration, use a low noise reference. Recommended reference voltage sources for the ADuC845/ADuC847/ADuC848 include the ADR421, REF43, and REF192.

The reference inputs provide a high impedance, dynamic load to external connections. Because the impedance of each reference input is dynamic, resistor/capacitor combinations on these pins can cause dc gain errors, depending on the output impedance of the source that is driving the reference inputs. Reference voltage sources, such as those mentioned above, for example, the ADR421, typically have low output impedances, and, therefore, decoupling capacitors on the REFIN± or REFIN2± inputs would be recommended (typically 0.1  $\mu$ F). Deriving the reference voltage from an external resistor configuration means that the reference input sees a significant external source impedance. External decoupling of the REFIN± and/or REFIN2± inputs is not recommended in this type of configuration.

## **BURNOUT CURRENT SOURCES**

The primary ADC on the ADuC845 and the ADC on the ADuC847 and ADuC848 incorporate two 100 nA constant current generators that are used to detect a failure in a connected sensor. One sources current from the  $AV_{DD}$  to AIN(+), and one sinks current from AIN(-) to AGND. These currents are only configurable for use on AIN5/AIN6 and/or AIN7/AIN8 in differential mode only, from the ICON.6 bit in the ICON SFR

## **TYPICAL PERFORMANCE CHARACTERISTICS**

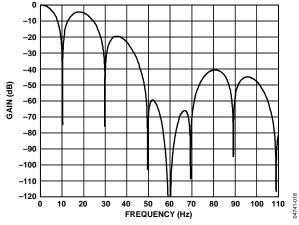

Figure 18. Filter Response, Chop On, SF = 69 Decimal

Figure 19. Filter Response, Chop On, SF = 255 Decimal

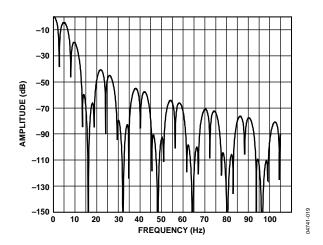

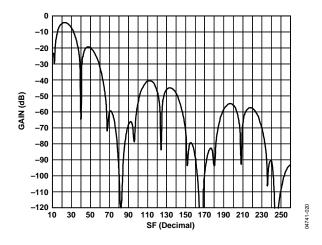

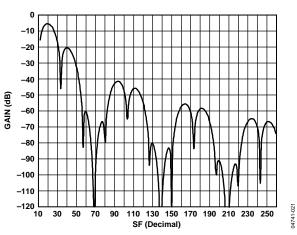

Figure 20. 50 Hz Normal Mode Rejection vs. SF Word, Chop On

Figure 21. 60 Hz Normal Mode Rejection vs. SF, Chop On

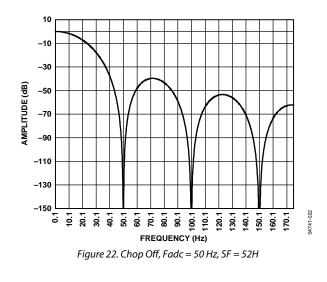

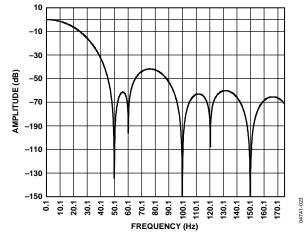

Figure 23. Chop Off, SF = 52H, REJ60 Enabled

### ADCSTAT (ADC STATUS REGISTER)

This SFR reflects the status of both ADCs including data ready, calibration, and various (ADC-related) error and warning conditions including REFIN± reference detect and conversion overflow/underflow flags.

| SFR Address:      | D8H |

|-------------------|-----|

| Power-On Default: | 00H |

| Bit Addressable:  | Yes |

| Bit No. | Name   | Description                                                                                                                                                                                                                                    |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 RDY0  |        | Ready Bit for the Primary ADC.                                                                                                                                                                                                                 |

|         |        | Set by hardware on completion of conversion or calibration.                                                                                                                                                                                    |

|         |        | Cleared directly by the user, or indirectly by a write to the mode bits, to start calibration. The primary ADC is inhibited from writing further results to its data or calibration registers until the RDY0 bit is cleared.                   |

| 6       | RDY1   | Ready Bit for Auxiliary (ADuC845 only) ADC.                                                                                                                                                                                                    |

|         |        | Same definition as RDY0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                                              |

| 5       | CAL    | Calibration Status Bit.                                                                                                                                                                                                                        |

|         |        | Set by hardware on completion of calibration.                                                                                                                                                                                                  |

|         |        | Cleared indirectly by a write to the mode bits to start another ADC conversion or calibration.                                                                                                                                                 |

|         |        | Note that calibration with the temperature sensor selected (auxiliary ADC on the ADuC845 only) fails to complete.                                                                                                                              |

| 4       | NOXREF | No External Reference Bit (only active if primary or auxiliary (ADuC845 only) ADC is active).                                                                                                                                                  |

|         |        | Set to indicate that one or both of the REFIN pins is floating or the applied voltage is below a specified threshold. When set, conversion results are clamped to all 1s. Only detects invalid REFIN±, does not check REFIN±.                  |

|         |        | Cleared to indicate valid V <sub>REF</sub> .                                                                                                                                                                                                   |

| 3       | ERRO   | Primary ADC Error Bit.                                                                                                                                                                                                                         |

|         |        | Set by hardware to indicate that the result written to the primary ADC data registers has been clamped to all 0s or all 1s. After a calibration, this bit also flags error conditions that caused the calibration registers not to be written. |

|         |        | Cleared by a write to the mode bits to initiate a conversion or calibration.                                                                                                                                                                   |

| 2       | ERR1   | Auxiliary ADC Error Bit. Same definition as ERR0 referred to the auxiliary ADC. Valid on the ADuC845 only.                                                                                                                                     |

| 1       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

| 0       |        | Not Implemented. Write Don't Care.                                                                                                                                                                                                             |

#### Table 23. ADCSTAT SFR Bit Designation

## ADCMODE (ADC MODE REGISTER)

Used to control the operational mode of both ADCs.

| SFR Address:      | D1H |

|-------------------|-----|

| Power-On Default: | 08H |

| Bit Addressable:  | No  |

### Table 24. ADCMODE SFR Bit Designations

| Bit No. | Name           | Descri                                                                                                                                                                                                                                                                                                                                             | ption                 |           |                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       |                | Not Implemented. Write Don't Care.                                                                                                                                                                                                                                                                                                                 |                       |           |                                                                                                                                                                                                                                                                                                                                                                         |

| 6       | REJ60          | Automatic 60 Hz Notch Select Bit.                                                                                                                                                                                                                                                                                                                  |                       |           |                                                                                                                                                                                                                                                                                                                                                                         |

|         |                | Setting this bit places a notch in the frequency response at 60 Hz, allowing simultaneous 50 Hz and 60 Hz rejection at an SF word of 82 decimal. This 60 Hz notch can be set only if SF $\geq$ 68 decimal, that is, the regular filter notch must be $\leq$ 60 Hz. This second notch is placed at 60 Hz only if the device clock is at 32.768 kHz. |                       |           |                                                                                                                                                                                                                                                                                                                                                                         |

| 5       | ADC0EN         | Primar                                                                                                                                                                                                                                                                                                                                             | y ADC I               | Enable.   |                                                                                                                                                                                                                                                                                                                                                                         |

|         |                | Set by                                                                                                                                                                                                                                                                                                                                             | the use               | er to ena | ble the primary ADC and place it in the mode selected in MD2–MD0.                                                                                                                                                                                                                                                                                                       |

|         |                | Cleare                                                                                                                                                                                                                                                                                                                                             | d by the              | e user to | place the primary ADC into power-down mode.                                                                                                                                                                                                                                                                                                                             |

| 4       | ADC1EN         | Auxilia                                                                                                                                                                                                                                                                                                                                            | ry ( <mark>ADu</mark> | IC845 or  | nly) ADC Enable.                                                                                                                                                                                                                                                                                                                                                        |

|         | (ADuC845 only) | Set by                                                                                                                                                                                                                                                                                                                                             | the use               | r to ena  | ble the auxiliary (ADuC845 only) ADC and place it in the mode selected in MD2–MD0.                                                                                                                                                                                                                                                                                      |

|         |                | Cleare                                                                                                                                                                                                                                                                                                                                             | d by the              | e user to | place the auxiliary (ADuC845 only) ADC in power-down mode.                                                                                                                                                                                                                                                                                                              |

| 3       | CHOP           | Chop I                                                                                                                                                                                                                                                                                                                                             | Node D                | isable.   |                                                                                                                                                                                                                                                                                                                                                                         |

|         |                | Set by the user to disable chop mode on both the primary and auxiliary (ADuC845 only) ADC allowing a three times higher ADC data throughput. SF values as low as 3 are allowed with this bit set, giving up to 1.3 kHz ADC update rates.                                                                                                           |                       |           |                                                                                                                                                                                                                                                                                                                                                                         |

|         |                |                                                                                                                                                                                                                                                                                                                                                    |                       |           | enable chop mode on both the primary and auxiliary (ADuC845 only) ADC.                                                                                                                                                                                                                                                                                                  |

| 2, 1, 0 | MD2, MD1, MD0  |                                                                                                                                                                                                                                                                                                                                                    | •                     |           | (ADuC845 only) ADC Mode Bits.                                                                                                                                                                                                                                                                                                                                           |

|         |                |                                                                                                                                                                                                                                                                                                                                                    |                       |           | perational mode of the enabled ADC as follows:                                                                                                                                                                                                                                                                                                                          |

|         |                | MD2                                                                                                                                                                                                                                                                                                                                                | MD1                   | MD0       |                                                                                                                                                                                                                                                                                                                                                                         |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                  | 0                     | 0         | ADC Power-Down Mode (Power-On Default).                                                                                                                                                                                                                                                                                                                                 |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                  | 0                     | 1         | Idle Mode. In idle mode, the ADC filter and modulator are held in a reset state although the modulator clocks are still provided.                                                                                                                                                                                                                                       |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                  | 1                     | 0         | Single Conversion Mode. In single conversion mode, a single conversion is performed<br>on the enabled ADC. Upon completion of a conversion, the ADC data registers<br>(ADC0H/M/L and/or ADC1H/M/L (ADuC845 only)) are updated. The relevant flags in<br>the ADCSTAT SFR are written, and power-down is re-entered with the MD2–MD0<br>accordingly being written to 000. |

|         |                |                                                                                                                                                                                                                                                                                                                                                    |                       |           | Note that ADC0L is not available on the ADuC848.                                                                                                                                                                                                                                                                                                                        |

|         |                | 0                                                                                                                                                                                                                                                                                                                                                  | 1                     | 1         | Continuous Conversion. In continuous conversion mode, the ADC data registers are regularly updated at the selected update rate (see the Sinc Filter SFR Bit Designations in Table 28).                                                                                                                                                                                  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                  | 0                     | 0         | Internal Zero-Scale Calibration. Internal short automatically connected to the enabled ADC input(s).                                                                                                                                                                                                                                                                    |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                  | 0                     | 1         | Internal Full-Scale Calibration. Internal or external REFIN± or REFIN2± $V_{REF}$ (as determined by XREF bits in ADC0CON2 and/or AXREF (ADuC845 only) in ADC1CON (ADuC845 only) is automatically connected to the enabled ADC input(s) for this calibration.                                                                                                            |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                  | 1                     | 0         | System Zero-Scale Calibration. User should connect system zero-scale input to the enabled ADC input(s) as selected by CH3–CH0 and ACH3–ACH0 bits in the ADC0CON2 and ADC1CON (ADuC845 only) registers.                                                                                                                                                                  |

|         |                | 1                                                                                                                                                                                                                                                                                                                                                  | 1                     | 1         | System Full-Scale Calibration. User should connect system full-scale input to the enabled ADC input(s) as selected by CH3–CH0 and ACH3–ACH0 bits in the ADC0CON2 and ADC1CON (ADuC845 only) registers.                                                                                                                                                                  |

### DAC CIRCUIT INFORMATION

The ADuC845/ADuC847/ADuC848 incorporate a 12-bit, voltage output DAC on-chip. It has a rail-to-rail voltage output buffer capable of driving 10 k $\Omega$ /100 pF, and has two selectable ranges, 0 V to V<sub>REF</sub> and 0 V to AV<sub>DD</sub>. It can operate in 12-bit or 8-bit mode. The DAC has a control register, DACCON, and two data registers, DACH/L. The DAC output can be programmed to appear at Pin 14 (DAC) or Pin 13 (AINCOM).

In 12-bit mode, the DAC voltage output is updated as soon as the DACL data SFR is written; therefore, the DAC data registers should be updated as DACH first, followed by DACL. The 12bit DAC data should be written into DACH/L right-justified such that DACL contains the lower 8 bits, and the lower nibble of DACH contains the upper 4 bits.

| DACCON Control R  | egister |

|-------------------|---------|

| SFR Address:      | FDH     |

| Power-On Default: | 00H     |

| Bit Addressable:  | No      |

| Bit No. | Name   | Description                                                                                                                                                                          |  |  |  |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7       |        | Not Implemented. Write Don't Care.                                                                                                                                                   |  |  |  |

| 6       |        | Not Implemented. Write Don't Care.                                                                                                                                                   |  |  |  |

| 5       |        | Not Implemented. Write Don't Care.                                                                                                                                                   |  |  |  |

| 4       | DACPIN | DAC Output Pin Select.                                                                                                                                                               |  |  |  |

|         |        | Set to 1 by the user to direct the DAC output to Pin 13 (AINCOM).                                                                                                                    |  |  |  |

|         |        | Cleared to 0 by the user to direct the DAC output to Pin 14 (DAC).                                                                                                                   |  |  |  |

| 3       | DAC8   | DAC 8-Bit Mode Bit.                                                                                                                                                                  |  |  |  |

|         |        | Set to 1 by the user to enable 8-bit DAC operation. In this mode, the 8 bits in DACL SFR are routed to the 8 MSBs of the DAC, and the 4 LSBs of the DAC are set to 0.                |  |  |  |

|         |        | Cleared to 0 by the user to enable 12-bit DAC operation. In this mode, the 8 LSBs of the result are routed to DACL, and the upper 4 MSB bits are routed to the lower 4 bits of DACH. |  |  |  |

| 2       | DACRN  | DAC Output Range Bit.                                                                                                                                                                |  |  |  |

|         |        | Set to 1 by the user to configure the DAC range of $0 V$ to $AV_{DD}$ .                                                                                                              |  |  |  |

|         |        | Cleared to 0 by the user to configure the DAC range of 0 V to 2.5 V ( $V_{REF}$ ).                                                                                                   |  |  |  |

| 1       | DACCLR | DAC Clear Bit.                                                                                                                                                                       |  |  |  |

|         |        | Set to 1 by the user to enable normal DAC operation.                                                                                                                                 |  |  |  |

|         |        | Cleared to 0 by the user to reset the DAC data registers DACL/H to 0.                                                                                                                |  |  |  |

| 0       | DACEN  | DAC Enable Bit.                                                                                                                                                                      |  |  |  |

|         |        | Set to 1 by the user to enable normal DAC operation.                                                                                                                                 |  |  |  |

|         |        | Cleared to 0 by the user to power down the DAC.                                                                                                                                      |  |  |  |

#### Table 33. DACCON–DAC Configuration Commands

#### DACH/DACL Data Registers

These DAC data registers are written to by the user to update the DAC output.

| SFR Address:      | DACL (DAC data low byte)—FBH  |

|-------------------|-------------------------------|

|                   | DACH (DAC data high byte)—FCH |

| Power-On Default: | 00H (both registers)          |

| Bit Addressable:  | No (both registers)           |

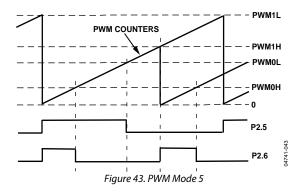

### Mode 5 (Dual 8-Bit PWM)

In Mode 5, the duty cycle and the resolution of the PWM outputs are individually programmable. The maximum resolution of the PWM output is 8 bits.

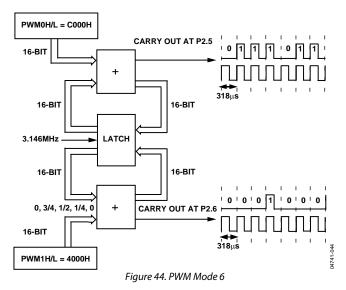

### Mode 6 (Dual RZ 16-Bit $\Sigma$ - $\Delta$ DAC)

Mode 6 provides a high speed PWM output similar to that of a  $\Sigma$ - $\Delta$  DAC. Mode 6 operates very similarly to Mode 4; however, the key difference is that Mode 6 provides return to zero (RZ)  $\Sigma$ - $\Delta$  DAC output. Mode 4 provides non-return-to-zero  $\Sigma$ - $\Delta$  DAC outputs. RZ mode ensures that any difference in the rise and fall times does not affect the  $\Sigma$ - $\Delta$  DAC INL. However, RZ mode halves the dynamic range of the  $\Sigma$ - $\Delta$  DAC outputs from 0 V- to AV<sub>DD</sub> down to 0 V to AV<sub>DD</sub>/2. For best results, this mode should be used with a PWM clock divider of 4.

If PWM1H is set to 4010H (slightly above one-quarter of FS), typically P2.6 is low for three full clocks ( $3 \times 80$  ns), high for one-half a clock (40 ns), and then low again for one-half a clock (40 ns) before repeating itself. Over every 65536 clocks, the PWM compromises for the fact that the output should be slightly above one-quarter of full scale by leaving the output high for two half clocks in four every so often.

For faster DAC outputs (at lower resolution), write 0s to the LSBs that are not required with a 1 in the LSB position. If, for example, only 12-bit performance is required, write 0001 to the 4 LSBs. This means that a 12-bit accurate  $\Sigma$ - $\Delta$  DAC output can occur at 3 kHz. Similarly, writing 00000001 to the 8 LSBs gives an 8-bit accurate  $\Sigma$ - $\Delta$  DAC output at 49 kHz.

The output resolution is set by the PWM1L and PWM1H SFRs for the P2.5 and P2.6 outputs, respectively. PWM0L and PWM0H set the duty cycles of the PWM outputs at P2.5 and P2.6, respectively. Both PWMs have the same clock source and clock divider.

### Mode 7

In Mode 7, the PWM is disabled, allowing P2.5 and P2.6 to be used as normal.

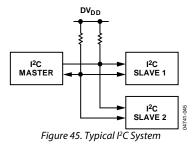

#### I2CADD-I<sup>2</sup>C Address Register 1

Function:

SFR Address:

Holds one of the I<sup>2</sup>C peripheral addresses for the device. It may be overwritten by user code. The uC001 Application Note describes the format of the I<sup>2</sup>C standard 7-bit address. 9BH

| Power-On Default: | 55H |

|-------------------|-----|

| Bit Addressable:  | No  |

#### I2CADD1-I<sup>2</sup>C Address Register 2

| Function:         | Same as the I2CADD. |

|-------------------|---------------------|

| SFR Address:      | F2H                 |

| Power-On Default: | 7FH                 |

| Bit Addressable:  | No                  |

#### I2CDAT-I<sup>2</sup>C Data Register

Function:The I2CDAT SFR is written to by user code to transmit data, or read by user code to read data just received by<br/>the I²C interface. Accessing I2CDAT automatically clears any pending I²C interrupt and the I2CI bit in the<br/>I2CCON SFR. User code should access I2CDAT only once per interrupt cycle.SFR Address:9AHPower-On Default:00HBit Addressable:No