Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 2K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0880hh020sg    |

|            | 16.3.2. ESPI Clock Phase and Polarity Control                      | 201 |

|------------|--------------------------------------------------------------------|-----|

|            | 16.3.3. Slave Select Modes of Operation                            | 203 |

|            | 16.3.4. SPI Protocol Configuration                                 | 207 |

|            | 16.3.5. Error Detection                                            | 210 |

|            | 16.3.6. ESPI Interrupts                                            | 211 |

|            | 16.3.7. ESPI Baud Rate Generator                                   | 212 |

| 16.4.      | ESPI Control Register Definitions                                  | 213 |

|            | 16.4.1. ESPI Data Register                                         |     |

|            | 16.4.2. ESPI Transmit Data Command and Receive Data Buffer Control |     |

|            | Register                                                           | 214 |

|            | 16.4.3. ESPI Control Register                                      | 215 |

|            | 16.4.4. ESPI Mode Register                                         | 217 |

|            | 16.4.5. ESPI Status Register                                       |     |

|            | 16.4.6. ESPI State Register                                        | 220 |

|            | 16.4.7. ESPI Baud Rate High and Low Byte Registers                 | 221 |

| Chapter 1  | 7. I2C Master/Slave Controller                                     | 223 |

| •          | Architecture                                                       |     |

| -,,-,      | 17.1.1. I2C Master/Slave Controller Registers                      |     |

| 17.2       | Operation                                                          |     |

| 17.2       | 17.2.1. SDA and SCL Signals                                        |     |

|            | 17.2.2. I <sup>2</sup> C Interrupts                                |     |

|            | 17.2.3. Start and Stop Conditions                                  |     |

|            | 17.2.4. Software Control of I2C Transactions                       |     |

|            | 17.2.5. Master Transactions                                        |     |

|            | 17.2.6. Slave Transactions                                         | 236 |

| 17.3.      | I <sup>2</sup> C Control Register Definitions                      | 243 |

|            | 17.3.1. I2C Data Register                                          |     |

|            | 17.3.2. I2C Interrupt Status Register                              |     |

|            | 17.3.3. I2C Control Register                                       | 247 |

|            | 17.3.4. I2C Baud Rate High and Low Byte Registers                  | 248 |

|            | 17.3.5. I2C State Register                                         | 250 |

|            | 17.3.6. I2C Mode Register                                          | 253 |

|            | 17.3.7. I2C Slave Address Register                                 | 255 |

| Chapter 1  | 8. Comparator                                                      | 256 |

| -          | Operation                                                          |     |

|            | Comparator Control Register Definitions                            |     |

| 10.4.      | 18.2.1. Comparator 0 Control Register                              |     |

|            | 18.2.2. Comparator 1 Control Register                              |     |

|            | -                                                                  |     |

| Chapter 15 | 9. Temperature Sensor                                              | 260 |

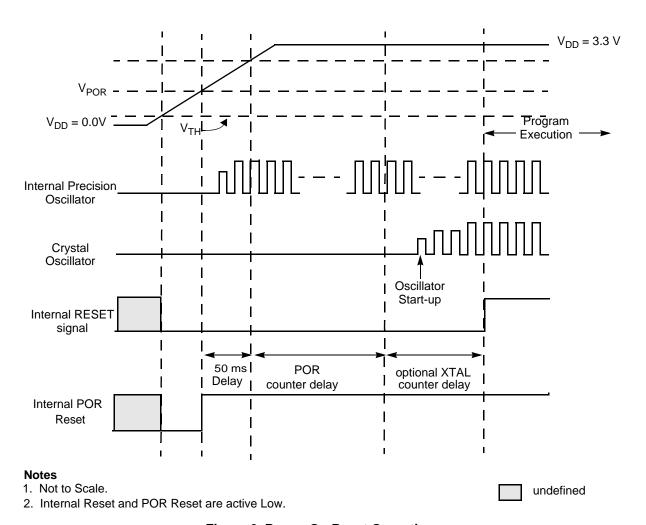

#### 5.2.1. Power-On Reset

Each device in the Z8 Encore! XP F1680 Series contains an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the whole device in the Reset state until the supply voltage reaches a safe circuit operating level when the device is powered on.

After power on, the POR circuit keeps idle until the supply voltage drops below  $V_{TH}$  voltage. Figure 7 on page 35 displays this POR timing.

After the F1680 Series MCU exits the POR state, the eZ8 CPU fetches the Reset vector. Following this POR, the POR/VBO status bit in the Reset Status Register is set to 1.

For the POR threshold voltage  $(V_{POR})$  and POR start voltage  $V_{TH}$ , see the <u>Electrical Characteristics chapter on page 349</u>.

Figure 6. Power-On Reset Operation

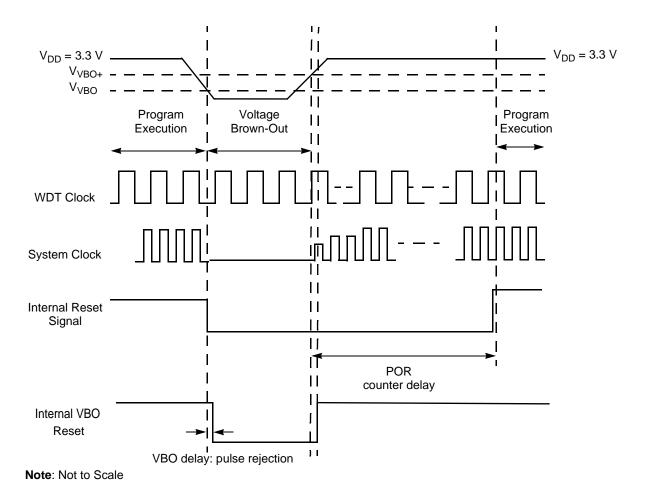

Figure 8. Voltage Brown-Out Reset Operation

## 5.2.3. Watchdog Timer Reset

If the device is operating in NORMAL or STOP modes, the WDT initiates a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1 (which is the unprogrammed state of the WDT\_RES Flash option bit). If the bit is programmed to 0, it configures the WDT to cause an interrupt, not a System Reset at time-out. The WDT status bit in the Reset Status Register is set to signify that the reset was initiated by the WDT.

eZ8 CPU services the Timer interrupt request following the normal Stop Mode Recovery sequence.

### 5.3.3. Stop Mode Recovery Using Comparator Interrupt

If Comparator enabled for STOP Mode operation interrupts during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status Register, the stop bit is set to 1. If the F1680 Series MCU is configured to respond to interrupts, the eZ8 CPU services the comparator interrupt request following the normal Stop Mode Recovery sequence.

### 5.3.4. Stop Mode Recovery Using GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. In the Reset Status Register, the stop bit is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin until the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

## 5.3.5. Stop Mode Recovery Using External RESET Pin

When the F1680 Series MCU is in STOP Mode and the external RESET pin is driven Low, a System Reset occurs. Because of a glitch filter operating on the RESET pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For details, see the Electrical Characteristics chapter on page 349.

### 5.4. Low-Voltage Detection

In addition to the VBO Reset described earlier, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. For more details about the available Low-Voltage Detection (LVD) threshold levels, see the <a href="https://dreshold.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi.nlm.ncbi

When the supply voltage drops below the LVD threshold, the LVD bit of the RSTSTAT Register is set to 1. This bit remains 1 until the low-voltage condition elapses. Reading or

### 8.4.3. Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) Register, shown in Table 39, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

Table 39. Interrupt Request 2 Register (IRQ2)

| Bits    | 7        | 6    | 5     | 4     | 3    | 2    | 1    | 0    |  |

|---------|----------|------|-------|-------|------|------|------|------|--|

| Field   | Reserved | MCTI | U1RXI | U1TXI | PC3I | PC2I | PC1I | PC0I |  |

| Reset   | 0        | 0    | 0     | 0     | 0    | 0    | 0    | 0    |  |

| R/W     | R/W      | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  |  |

| Address |          | FC6H |       |       |      |      |      |      |  |

| Bit           | Description                                                                                                                                                                                                             |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]           | Reserved; must be 0.                                                                                                                                                                                                    |

| [6]<br>MCTI   | Multi-channel timer Interrupt Request 0 = No interrupt request is pending for multi-channel timer. 1 = An interrupt request from multi-channel timer is awaiting service.                                               |

| [5]<br>U1RXI  | UART 1 Receiver Interrupt Request 0 = No interrupt request is pending for the UART 1 receiver. 1 = An interrupt request from the UART 1 receiver is awaiting service.                                                   |

| [4]<br>U1TXI  | UART 1 Transmitter Interrupt Request 0 = No interrupt request is pending for the UART 1 transmitter. 1 = An interrupt request from the UART 1 transmitter is awaiting service.                                          |

| [3:0]<br>PCxl | Port C Pin x Interrupt Request  0 = No interrupt request is pending for GPIO Port C pin x.  1 = An interrupt request from GPIO Port C pin x is awaiting service; x indicates the specific GPIO Port C pin number (0–3). |

# Chapter 9. Timers

The Z8 Encore! XP F1680 Series products contain three 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- Two independent capture/compare channels which reference the common timer

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the timer clock frequency

- Timer output pin

- Timer interrupt

- Noise Filter on Timer input signal

- Operation in any mode with 32kHz secondary oscillator

In addition to the timers described in this chapter, the Baud Rate Generator (BRG) of unused UART peripheral can also be used to provide basic timing functionality. For more information about using the Baud Rate Generator as additional timers, see the <u>LIN-UART</u> chapter on page 144.

Table 60. Timer 0-2 PWM0 Low Byte Register (TxPWM0L)

| Bit     | 7   | 6     | 5   | 4        | 3        | 2   | 1   | 0   |  |

|---------|-----|-------|-----|----------|----------|-----|-----|-----|--|

| Field   |     | PWM0L |     |          |          |     |     |     |  |

| Reset   | 0   | 0     | 0   | 0        | 0        | 0   | 0   | 0   |  |

| R/W     | R/W | R/W   | R/W | R/W      | R/W      | R/W | R/W | R/W |  |

| Address |     |       |     | F05H, F0 | DH, F15H |     |     |     |  |

| Bit          | Description                                                                            |

|--------------|----------------------------------------------------------------------------------------|

| [7:0]        | Pulse Width Modulator 0 High and Low Bytes                                             |

| PWM0H,       | These two bytes, {PWM0H[7:0], PWM0L[7:0]}, form a 16-bit value that is compared to the |

| <b>PWM0L</b> | current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM |

|              | output value is set by the TPOL bit in the Timer Control 1 Register (TxCTL1).          |

|              | The TxPWM0H and TxPWM0L registers also store the 16-bit captured timer value when      |

|              | operating in CAPTURE, CAPTURE/COMPARE and DEMODULATION Modes.                          |

## 9.3.4. Timer 0-2 PWM1 High and Low Byte Registers

The Timer 0–2 PWM1 High and Low Byte (TxPWM1H and TxPWM1L) registers, shown in Tables 61 and 62, store Capture values for DEMODULATION Mode.

Table 61. Timer 0-2 PWM1 High Byte Register (TxPWM1H)

| Bit     | 7   | 6                | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | PWM1H            |     |     |     |     |     |     |  |

| Reset   | 0   | 0                | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W              | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F20H, F24H, F28H |     |     |     |     |     |     |  |

Table 62. Timer 0–2 PWM1 Low Byte Register (TxPWM1L)

| Bit     | 7   | 6                | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------------|-----|-----|-----|-----|-----|-----|--|

| Field   |     | PWM1L            |     |     |     |     |     |     |  |

| Reset   | 0   | 0                | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W | R/W              | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F21H, F25H, F29H |     |     |     |     |     |     |  |

| Bit    | Description                                                                          |

|--------|--------------------------------------------------------------------------------------|

| [7:0]  | Pulse Width Modulator 1 High and Low Bytes                                           |

| PWM1H, | These two bytes, {PWM1H[7:0], PWM1L[7:0]}, store the 16-bit captured timer value for |

| PWM1L  | DEMODULATION Mode.                                                                   |

#### 10.3.3. PWM Output Operation

In a PWM OUTPUT operation, the timer generates a PWM output signal on the channel output pin (T4CHA, T4CHB, T4CHC, or T4CHD). The channel output toggles whenever the timer count matches the channel compare value (defined in the MCTCHyH and MCTCHyL registers). In addition, a channel interrupt is generated and the channel event flag is set in the status register. The timer continues counting according to its programmed mode.

The channel output signal begins with the output value = CHPOL and then transitions to  $\overline{\text{CHPOL}}$  when timer value matches the PWM value. If timer mode is Count Modulo, the channel output signal returns to output = CHPOL when timer reaches the reload value and is reset. If timer mode is Count up/down, channel output signal returns to output = CHPOL when the timer count matches the PWM value again (when counting down).

#### 10.3.4. Capture Operation

In a CAPTURE operation, the current timer count is recorded when the selected transition occurs on T4CHA, T4CHB, T4CHC or T4CHD. The Capture count value is written to the Channel High and Low Byte registers. In addition, a channel interrupt is generated and the channel event flag (CHyEF) is set in the Channel Status Register. The CHPOL bit in the Channel Control Register determines if the Capture occurs on a rising edge or a falling edge of the Channel Input signal. The timer continues counting according to the programmed mode.

## 10.4. Multi-Channel Timer Interrupts

The Multi-Channel Timer provides a single interrupt which has five possible sources. These sources are the internal timer and the four channel inputs (T4CHA, T4CHB, T4CHC, T4CHD).

## 10.4.1. Timer Interrupt

If enabled by the TCIEN bit of the MCTCTL0 Register, the timer interrupt will be generated when the timer completes a count cycle. This occurs during transition from counter = reload register value to counter = 0 in count modulo mode and occurs during transition from counter = 1 to counter = 0 in count up/down mode.

## 10.4.2. Capture/Compare Channel Interrupt

A channel interrupt is generated whenever there is a successful Capture/Compare Event on the Timer Channel and the associated CHIEN bit is set.

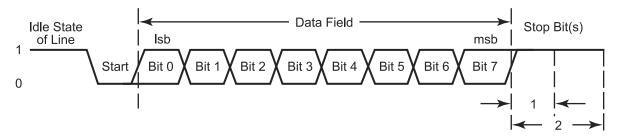

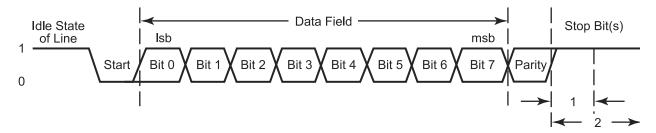

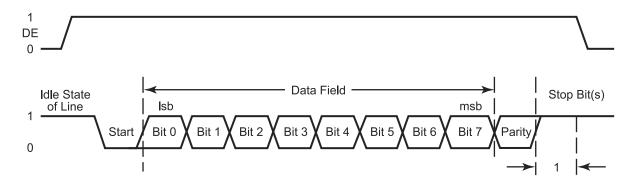

Figure 20. LIN-UART Asynchronous Data Format without Parity

Figure 21. LIN-UART Asynchronous Data Format with Parity

### 12.1.2. Transmitting Data using the Polled Method

Observe the following steps to transmit data using the polled-operating method:

- 1. Write to the LIN-UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the LIN-UART pin functions by configuring the associated GPIO port pins for alternate-function operation.

- 3. If MULTIPROCESSOR Mode is appropriate, write to the LIN-UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the MULTIPROCESSOR Mode Select bit (MPEN) to enable MULTIPROCESSOR Mode.

- 5. Write to the LIN-UART Control 0 Register to:

- a. Set the Transmit Enable bit (TEN) to enable the LIN-UART for data transmission.

- b. If parity is appropriate and MULTIPROCESSOR Mode is not enabled, set the parity enable bit (PEN) and select either even-or-odd parity (PSEL).

- c. Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

Figure 22. LIN-UART Driver Enable Signal Timing with One Stop Bit and Parity

The Driver Enable to start bit set-up time is calculated as follows:

$$\frac{1}{\text{Baud Rate (Hz)}} \le \text{DE to Start Bit Set-up Time(s)} \le \frac{2}{\text{Baud Rate (Hz)}}$$

### 12.1.8. LIN-UART Special Modes

The special modes of the LIN-UART are:

- MULTIPROCESSOR Mode

- LIN Mode

The LIN-UART features a common control register (Control 0) that has a unique register address and several mode-specific control registers (Multiprocessor Control, Noise Filter Control and LIN Control) that share a common register address (Control 1). When the Control 1 address is read or written, the MSEL[2:0] (Mode Select) field of the Mode Select and Status Register determines which physical register is accessed. Similarly, there are mode-specific status registers, one of which is returned when the Status 0 Register is read depending on the MSEL field.

#### 12.1.9. MULTIPROCESSOR Mode

The LIN-UART features a MULTIPROCESSOR (9-bit) Mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8 bits of data and immediately preceding the stop bit(s) as displayed in Figure 23.

### 12.3.6.1. Multiprocessor Control Register

When MSEL = 000b, the Multiprocessor Control Register, shown in Table 90, provides control for UART MULTIPROCESSOR Mode, IRDA Mode and Baud Rate Timer Mode as well as other features that can apply to multiple modes.

Table 90. Multiprocessor Control Register (U0CTL1 = F43H with MSEL = 000b)

| Bit     | 7     | 6          | 5     | 4    | 3     | 2      | 1      | 0    |  |

|---------|-------|------------|-------|------|-------|--------|--------|------|--|

| Field   | MPMD1 | MPEN       | MPMD0 | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| Reset   | 0     | 0          | 0     | 0    | 0     | 0      | 0      | 0    |  |

| R/W     | R/W   | R/W        | R/W   | R/W  | R/W   | R/W    | R/W    | R/W  |  |

| Address |       | F43H, F4BH |       |      |       |        |        |      |  |

Note: R/W = Read/Write.

| Bit Position | Value                                                                                                                                                     | Description                                                                                                                                                                                          |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [7,5]        | MULTIPROCESSOR (9-bit) Mode                                                                                                                               |                                                                                                                                                                                                      |  |  |  |  |  |

| MPMD[1:0]    | 00                                                                                                                                                        | The LIN-UART generates an interrupt request on all data and address bytes.                                                                                                                           |  |  |  |  |  |

|              | 01                                                                                                                                                        | The LIN-UART generates an interrupt request only on received address bytes.                                                                                                                          |  |  |  |  |  |

|              | 10                                                                                                                                                        | The LIN-UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs. |  |  |  |  |  |

|              | The LIN-UART generates an interrupt request on all received data be which the most recent address byte matched the value in the Address Compare Register. |                                                                                                                                                                                                      |  |  |  |  |  |

| [6]          | Multiprocessor Enable                                                                                                                                     |                                                                                                                                                                                                      |  |  |  |  |  |

| MPEN         | This bit is used to enable MULTIPROCESSOR (9-bit) Mode.                                                                                                   |                                                                                                                                                                                                      |  |  |  |  |  |

|              | 0                                                                                                                                                         | Disable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                 |  |  |  |  |  |

|              | 1                                                                                                                                                         | Enable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                  |  |  |  |  |  |

| [4]<br>MPBT  | Multiprocessor Bit Transmit This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled.                                                      |                                                                                                                                                                                                      |  |  |  |  |  |

|              | 0                                                                                                                                                         | Send a 0 in the multiprocessor bit location of the data stream (9th bit).                                                                                                                            |  |  |  |  |  |

|              | 1                                                                                                                                                         | Send a 1 in the multiprocessor bit location of the data stream (9th bit).                                                                                                                            |  |  |  |  |  |

| [3]          | Driver                                                                                                                                                    | Enable Polarity                                                                                                                                                                                      |  |  |  |  |  |

| DEPOL        | 0                                                                                                                                                         | DE signal is active High.                                                                                                                                                                            |  |  |  |  |  |

|              | 1                                                                                                                                                         | DE signal is active Low.                                                                                                                                                                             |  |  |  |  |  |

### 14.3.5. Sample Settling Time Register

The Sample Settling Time Register, shown in Table 105, is used to program the length of time from the SAMPLE/HOLD signal to the start signal, when the conversion can begin. The number of clock cycles required for settling will vary from system to system depending on the system clock period used. The system designer should program this register to contain the number of clocks required to meet a 0.5 µs minimum settling time.

**Table 105. Sample Settling Time (ADCSST)**

| Bits    | 7 | 6    | 5     | 4  | 3   | 2 | 1 | 0    |  |  |  |  |  |  |

|---------|---|------|-------|----|-----|---|---|------|--|--|--|--|--|--|

| Field   |   | Rese | erved |    | SST |   |   |      |  |  |  |  |  |  |

| Reset   |   | (    | )     |    | 1   | 1 | 1 | 1    |  |  |  |  |  |  |

| R/W     |   | F    | ₹     |    | R/W |   |   |      |  |  |  |  |  |  |

| Address |   |      |       | F7 | 4H  |   |   | F74H |  |  |  |  |  |  |

| Bit Position | Value<br>(H) | Description                                                                    |

|--------------|--------------|--------------------------------------------------------------------------------|

| [7:4]        | 0            | Reserved; must be 0.                                                           |

| [3:0]<br>SST | 0–F          | Sample settling time in number of system clock periods to meet 0.5 µs minimum. |

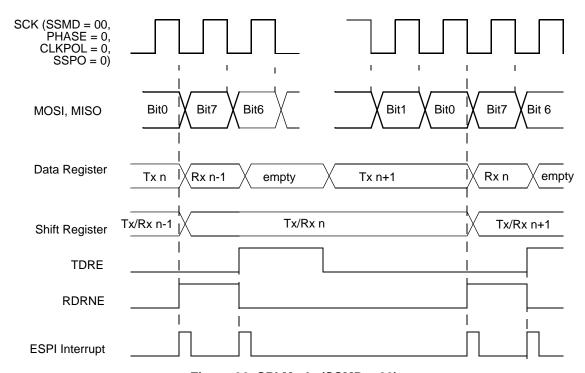

Figure 36. SPI Mode (SSMD = 00)

#### 16.3.3.2. Synchronous Frame Sync Pulse Mode

This mode is selected by setting the SSMD field of the Mode Register to 10. This mode is typically used for continuous transfer of fixed length frames where the frames are delineated by a pulse of duration one SCK period. The SSV bit in the ESPI Transmit Data Command register does not control the  $\overline{SS}$  pin directly in this mode. SSV must be set before or in sync with the first transmit data byte being written. The  $\overline{SS}$  signal will assert 1 SCK cycle before the first data bit and will stop after 1 SCK period. SCK is active from the initial assertion of  $\overline{SS}$  until the transaction end due to lack of transmit data.

The transaction is terminated by the Master when it no longer has data to send. If TDRE=1 at the end of a character, the  $\overline{SS}$  output will remain detached and SCK stops after the last bit is transferred. The TUND bit (transmit underrun) will assert in this case. After the transaction has completed, hardware will clear the SSV bit. Figure 37 displays a frame with synchronous frame sync pulse mode.

## 17.3.3. I<sup>2</sup>C Control Register

The I<sup>2</sup>C Control Register, shown in Table 121, enables and configures I<sup>2</sup>C operation.

Note:

**BIRQ**

The R/W1 bit can be set (written to 1) when IEN = 1, but cannot be cleared (written to 0).

Table 121. I<sup>2</sup>C Control Register (I2CCTL)

| Bits    | 7    | 6     | 5    | 4    | 3   | 2    | 1     | 0      |

|---------|------|-------|------|------|-----|------|-------|--------|

| Field   | IEN  | START | STOP | BIRQ | TXI | NAK  | FLUSH | FILTEN |

| Reset   | 0    | 0     | 0    | 0    | 0   | 0    | 0     | 0      |

| R/W     | R/W  | R/W1  | R/W1 | R/W  | R/W | R/W1 | W     | R/W    |

| Address | F52H |       |      |      |     |      |       |        |

| Bit          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]          | I <sup>2</sup> C Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IEN          | This bit enables the I <sup>2</sup> C controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [6]<br>START | Send Start Condition  When set, this bit causes the I <sup>2</sup> C controller (when configured as the master) to send a start condition. After it is asserted, this bit is cleared by the I <sup>2</sup> C controller after it sends the start condition or by deasserting the IEN bit. If this bit is 1, it cannot be cleared by writing to the bit. After this bit is set, a start condition is sent if there is data in the I2CDATA or I <sup>2</sup> C Shift Register. If there is no data in one of these registers, the I <sup>2</sup> C controller waits until data is loaded. If this bit is set while the I <sup>2</sup> C controller is shifting out data, it generates a restart condition after the byte shifts and the Acknowledge phase completes. If the stop bit is also set, it waits until the stop condition is sent before the start condition. If start is set while a SLAVE Mode transaction is underway to this device, the start bit will be cleared and ARBLST bit in the Interrupt Status Register will be set. |

| [5]<br>STOP  | Send Stop Condition  When set, this bit causes the I <sup>2</sup> C controller (when configured as the master) to send the stop condition after the byte in the I <sup>2</sup> C Shift Register has completed transmission or after a byte is received in a receive operation. When set, this bit is reset by the I <sup>2</sup> C controller after a stop condition has been sent or by deasserting the IEN bit. If this bit is 1, it cannot be cleared to 0 by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

writing to the register. If stop is set while a SLAVE Mode transaction is underway, the stop bit is cleared by hardware.

[4] Baud Rate Generator Interrupt Request

This bit is ignored when the  $I^2C$  controller is enabled. If this bit is set = 1 when the  $I^2C$  controller is disabled (IEN = 0), the baud rate generator is used as an additional timer causing an interrupt to occur every time the baud rate generator counts down to one. The baud rate generator runs continuously in this mode, generating periodic interrupts.

#### **22.2.1. Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the Byte Write routine (0x43FD). At the return from the subroutine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 159. Also, the user code should pop the address and data bytes off the stack.

The write routine uses 16 bytes of stack space in addition to the two bytes of address and data pushed by the user code. Sufficient memory must be available for this stack usage.

Because of the flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $136\mu s$  (assuming a 20MHz system clock). For every 200 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 58ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $7\mu s$  execution time.

**Bits** 7 6 5 4 3 2 1 0 Field FΕ **IGADDR** Reserved WE Default 0 0 0 0 0 0 0 0 Value

#### Table 159. Write Status Byte

| Bit           | Description                                                                                                                                                                                                                                                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]         | Reserved; must be 0.                                                                                                                                                                                                                                        |

| [2]<br>FE     | Flash Error If Flash error is detected, this bit is set to 1.                                                                                                                                                                                               |

| [1]<br>IGADDR | Illegal Address When NVDS byte writes to invalid addresses (those exceeding the NVDS array size) occur, this bit is set to 1. Note: When the NVDS array size is 256 bytes, there is no address exceeding the size; therefore the IGADDR bit cannot be used. |

| [0]<br>WE     | Write Error A failure occurs during writing data into Flash. When writing data into a certain address, a read back operation is performed. If the read back value is not the same as the value written, this bit is set to 1.                               |

## 22.2.2. Byte Read

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine (0x4000). At

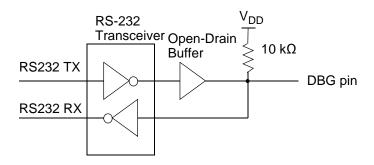

Figure 58. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

#### **23.2.1. DEBUG Mode**

The operating characteristics of the Z8 Encore! XP F1680 Series device in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode or otherwise defined by the on-chip peripheral to disable in DEBUG mode

- Automatically exits HALT Mode

- Constantly refreshes the Watch-Dog Timer, if enabled

#### 23.2.1.1. Entering DEBUG Mode

The device enters DEBUG mode following any of the these operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface

- eZ8 CPU execution of a breakpoint (BRK) instruction (when enabled)

- Match of PC to OCDCNTR Register (when enabled)

- OCDCNTR Register decrements to 0000H (when enabled)

- The DBG pin is Low when the device exits Reset

#### 23.2.1.2. Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-on reset

Table 188. Absolute Maximum Ratings\* (Continued)

| Parameter                                                         | Min | Max | Units | Notes |

|-------------------------------------------------------------------|-----|-----|-------|-------|

| 44-Pin QFN Maximum Ratings at -40°C to 70°C                       |     |     |       |       |

| Total power dissipation                                           |     | 750 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 200 | mA    |       |

| 44-Pin QFN Maximum Ratings at 70°C to 105°C                       |     |     |       |       |

| Total power dissipation                                           |     | 295 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 83  | mA    |       |

| 44-pin LQFP Maximum Ratings at -40°C to 70°C                      |     |     |       |       |

| Total power dissipation                                           |     | 750 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 200 | mA    |       |

| 44-pin LQFP Maximum Ratings at 70°C to 105°C                      |     |     |       |       |

| Total power dissipation                                           |     | 410 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 114 | mA    |       |

| Notes: *Operating temperature is specified in DC Characteristics. |     |     |       |       |

<sup>1.</sup> This voltage applies to all pins except the following:  $\rm V_{DD},\, AV_{DD}.$

### 29.2. DC Characteristics

Table 189 lists the DC characteristics of the Z8 Encore! XP F1680 Series products. All voltages are referenced to  $V_{SS}$ , which is the primary system ground.

**Table 189. DC Characteristics**

|                  |                             |                     | 0°C to -<br>0°C to | ⊦70°C<br>+105°C     |       |                                             |

|------------------|-----------------------------|---------------------|--------------------|---------------------|-------|---------------------------------------------|

| Symbol           | Parameter                   | Min                 | Тур                | Max                 | Units | Conditions                                  |

| V <sub>DD</sub>  | Supply Voltage              | 1.8                 | -                  | 3.6                 | V     |                                             |

| V <sub>IL1</sub> | Low Level Input<br>Voltage  | -0.3                | _                  | 0.3*V <sub>DD</sub> | V     | For all input pins except RESET, DBG, XIN   |

| V <sub>IL2</sub> | Low Level Input<br>Voltage  | -0.3                | -                  | 0.2*V <sub>DD</sub> | V     | For RESET, DBG, XIN                         |

| V <sub>IH1</sub> | High Level Input<br>Voltage | 0.7*V <sub>DD</sub> | -                  | 5.5                 | V     | Port A, B, C, D and E pins (Digital inputs) |

#### Notes:

- 1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

- 2. These values are provided for design guidance only and are not tested in production.

**Table 201. Low Voltage Detect Electrical Characteristics (Continued)**

|                     | <del>.</del>                                                                             |         | = 0°C to +7<br>-40°C to +1 | _   |       |            |

|---------------------|------------------------------------------------------------------------------------------|---------|----------------------------|-----|-------|------------|

|                     |                                                                                          | $V_{D}$ | <sub>D</sub> = 1.8 to 3.   | 6 V |       |            |

| Symbol              | Parameter                                                                                | Min     | Тур                        | Max | Units | Conditions |

| V <sub>TH_PRO</sub> | Detected Source Voltage for Flash<br>Protection                                          | 2.4     | 2.5                        | 2.6 | V     |            |

| T <sub>DELAY</sub>  | Delay from source voltage falling lower than $V_{TP}$ to $I_{VD\_OUT}$ output logic High | 50      | 1000                       | _   | ns    |            |

|                     | TP is a user-set threshold voltage to be detected                                        | ed.     |                            |     |       |            |

**Table 202. Crystal Oscillator Characteristics**

|                       |                                             |          | T <sub>A</sub> |        |                          |        |        |       |                |

|-----------------------|---------------------------------------------|----------|----------------|--------|--------------------------|--------|--------|-------|----------------|

|                       | -                                           | $V_{DD}$ | = 2.7 to       | 3.6 V  | V <sub>DD</sub> = 1.8 to |        | 2.7 V  | _     |                |

| Symbol                | Parameter                                   | Min      | Тур            | Max    | Min                      | Тур    | Max    | Units | Conditions     |

| I <sub>DD</sub> XTAL  | Crystal Oscillator<br>Active Supply Current | -        | -              | 500    | -                        | -      | 300    | μΑ    |                |

| I <sub>DDQ</sub> XTAL | Crystal Oscillator<br>Quiescent Current     | -        | 5              | -      | _                        | 5      | -      | nA    |                |

| S <sub>CLK</sub>      | Clk_out State in<br>Crystal Disable         | 1        | 1              | 1      | 1                        | 1      | 1      |       |                |

| F <sub>XTAL</sub>     | External Crystal Oscillator Frequency       | 1        | -              | 20     | 1                        | -      | 20     | MHz   | See Figure 74. |

| T <sub>SET</sub>      | Startup Time After<br>Enable                | -        | 10,000         | 30,000 | _                        | 10,000 | 30,000 | Cycle |                |

|                       | Clk_out Duty Cycle                          | 40       | 50             | 60     | 40                       | 50     | 60     | %     |                |

|                       | Clk_out Jitter                              | _        | 1              | _      | _                        | 1      | -      | %     |                |

Table 203. Low Power 32kHz Secondary Oscillator Characteristics

|                        |                                                     | T <sub>A</sub> = 0°C to +70°C<br>T <sub>A</sub> = -40°C to +105°C |        |      |                                          |        |      |       |            |

|------------------------|-----------------------------------------------------|-------------------------------------------------------------------|--------|------|------------------------------------------|--------|------|-------|------------|

|                        | _                                                   | V <sub>DD</sub> = 2.7 to 3.6 V                                    |        |      | $V_{DD} = 1.8 \text{ to } 2.7 \text{ V}$ |        |      |       |            |

| Symbol                 | Parameter                                           | Min                                                               | Тур    | Max  | Min                                      | Тур    | Max  | Units | Conditions |

| I <sub>DD</sub> XTAL2  | 32 kHz Secondary<br>Oscillator Active Current       | -                                                                 | _      | 20   | -                                        | _      | 10   | μA    |            |

| I <sub>DDQ</sub> XTAL2 | 32 kHz Secondary<br>Oscillator Quiescent<br>Current | _                                                                 | 5      | -    | _                                        | 5      | -    | nA    |            |

| S <sub>CLK</sub>       | Clk_out State in Crystal<br>Disable                 | 1                                                                 | 1      | 1    | 1                                        | 1      | 1    |       |            |

| F <sub>XTAL2</sub>     | External Crystal<br>Oscillator Frequency            | -                                                                 | 32.768 | -    | -                                        | 32.768 | -    | kHz   |            |

| T <sub>SET</sub>       | Startup Time After<br>Enable                        | -                                                                 | 400    | 1000 | -                                        | 400    | 1000 | mS    |            |

|                        | Clk_out Duty Cycle                                  | 40                                                                | 50     | 60   | 40                                       | 50     | 60   | %     |            |

|                        | Clk_out Jitter                                      | -                                                                 | 1      | _    | _                                        | 1      | -    | %     |            |

| input data sample timing 366                     | IM 330                              |

|--------------------------------------------------|-------------------------------------|

| interrupts 58                                    | immediate data 330                  |

| port A-C pull-up enable sub-registers 63, 64     | immediate operand prefix 331        |

| port A-H address registers 59                    | INC 332                             |

| port A-H alternate function sub-registers 61     | increment 332                       |

| port A-H control registers 60                    | increment word 332                  |

| port A-H data direction sub-registers 60         | INCW 332                            |

| port A-H high drive enable sub-registers 62      | indexed 330                         |

| port A-H input data registers 65                 | indirect address prefix 331         |

| port A-H output control sub-registers 62         | indirect register 330               |

| port A-H output data registers 66                | indirect register pair 330          |

| port A-H stop mode recovery sub-registers 63     | indirect working register 330       |

| port availability by device 46                   | indirect working register pair 330  |

| port input timing 366                            | infrared encoder/decoder (IrDA) 182 |

| port output timing 367                           | Instruction Set 328                 |

|                                                  | instruction set, ez8 CPU 328        |

| Н                                                | instructions                        |

| H 331                                            | ADC 332                             |

| HALT 333                                         | ADCX 332                            |

| halt mode 43, 333                                | ADD 332                             |

| hexadecimal number prefix/suffix 331             | ADDX 332                            |

|                                                  | AND 334                             |

| I                                                | ANDX 334                            |

| I2C 4                                            | arithmetic 332                      |

| 10-bit address read transaction 234              | BCLR 333                            |

| 10-bit address transaction 231                   | BIT 333                             |

| 10-bit addressed slave data transfer format 231, | bit manipulation 333                |

| 239                                              | block transfer 333                  |

| 7-bit address transaction 228, 236               | BRK 335                             |

| 7-bit address, reading a transaction 233         | BSET 333                            |

| 7-bit addressed slave data transfer format 230,  | BSWAP 333, 335                      |

| 238                                              | BTJ 335                             |

| 7-bit receive data transfer format 234, 240, 242 | BTJNZ 335                           |

| baud high and low byte registers 248, 250, 255   | BTJZ 335                            |

| C status register 251                            | CALL 335                            |

| controller 223                                   | CCF 333                             |

| controller signals 14                            | CLR 334                             |

| interrupts 226                                   | COM 334                             |

| operation 225                                    | CP 332                              |

| SDA and SCL signals 225                          | CPC 332                             |

| stop and start conditions 228                    | CPCX 332                            |

| I2CBRH register 250, 255                         | CPU control 333                     |

| I2CCTL register 247                              | CPX 332                             |

| I2CSTAT register 251                             | DA 332                              |

|                                                  |                                     |