Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1680hj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex) | Register Description | Mnemonic | Reset (Hex) <sup>1</sup> | Page #    |

|---------------|----------------------|----------|--------------------------|-----------|

| FD2           | Port A Input Data    | PAIN     | XX                       | <u>60</u> |

| FD3           | Port A Output Data   | PAOUT    | 00                       | <u>60</u> |

| GPIO Port B   |                      |          |                          |           |

| FD4           | Port B Address       | PBADDR   | 00                       | <u>58</u> |

| FD5           | Port B Control       | PBCTL    | 00                       | <u>60</u> |

| FD6           | Port B Input Data    | PBIN     | XX                       | <u>60</u> |

| FD7           | Port B Output Data   | PBOUT    | 00                       | <u>60</u> |

| GPIO Port C   |                      |          |                          |           |

| FD8           | Port C Address       | PCADDR   | 00                       | <u>58</u> |

| FD9           | Port C Control       | PCCTL    | 00                       | <u>60</u> |

| FDA           | Port C Input Data    | PCIN     | XX                       | <u>60</u> |

| FDB           | Port C Output Data   | PCOUT    | 00                       | <u>60</u> |

| GPIO Port D   |                      |          |                          |           |

| FDC           | Port D Address       | PDADDR   | 00                       | <u>58</u> |

| FDD           | Port D Control       | PDCTL    | 00                       | <u>60</u> |

| FDE           | Port D Input Data    | PDIN     | XX                       | <u>60</u> |

| FDF           | Port D Output Data   | PDOUT    | 00                       | <u>60</u> |

| GPIO Port E   |                      |          |                          |           |

| FE0           | Port E Address       | PEADDR   | 00                       | <u>58</u> |

| FE1           | Port E Control       | PECTL    | 00                       | <u>60</u> |

| FE2           | Port E Input Data    | PEIN     | XX                       | <u>60</u> |

| FE3           | Port E Output Data   | PEOUT    | 00                       | <u>60</u> |

| FE4–FEF       | Reserved             | _        | XX                       |           |

| Reset         |                      |          |                          |           |

| FF0           | Reset Status         | RSTSTAT  | XX                       | <u>40</u> |

| FF1           | Reserved             | _        | XX                       |           |

| Notes:        |                      |          |                          |           |

### Table 8. Register File Address Map (Continued)

Notes:

1. XX=Undefined.

2. The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM. reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the stop bit in the Reset Status Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating<br>Mode | Stop Mode Recovery Source                                                      | Action                                                               |

|-------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP Mode         | Watchdog Timer time-out when configured for Reset                              | Stop Mode Recovery                                                   |

|                   | Watchdog Timer time-out when configured for interrupt                          | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                   | Interrupt from Timer enabled for STOP<br>Mode operation                        | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                   | Interrupt from Comparator enabled for STOP Mode operation                      | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                   | Data transition on any GPIO port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

|                   | Assertion of external RESET Pin                                                | System Reset                                                         |

|                   | Debug Pin driven Low                                                           | System Reset                                                         |

### Table 11. Stop Mode Recovery Sources and Resulting Action

## 5.3.1. Stop Mode Recovery Using Watchdog Timer Time-Out

If the WDT times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status Register, the WDT and stop bits are set to 1. If the WDT is configured to generate an interrupt on time-out and the F1680 Series MCU is configured to respond to interrupts. The eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

## 5.3.2. Stop Mode Recovery Using Timer Interrupt

If a Timer with 32K crystal enabled for STOP Mode operation interrupts during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status Register, the stop bit is set to 1. If the F1680 Series MCU is configured to respond to interrupts, the

# 7.10. GPIO Interrupts

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pininput signal. Other port-pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more details about interrupts using the GPIO pins, see the <u>Interrupt Controller</u> chapter on page 68.

# 7.11. GPIO Control Register Definitions

Four registers for each port provide access to GPIO control, input data and output data. Table 20 lists these port registers. Use Port A–E Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |  |  |  |

|---------------------------|-------------------------------------------------------------|--|--|--|

| P <i>x</i> ADDR           | Port A–E Address Register (Selects subregisters)            |  |  |  |

| PxCTL                     | Port A–E Control Register (Provides access to subregisters) |  |  |  |

| PxIN                      | Port A–E Input Data Register                                |  |  |  |

| PxOUT                     | Port A–E Output Data Register                               |  |  |  |

| Port Subregister Mnemonic | Port Register Name                                          |  |  |  |

| PxDD                      | Data Direction                                              |  |  |  |

| PxAF                      | Alternate Function                                          |  |  |  |

| PxOC                      | Output Control (Open-Drain)                                 |  |  |  |

| PxHDE                     | High Drive Enable                                           |  |  |  |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable                            |  |  |  |

| PxPUE                     | Pull-up Enable                                              |  |  |  |

| PxAFS1                    | Alternate Function Set 1                                    |  |  |  |

| PxAFS2                    | Alternate Function Set 2                                    |  |  |  |

### Table 20. GPIO Port Registers and Subregisters

Table 54 provides an example initialization sequence for configuring Timer 0 in DEMOD-ULATION Mode and initiating operation.

| Register   | Value | Comment                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T0CTL0     | C0H   | TMODE[3:0] = 1100B selects DEMODULATION Mode.                                                                                                                                                                                                                                                                                                                                                                                   |

| T0CTL1     | 04H   | TICONFIG[1:0] = $10B$ enables interrupt only on Capture events.                                                                                                                                                                                                                                                                                                                                                                 |

| T0CTL2     | 11H   | <ul> <li>CSC = 0 selects the Timer Input from the GPIO pin.</li> <li>PWMD[2:0] = 000B has no effect.</li> <li>INPCAP = 0 has no effect.</li> <li>TEN = 0 disables the timer.</li> <li>PRES[2:0] = 000B sets prescaler to divide by 1.</li> <li>TPOLHI,TPOL = 10 enables trigger and Capture on both rising and falling edges of Timer Input.</li> <li>TCLKS = 1 enables 32kHz peripheral clock as timer clock source</li> </ul> |

| ТОН        | 00H   | Timer starting value = 0001H.                                                                                                                                                                                                                                                                                                                                                                                                   |

| TOL        | 01H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TORH       | ABH   | Timer reload value = ABCDH                                                                                                                                                                                                                                                                                                                                                                                                      |

| TORL       | CDH   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TOPWMOH    | 00H   | Initial PWM0 value = 0000H                                                                                                                                                                                                                                                                                                                                                                                                      |

| TOPWMOL    | 00H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T0PWM1H    | 00H   | Initial PWM1 value = 0000H                                                                                                                                                                                                                                                                                                                                                                                                      |

| T0PWM1H    | 00H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TONFC      | C0H   | NFEN = 1 enables noise filter<br>NFCTL = 100B enables 8-bit up/down counter                                                                                                                                                                                                                                                                                                                                                     |

| PAADDR     | 02H   | Selects Port A Alternate Function control register.                                                                                                                                                                                                                                                                                                                                                                             |

| PACTL[1:0] | 11B   | PACTL[0] enables Timer 0 Input alternate function.<br>PACTL[1] enables Timer 0 Output alternate function.                                                                                                                                                                                                                                                                                                                       |

| IRQ0ENH[5] | 0B    | Disables the Timer 0 interrupt.                                                                                                                                                                                                                                                                                                                                                                                                 |

| IRQ0ENL[5] | 0B    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T0CTL1     | 84H   | TEN = 1 enables the timer. All other bits remain in their appropriate settings.                                                                                                                                                                                                                                                                                                                                                 |

| Notes:     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 54. DEMODULATION Mode Initialization Example

Notes: After receiving the input trigger (rising or falling edge), Timer 0 will:

1. Start counting on the timer clock.

2. Upon receiving a Timer 0 Input rising edge, save the Capture value in the T0PWM0 registers, generate an interrupt, and continue to count.

3. Upon receiving a Timer 0 Input falling edge, save the Capture value in the T0PWM1 registers, generate an interrupt, and continue to count.

4. After the timer count to ABCD clocks, set the reload event flag and reset the Timer count to the start value.

### Table 88. Mode Status Fields

| MULTIPROCESSOR<br>Mode Status Field       | <ul> <li>NEWFRM</li> <li>Status bit denoting the start of a new frame. Reading the LIN-UART Receive</li> <li>Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul>                                                                                                            |  |  |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                           | Multiprocessor Receive (MPRX)<br>Returns the value of the last multiprocessor bit received. Reading from the LIN-<br>UART Receive Data Register resets this bit to 0.                                                                                                                                                                                                                                                |  |  |  |  |

| Digital Noise Filter<br>Mode Status Field | Noise Event (NE); MSEL = 001b<br>This bit is asserted if digital noise is detected on the receive data line when the<br>data is sampled (center of bit-time). If this bit is set, it does not mean that the<br>receive data is corrupted (though it can be in extreme cases), means that one or<br>more of the noise filter data samples near the center of the bit-time did not match<br>the average data value.    |  |  |  |  |

| LIN Mode Status Field                     | <b>Noise Event (NE); MSEL = 010b</b><br>This bit is asserted if some noise level is detected on the receive data line when<br>the data is sampled (center of bit-time). If this bit is set, it does not indicate that<br>the receive data is corrupt (though it can be in extreme cases), means that one or<br>more of the 16x data samples near the center of the bit-time did not match the<br>average data value. |  |  |  |  |

|                                           | <b>RxBreakLength</b><br>LIN mode received break length. This field can be read following a break (LIN<br>Wake-up or Break) so that the software can determine the measured duration of<br>the break. If the break exceeds 15 bit times the value saturates at 1111b.                                                                                                                                                 |  |  |  |  |

| Hardware Revision<br>Mode Status Field    | Noise Event (NE); MSEL = 111b<br>This field indicates the hardware revision of the LIN-UART block.<br>00_xxx LIN UART hardware revision.<br>01_xxx Reserved.<br>10_xxx Reserved.<br>11_xxx Reserved.                                                                                                                                                                                                                 |  |  |  |  |

| Applicable | BRG<br>Divisor | Actual Rate |           | Applicable | BRG<br>Divisor | Actual Rate |           |

|------------|----------------|-------------|-----------|------------|----------------|-------------|-----------|

| Rate (kHz) | (Decimal)      | (kHz)       | Error (%) | Rate (kHz) | (Decimal)      | (kHz)       | Error (%) |

| 38.4       | 16             | 39.1        | 1.73      | 0.30       | 2083           | 0.30        | 0.2       |

| 19.2       | 33             | 18.9        | 0.16      |            |                |             |           |

Table 97. LIN-UART Baud Rates, 10.0 MHz System Clock (Continued)

### Table 98. LIN-UART Baud Rates, 5.5296 MHz System Clock

| Applicable<br>Rate (kHz) | BRG<br>Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) | Applicable<br>Rate (kHz) | BRG<br>Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

|--------------------------|-----------------------------|----------------------|-----------|--------------------------|-----------------------------|----------------------|-----------|

| 1250.0                   | N/A                         | N/A                  | N/A       | 9.60                     | 36                          | 9.60                 | 0.00      |

| 625.0                    | N/A                         | N/A                  | N/A       | 4.80                     | 72                          | 4.80                 | 0.00      |

| 250.0                    | 1                           | 345.6                | 38.24     | 2.40                     | 144                         | 2.40                 | 0.00      |

| 115.2                    | 3                           | 115.2                | 0.00      | 1.20                     | 288                         | 1.20                 | 0.00      |

| 57.6                     | 6                           | 57.6                 | 0.00      | 0.60                     | 576                         | 0.60                 | 0.00      |

| 38.4                     | 9                           | 38.4                 | 0.00      | 0.30                     | 1152                        | 0.30                 | 0.00      |

| 19.2                     | 18                          | 19.2                 | 0.00      |                          |                             |                      |           |

### Table 99. LIN-UART Baud Rates, 3.579545 MHz System Clock

|                          | BRG                  |                      |           |                          | BRG                  |                      |           |

|--------------------------|----------------------|----------------------|-----------|--------------------------|----------------------|----------------------|-----------|

| Applicable<br>Rate (kHz) | Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) | Applicable<br>Rate (kHz) | Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

| 1250.0                   | N/A                  | N/A                  | N/A       | 9.60                     | 23                   | 9.73                 | 1.32      |

| 625.0                    | N/A                  | N/A                  | N/A       | 4.80                     | 47                   | 4.76                 | -0.83     |

| 250.0                    | 1                    | 223.72               | -10.51    | 2.40                     | 93                   | 2.41                 | 0.23      |

| 115.2                    | 2                    | 111.9                | -2.90     | 1.20                     | 186                  | 1.20                 | 0.23      |

| 57.6                     | 4                    | 55.9                 | -2.90     | 0.60                     | 373                  | 0.60                 | -0.04     |

| 38.4                     | 6                    | 37.3                 | -2.90     | 0.30                     | 746                  | 0.30                 | -0.04     |

| 19.2                     | 12                   | 18.6                 | -2.90     |                          |                      |                      |           |

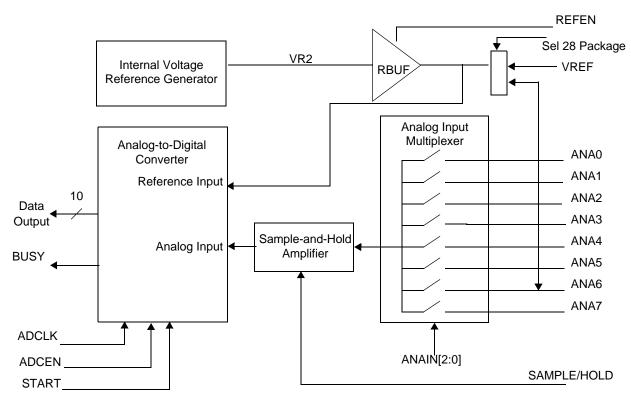

Figure 30. Analog-to-Digital Converter Block Diagram

## 14.2.1. ADC Timing

Each ADC measurement consists of 3 phases:

- 1. Input sampling (programmable, minimum of 1.8µs).

- 2. Sample-and-hold amplifier settling (programmable, minimum of  $0.5 \mu s$ ).

- 3. Conversion is 13 ADCLK cycles.

Figure 31 displays the timing of an ADC conversion.

| Bits          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6             | 5              | 4                           | 3             | 2                         | 1                       | 0           |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------------------|---------------|---------------------------|-------------------------|-------------|--|

| Field         | ACKV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ACK           | AS             | DS                          | 10B           | RSTR                      | SCLOUT                  | BUSY        |  |

| Reset         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0             | 0              | 0                           | 0             | 0                         | 1                       | 0           |  |

| R/W           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R             | R              | R                           | R             | R                         | R                       | R           |  |

| Address       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                | F5                          | 5H            |                           |                         |             |  |

| Bit           | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description   |                |                             |               |                           |                         |             |  |

| [7]<br>ACKV   | ACK Valid<br>This bit is set, if sending data (Master or Slave) and the ACK bit in this register is valid for the<br>byte just transmitted. This bit can be monitored if it is appropriate for software to verify the ACK<br>value before writing the next byte to be sent. To operate in this mode, the Data Register must<br>not be written when TDRE asserts; instead, the software waits for ACKV to assert. This bit<br>clears when transmission of the next byte begins or the transaction is ended by a stop or<br>restart condition. |               |                |                             |               |                           |                         |             |  |

| [6]<br>ACK    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | icates the st |                | Acknowledge<br>leared for a |               |                           | nitted or rece<br>tion. | eived. This |  |

| [5]<br>AS     | Address S<br>This bit is a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | vhile the add  | lress is bein               | g transferred | d on the I <sup>2</sup> C | bus.                    |             |  |

| [4]<br>DS     | Data State<br>This bit is a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ctive High w  | vhile the data | a is being tra              | ansferred on  | the I <sup>2</sup> C bus  | 6.                      |             |  |

| [3]<br>10B    | <b>10B</b><br>This bit indicates whether a 7-bit or 10-bit address is being transmitted when operating as a Master. After the start bit is set, if the five most-significant bits of the address are 11110B, this bit is set. When set, it is Reset after the address has been sent.                                                                                                                                                                                                                                                         |               |                |                             |               |                           |                         |             |  |

| [2]<br>RSTR   | <b>RESTART</b><br>This bit is updated each time a stop or restart interrupt occurs (SPRS bit set in I2CISTAT Register).<br>0 = Stop condition.<br>1 = Restart condition.                                                                                                                                                                                                                                                                                                                                                                     |               |                |                             |               |                           |                         |             |  |

| [1]<br>SCLOUT | <b>Serial Clock Output</b><br>Current value of Serial Clock being output onto the bus. The actual values of the SCL and SDA signals on the I <sup>2</sup> C bus can be observed via the GPIO Input Register.                                                                                                                                                                                                                                                                                                                                 |               |                |                             |               |                           |                         | L and SDA   |  |

| [0]<br>BUSY   | $I^2$ <b>C Bus Busy</b><br>0 = No activity on the I <sup>2</sup> C Bus.<br>1 = A transaction is underway on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                                                                                                        |               |                |                             |               |                           |                         |             |  |

# Table 125. I<sup>2</sup>C State Register (I2CSTATE)—Description when DIAG = 0

# Chapter 20. Flash Memory

The products in the Z8 Encore! XP F1680 Series feature either 24KB (24576 bytes), 16KB (16384 bytes) and 8KB (8192 bytes) of nonvolatile Flash memory with read/write/ erase capability. The Flash memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash memory array is arranged in pages with 512 bytes per page. The 512 byte page is the minimum Flash block size that can be erased. Each page is divided into 4 rows of 128 bytes.

For program/data protection, Flash memory is also divided into sectors. In the Z8 Encore! XP F1680 Series, Flash memory is divided into 8 sectors which can be protected from programming and erase operation on a per sector basis.

The first 2 bytes of the Flash program memory are used as Flash option bits. For more information about their operation, see the <u>Flash Option Bits</u> chapter on page 276.

Table 132 lists the Flash memory configuration for each device in the Z8 Encore! XP F1680 Series.

| Part Number | Flash Size in<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) | Number of<br>Sectors | Pages per<br>Sector |

|-------------|-----------------------------|----------------|-----------------------------|------------------------------|----------------------|---------------------|

| Z8F2480     | 24 (24576)                  | 48             | 0000H–5FFFH                 | 3072                         | 8                    | 6                   |

| Z8F1680     | 16 (16384)                  | 32             | 0000H–3FFFH                 | 2048                         | 8                    | 4                   |

| Z8F0880     | 8 (8192)                    | 16             | 0000H–1FFFH                 | 1024                         | 8                    | 2                   |

### Table 132. Z8 Encore! XP F1680 Series Flash Memory Configurations

# 20.1. Flash Information Area

The Flash Information Area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are user-accessible. Factory trim values for the analog peripherals are stored in the Flash Information Area, and so are factory calibration data for the Temperature Sensor. Figures 51 through 53 display the Flash memory arrangement.

## 20.2.8. Flash Controller Behavior in Debug Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Sector Protect register can be written to 1 or 0

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control Register

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the Flash controller must go through the unlock sequence again to select another page.

# 20.3. Flash Control Register Definitions

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 271

Flash Status Register: see page 272

Flash Page Select Register: see page 273

Flash Sector Protect Register: see page 274

Flash Frequency High and Low Byte Registers: see page 274

## 20.3.1. Flash Control Register

The Flash Controller must be unlocked using the Flash Control Register (see Table 134) before programming or erasing Flash memory. The Flash Controller is unlocked by writing to the Flash Page Select Register, then 73H 8CH, sequentially, to the Flash Control Register, and finally again to the Flash Page Select Register with the same value as the previous write. When the Flash Controller is unlocked, Mass Erase or Page Erase can be initiated by writing the appropriate command to the FCTL. Erase applies only to the active page selected in the Flash Page Select Register. Mass Erase is enabled only through the

# Chapter 21. Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP F1680 Series MCU operation. The feature configuration data is stored in Flash program memory and are read during Reset. The features available for control through the Flash option bits include:

- Watchdog Timer time-out response selection–interrupt or System Reset

- Watchdog Timer enabled at Reset

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- VBO configuration-always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- LVD voltage threshold selection

- Oscillator mode selection for high, medium and low-power crystal oscillators or an external RC oscillator

- Factory trimming information for the IPO and Temperature Sensor

## 21.1. Operation

This section describes the types of option bits and their configuration in the Option Configuration registers.

## 21.1.1. Option Bit Configuration by Reset

Each time the Flash option bits are programmed or erased, the device must be Reset for the change to take effect. During any Reset operation (System Reset or Stop Mode Recovery), the Flash option bits are automatically read from Flash Program Memory and written to the Option Configuration registers. These Option Configuration registers control operation of the devices within the Z8 Encore! XP F1680 Series MCU. Option bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

285

|          | LV      | D Threshold | (V)     |                                          |

|----------|---------|-------------|---------|------------------------------------------|

| LVD_TRIM | Minimum | Typical     | Maximum | Description                              |

| 01101    |         | 2.55        |         |                                          |

| 01110    |         | 2.50        |         |                                          |

| 01111    |         | 2.45        |         |                                          |

| 10000    |         | 2.40        |         |                                          |

| 10001    |         | 2.35        |         |                                          |

| 10010    |         | 2.30        |         |                                          |

| 10011    |         | 2.25        |         |                                          |

| 10100    |         | 2.20        |         |                                          |

| 10101    |         | 2.15        |         |                                          |

| 10110    |         | 2.10        |         |                                          |

| 10111    |         | 2.05        |         |                                          |

| 11000    |         | 2.00        |         |                                          |

| 11001    |         | 1.95        |         |                                          |

| 11010    |         | 1.90        |         |                                          |

| 11011    |         | 1.85        |         |                                          |

| 11100    |         | 1.80        |         |                                          |

| 11101    |         | 1.75        |         |                                          |

| 11110    |         | 1.70        |         |                                          |

| 11111    |         | 1.65        |         | Minimum LVD threshold, default on Reset. |

### Table 150. LVD\_Trim Values (Continued)

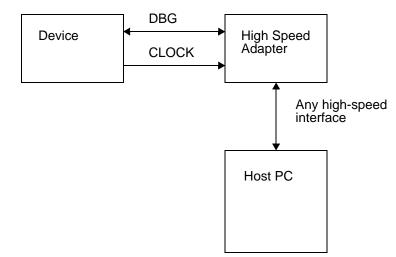

Figure 60. Synchronous Operation

## 23.2.5. OCD Serial Errors

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of ten continuous bits Low)

- Framing Error (received stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a Serial Break 4096 system clock cycles long back to the host and resets the Autobaud Detector/Generator. A Framing Error or Transmit Collision can be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to theZ8 Encore! XP F1680 Series device or when recovering from an error. A Serial Break from the host resets the Autobaud Generator/Detector but does not reset the OCD Control Register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

300

## 23.2.6. Automatic Reset

The Z8 Encore! XP F1680 Series devices have the capability to switch clock sources during operation. If the Autobaud is set and the clock source is switched, the Autobaud value becomes invalid. A new Autobaud value must be configured with the new clock frequency.

The oscillator control logic has clock switch detection. If a clock switch is detected and the Autobaud is set, the device will automatically send a Serial Break for 4096 clocks. This will reset the Autobaud and indicate to the host that a new Autobaud character should be sent.

## 23.2.7. Transmit Flow Control

Transmit flow control is implemented by the use of a remote start bit. When transmit flow control is enabled, the transmitter will wait for the remote host to send the start bit. Transmit flow control is useful in applications where receive overruns can occur.

The remote host can transmit a remote start bit by sending the character FFH. The transmitter will append its data after the start bit. Due to the *wire-and* nature of the open drain bus, the start bit sent by the remote host and the data bits sent by the Z8 Encore! XP F1680 Series device appear as one character; see Figure 61.

| Receiving<br>Device    |      | ST                          |     |     |    |    |    |    |    |    |    |

|------------------------|------|-----------------------------|-----|-----|----|----|----|----|----|----|----|

| Transmitting<br>Device |      |                             | D0  | D1  | D2 | D3 | D4 | D5 | D6 | D7 | SP |

|                        |      |                             |     |     |    |    |    |    |    |    |    |

| Single Wire<br>Bus     |      | ST                          | D0  | D1  | D2 | D3 | D4 | D5 | D6 | D7 | SP |

|                        | SP = | = Start<br>= Stop<br>D7 = D | bit | its |    |    |    |    |    |    |    |

Figure 61. Start Bit Flow Control

## 23.2.8. Breakpoints

Execution breakpoints are generated using the BRK instruction (op code 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If breakpoints are enabled, the OCD idles the eZ8 CPU and enters DEBUG mode. If breakpoints are not

# 23.4.3. Line Control Register

The Line Control Register, shown in Table 166, is used to configure the output driver characteristics during transmission. This register is only used in high-speed implementations.

| Bit            | 7                                                                                                                                                                                                                                                                   | 6             | 5                                              | 4    | 3           | 2    | 1   | 0    |  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------|------|-------------|------|-----|------|--|--|--|--|--|--|

| Field          | Re                                                                                                                                                                                                                                                                  | eset          | NBTX                                           | NBEN | TXFC        | TXDH | TXD | TXHD |  |  |  |  |  |  |

| Reset          | C                                                                                                                                                                                                                                                                   | 00            | 0                                              | 0    | 0           | 0    | 0   | 0    |  |  |  |  |  |  |

| R/W            | 1                                                                                                                                                                                                                                                                   | R             | R/W                                            | R/W  | R/W         | R/W  | R/W | R/W  |  |  |  |  |  |  |

| Bit            | Description                                                                                                                                                                                                                                                         |               |                                                |      |             |      |     |      |  |  |  |  |  |  |

| [7:6]<br>Reset | Reset                                                                                                                                                                                                                                                               |               |                                                |      |             |      |     |      |  |  |  |  |  |  |

| [5]<br>NBTX    | Nine Bit Transmit<br>This control bit sets the polarity of the ninth bit when nine bit mode is enabled.<br>0 = Ninth bit is zero.<br>1 = Ninth bit is one.                                                                                                          |               |                                                |      |             |      |     |      |  |  |  |  |  |  |

| [4]<br>NBEN    | <ul> <li>Nine Bit Enable</li> <li>This control bit enables nine-bit mode; it is useful when transmit flow control using remote start bit is enabled to detect valid characters.</li> <li>0 = Nine Bit mode disabled.</li> <li>1 = Nine Bit mode enabled.</li> </ul> |               |                                                |      |             |      |     |      |  |  |  |  |  |  |

| [3]<br>TXFC    |                                                                                                                                                                                                                                                                     | nit Flow Cor  | <b>ol</b><br>htrol disabled<br>htrol using rel |      | it.         |      |     |      |  |  |  |  |  |  |

| [2]<br>TXDH    |                                                                                                                                                                                                                                                                     | ot driven H   | igh during 0<br>during 0 to 1                  |      | INS.        |      |     |      |  |  |  |  |  |  |

| [1]<br>TXD     |                                                                                                                                                                                                                                                                     | only driven L | ow during tran                                 |      | (Open-Drair | ı).  |     |      |  |  |  |  |  |  |

| [0]<br>TXHD    | <ul> <li>1 = Pin is always driven during transmission.</li> <li>Transmit High Drive Strength</li> <li>0 = Pin output driver is Low drive strength.</li> <li>1 = Pin output driver is High drive strength.</li> </ul>                                                |               |                                                |      |             |      |     |      |  |  |  |  |  |  |

| Assembly      |                          |      | ress<br>ode | Op<br>Code(s) |   |   | Fla | ıgs |   | Fetch | Instr. |   |

|---------------|--------------------------|------|-------------|---------------|---|---|-----|-----|---|-------|--------|---|

| Mnemonic      | Symbolic Operation       | dst  | src         | (Hex)         | С | Ζ | S   | ۷   | D | Н     |        |   |

| LD dst, rc    | dst ← src                | r    | IM          | 0C-FC         | _ | _ | _   | -   | _ | _     | 2      | 2 |

|               |                          | r    | X(r)        | C7            | - |   |     |     |   |       | 3      | 3 |

|               |                          | X(r) | r           | D7            | _ |   |     |     |   |       | 3      | 4 |

|               |                          | r    | lr          | E3            | _ |   |     |     |   |       | 2      | 3 |

|               |                          | R    | R           | E4            | _ |   |     |     |   |       | 3      | 2 |

|               |                          | R    | IR          | E5            | _ |   |     |     |   |       | 3      | 4 |

|               |                          | R    | IM          | E6            | _ |   |     |     |   |       | 3      | 2 |

|               |                          | IR   | IM          | E7            | _ |   |     |     |   |       | 3      | 3 |

|               |                          | lr   | r           | F3            | _ |   |     |     |   |       | 2      | 3 |

|               |                          | IR   | R           | F5            | _ |   |     |     |   |       | 3      | 3 |

| LDC dst, src  | dst ← src                | r    | Irr         | C2            | _ | - | _   | -   | _ | _     | 2      | 5 |

|               |                          | lr   | Irr         | C5            | _ |   |     |     |   |       | 2      | 9 |

|               |                          | Irr  | r           | D2            | _ |   |     |     |   |       | 2      | 5 |

| LDCI dst, src | dst ← src                | lr   | Irr         | C3            | _ | _ | _   | -   | _ | -     | 2      | 9 |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3            | _ |   |     |     |   |       | 2      | 9 |

| LDE dst, src  | dst ← src                | r    | Irr         | 82            | _ | - | _   | _   | _ | -     | 2      | 5 |

|               |                          | Irr  | r           | 92            | _ |   |     |     |   |       | 2      | 5 |

| LDEI dst, src | dst ← src                | lr   | Irr         | 83            | _ | _ | _   | -   | _ | -     | 2      | 9 |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93            | _ |   |     |     |   |       | 2      | 9 |

| LDWX dst, src | dst ← src                | ER   | ER          | 1FE8          | _ | _ | _   | _   | _ | _     | 5      | 4 |

### Table 186. eZ8 CPU Instruction Summary (Continued)

Flags notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|   |                           |                            |                              |                                |                             |                             | Lo                            | ower Nil                      | ble (He                       | x)                             |                            |                   |                           |                           |                  |                           |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|-----------------------------|-----------------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|---------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                           | 5                           | 6                             | 7                             | 8                             | 9                              | А                          | В                 | С                         | D                         | Е                | F                         |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM          | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM          | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                   |                           |                           |                  | See 2nd<br>Op Code<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br><b>SUB</b><br>r1,lr2    | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM          | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1, 2<br>ATM               |

| 3 | 2.2<br><b>DEC</b><br>R1   | 2.3<br><b>DEC</b><br>IR1   | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br>SBC<br>R2,R1         | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM          | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                   |                           |                           |                  |                           |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br>OR<br>r1,r2           | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1   | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM    | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                   |                           |                           |                  |                           |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br><b>AND</b><br>R2,R1  | 3.4<br>AND<br>IR2,R1        | 3.3<br>AND<br>R1,IM           | 3.4<br>AND<br>IR1,IM          | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.2<br>WDT                |

| 6 | 2.2<br><b>COM</b><br>R1   | 2.3<br><b>COM</b><br>IR1   | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1  | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM   | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.2<br><b>STOP</b>        |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1   | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM    | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.2<br>HALT               |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,lrr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br>LDX<br>lr1,ER2       | 3.4<br>LDX                    | 3.5<br><b>LDX</b><br>IRR2,IR1 | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br>LDX<br>rr1,r2,X         |                            |                   |                           |                           |                  | 1.2<br>DI                 |

| 9 | 2.2<br>RL<br>R1           | 2.3<br>RL<br>IR1           | 2.5<br>LDE<br>r2,lrr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1        | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br>LDX<br>IR2,IRR1        | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                   |                           |                           |                  | 1.2<br>El                 |

| A | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM    | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.4<br>RET                |

| В | 2.2<br><b>CLR</b><br>R1   | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM   | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.5<br>IRET               |

| С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1    | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X   | 3.2<br>PUSHX<br>ER2           |                                |                            |                   |                           |                           |                  | 1.2<br>RCF                |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6                         | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X   | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                   |                           |                           |                  | 1.2<br>SCF                |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br>BIT<br>p,b,r1         | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1   | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM    | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                   |                           |                           |                  | 1.2<br>CCF                |

| F | 2.2<br>SWAP<br>R1         | 2.3<br>SWAP<br>IR1         | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br>MULT<br>RR1          | 3.3<br>LD<br>R2,IR1         | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b>             |                               | , ,                            | V                          | V                 | V                         | ▼                         | V                |                           |

### Figures 67 and 68 provide information about each of the eZ8 CPUinstructions.

Figure 67. First Op Code Map

|                      |                                       |                   |          | = 0°C<br>-40°C | _                 |          |      |       |               |

|----------------------|---------------------------------------|-------------------|----------|----------------|-------------------|----------|------|-------|---------------|

|                      |                                       | V <sub>DD</sub> = | = 2.7 to | 03.6V          | V <sub>DD</sub> = | = 1.8 to | 2.7V | _     |               |

| Symbol               | Parameter                             | Min               | Тур      | Max            | Min               | Тур      | Мах  | Units | Conditions    |

| AV                   | DC Gain                               | —                 | 80       | —              | _                 | 60       | _    | dB    |               |

| PM                   | Phase Margin                          | _                 | 53       | _              | _                 | 45       | _    | deg   | 13 pF loading |

| GBW                  | Gain Bandwidth Product                | —                 | 0.3      | —              | _                 | 0.3      | _    | MHz   |               |

| V <sub>OS</sub>      | Input Offset Voltage                  | -4                | _        | 4              | -4                | _        | 4    | mV    |               |

| V <sub>OSTA</sub>    | Input Offset Temperature Drift        | _                 | 1        | 10             | _                 | 1        | 10   | µV/ºC |               |

| I <sub>outTA</sub>   | Output Current (Drive ability of LPO) | 50                | _        | -              | 40                | _        | -    | μA    |               |

| I <sub>DD</sub> LPO  | LPO Active Current                    | _                 | 10       | _              | _                 | 10       | -    | μA    |               |

| I <sub>DDQ</sub> LPO | LPO Quiescent Current                 | _                 | 5        | -              | _                 | 5        | _    | nA    |               |

| V <sub>COM</sub>     | Maximum Common Input Voltage          | _                 | _        | 1.4            | -                 | -        | 0.7  | V     |               |

### Table 199. Low Power Operational Amplifier Characteristics

### **Table 200. IPO Electrical Characteristics**

|                      |                                       |     | = 1.8 to 3<br>40°C to + |     |     | ₀ = 2.7 to 3<br>= 0°C to +7 |     |                  |

|----------------------|---------------------------------------|-----|-------------------------|-----|-----|-----------------------------|-----|------------------|

| Symbol               | Parameter                             | Min | Тур                     | Max | Min | Тур                         | Max | Units Conditions |

| T <sub>SETUP</sub>   | Setup Time for<br>Output<br>Frequency |     |                         | 15  |     |                             | 15  | μs               |

| I <sub>DD</sub> IPO  | IPO Active<br>Supply<br>Current       |     | 500                     |     |     | 500                         |     | μA               |

| I <sub>DDQ</sub> IPO | IPO Quiescent<br>Current              |     | 5                       |     |     | 5                           |     | nA               |

366

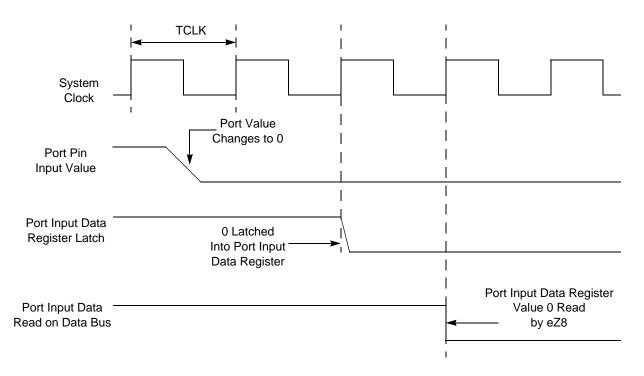

## 29.4.1. General Purpose I/O Port Input Data Sample Timing

Figure 75 displays timing of the GPIO Port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

Figure 75. Port Input Sample Timing

### Table 204. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |     |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|-----|--|--|--|--|

| Parameter           | Abbreviation                                                                                       | Min        | Max |  |  |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                        | 5          | _   |  |  |  |  |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                         | 0          | _   |  |  |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 µs       |     |  |  |  |  |

| 374 | 4 |

|-----|---|

|     |   |

| Part Number     | Flash                                                                                                              | Register RAM | Program RAM | NVDS     | 1 <sup>2</sup> C | SPI    | /O Lines | Interrupt Vectors | 6-Bit Timers w/ PWM | 0-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Multichannel Timer | Description         |

|-----------------|--------------------------------------------------------------------------------------------------------------------|--------------|-------------|----------|------------------|--------|----------|-------------------|---------------------|--------------------|----------------|------------|--------------------|--------------------|---------------------|

| _               |                                                                                                                    |              |             |          |                  |        | _        | _                 | -                   | ~                  | _              | -          | <u> </u>           | _                  |                     |

|                 | Z8 Encore! XP F1680 Series with 8KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0°C to 70°C |              |             |          |                  |        |          |                   |                     |                    |                |            |                    |                    |                     |

| Z8F0880SH020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 0      | 17       | 20                | 3                   | 7                  | 1              | 1          | 1                  | 0                  | SOIC 20-pin package |

| Z8F0880HH020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 0      | 17       | 20                | 3                   | 7                  | 1              | 1          | 1                  | 0                  | SSOP 20-pin package |

| Z8F0880PH020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 0      | 17       | 20                | 3                   | 7                  | 1              | 1          | 1                  | 0                  | PDIP 20-pin package |

| Z8F0880SJ020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 1      | 23       | 21                | 3                   | 8                  | 1              | 1          | 1                  | 0                  | SOIC 28-pin package |

| Z8F0880HJ020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 1      | 23       | 21                | 3                   | 8                  | 1              | 1          | 1                  | 0                  | SSOP 28-pin package |

| Z8F0880PJ020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 1      | 23       | 21                | 3                   | 8                  | 1              | 1          | 1                  | 0                  | PDIP 28-pin package |

| Z8F0880PM020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 1      | 33       | 23                | 3                   | 8                  | 2              | 2          | 1                  | 0                  | PDIP 40-pin package |

| Z8F0880AN020SG  | 8KB                                                                                                                | 1K B         | 1KB         | 128 B    | 1                | 1      | 37       | 24                | 3                   | 8                  | 2              | 2          | 1                  | 1                  | LQFP 44-pin package |

| Z8F0880QN020SG  | 8KB                                                                                                                | 1KB          | 1KB         | 128 B    | 1                | 1      | 37       | 24                | 3                   | 8                  | 2              | 2          | 1                  | 1                  | QFN 44-pin package  |