Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1680ph020eg    |

xviii

# List of Tables

| Table 1.  | Z8 Encore! XP F1680 Series Part Selection Guide                       | . 2 |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2.  | F1680 Series MCU Acronyms                                             | . 8 |

| Table 3.  | Z8 Encore! XP F1680 Series Package Options                            | 10  |

| Table 4.  | Signal Descriptions                                                   | 14  |

| Table 5.  | Pin Characteristics (20-, 28-, 40- and 44-pin Devices)                | 17  |

| Table 6.  | F1680 Series MCU Program Memory Maps                                  | 20  |

| Table 7.  | F1680 Series MCU Flash Memory Information Area Map                    | 22  |

| Table 8.  | Register File Address Map                                             | 23  |

| Table 9.  | Reset and Stop Mode Recovery Characteristics and Latency              | 32  |

| Table 10. | Reset Sources and Resulting Reset Type                                | 33  |

| Table 11. | Stop Mode Recovery Sources and Resulting Action                       | 38  |

| Table 12. | Reset Status Register (RSTSTAT)                                       | 40  |

| Table 13. | Reset Status Per Event                                                | 41  |

| Table 14. | Power Control Register 0 (PWRCTL0)                                    | 44  |

| Table 15. | Setup Condition for LVD and VBO Circuits in Different Operation Modes | 45  |

| Table 16. | Port Availability by Device and Package Type                          | 46  |

| Table 17. | Port Alternate Function Mapping, 20-Pin Parts1,2                      | 49  |

| Table 18. | Port Alternate Function Mapping, 28-Pin Parts1,2                      | 51  |

| Table 19. | Port Alternate Function Mapping, 40-/44-Pin Parts1,2                  | 54  |

| Table 20. | GPIO Port Registers and Subregisters                                  | 58  |

| Table 21. | Port A–E GPIO Address Registers (PxADDR)                              | 59  |

| Table 22. | Port A–E Control Registers (PxCTL).                                   | 60  |

| Table 23. | Port A–E Data Direction Subregisters (PxDD)                           | 60  |

| Table 24. | Port A–E Alternate Function Subregisters (PxAF)                       | 61  |

| Table 25. | Port A–E Output Control Subregisters (PxOC)                           | 62  |

| Table 26. | Port A–E High Drive Enable Subregisters (PxHDE)                       | 62  |

| Table 27. | Port A–E Stop Mode Recovery Source Enable Subregisters (PxSMRE)       | 63  |

| Table 28. | Port A–E Pull-Up Enable Subregisters (PxPUE)                          | 63  |

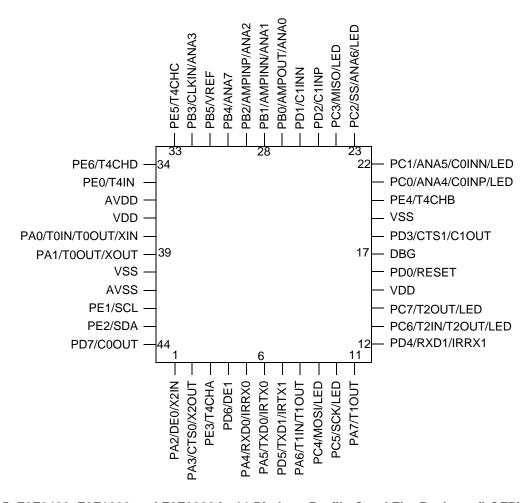

Figure 5. Z8F2480, Z8F1680 and Z8F0880 in 44-Pin Low-Profile Quad Flat Package (LQFP) or Quad Flat No Lead (QFN)

**Table 4. Signal Descriptions (Continued)**

| Signal Mnemonic               | I/O    | Description                                                                                                                                                                      |

|-------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK                           | I/O    | SPI Serial Clock: The SPI master supplies this signal. If the F1680 Series MCU is the SPI master, this pin is an output. If it is the SPI slave, this pin is an input.           |

| MOSI                          | I/O    | Master Out Slave In: This signal is the data output from the SPI master device and the data input to the SPI slave device.                                                       |

| MISO                          | I/O    | Master In Slave Out: This pin is the data input to the SPI master device and the data output from the SPI slave device.                                                          |

| Timers                        |        |                                                                                                                                                                                  |

| T0OUT/T1OUT/<br>T2OUT         | 0      | Timer Output 0–2: These signals are output from the timers.                                                                                                                      |

| T0OUT/T1OUT/<br>T2OUT         | 0      | Timer Complement Output 0–2: These signals are output from the timers in PWM DUAL OUTPUT Mode.                                                                                   |

| T0IN/T1IN/T2IN                | I      | Timer Input 0–2: These signals are used as the capture, gating and counter inputs. The T0IN/T1IN/T2IN signal is multiplexed with T0OUT/T1OUT/T2OUT signals.                      |

| Multi-Channel Tim             | ers    |                                                                                                                                                                                  |

| TACHA, TACHB,<br>TACHC, TACHD | I/O    | Multi-channel timer Input/Output: These signals function as Capture input or Compare output for channels CHA, CHB, CHC and CHD.                                                  |

| T4IN                          | 1      | Multi-channel Timer clock input: This signal allows external input to serve as the clock source for the Multi-channel timer.                                                     |

| Comparators                   |        |                                                                                                                                                                                  |

| C0INP/C0INN,<br>C1INP/C1INN   | I      | Comparator Inputs: These signals are positive and negative inputs to the comparator 0 and comparator 1.                                                                          |

| C0OUT/C1OUT                   | 0      | Comparator Outputs: These are the output from the comparator 0 and the comparator 1.                                                                                             |

| Analog                        |        |                                                                                                                                                                                  |

| ANA[7:0]                      | I      | Analog Port: These signals are used as inputs to the ADC. The ANA0, ANA1 and ANA2 pins can also access the inputs and outputs of the integrated Low-Power Operational Amplifier. |

| VREF                          | I/O    | ADC reference voltage input.                                                                                                                                                     |

| Low-Power Opera               | tional | Amplifier                                                                                                                                                                        |

| AMPINP/AMPINN                 | 1      | Low-Power Operational Amplifier Inputs: If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                    |

| AMPOUT                        | 0      | Low-Power Operational Amplifier Output: If enabled, this pin is driven by the on-chip low-power operational amplifier.                                                           |

|                               |        |                                                                                                                                                                                  |

**Table 8. Register File Address Map (Continued)**

| Address (Hex)    | Register Description                       | Mnemonic  | Reset (Hex) <sup>1</sup> | Page #     |

|------------------|--------------------------------------------|-----------|--------------------------|------------|

| F4B              | LIN UART1 Control 1—Multiprocessor Control | U1CTL1    | 00                       | <u>172</u> |

|                  | LIN UART1 Control 1—Noise Filter Control   | U1CTL1    | 00                       | <u>174</u> |

|                  | LIN UART1 Control 1—LIN Control            | U1CTL1    | 00                       | <u>175</u> |

| F4C              | LIN UART1 Mode Select and Status           | U1MDSTAT  | 00                       | <u>168</u> |

| F4D              | UART1 Address Compare                      | U1ADDR    | 00                       | <u>177</u> |

| F4E              | UART1 Baud Rate High Byte                  | U1BRH     | FF                       | <u>177</u> |

| F4F              | UART1 Baud Rate Low Byte                   | U1BRL     | FF                       | <u>178</u> |

| I <sup>2</sup> C |                                            |           |                          |            |

| F50              | I <sup>2</sup> C Data                      | I2CDATA   | 00                       | <u>244</u> |

| F51              | I <sup>2</sup> C Interrupt Status          | 12CISTAT  | 80                       | <u>245</u> |

| F52              | I <sup>2</sup> C Control                   | I2CCTL    | 00                       | <u>247</u> |

| F53              | I <sup>2</sup> C Baud Rate High Byte       | I2CBRH    | FF                       | <u>248</u> |

| F54              | I <sup>2</sup> C Baud Rate Low Byte        | I2CBRL    | FF                       | <u>249</u> |

| F55              | I <sup>2</sup> C State                     | I2CSTATE  | 02                       | <u>251</u> |

| F56              | I <sup>2</sup> C Mode                      | I2CMODE   | 00                       | <u>252</u> |

| F57              | I <sup>2</sup> C Slave Address             | I2CSLVAD  | 00                       | <u>255</u> |

| F58-F5F          | Reserved                                   | _         | XX                       |            |

| Enhanced Seria   | al Peripheral Interface (ESPI)             |           |                          |            |

| F60              | ESPI Data                                  | ESPIDATA  | XX                       | <u>214</u> |

| F61              | ESPI Transmit Data Command                 | ESPITDCR  | 00                       | 214        |

| F62              | ESPI Control                               | ESPICTL   | 00                       | <u>215</u> |

| F63              | ESPI Mode                                  | ESPIMODE  | 00                       | <u>217</u> |

| F64              | ESPI Status                                | ESPISTAT  | 01                       | <u>219</u> |

| F65              | ESPI State                                 | ESPISTATE | 00                       | <u>220</u> |

| F66              | ESPI Baud Rate High Byte                   | ESPIBRH   | FF                       | <u>220</u> |

| F67              | ESPI Baud Rate Low Byte                    | ESPIBRL   | FF                       | 220        |

| F68–F6F          | Reserved                                   | _         | XX                       |            |

|                  |                                            |           |                          |            |

#### Notes:

<sup>1.</sup> XX=Undefined.

<sup>2.</sup> The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM.

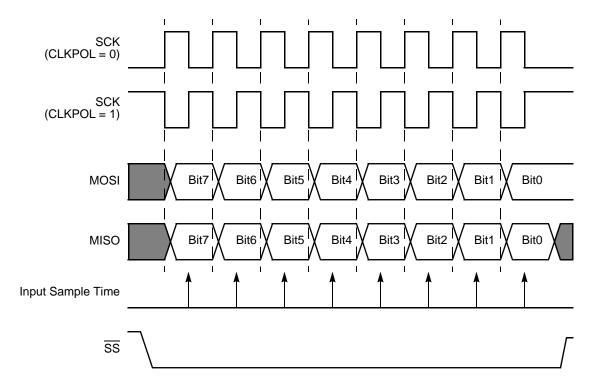

Figure 35. ESPI Timing when PHASE = 1

## 16.3.3. Slave Select Modes of Operation

This section describes the different modes of data transfer supported by the ESPI block. The mode is selected by the Slave Select Mode (SSMD) field of the Mode Register.

#### 16.3.3.1. SPI Mode

This mode is selected by setting the SSMD field of the Mode Register to 00. In this mode software controls the assertion of the  $\overline{SS}$  signal directly via the SSV bit of the SPI Transmit Data Command register. Software can be used to control an SPI mode transaction. Prior to or simultaneously with writing the first transmit data byte; software sets the SSV bit. Software sets the SSV bit either by performing a byte write to the Transmit Data Command register prior to writing the first transmit character to the Data Register or by performing a word write to the Data Register address which loads the first transmit character and simultaneously sets the SSV bit.  $\overline{SS}$  will remain asserted when one or more characters are transferred. There are two mechanisms for deasserting  $\overline{SS}$  at the end of the transaction. One method used by software is to set the TEOF bit of the Transmit Data Command register, when the last TDRE interrupt is being serviced (set TEOF before or simultaneously with writing the last data byte). After the last bit of the last character is

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>BRKPC  | Break when PC == OCDCNTR  If this bit is set to 1, then the OCDCNTR Register is used as a hardware breakpoint. When the program counter matches the value in the OCDCNTR Register, DBGMODE is automatically set to 1. If this bit is set, the OCDCNTR Register does not count when the CPU is running.  0 = OCDCNTR is set up as a counter.  1 = OCDCNTR generates a hardware break when PC == OCDCNTR. |

| [2]<br>BRKZRO | Break when OCDCNTR == 0000H  If this bit is set, then the OCD automatically sets the DBGMODE bit when the OCDCNTR  Register counts down to 0000H. If this bit is set, the OCDCNTR Register is not reset when the part exits DEBUG Mode.  0 = OCD does not generate BRK when OCDCNTR decrements to 0000H.  1 = OCD sets DBGMODE to 1 when OCDCNTR decrements to 0000H.                                   |

| [1]           | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                                                                                    |

| [0]<br>RST    | Reset Setting this bit to 1 resets the device. The controller goes through a normal POR sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 when the reset finishes.  0 = No effect.  1 = Reset the device.                                                                                                                                      |

Table 188. Absolute Maximum Ratings\* (Continued)

| Parameter                                                         | Min | Max | Units | Notes |

|-------------------------------------------------------------------|-----|-----|-------|-------|

| 44-Pin QFN Maximum Ratings at -40°C to 70°C                       |     |     |       |       |

| Total power dissipation                                           |     | 750 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 200 | mA    |       |

| 44-Pin QFN Maximum Ratings at 70°C to 105°C                       |     |     |       |       |

| Total power dissipation                                           |     | 295 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 83  | mA    |       |

| 44-pin LQFP Maximum Ratings at -40°C to 70°C                      |     |     |       |       |

| Total power dissipation                                           |     | 750 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 200 | mA    |       |

| 44-pin LQFP Maximum Ratings at 70°C to 105°C                      |     |     |       |       |

| Total power dissipation                                           |     | 410 | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>    |     | 114 | mA    |       |

| Notes: *Operating temperature is specified in DC Characteristics. |     |     |       |       |

<sup>1.</sup> This voltage applies to all pins except the following:  $\rm V_{DD},\, AV_{DD}.$

### 29.2. DC Characteristics

Table 189 lists the DC characteristics of the Z8 Encore! XP F1680 Series products. All voltages are referenced to  $V_{SS}$ , which is the primary system ground.

**Table 189. DC Characteristics**

|                  |                             | $T_A = 0^{\circ} C \text{ to } +70^{\circ} C$<br>$T_A = -40^{\circ} C \text{ to } +105^{\circ} C$ |     |                     |       |                                             |

|------------------|-----------------------------|---------------------------------------------------------------------------------------------------|-----|---------------------|-------|---------------------------------------------|

| Symbol           | Parameter                   | Min                                                                                               | Тур | Max                 | Units | Conditions                                  |

| V <sub>DD</sub>  | Supply Voltage              | 1.8                                                                                               | -   | 3.6                 | V     |                                             |

| V <sub>IL1</sub> | Low Level Input<br>Voltage  | -0.3                                                                                              | _   | 0.3*V <sub>DD</sub> | V     | For all input pins except RESET, DBG, XIN   |

| V <sub>IL2</sub> | Low Level Input<br>Voltage  | -0.3                                                                                              | -   | 0.2*V <sub>DD</sub> | V     | For RESET, DBG, XIN                         |

| V <sub>IH1</sub> | High Level Input<br>Voltage | 0.7*V <sub>DD</sub>                                                                               | -   | 5.5                 | V     | Port A, B, C, D and E pins (Digital inputs) |

#### Notes:

- 1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

- 2. These values are provided for design guidance only and are not tested in production.

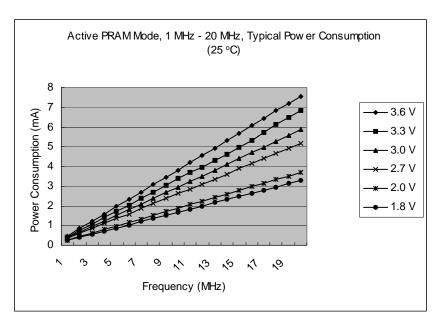

Figure 70. Typical Active PRAM Mode Supply Current (1–20MHz)

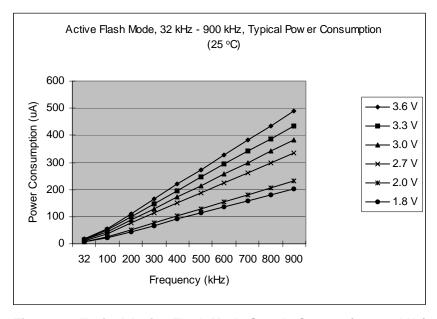

Figure 71. Typical Active Flash Mode Supply Current (32–900kHz)