Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                     |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1680pj020eg    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

vii

| 7.     | 8.    | 5 V Tole | erance                                                 | 48 |

|--------|-------|----------|--------------------------------------------------------|----|

| 7.9    | 9.    | Externa  | l Clock Setup                                          | 49 |

| 7.     | 10.   | GPIO In  | nterrupts                                              | 58 |

| 7.     | 11.   | GPIO C   | Control Register Definitions                           | 58 |

|        |       |          | Port A–E Address Registers                             |    |

|        |       |          | Port A–E Control Registers                             |    |

|        |       |          | Port A–E Data Direction Subregisters                   |    |

|        |       | 7.11.4.  | Port A–E Alternate Function Subregisters               | 61 |

|        |       | 7.11.5.  | Port A–E Output Control Subregisters                   | 62 |

|        |       | 7.11.6.  | Port A–E High Drive Enable Subregisters                | 62 |

|        |       | 7.11.7.  | Port A–E Stop Mode Recovery Source Enable Subregisters | 63 |

|        |       | 7.11.8.  | Port A–E Pull-up Enable Subregisters                   | 63 |

|        |       | 7.11.9.  | Port A–E Alternate Function Set 1 Subregisters         | 64 |

|        |       | 7.11.10. | Port A–E Alternate Function Set 2 Subregisters         | 64 |

|        |       | 7.11.11. | Port A–E Input Data Registers                          | 65 |

|        |       |          | .Port A–E Output Data Register                         |    |

|        |       |          | LED Drive Enable Register                              |    |

|        |       | 7.11.14. | LED Drive Level Registers                              | 67 |

| Chapte | er 8. | Interru  | ıpt Controller                                         | 68 |

| 8.     | 1.    | Interrup | ot Vector Listing                                      | 68 |

| 8.3    | 2.    | •        | cture                                                  |    |

| 8      | 3     |          | on                                                     |    |

| 0      |       | _        | Master Interrupt Enable                                |    |

|        |       |          | Interrupt Vectors and Priority                         |    |

|        |       |          | Interrupt Assertion                                    |    |

|        |       |          | Software Interrupt Assertion                           |    |

| 8.4    | 4.    |          | ot Control Register Definitions                        |    |

|        |       | _        | Interrupt Request 0 Register                           |    |

|        |       |          | Interrupt Request 1 Register                           |    |

|        |       |          | Interrupt Request 2 Register                           |    |

|        |       |          | IRQ0 Enable High and Low Bit Registers                 |    |

|        |       |          | IRQ1 Enable High and Low Bit Registers                 |    |

|        |       | 8.4.6.   | IRQ2 Enable High and Low Bit Registers                 | 79 |

|        |       | 8.4.7.   | Interrupt Edge Select Register                         | 82 |

|        |       | 8.4.8.   | Shared Interrupt Select Register                       | 82 |

|        |       | 8.4.9.   | Interrupt Control Register                             | 83 |

| Chapte | er 9. | Timers   | s                                                      | 84 |

| 9.     |       |          | cture                                                  |    |

| 9.     |       |          | on                                                     |    |

| ر.     | ٠-    | Speran   | VII                                                    | O. |

# Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

X

|           | 12.3.5. LIN-UART Control 0 Register                    | 170 |

|-----------|--------------------------------------------------------|-----|

|           | 12.3.6. LIN-UART Control 1 Registers                   | 171 |

|           | 12.3.7. Noise Filter Control Register                  | 174 |

|           | 12.3.8. LIN Control Register                           | 175 |

|           | 12.3.9. LIN-UART Address Compare Register              |     |

|           | 12.3.10.LIN-UART Baud Rate High and Low Byte Registers | 177 |

| Chapter 1 | 3. Infrared Encoder/Decoder                            | 182 |

| 13.1.     | Architecture                                           | 182 |

| 13.2.     | Operation                                              | 182 |

|           | 13.2.1. Transmitting IrDA Data                         | 183 |

|           | 13.2.2. Receiving IrDA Data                            | 184 |

| 13.3.     | Infrared Encoder/Decoder Control Register Definitions  | 185 |

| Chapter 1 | 4. Analog-to-Digital Converter                         | 186 |

| 14.1.     | Architecture                                           | 186 |

| 14.2.     | Operation                                              | 186 |

|           | 14.2.1. ADC Timing                                     | 187 |

|           | 14.2.2. ADC Interrupt                                  | 188 |

|           | 14.2.3. Reference Buffer                               | 188 |

|           | 14.2.4. Internal Voltage Reference Generator           | 189 |

|           | 14.2.5. Calibration and Compensation                   | 189 |

| 14.3.     | ADC Control Register Definitions                       | 189 |

|           | 14.3.1. ADC Control Register 0                         | 189 |

|           | 14.3.2. ADC Raw Data High Byte Register                | 191 |

|           | 14.3.3. ADC Data High Byte Register                    | 191 |

|           | 14.3.4. ADC Data Low Bits Register                     | 192 |

|           | 14.3.5. Sample Settling Time Register                  | 193 |

|           | 14.3.6. Sample Time Register                           | 194 |

|           | 14.3.7. ADC Clock Prescale Register                    | 195 |

| Chapter 1 | 5. Low-Power Operational Amplifier                     | 196 |

| Chapter 1 | 6. Enhanced Serial Peripheral Interface                | 197 |

| 16.1.     | Architecture                                           | 197 |

| 16.2.     | ESPI Signals                                           | 199 |

|           | 16.2.1. Master-In/Slave-Out                            | 199 |

|           | 16.2.2. Master-Out/Slave-In                            | 199 |

|           | 16.2.3. Serial Clock                                   | 199 |

|           | 16.2.4. Slave Select                                   | 200 |

| 16.3.     | Operation                                              | 200 |

|           | 16.3.1 Throughput                                      | 201 |

# Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

xvi

| Figure 27. | Infrared Data Communication System Block Diagram                           |

|------------|----------------------------------------------------------------------------|

| Figure 28. | Infrared Data Transmission                                                 |

| Figure 29. | IrDA Data Reception                                                        |

| Figure 30. | Analog-to-Digital Converter Block Diagram                                  |

| Figure 31. | ADC Timing Diagram                                                         |

| Figure 32. | ADC Convert Timing                                                         |

| Figure 33. | ESPI Block Diagram                                                         |

| Figure 34. | ESPI Timing when PHASE=0                                                   |

| Figure 35. | ESPI Timing when PHASE = 1                                                 |

| Figure 36. | SPI Mode (SSMD = 00)                                                       |

| Figure 37. | Synchronous Frame Sync Pulse mode (SSMD = 10)                              |

| Figure 38. | Synchronous Message Framing Mode (SSMD = 11), Multiple Frames 207          |

| Figure 39. | ESPI Configured as an SPI Master in a Single Master, Single Slave System   |

| Figure 40. | ESPI Configured as an SPI Master in a Single Master, Multiple Slave System |

| Figure 41. | ESPI Configured as an SPI Slave                                            |

| Figure 42. | I2C Controller Block Diagram                                               |

| Figure 43. | Data Transfer Format—Master Write Transaction with a 7-Bit Address . 230   |

| Figure 44. | Data Transfer Format—Master Write Transaction with a 10-Bit Address 231    |

| Figure 45. | Data Transfer Format—Master Read Transaction with a 7-Bit Address . 233    |

| Figure 46. | Data Transfer Format—Master Read Transaction with a 10-Bit Address 234     |

| Figure 47. | Data Transfer Format—Slave Receive Transaction with 7-Bit Address 238      |

| Figure 48. | Data Transfer Format—Slave Receive Transaction with 10-Bit Address . 239   |

| Figure 49. | Data Transfer Format—Slave Transmit Transaction with 7-bit Address . 240   |

| Figure 50. | Data Transfer Format—Slave Transmit Transaction with 10-Bit Address 242    |

| Figure 51. | 8KB Flash Memory Arrangement                                               |

| Figure 52. | 16KB Flash Memory Arrangement                                              |

| Figure 53. | 24KB Flash Memory Arrangement                                              |

| Figure 54. | Flowchart: Flash Controller Operation                                      |

| Figure 55. | On-Chip Debugger Block Diagram                                             |

Table 7. F1680 Series MCU Flash Memory Information Area Map

| Program Memory Address (Hex) | Function                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------|

| FE00-FE3F                    | Zilog option bits                                                                         |

| FE40-FE53                    | Part Number:<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                    | Reserved                                                                                  |

| FE60-FE7F                    | Zilog calibration data (only use the first two bytes FE60 and FE61)                       |

| FE80-FFFF                    | Reserved                                                                                  |

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                                                    | Reset Characteristics and Latency                     |         |                                                                                                                                                                 |  |

|----------------------------------------------------|-------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset Type                                         | Control Registers                                     | eZ8 CPU | Reset Latency (Delay)                                                                                                                                           |  |

| System Reset (non-POR Reset)                       | Reset (as applicable)                                 | Reset   | 68 Internal Precision Oscillator Cycles after IPO starts up                                                                                                     |  |

| System Reset (POR Reset)                           | Reset (as applicable)                                 | Reset   | 68 Internal Precision Oscillator Cycles + 50ms Wait time                                                                                                        |  |

| System Reset with<br>Crystal Oscillator<br>Enabled | Reset (as applicable)                                 | Reset   | 568–10068 Internal Precision Oscillator<br>Cycles after IPO starts up; see <u>Table 141</u><br>on page 280 for a description of the<br>EXTLTMG user option bit. |  |

| Stop Mode Recovery                                 | Unaffected, except<br>RSTSTAT and<br>OSCCTL registers | Reset   | 4 Internal Precision Oscillator Cycles after IPO starts up                                                                                                      |  |

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator (IPO) requires  $4\mu s$  to start up. When the reset type is a System Reset, the F1680 Series MCU is held in Reset for 68 IPO cycles. If the crystal oscillator is enabled in Flash option bits, the Reset period is increased to  $568{\text -}10068$  IPO cycles. For more details, see Table 141 on page 280 for a description of the EXTLTMG user option bit. When the reset type is a Stop Mode Recovery, the F1680 Series MCU goes to NORMAL Mode immediately after 4 IPO cycles. The total Stop Mode Recovey delay is less than  $6\mu s$ . When a Reset occurs due to a VBO condition, this delay is measured from the time the supply voltage first exceeds the VBO level (discussed later in this chapter). When a Reset occurs due to a POR condition, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the Reset period, the device remains in reset until the pin is deasserted.

#### Note:

After a Stop Mode Recovery, the external crystal oscillator is unstable. Use software to wait until it is stable before you can use it as main clock.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 that is shared with the Reset pin. On Reset, the Port D0 pin is configured as a bidirectional open-drain Reset. The pin is internally driven Low during port reset, after which the user code can reconfigure this pin as a general-purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and WDT oscillator continue to function.

#### **Table 88. Mode Status Fields**

| MULTIPROCESSOR<br>Mode Status Field       | NEWFRM Status bit denoting the start of a new frame. Reading the LIN-UART Receive Data Register resets this bit to 0. 0 = The current byte is not the first data byte of a new frame. 1 = The current byte is the first data byte of a new frame.                                                                                                                                                   |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                           | Multiprocessor Receive (MPRX) Returns the value of the last multiprocessor bit received. Reading from the LIN-UART Receive Data Register resets this bit to 0.                                                                                                                                                                                                                                      |  |

| Digital Noise Filter<br>Mode Status Field | Noise Event (NE); MSEL = 001b  This bit is asserted if digital noise is detected on the receive data line when the data is sampled (center of bit-time). If this bit is set, it does not mean that the receive data is corrupted (though it can be in extreme cases), means that one or more of the noise filter data samples near the center of the bit-time did not match the average data value. |  |

| LIN Mode Status Field                     | Noise Event (NE); MSEL = 010b  This bit is asserted if some noise level is detected on the receive data line when the data is sampled (center of bit-time). If this bit is set, it does not indicate that the receive data is corrupt (though it can be in extreme cases), means that one or more of the 16x data samples near the center of the bit-time did not match the average data value.     |  |

|                                           | RxBreakLength LIN mode received break length. This field can be read following a break (LIN Wake-up or Break) so that the software can determine the measured duration of the break. If the break exceeds 15 bit times the value saturates at 1111b.                                                                                                                                                |  |

| Hardware Revision<br>Mode Status Field    | Noise Event (NE); MSEL = 111b  This field indicates the hardware revision of the LIN-UART block.  00_xxx LIN UART hardware revision.  01_xxx Reserved.  10_xxx Reserved.  11_xxx Reserved.                                                                                                                                                                                                          |  |

A receive interrupt is generated by the RDRNE status bit when the ESPI block is enabled, the DIRQE bit is set and a character transfer completes. At the end of the character transfer, the contents of the Shift Register are transferred into the Data Register, causing the RDRNE bit to assert. The RDRNE bit is cleared when the Data Buffer is read as empty. If information is being transmitted but not received by the software application, the receive interrupt can be eliminated by selecting Transmit Only mode (ESPIEN1,0 = 10) in either MASTER or SLAVE modes. When information is being sent and received under interrupt control, RDRNE and TDRE will both assert simultaneously at the end of a character transfer. Since the new receive data is in the Data Register, the receive interrupt must be serviced before the transmit interrupt.

ESPI error interrupts occur if any of the TUND, COL, ABT and ROVR bits in the ESPI Status Register are set. These bits are cleared by writing a 1. If the ESPI is disabled (ESPIEN1, 0 = 00), an ESPI interrupt can be generated by a Baud Rate Generator timeout. This timer function must be enabled by setting the BRGCTL bit in the ESPICTL register. This timer interrupt does not set any of the bits of the ESPI Status Register.

#### 16.3.7. ESPI Baud Rate Generator

In ESPI MASTER Mode, the Baud Rate Generator creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the Baud Rate Generator is the system clock. The ESPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the ESPI Baud Rate Generator. The ESPI baud rate is calculated using the following equation:

SPI Baud Rate (bits § s) =

$$\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$$

Minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of  $(2 \times 65536 = 131072)$ .

When the ESPI is disabled, the Baud Rate Generator can function as a basic 16-bit timer with interrupt on time-out. Observe the following steps to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the ESPI by clearing the ESPIEN1,0 bits in the ESPI Control Register.

- 2. Load the appropriate 16-bit count value into the ESPI Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the ESPI Control Register to 1.

When configured as a general purpose timer, the SPI BRG interrupt interval is calculated using the following equation:

| Bit                          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6,0]<br>ESPIEN1,<br>ESPIEN0 | ESPI Enable and Direction Control  00 = The ESPI block is disabled. BRG can be used as a general-purpose timer by setting BRGCTL = 1.  01 = Receive Only Mode. Use this setting in SLAVE Mode if software application is receiving data but not sending. TDRE will not assert. Transmitted data will be all 1s. Not valid in MASTER Mode since Master must source data to drive the transfer.  10 = Transmit Only Mode  Use this setting in MASTER or SLAVE Mode when the software application is sending data but not receiving. RDRNE will not assert.  11 = Transmit/Receive Mode  Use this setting if the software application is both sending and receiving information. Both TDRE and RDRNE will be active.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [5]<br>BRGCTL                | Baud Rate Generator Control  The function of this bit depends upon ESPIEN1,0. When ESPIEN1,0 = 00, this bit allows enabling the BRG to provide periodic interrupts.  If the ESPI is disabled  0 = The Baud Rate Generator timer function is disabled. Reading the Baud Rate High and Low registers returns the BRG reload value.  1 = The Baud Rate Generator timer function and time-out interrupt is enabled. Reading the Baud Rate High and Low registers returns the BRG Counter value.  If the ESPI is enabled  0 = Reading the Baud Rate High and Low registers returns the BRG reload value. If MMEN = 1, the BRG is enabled to generate SCK. If MMEN = 0, the BRG is disabled.  1 = Reading the Baud Rate High and Low registers returns the BRG Counter value. If MMEN = 1, the BRG is enabled to generate SCK. If MMEN = 0 the BRG is enabled to provide a Slave SCK time-out. See the SLAVE Mode Abort error description on page 211.  Caution: If reading the counter one byte at a time while the BRG is counting keep in mind that the values will not be in sync. Zilog recommends reading the counter using (2-byte) word reads. |

| [4]<br>PHASE                 | Phase Select Sets the phase relationship of the data to the clock. For more information about operation of the PHASE bit, see the ESPI Clock Phase and Polarity Control section on page 201.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [3]<br>CLKPOL                | Clock Polarity 0 = SCK idles Low (0). 1 = SCK idles High (1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [2]<br>WOR                   | Wire-OR (Open-Drain) Mode Enabled  0 = ESPI signal pins not configured for open-drain.  1 = All four ESPI signal pins (SCK, SS, MISO and MOSI) configured for open-drain function.  This setting is typically used for multi-Master and/or Multi-Slave configurations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [1]<br>MMEN                  | ESPI MASTER Mode Enable  This bit controls the data I/O pin selection and SCK direction.  0 = Data out on MISO, data in on MOSI (used in SPI SLAVE Mode), SCK is an input.  1 = Data out on MOSI, data in on MISO (used in SPI MASTER Mode), SCK is an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- 4. If this operation is a single-byte transfer, the software asserts the NAK bit of the I<sup>2</sup>C Control Register so that after the first byte of data has been read by the I<sup>2</sup>C controller, a Not Acknowledge instruction is sent to the I<sup>2</sup>C slave.

- 5. The I<sup>2</sup>C controller sends a start condition.

- 6. The I<sup>2</sup>C controller sends the address and Read bit out via the SDA signal.

- 7. The I<sup>2</sup>C slave acknowledges the address by pulling the SDA signal Low during the next High period of SCL.

If the slave does not acknowledge the address byte, the I<sup>2</sup>C controller sets the NCKI bit in the I<sup>2</sup>C Status Register, sets the ACKV bit and clears the ACK bit in the I<sup>2</sup>C State Register. The software responds to the Not Acknowledge interrupt by setting the stop bit and clearing the TXI bit. The I<sup>2</sup>C controller flushes the Transmit Data Register, sends a stop condition on the bus and clears the stop and NCKI bits. The transaction is complete and the following steps can be ignored.

- 8. The I<sup>2</sup>C controller shifts in the first byte of data from the I<sup>2</sup>C slave on the SDA signal.

- 9. The I<sup>2</sup>C controller asserts the receive interrupt.

- 10. The software responds by reading the I<sup>2</sup>C Data Register. If the next data byte is to be the final byte, the software must set the NAK bit of the I<sup>2</sup>C Control Register.

- 11. The I<sup>2</sup>C controller sends a Not Acknowledge to the I<sup>2</sup>C slave if the next byte is the final byte; otherwise, it sends an Acknowledge.

- 12. If there are more bytes to transfer, the  $I^2C$  controller returns to <u>Step 7</u>.

- 13. A NAK interrupt (NCKI bit in I2CISTAT) is generated by the  $I^2C$  controller.

- 14. The software responds by setting the stop bit of the I<sup>2</sup>C Control Register.

- 15. A stop condition is sent to the  $I^2C$  slave.

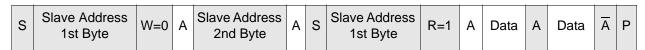

#### 17.2.5.7. Master Read Transaction with a 10-Bit Address

Figure 46 displays the read transaction format for a 10-bit addressed Slave.

Figure 46. Data Transfer Format—Master Read Transaction with a 10-Bit Address

The first 7 bits transmitted in the first byte are 11110xx. The two xx bits are the two most-significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write control bit.

Observe the following data transfer procedure for a Read operation to a 10-bit addressed slave:

| U | Otart           |

|---|-----------------|

| W | Write           |

| Α | Acknowledge     |

| Ā | Not Acknowledge |

Start

P Stop

S

#### 17.2.6.5. Slave Receive Transaction with 7-Bit Address

The data transfer format for writing data from a Master to a Slave in 7-bit address mode is displayed in Figure 47. The procedure that follows describes the I<sup>2</sup>C Master/Slave Controller operating as a slave in 7-bit addressing mode and receiving data from the bus master.

| S | Slave Address | W=0 | Α | Data | Α | Data | Α | Data | $A/\overline{A}$ | P/S |

|---|---------------|-----|---|------|---|------|---|------|------------------|-----|

|   |               |     |   |      |   |      |   |      |                  |     |

Figure 47. Data Transfer Format—Slave Receive Transaction with 7-Bit Address

- 1. The software configures the controller for operation as a slave in 7-bit addressing mode, as follows:

- a. Initialize the MODE field in the I<sup>2</sup>C Mode Register for either SLAVE ONLY mode or MASTER/SLAVE Mode with 7-bit addressing.

- b. Optionally set the GCE bit.

- c. Initialize the SLA[6:0] bits in the I<sup>2</sup>C Slave Address Register.

- d. Set IEN = 1 in the  $I^2C$  Control Register. Set NAK = 0 in the  $I^2C$  Control Register.

- 2. The bus master initiates a transfer, sending the address byte. In SLAVE Mode, the  $I^2C$  controller recognizes its own address and detects that  $R/\overline{W}$  bit = 0 (written from the master to the slave). The  $I^2C$  controller acknowledges indicating it is available to accept the transaction. The SAM bit in the I2CISTAT Register is set to 1, causing an interrupt. The RD bit in the I2CISTAT Register is cleared to 0, indicating a Write to the slave. The  $I^2C$  controller holds the SCL signal Low waiting for the software to load the first data byte.

- 3. The software responds to the interrupt by reading the I2CISTAT Register (which clears the SAM bit). After seeing the SAM bit to 1, the software checks the RD bit. Because RD = 0, no immediate action is required until the first byte of data is received. If software is only able to accept a single byte, it sets the NAK bit in the I2CCTL Register at this time.

- 4. The Master detects the Acknowledge and sends the byte of data.

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>BRKPC  | Break when PC == OCDCNTR  If this bit is set to 1, then the OCDCNTR Register is used as a hardware breakpoint. When the program counter matches the value in the OCDCNTR Register, DBGMODE is automatically set to 1. If this bit is set, the OCDCNTR Register does not count when the CPU is running.  0 = OCDCNTR is set up as a counter.  1 = OCDCNTR generates a hardware break when PC == OCDCNTR. |

| [2]<br>BRKZRO | Break when OCDCNTR == 0000H  If this bit is set, then the OCD automatically sets the DBGMODE bit when the OCDCNTR  Register counts down to 0000H. If this bit is set, the OCDCNTR Register is not reset when the part exits DEBUG Mode.  0 = OCD does not generate BRK when OCDCNTR decrements to 0000H.  1 = OCD sets DBGMODE to 1 when OCDCNTR decrements to 0000H.                                   |

| [1]           | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                                                                                    |

| [0]<br>RST    | Reset Setting this bit to 1 resets the device. The controller goes through a normal POR sequence with the exception that the On-Chip Debugger is not reset. This bit is automatically cleared to 0 when the reset finishes.  0 = No effect.  1 = Reset the device.                                                                                                                                      |

Table 186. eZ8 CPU Instruction Summary (Continued)

| Assembly                                     |                                     | Address<br>Mode C |       | Op<br>Code(s) | Flags |   |   |   |   |   | Fetch | Instr. |

|----------------------------------------------|-------------------------------------|-------------------|-------|---------------|-------|---|---|---|---|---|-------|--------|

| Mnemonic                                     | Symbolic Operation                  | dst               | src   | (Hex)         | С     | Z | s | ٧ | D | Н |       |        |

| LDX dst, src                                 | dst ← src                           | r                 | ER    | 84            | _     | - | - | - | - | - | 3     | 2      |

|                                              |                                     | lr                | ER    | 85            | _     |   |   |   |   |   | 3     | 3      |

|                                              |                                     | R                 | IRR   | 86            |       |   |   |   |   |   | 3     | 4      |

|                                              |                                     | IR                | IRR   | 87            | _     |   |   |   |   |   | 3     | 5      |

|                                              |                                     | r                 | X(rr) | 88            | _     |   |   |   |   |   | 3     | 4      |

|                                              |                                     | X(rr)             | r     | 89            | _     |   |   |   |   |   | 3     | 4      |

|                                              |                                     | ER                | r     | 94            | _     |   |   |   |   |   | 3     | 2      |

|                                              |                                     | ER                | lr    | 95            | _     |   |   |   |   |   | 3     | 3      |

|                                              |                                     | IRR               | R     | 96            | _     |   |   |   |   |   | 3     | 4      |

|                                              |                                     | IRR               | IR    | 97            | _     |   |   |   |   |   | 3     | 5      |

|                                              |                                     | ER                | ER    | E8            | _     |   |   |   |   |   | 4     | 2      |

|                                              |                                     | ER                | IM    | E9            | _     |   |   |   |   |   | 4     | 2      |

| LEA dst, $X(src)$ dst $\leftarrow$ src + $X$ |                                     | r                 | X(r)  | 98            | _     | _ | _ | - | _ | _ | 3     | 3      |

|                                              |                                     | rr                | X(rr) | 99            | _     |   |   |   |   |   | 3     | 5      |

| MULT dst                                     | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR                |       | F4            | -     | - | _ | - | - | - | 2     | 8      |

| NOP                                          | No operation                        |                   |       | 0F            | _     | - | _ | - | _ | _ | 1     | 2      |

| OR dst, src                                  | dst ← dst OR src                    | r                 | r     | 42            | -     | * | * | 0 | _ | _ | 2     | 3      |

|                                              |                                     | r                 | lr    | 43            | _     |   |   |   |   |   | 2     | 4      |

|                                              |                                     | R                 | R     | 44            | _     |   |   |   |   |   | 3     | 3      |

|                                              |                                     | R                 | IR    | 45            | _     |   |   |   |   |   | 3     | 4      |

|                                              |                                     | R                 | IM    | 46            | _     |   |   |   |   |   | 3     | 3      |

|                                              |                                     | IR                | IM    | 47            | _     |   |   |   |   |   | 3     | 4      |

| ORX dst, src                                 | dst ← dst OR src                    | ER                | ER    | 48            | _     | * | * | 0 | _ | _ | 4     | 3      |

|                                              |                                     | ER                | IM    | 49            | _     |   |   |   |   |   | 4     | 3      |

| POP dst                                      | dst ← @SP                           | R                 |       | 50            | _     | _ | _ | _ | _ | _ | 2     | 2      |

|                                              | SP ← SP + 1                         | IR                |       | 51            | _     |   |   |   |   |   | 2     | 3      |

### Flags notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 200. IPO Electrical Characteristics (Continued)

|                  |                                        |         | = 1.8 to 3<br>40°C to + |         |          | = 2.7 to 3<br>0°C to + |          |       |                                   |

|------------------|----------------------------------------|---------|-------------------------|---------|----------|------------------------|----------|-------|-----------------------------------|

| Symbol           | Parameter                              | Min     | Тур                     | Max     | Min      | Тур                    | Max      | Units | Conditions                        |

|                  | Output<br>Frequency                    | 10.6168 | 11.0592                 | 11.5016 | 10.78272 | 11.0592                | 11.33568 |       |                                   |

|                  | Divided-by-2<br>Output<br>Frequency    | 5.3084  | 5.5296                  | 5.7508  | 5.39136  | 5.5296                 | 5.66784  | _     |                                   |

|                  | Divided-by-4<br>Output<br>Frequency    | 2.6542  | 2.7648                  | 2.8754  | 2.69568  | 2.7648                 | 2.83392  | _     | ±2.5% 2.7 to 3.6 V,               |

|                  | Divided-by-8<br>Output<br>Frequency    | 1.3271  | 1.3824                  | 1.4377  | 1.34784  | 1.3824                 | 1.41696  | _     | 0–70°C;<br>±4% 1.8 to             |

| F <sub>IPO</sub> | Divided-by-16<br>Output<br>Frequency   | 0.6636  | 0.6912                  | 0.7188  | 0.67392  | 0.6912                 | 0.70848  | MHz   | 2.7 V,<br>0-70°C                  |

|                  | Divided-by-32<br>Output<br>Frequency   | 0.3318  | 0.3456                  | 0.3594  | 0.33696  | 0.3456                 | 0.35424  | _     | ±4% 1.8 to<br>3.6 V,<br>-40-105°C |

|                  | Divided-by-<br>128 Output<br>Frequency | 0.0829  | 0.0864                  | 0.0899  | 0.08424  | 0.0864                 | 0.08856  | _     |                                   |

|                  | Divided-by-<br>256 Output<br>Frequency | 0.0415  | 0.0432                  | 0.0449  | 0.04212  | 0.0432                 | 0.04428  | _     |                                   |

|                  | Duty Cycle of<br>Output                | 45      |                         | 55      | 45       |                        | 55       | %     |                                   |

**Table 201. Low Voltage Detect Electrical Characteristics**

|                      |                         | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ |                              |                       |       |            |

|----------------------|-------------------------|-----------------------------------------------------------------------------------------------|------------------------------|-----------------------|-------|------------|

|                      |                         | $V_{DD} = 1.8 \text{ to } 3.6 \text{ V}$                                                      |                              |                       |       |            |

| Symbol               | Parameter               | Min                                                                                           | Тур                          | Max                   | Units | Conditions |

| I <sub>DD</sub> LVD  | LVD Active Current      | _                                                                                             | _                            | 50                    | μΑ    |            |

| I <sub>DDQ</sub> LVD | LVD Quiescent Current   | -                                                                                             | 5                            | _                     | nA    |            |

| $V_{TH}$             | Detected Source Voltage | V <sub>TP</sub> – 10%                                                                         | V <sub>TP</sub> <sup>1</sup> | V <sub>TP</sub> + 10% | V     |            |

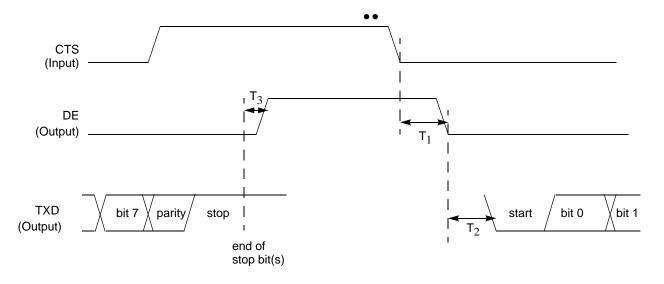

## **29.4.4. UART Timing**

Figure 78 and Table 207 provide timing information for the UART pins for situations in which CTS is used for flow control. The CTS to DE assertion delay (T1) assumes that the Transmit Data Register has been loaded with data prior to CTS assertion.

Figure 78. UART Timing With CTS

Table 207. UART Timing with CTS

|                |                                                    | Delay (ns)                 |                                            |  |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                       | Min                        | Max                                        |  |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period<br>+ 1 bit time |  |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | ± 5                        |                                            |  |  |  |  |

| T <sub>3</sub> | End of stop bit(s) to DE deassertion delay         | ± 5                        |                                            |  |  |  |  |

Figure 79 and Table 208 provide timing information for the UART pins for situations in which CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| input data sample timing 366                     | IM 330                              |

|--------------------------------------------------|-------------------------------------|

| interrupts 58                                    | immediate data 330                  |

| port A-C pull-up enable sub-registers 63, 64     | immediate operand prefix 331        |

| port A-H address registers 59                    | INC 332                             |

| port A-H alternate function sub-registers 61     | increment 332                       |

| port A-H control registers 60                    | increment word 332                  |

| port A-H data direction sub-registers 60         | INCW 332                            |

| port A-H high drive enable sub-registers 62      | indexed 330                         |

| port A-H input data registers 65                 | indirect address prefix 331         |

| port A-H output control sub-registers 62         | indirect register 330               |

| port A-H output data registers 66                | indirect register pair 330          |

| port A-H stop mode recovery sub-registers 63     | indirect working register 330       |

| port availability by device 46                   | indirect working register pair 330  |

| port input timing 366                            | infrared encoder/decoder (IrDA) 182 |

| port output timing 367                           | Instruction Set 328                 |

|                                                  | instruction set, ez8 CPU 328        |

| H                                                | instructions                        |

| H 331                                            | ADC 332                             |

| HALT 333                                         | ADCX 332                            |

| halt mode 43, 333                                | ADD 332                             |

| hexadecimal number prefix/suffix 331             | ADDX 332                            |

|                                                  | AND 334                             |

| 1                                                | ANDX 334                            |

| I2C 4                                            | arithmetic 332                      |

| 10-bit address read transaction 234              | BCLR 333                            |

| 10-bit address transaction 231                   | BIT 333                             |

| 10-bit addressed slave data transfer format 231, | bit manipulation 333                |

| 239                                              | block transfer 333                  |

| 7-bit address transaction 228, 236               | BRK 335                             |

| 7-bit address, reading a transaction 233         | BSET 333                            |

| 7-bit addressed slave data transfer format 230,  | BSWAP 333, 335                      |

| 238                                              | BTJ 335                             |

| 7-bit receive data transfer format 234, 240, 242 | BTJNZ 335                           |

| baud high and low byte registers 248, 250, 255   | BTJZ 335                            |

| C status register 251                            | CALL 335                            |

| controller 223                                   | CCF 333                             |

| controller signals 14                            | CLR 334                             |

| interrupts 226                                   | COM 334                             |

| operation 225                                    | CP 332                              |

| SDA and SCL signals 225                          | CPC 332                             |

| stop and start conditions 228                    | CPCX 332                            |

| I2CBRH register 250, 255                         | CPU control 333                     |

| I2CCTL register 247                              | CPX 332                             |

| I2CSTAT register 251                             | DA 332                              |

|                                                  |                                     |