Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 37                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-VFQFN Exposed Pad                                         |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1680gn020eg    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Date        | Revision<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page                                                      |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Oct<br>2007 | 06                | Updated Trim Bit Address Description, Trim Bit Address 0007H, Trim Bit Address 0008H, DC Characteristics, Supply Current Characteristics, VDD Versus Maximum System Clock Frequency, Watchdog Timer Electrical Characteristics and Timing, Analog-to-Digital Converter Electrical Characteristics and Timing, Comparator Electrical Characteristics, Low Power Operational Amplifier Characteristics, IPO Electrical Characteristics and Low Voltage Detect Electrical Characteristics. Added Figure 73. | 282, 288, 288,<br>350, 352, 356,<br>357, 359, 360,<br>361 |

| Sep<br>2007 | 05                | Updated Supply Current Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>352</u>                                                |

| Aug<br>2007 | 04                | Changed description of Z8F16800144ZCOG to Z8 Encore! XP Dual 44-pin F1680 Series Development Kit. Updated electrical characteristics in Table 189, Table 190, Table 192, Table 193, Table 195, Table 196. Removed VBO_Trim section and table.                                                                                                                                                                                                                                                            | 350, 352, 358,<br>359, 360, 374                           |

# Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

X

|           | 12.3.5. LIN-UART Control 0 Register                    | 170 |

|-----------|--------------------------------------------------------|-----|

|           | 12.3.6. LIN-UART Control 1 Registers                   | 171 |

|           | 12.3.7. Noise Filter Control Register                  | 174 |

|           | 12.3.8. LIN Control Register                           | 175 |

|           | 12.3.9. LIN-UART Address Compare Register              |     |

|           | 12.3.10.LIN-UART Baud Rate High and Low Byte Registers | 177 |

| Chapter 1 | 3. Infrared Encoder/Decoder                            | 182 |

| 13.1.     | Architecture                                           | 182 |

| 13.2.     | Operation                                              | 182 |

|           | 13.2.1. Transmitting IrDA Data                         | 183 |

|           | 13.2.2. Receiving IrDA Data                            | 184 |

| 13.3.     | Infrared Encoder/Decoder Control Register Definitions  | 185 |

| Chapter 1 | 4. Analog-to-Digital Converter                         | 186 |

| 14.1.     | Architecture                                           | 186 |

| 14.2.     | Operation                                              | 186 |

|           | 14.2.1. ADC Timing                                     | 187 |

|           | 14.2.2. ADC Interrupt                                  | 188 |

|           | 14.2.3. Reference Buffer                               | 188 |

|           | 14.2.4. Internal Voltage Reference Generator           | 189 |

|           | 14.2.5. Calibration and Compensation                   | 189 |

| 14.3.     | ADC Control Register Definitions                       | 189 |

|           | 14.3.1. ADC Control Register 0                         | 189 |

|           | 14.3.2. ADC Raw Data High Byte Register                | 191 |

|           | 14.3.3. ADC Data High Byte Register                    | 191 |

|           | 14.3.4. ADC Data Low Bits Register                     | 192 |

|           | 14.3.5. Sample Settling Time Register                  | 193 |

|           | 14.3.6. Sample Time Register                           | 194 |

|           | 14.3.7. ADC Clock Prescale Register                    | 195 |

| Chapter 1 | 5. Low-Power Operational Amplifier                     | 196 |

| Chapter 1 | 6. Enhanced Serial Peripheral Interface                | 197 |

| 16.1.     | Architecture                                           | 197 |

| 16.2.     | ESPI Signals                                           | 199 |

|           | 16.2.1. Master-In/Slave-Out                            | 199 |

|           | 16.2.2. Master-Out/Slave-In                            | 199 |

|           | 16.2.3. Serial Clock                                   | 199 |

|           | 16.2.4. Slave Select                                   | 200 |

| 16.3.     | Operation                                              | 200 |

|           | 16.3.1 Throughput                                      | 201 |

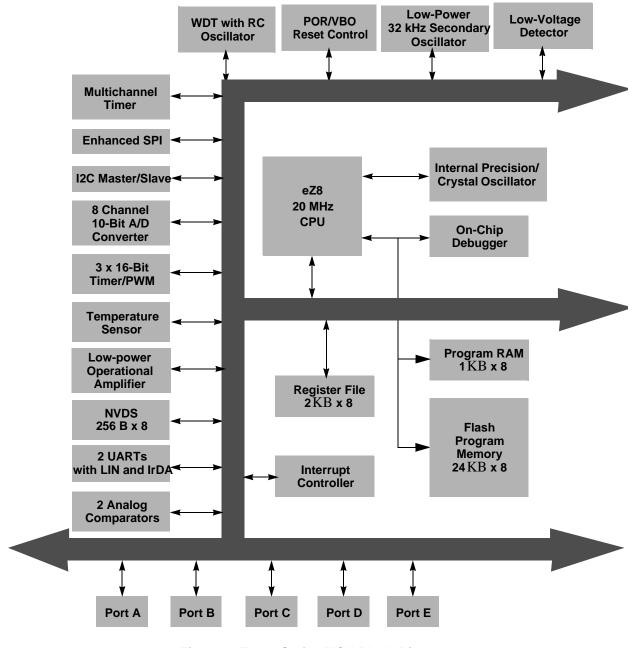

## 1.3. Block Diagram

Figure 1 displays the architecture of the F1680 Series MCU.

Figure 1. F1680 Series MCU Block Diagram

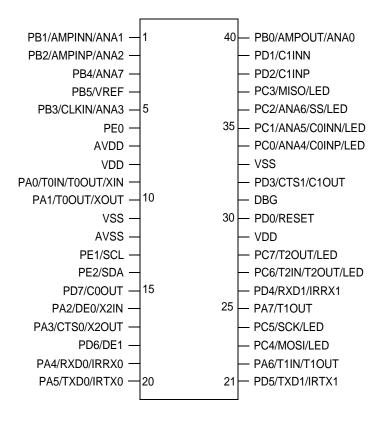

Figure 4. Z8F2480, Z8F1680 and Z8F0880 in 40-Pin Dual Inline Package (PDIP)

Table 8. Register File Address Map (Continued)

| Address (Hex)   | Register Description                  | Mnemonic | Reset (Hex) <sup>1</sup> | Page #                                  |

|-----------------|---------------------------------------|----------|--------------------------|-----------------------------------------|

| Watchdog Time   | er                                    |          |                          |                                         |

| FF2             | Watchdog Timer Reload High Byte       | WDTH     | FF                       | <u>143</u>                              |

| FF3             | Watchdog Timer Reload Low Byte        | WDTL     | FF                       | <u>143</u>                              |

| FF4–FF5         | Reserved                              | _        | XX                       |                                         |

| Trim Bit Contro | I                                     |          |                          |                                         |

| FF6             | Trim Bit Address                      | TRMADR   | 00                       | <u>281</u>                              |

| FF7             | Trim Data                             | TRMDR    | XX                       | <u>281</u>                              |

| Flash Memory (  | Controller                            |          |                          |                                         |

| FF8             | Flash Control                         | FCTL     | 00                       | <u>272</u>                              |

|                 | Flash Status                          | FSTAT    | 00                       | <u>272</u>                              |

| FF9             | Flash Page Select                     | FPS      | 00                       | <u>273</u>                              |

|                 | Flash Sector Protect                  | FPROT    | 00                       | <u>274</u>                              |

| FFA             | Flash Programming Frequency High Byte | FFREQH   | 00                       | <u>275</u>                              |

| FFB             | Flash Programming Frequency Low Byte  | FFREQL   | 00                       | <u>275</u>                              |

| eZ8 CPU         |                                       |          |                          |                                         |

| FFC             | Flags                                 | _        | XX                       | refer to                                |

| FFD             | Register Pointer                      | RP       | XX                       | the <u>eZ8</u><br>CPU                   |

| FFE             | Stack Pointer High Byte               | SPH      | XX                       | Core                                    |

| FFF             | Stack Pointer Low Byte                | SPL      | XX                       | <u>User</u><br><u>Manual</u><br>(UM0128 |

#### Notes:

<sup>1.</sup> XX=Undefined.

<sup>2.</sup> The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM.

### 7.11.14. LED Drive Level Registers

Two LED Drive Level registers consist of the LED Drive Level High Bit Register (LEDLVLH[7:0]) and the LED Drive Level Low Bit Register (LEDLVLL[7:0]), as shown in Tables 34 and 35. Two control bits, LEDLVLH[x] and LEDLVLL[x], are used to select one of four programmable current drive levels for each associated Port C[x] pin. Each Port C pin is individually programmable.

Table 34. LED Drive Level High Bit Register (LEDLVLH)

| Bits    | 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|------|------|-----|-----|-----|

| Field   |     |     |     | LEDI | _VLH |     |     |     |

| Reset   | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F8   | 3H   |     |     |     |

Table 35. LED Drive Level Low Bit Register (LEDLVLL)

| Bits    | 7   | 6    | 5   | 4   | 3    | 2   | 1   | 0   |

|---------|-----|------|-----|-----|------|-----|-----|-----|

| Field   |     |      |     | LED | LVLL |     |     |     |

| Reset   | 0   | 0    | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W | R/W  | R/W | R/W | R/W |

| Address |     | F84H |     |     |      |     |     |     |

| Bit                          | Description                                                                                                                                                                                                                                                                                        |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>LEDLVLH,<br>LEDLVLL | LED Drive Level High Bit LED Drive Level Low Bit These bits are used to set the LED drive current. {LEDLVLH[x], LEDLVLL[x]}, in which x=Port C[0] to Port C[7]. Select one of the following four programmable current drive levels for each Port C pin.  00 = 3 mA 01 = 7 mA 10 = 13 mA 11 = 20 mA |

## Chapter 9. Timers

The Z8 Encore! XP F1680 Series products contain three 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated signals. The timers' features include:

- 16-bit reload counter

- Programmable prescaler with prescale values ranging from 1 to 128

- PWM output generation

- Capture and compare capability

- Two independent capture/compare channels which reference the common timer

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the timer clock frequency

- Timer output pin

- Timer interrupt

- Noise Filter on Timer input signal

- Operation in any mode with 32kHz secondary oscillator

In addition to the timers described in this chapter, the Baud Rate Generator (BRG) of unused UART peripheral can also be used to provide basic timing functionality. For more information about using the Baud Rate Generator as additional timers, see the <u>LIN-UART</u> chapter on page 144.

- Configure the timer for DEMODULATION Mode. Setting the mode also involves writing to the TMODEHI bit in the TxCTL0 Register

- Set the prescale value

- Set the TPOL bit to set the Capture edge (rising or falling) for the Timer Input.

This setting applies only if the TPOLHI bit in the TxCTL2 Register is not set

- 2. Write to the Timer Control 2 Register to:

- Choose the timer clock source

- Set the TPOLHI bit if the Capture is required on both edges of the input signal

- 3. Write to the Timer Control 0 Register to set the timer interrupt configuration field TICONFIG.

- 4. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 6. Clear the Timer TxPWM0 and TxPWM1 High and Low Byte registers to 0000H.

- 7. If required, enable the noise filter and set the noise filter control by writing to the relevant bits in the Noise Filter Control Register.

- 8. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt will be generated for both input capture and reload events. If required, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the Timer Control 0 Register.

- 9. Configure the associated GPIO port pin for the Timer Input alternate function.

- 10. Write to the Timer Control 1 Register to enable the timer. Counting will start on the occurrence of the first external input transition.

In DEMODULATION Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

$$Capture \ Elapsed \ Time \ (s) \ = \ \frac{(Capture \ Value - Start \ Value) \times Prescale}{Timer \ Clock \ Frequency \ (Hz)}$$

| <b>Bit Position</b> | Valu                                                               | e Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [2]<br>BRGCTL       | This<br>recei<br>UAR<br>issue                                      | d Rate Generator Control bit causes different LIN-UART behavior depending on whether the LIN-UART ver is enabled (REN = 1 in the LIN-UART Control 0 Register). When the LIN- T receiver is not enabled, this bit determines whether the Baud Rate Generator es interrupts. When the LIN-UART receiver is enabled, this bit allows Reads from aud rate registers to return the BRG count value instead of the reload value. |  |  |  |  |  |

|                     | Baud                                                               | d Rate Generator Control when the LIN-UART receiver is not enabled:                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                     | 0                                                                  | BRG is disabled. Reads from the Baud Rate High and Low Byte registers return the BRG reload value.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                     | 1                                                                  | BRG is enabled and counting. The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.                                                                                                                                                                                                                      |  |  |  |  |  |

|                     | Baud Rate Generator Control when the LIN-UART receiver is enabled: |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                     | 0                                                                  | Reads from the Baud Rate High and Low Byte registers return the BRG reload value.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                     | 1                                                                  | Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the timers, there is no mechanism to latch the High Byte when the Low Byte is read.                                                                                                                                                                                                                                        |  |  |  |  |  |

| [1]                 | Rece                                                               | eive Data Interrupt                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| RDAIRQ              | 0                                                                  | Received data and receiver errors generates an interrupt request to the Interrupt controller.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                     | 1                                                                  | Received data does not generate an interrupt request to the Interrupt controller. Only receiver errors generate an interrupt request.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| [0]                 | Loop                                                               | Back Enable                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| IREN                | 0                                                                  | Infrared Encoder/Decoder is disabled. LIN-UART operates normally.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                     | 1                                                                  | Infrared Encoder/Decoder is enabled. The LIN-UART transmits and receives data through the Infrared Encoder/Decoder.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

## Chapter 14. Analog-to-Digital Converter

The Z8 Encore! includes an eight-channel Successive Approximation Register Analog-to-Digital converter (SAR ADC). The ADC converts an analog input signal to a 10-bit binary number. The features of the ADC include:

- Eight analog input sources multiplexed with general-purpose I/O ports

- Fast conversion time, less than 4.9 µs

- Programmable timing controls

- Interrupt on conversion complete

- Internal 1.6 V voltage reference generator

- Internal reference voltage available externally

- Ability to supply external reference voltage

### 14.1. Architecture

The ADC architecture, shown in Figure 30, consists of an 8-input multiplexer, sample-and-hold amplifier and 10-bit SAR ADC. The ADC digitizes the signal on a selected channel and stores the digitized data in the ADC data registers. In environments with high electrical noise, an external RC filter must be added at the input pins to reduce high-frequency noise.

## 14.2. Operation

The ADC converts the analog input,  $ANA_X$ , to a 10-bit digital representation. The equation for calculating the digital value is calculated by:

ADC Output =

$$1024 \times (ANA_x \div V_{REF})$$

Assuming zero gain and offset errors, any voltage outside the ADC input limits of  $AV_{SS}$  and  $V_{REF}$  returns all 0s or 1s, respectively.

A new conversion can be initiated by software write to the ADC Control Register's start bit. Initiating a new conversion stops any conversion currently in progress and begins a new conversion. To avoid disrupting a conversion already in progress, this start bit can be read to indicate ADC operation status (busy or available).

### 14.3.7. ADC Clock Prescale Register

The ADC Clock Prescale Register, shown in Table 107, is used to provide a divided system clock to the ADC. When this register is programmed with 0H, the System Clock is used for the ADC Clock. DIV16 maintains the highest priority, DIV2 has the lowest priority.

Table 107. ADC Clock Prescale Register (ADCCP)

| Bits    | 7       | 6    | 5     | 4  | 3     | 2    | 1    | 0    |

|---------|---------|------|-------|----|-------|------|------|------|

| Field   |         | Rese | erved |    | DIV16 | DIV8 | DIV4 | DIV2 |

| Reset   | 0 0 0 0 |      |       |    |       |      | 0    |      |

| R/W     |         | R/W  |       |    |       |      |      |      |

| Address |         |      |       | F7 | 6H    |      |      |      |

| Bit          | Description                                                                             |

|--------------|-----------------------------------------------------------------------------------------|

| [7:4]        | Reserved; must be 0.                                                                    |

| [3]<br>DIV16 | Divide by 16 0 = Clock is not divided. 1 = System Clock is divided by 16 for ADC Clock. |

| [2]<br>DIV8  | Divide by 8 0 = Clock is not divided. 1 = System Clock is divided by 8 for ADC Clock.   |

| [1]<br>DIV4  | Divide by 4 0 = Clock is not divided. 1 = System Clock is divided by 4 for ADC Clock.   |

| [0]<br>DIV2  | Divide by 2 0 = Clock is not divided. 1 = System Clock is divided by 2 for ADC Clock.   |

**Caution:** The maximum ADC clock at 2.7 V – 3.6 V is 5MHz. The maximum ADC clock at 1.8 V – 2.7 V is 2.5 MHz. Set the Prescale Register correctly according to the different system clocks. See the ADC Clock Prescale Register for details.

| Bit                          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6,0]<br>ESPIEN1,<br>ESPIEN0 | ESPI Enable and Direction Control  00 = The ESPI block is disabled. BRG can be used as a general-purpose timer by setting BRGCTL = 1.  01 = Receive Only Mode. Use this setting in SLAVE Mode if software application is receiving data but not sending. TDRE will not assert. Transmitted data will be all 1s. Not valid in MASTER Mode since Master must source data to drive the transfer.  10 = Transmit Only Mode  Use this setting in MASTER or SLAVE Mode when the software application is sending data but not receiving. RDRNE will not assert.  11 = Transmit/Receive Mode  Use this setting if the software application is both sending and receiving information. Both TDRE and RDRNE will be active.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| [5]<br>BRGCTL                | Baud Rate Generator Control  The function of this bit depends upon ESPIEN1,0. When ESPIEN1,0 = 00, this bit allows enabling the BRG to provide periodic interrupts.  If the ESPI is disabled  0 = The Baud Rate Generator timer function is disabled. Reading the Baud Rate High and Low registers returns the BRG reload value.  1 = The Baud Rate Generator timer function and time-out interrupt is enabled. Reading the Baud Rate High and Low registers returns the BRG Counter value.  If the ESPI is enabled  0 = Reading the Baud Rate High and Low registers returns the BRG reload value. If MMEN = 1, the BRG is enabled to generate SCK. If MMEN = 0, the BRG is disabled.  1 = Reading the Baud Rate High and Low registers returns the BRG Counter value. If MMEN = 1, the BRG is enabled to generate SCK. If MMEN = 0 the BRG is enabled to provide a Slave SCK time-out. See the SLAVE Mode Abort error description on page 211.  Caution: If reading the counter one byte at a time while the BRG is counting keep in mind that the values will not be in sync. Zilog recommends reading the counter using (2-byte) word reads. |

| [4]<br>PHASE                 | Phase Select Sets the phase relationship of the data to the clock. For more information about operation of the PHASE bit, see the ESPI Clock Phase and Polarity Control section on page 201.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [3]<br>CLKPOL                | Clock Polarity 0 = SCK idles Low (0). 1 = SCK idles High (1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [2]<br>WOR                   | Wire-OR (Open-Drain) Mode Enabled  0 = ESPI signal pins not configured for open-drain.  1 = All four ESPI signal pins (SCK, SS, MISO and MOSI) configured for open-drain function.  This setting is typically used for multi-Master and/or Multi-Slave configurations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [1]<br>MMEN                  | ESPI MASTER Mode Enable  This bit controls the data I/O pin selection and SCK direction.  0 = Data out on MISO, data in on MOSI (used in SPI SLAVE Mode), SCK is an input.  1 = Data out on MOSI, data in on MISO (used in SPI MASTER Mode), SCK is an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>TXI    | Enable TDRE Interrupts This bit enables interrupts when the I <sup>2</sup> C Data Register is empty.                                                                                                                                                                                                                                                                             |

| [2]<br>NAK    | Send NAK Setting this bit sends a Not Acknowledge condition after the next byte of data has been received. It is automatically deasserted after the Not Acknowledge is sent or the IEN bit is cleared. If this bit is 1, it cannot be cleared to 0 by writing to the register.                                                                                                   |

| [1]<br>FLUSH  | Flush Data Setting this bit clears the I <sup>2</sup> C Data Register and sets the TDRE bit to 1. This bit allows flushing of the I <sup>2</sup> C Data Register when an NAK condition is received after the next data byte is written to the I <sup>2</sup> C Data Register. Reading this bit always returns 0.                                                                 |

| [0]<br>FILTEN | I <sup>2</sup> C Signal Filter Enable Setting this bit enables low-pass digital filters on the SDA and SCL input signals. This function provides the spike suppression filter required in I <sup>2</sup> C Fast Mode. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs. |

## 17.3.4. I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 122 and 123, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. The I<sup>2</sup>C baud rate is calculated using the following equation.

$$I^2C$$

Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{4 \times \text{BRG}[15:0]}$

**Note:** If BRG = 0000H, use 10000H in the equation.

## Table 122. I<sup>2</sup>C Baud Rate High Byte Register (I2CBRH = 53H)

| Bits    | 7 6 |     | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |     |     |     | BF  | RH  |     |     |     |  |

| Reset   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     |     |     | F5  | 3H  |     |     |     |  |

| Bit Position | Value       | Description                                                                           |  |

|--------------|-------------|---------------------------------------------------------------------------------------|--|

| [7:0]        |             | ate High Byte                                                                         |  |

| BRH          | The most si | nificant byte, BRG[15:8], of the I <sup>2</sup> C Baud Rate Generator's reload value. |  |

# 20.2.1. Flash Operation Timing Using Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash frequency High and Low Byte registers. The Flash frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for flash program and erase operations. The 16-bit binary Flash frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$$

Caution: Flash programming and erasure are not supported for system clock frequencies below 32 kHz (32768 Hz) or above 20 MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F1680 Series devices.

## 20.2.2. Flash Code Protection Against External Access

The user code contained within Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. For more details, see the <u>Flash Option Bits</u> chapter on page 276 and the <u>On-Chip Debugger</u> chapter on page 294.

## 20.2.3. Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F1680 Series provides several levels of protection against accidental program and erasure of the contents of Flash memory. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### 20.2.3.1. Flash Code Protection Using the Flash Option Bits

The FWP Flash option bit provides Flash Program Memory protection as listed in Table 133. For more details, see the Flash Option Bits chapter on page 276.

**Table 179. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| TM       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

#### **Table 180. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

#### **Table 181. CPU Control Instructions**

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

| SCF      | _        | Set Carry Flag        |

| SRP      | src      | Set Register Pointer  |

Table 186. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                          |     | ress<br>de | Op<br>Code(s) |   |   | Fla | ags | _ Fetch | Instr. |   |   |

|---------------|--------------------------|-----|------------|---------------|---|---|-----|-----|---------|--------|---|---|

| Mnemonic      | Symbolic Operation       | dst | src        | (Hex)         | С | Z | S   | ٧   | D       | Н      |   |   |

| CLR dst       | dst ← 00H                | R   |            | В0            | _ | _ | -   | -   | -       | -      | 2 | 2 |

|               |                          | IR  |            | B1            | _ |   |     |     |         |        | 2 | 3 |

| COM dst       | dst ← ~dst               | R   |            | 60            | _ | * | *   | 0   | _       | _      | 2 | 2 |

|               |                          | IR  |            | 61            | _ |   |     |     |         |        | 2 | 3 |

| CP dst, src   | dst – src                | r   | r          | A2            | * | * | *   | *   | _       | -      | 2 | 3 |

|               |                          | r   | lr         | А3            | _ |   |     |     |         |        | 2 | 4 |

|               |                          | R   | R          | A4            | _ |   |     |     |         |        | 3 | 3 |

|               |                          | R   | IR         | A5            | _ |   |     |     |         |        | 3 | 4 |

|               |                          | R   | IM         | A6            | _ |   |     |     |         |        | 3 | 3 |

|               |                          | IR  | IM         | A7            | _ |   |     |     |         |        | 3 | 4 |

| CPC dst, src  | dst – src – C            | r   | r          | 1F A2         | * | * | *   | *   | _       | -      | 3 | 3 |

|               |                          | r   | lr         | 1F A3         | _ |   |     |     |         |        | 3 | 4 |

|               |                          | R   | R          | 1F A4         | _ |   |     |     |         |        | 4 | 3 |

|               |                          | R   | IR         | 1F A5         | _ |   |     |     |         |        | 4 | 4 |

|               |                          | R   | IM         | 1F A6         | _ |   |     |     |         |        | 4 | 3 |

|               |                          | IR  | IM         | 1F A7         | _ |   |     |     |         |        | 4 | 4 |

| CPCX dst, src | dst – src – C            | ER  | ER         | 1F A8         | * | * | *   | *   | _       | -      | 5 | 3 |

|               |                          | ER  | IM         | 1F A9         | _ |   |     |     |         |        | 5 | 3 |

| CPX dst, src  | dst – src                | ER  | ER         | A8            | * | * | *   | *   | -       | -      | 4 | 3 |

|               |                          | ER  | IM         | A9            | _ |   |     |     |         |        | 4 | 3 |

| DA dst        | dst ← DA(dst)            | R   |            | 40            | * | * | *   | Χ   | _       | -      | 2 | 2 |

|               |                          | IR  |            | 41            | _ |   |     |     |         |        | 2 | 3 |

| DEC dst       | dst ← dst – 1            | R   |            | 30            | _ | * | *   | *   | -       | -      | 2 | 2 |

|               |                          | IR  |            | 31            | _ |   |     |     |         |        | 2 | 3 |

| DECW dst      | dst ← dst – 1            | RR  |            | 80            | _ | * | *   | *   | -       | -      | 2 | 5 |

|               |                          | IRR |            | 81            | _ |   |     |     |         |        | 2 | 6 |

| DI            | $IRQCTL[7] \leftarrow 0$ |     |            | 8F            | _ | _ | _   | -   | -       | _      | 1 | 2 |

Flags notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Figures 67 and 68 provide information about each of the eZ8 CPU instructions.

|          |   |                           | Lower Nibble (Hex)         |                              |                                |                             |                               |                               |                                |                               |                                |                            |                          |                           |                           |                         |                           |

|----------|---|---------------------------|----------------------------|------------------------------|--------------------------------|-----------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|---------------------------|-------------------------|---------------------------|

|          |   | 0                         | 1                          | 2                            | 3                              | 4                           | 5                             | 6                             | 7                              | 8                             | 9                              | Α                          | В                        | С                         | D                         | Е                       | F                         |

|          | 0 | 1.1<br>BRK                | 2.2<br><b>SRP</b><br>IM    | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br><b>ADD</b><br>IR2,R1   | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br><b>INC</b><br>r1 | 1.2<br><b>NOP</b>         |

| 2        | 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br><b>ADC</b><br>r1,r2   | 2.4<br><b>ADC</b><br>r1,lr2    | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br><b>ADC</b><br>IR2,R1   | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                           |                           |                         | See 2nd<br>Op Code<br>Map |

|          | 2 | 2.2<br><b>INC</b><br>R1   | 2.3<br><b>INC</b><br>IR1   | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br><b>SUB</b><br>r1,lr2    | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br><b>SUB</b><br>IR2,R1   | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br><b>SUB</b><br>IR1,IM    | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br>SUBX<br>IM,ER1          |                            |                          |                           |                           |                         | 1, 2<br>ATM               |

|          | 3 | 2.2<br><b>DEC</b><br>R1   | 2.3<br><b>DEC</b><br>IR1   | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2    | 3.3<br><b>SBC</b><br>R2,R1  | 3.4<br><b>SBC</b><br>IR2,R1   | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br>SBCX<br>ER2,ER1        | 4.3<br>SBCX<br>IM,ER1          |                            |                          |                           |                           |                         |                           |

|          | 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1   | 3.4<br><b>OR</b><br>IR2,R1    | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                           |                           |                         |                           |

| Hex)     | 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1  | 3.4<br><b>AND</b><br>IR2,R1   | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br><b>ANDX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1.2<br><b>WDT</b>         |

|          | 6 | 2.2<br><b>COM</b><br>R1   | 2.3<br><b>COM</b><br>IR1   | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1  | 3.4<br><b>TCM</b><br>IR2,R1   | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                           |                           |                         | STOP                      |

|          | 7 | 2.2<br><b>PUSH</b><br>R2  | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1   | 3.4<br><b>TM</b><br>IR2,R1    | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br>HALT               |

| oper Nik | 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,lrr2 | 2.9<br><b>LDEI</b><br>lr1,lrr2 | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br><b>LDX</b><br>Ir1,ER2  | 3.4<br><b>LDX</b><br>IRR2,R1  | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                           |                           |                         | 1.2<br><b>DI</b>          |

| 5        | 9 | 2.2<br><b>RL</b><br>R1    | 2.3<br><b>RL</b><br>IR1    | 2.5<br><b>LDE</b><br>r2,lrr1 | 2.9<br><b>LDEI</b><br>lr2,lrr1 | 3.2<br><b>LDX</b><br>r2,ER1 | 3.3<br><b>LDX</b><br>Ir2,ER1  | 3.4<br><b>LDX</b><br>R2,IRR1  | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                           |                           |                         | 1.2<br><b>EI</b>          |

|          | Α | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1    | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.4<br>RET                |

|          | В | 2.2<br><b>CLR</b><br>R1   | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br><b>XOR</b><br>IR2,R1   | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                           |                           |                         | 1.5<br>IRET               |

|          | С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1    | 2.9<br><b>LDC</b><br>lr1,lrr2 |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                           |                           |                         | n.2<br>RCF                |

|          | D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,lrr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1         | 2.2<br><b>BSWAP</b><br>R1     | CALL<br>DA                    | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                           |                           |                         | 1.2<br><b>SCF</b>         |

|          | Е | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1   | 3.3<br><b>LD</b><br>IR2,R1    | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                           |                           |                         | 1.2<br><b>CCF</b>         |

|          | F | 2.2<br><b>SWAP</b><br>R1  | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br><b>TRAP</b><br>Vector | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1   | 3.3<br><b>LD</b><br>R2,IR1    | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | <b>V</b>                   | <b>V</b>                 | <b>V</b>                  | <b>V</b>                  | <b>V</b>                |                           |

Figure 67. First Op Code Map

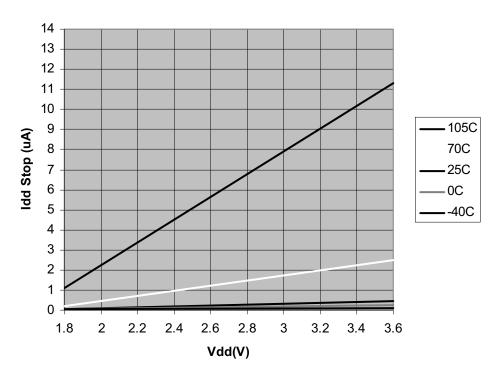

Figure 73 displays the STOP Mode supply current versus ambient temperature and  $V_{DD}$  level with all peripherals disabled.

# Idd Stop Current vs. Vdd with Temperature

Figure 73. STOP Mode Current Consumption as a Function of  $V_{\text{DD}}$  with Temperature as a Parameter; all Peripherals Disabled

## Chapter 30. Packaging

Zilog's F1680 Series of MCUs includes the Z8F0880, Z8F1680 and Z8F2480 devices, which are available in the following packages:

- 20-pin Plastic Dual-Inline Package (PDIP)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

- 40-pin Plastic Dual-Inline Package (PDIP)

- 44-pin Low-Profile Quad Flat Package (LQFP)

- 44-pin Quad Flat No Lead (QFN)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product Specification (PS0072)</u>, which is available free for download from the Zilog website.

Index

interrupts 157 WDTCTL register 40, 257, 258, 319, 320 WDTH register 143 multiprocessor mode 151 receiving data using interrupt-driven method working register 330 working register pair 330 receiving data using the polled method 148 X transmitting data using the interrupt-driven method 147 X 330 transmitting data using the polled method 146 XOR 334 x baud rate high and low registers 177 **XORX 334** x control 0 and control 1 registers 170, 171 Ζ x status 0 and status 1 registers 165, 168 User Option Bits 278 Z8 Encore! UxBRH register 177 block diagram 3 UxBRL register 178 features 1 UxCTL0 register 170, 177 part selection guide 2 UxCTL1 register 119, 172, 174, 175 Zilog Calibration Option Bits 289 UxRXD register 164 UxSTAT0 register 165, 166 UxSTAT1 register 168 UxTXD register 163 V vector 330 voltage brownout reset (VBR) 35

### W

PS025015-1212

watch-dog timer approximate time-out delay 141 approximate time-out delays 140 CNTL 35 control register 257, 258, 320 electrical characteristics and timing 361 operation 140 refresh 141 reload unlock sequence 142 reload upper, high and low registers 143 reset 36 reset in normal operation 142 reset in STOP mode 142 time-out response 141 watchdog timer electrical characteristics and timing 359 refresh 334

voltage measurement timing diagram 188