Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f1680sj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP <sup>®</sup> F1680 Series Product Specification

13

| Program Memory<br>Address (Hex)              | Function                                            |

|----------------------------------------------|-----------------------------------------------------|

| Z8F1680 Device                               |                                                     |

| 0000-0001                                    | Flash option bits                                   |

| 0002–0003                                    | Reset vector                                        |

| 0004–0005                                    | WDT interrupt vector                                |

| 0006–0007                                    | Illegal instruction trap                            |

| 0008–0037                                    | Interrupt vectors*                                  |

| 0038-003D                                    | Oscillator fail traps*                              |

| 003E-3FFF                                    | Program Flash                                       |

| E000-E3FF                                    | 1KB PRAM                                            |

| Z8F0880 Device                               |                                                     |

| 0000–0001                                    | Flash option bits                                   |

| 0002–0003                                    | Reset vector                                        |

| 0004–0005                                    | WDT interrupt vector                                |

| 0006-0007                                    | Illegal instruction trap                            |

| 0008–0037                                    | Interrupt vectors*                                  |

| 0038-003D                                    | Oscillator fail traps*                              |

| 003E-1FFF                                    | Program Flash                                       |

| E000-E3FF                                    | 1KB PRAM                                            |

| Note: *See <u>Table 36</u><br>rupt vectors a | <u>on page 69</u> for a list of inter<br>and traps. |

Table 6. F1680 Series MCU Program Memory Maps (Continued)

# 3.3. Data Memory

The F1680 Series MCU does not use Cheuez &4 KB Data Memory address space.

## 3.4. Flash Information Area

Table 7 describes the F1680 Series MCU Flash Information Area. This 512-byte Information Area is accessed thing bit 7 of the Flash Selarget Register to 1. When access is enabled, the Flash Information Area access is enabled, the Flash Information Area access is enabled, all reads from these and genory addresses retuin formation Area access is enabled, all reads from these and genory addresses retuin formation Area at a rather than the Program Memory data. Access the formation Area is read-only.

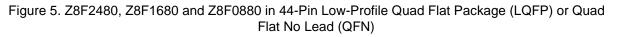

## 5.2.1. Power-On Reset

Each device in the Z8 Encore! XP F1680 Series contains an internal Power-On Reset (POR) circuit. The POR circuit monitorspithe soltage and holds the whole device in the Reset state until the supply voltage reaches a safe circuit operating level when the device is powered on.

After power on, the POR circuit keepstidle the supply voltage drops balow V voltage. Figure 7 on page 35 displays this POR timing.

After the F1680 Series MCU exits the POR state, the eZ8 CPU fetches the Reset vector Following this POR, the RVBO status bit in the Reset Status Register is set to 1.

For the POR threshold voltage, Vand POR start voltage, Vaee the Electrical Characteristics chapter on page 349

Figure 6. Power-On Reset Operation

| 4 | 1 |

|---|---|

| _ |   |

| Bit        | Description (Continued)                                                                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]<br>EXT | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESpin occurs. A POR or a Stop<br>Mode Recovery from a change in an input pirsets this bit. Reading this register resets<br>this bit.        |

| [3:1]      | Reserved; must be 0.                                                                                                                                                                                                                |

| [0]<br>LVD | Low-Voltage Detection Indicator<br>If this bit is set to 1 the current state of the supply voltage is below the low-voltage detection<br>threshold. This value is not latched but iseal-time indicator of the supply voltage level. |

| WDT<br>0<br>0 | EXT<br>0   |

|---------------|------------|

| 0             | 0          |

| 0             | 4          |

|               | 1          |

| 1             | 0          |

| ) 0           | 0          |

| ) 0           | 0          |

| 1 0           | 0          |

| 1 1           | 0          |

|               | 1 0<br>1 1 |

### Table 13. Reset Status Per Event

# 7.10. GPIO Interrupts

Many of the GPIO port pins can be **usted** raupt sources. Sporte pins can be configured to generate an interrupt request the eising edge or falling edge of the pininput signal. Other port-pin interrupt sources generate an interrupt when any edge occ (both rising and falling). From e details about interrus prosents the GPIO pins, see the Interrupt Control tetrapter on page 68.

# 7.11. GPIO Control Register Definitions

Four registers for each port provide aGEH3scootrol, input data and output data. Table 20 lists these port registers. Alse Actiontess and Control registers together to provide access to subregisters for configuration and control.

| Port Register Mnemonic    | Port Register Name                                        |

|---------------------------|-----------------------------------------------------------|

| PxADDR                    | Port A–E Address Register (Selects subregisters)          |

| P <i>x</i> CTL            | Port A-E Control Register (Povides access tosubregisters) |

| P <i>x</i> IN             | Port A–E Input Data Register                              |

| P <i>x</i> OUT            | Port A–E Output Data Register                             |

| Port Subregister Mnemonic | Port Register Name                                        |

| P <i>x</i> DD             | Data Direction                                            |

| PxAF                      | Alternate Function                                        |

| PxOC                      | Output Control (Open-Drain)                               |

| PxHDE                     | High Drive Enable                                         |

| PxSMRE                    | Stop Mode Recovery Source Enable                          |

| P <i>x</i> PUE            | Pull-up Enable                                            |

| PxAFS1                    | Alternate Function Set 1                                  |

| PxAFS2                    | Alternate Function Set 2                                  |

|                           |                                                           |

Table 20. GPIO Port Registers and Subregisters

# 9.1. Architecture

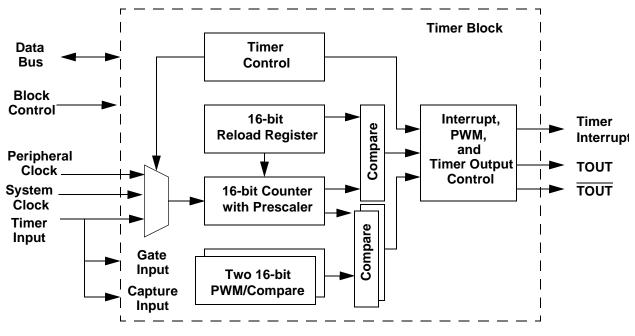

Figure 11 displays the hadrecture of the timers.

Figure 11. Timer Block Diagram

# 9.2. Operation

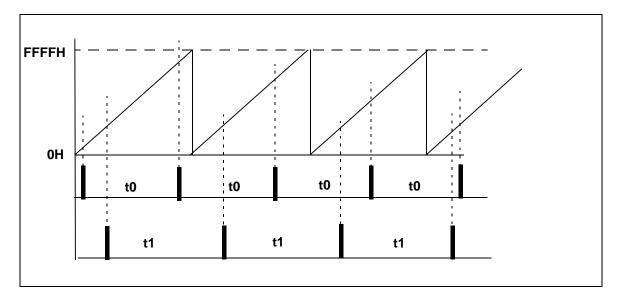

The timers are 16-bit up-counters. Minimum timelay is set by loading the value 0001H into the Timer Reload High and Low registers and setting the prescale value to 1. Maximum time-out delaget by loading the valueH into the Timer Reload High and Low Byte registed setting the prescale trailers. If the Timer reaches FFFFH, the timer rolls overotooH and continues counting.

## 9.2.1. Timer Clock Source

The timer clock source can come frontheitheripherial clock or the system clock. Peripheral clock is based on a low frequency/low power 32 kHz secondary oscillator th can be used with external watch crystal. Peripheral clock source is only available for driving Timer and Noise Filter operation of supported for other peripherals.

For timer operation in STOP Mode, peripheranhoustic be selected as the clock source. Peripheral clock can be selected as for burget ACTIVE and STOP Mode operation.

If system clock is chosen as the clockt **boutime** ceases to operate as a system clock and is put into STOP Mode. In this **case** is not reset and operation will resume after Stop Mode Recovery occurs.

### 9.2.2.3. Power Reducti on During Operation

Removal of the TEN bit will inhibit clooking entire timer block. The CPU can still read/write registers when able bit(s) are taken out.

## 9.2.3. Timer Operating Modes

The timers can be configured to opthet following modes, each of which is described in this section where indicated in Table 52.

| Mode                    | Page<br>Number |

|-------------------------|----------------|

| TRIGGERED ONE-SHOT Mode | <u>88</u>      |

| CONTINUOUS Mode         | <u>90</u>      |

| COUNTER Mode            | <u>91</u>      |

| COMPARATOR COUNTER Mode | <u>92</u>      |

| PWM SINGLE OUTPUT Mode  | <u>93</u>      |

| PWM DUAL Output Mode    | <u>95</u>      |

| CAPTURE Mode            | <u>97</u>      |

| CAPTURE RESTART Mode    | <u>98</u>      |

| COMPARE Mode            | <u>100</u>     |

| GATED Mode              | <u>100</u>     |

| CAPTURE/COMPARE Mode    | <u>102</u>     |

| DEMODULATION Mode       | <u>103</u>     |

|                         |                |

#### Table 52. Timer Operating Modes

### 9.2.3.1. ONE-SHOT Mode

In ONE-SHOT Mode, the time under up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The dounts time regarder to the 16-bit reload value. Upon reachine green value, the time ergence an interrupt, and the count value in the Timer High convol Byte registers is reseting. Then, the timer is automatically disabled and stops counting.

Additionally, if the Timer Output alternation fuis enabled, the Timer Output pin changes state for one clock cycle (from Highwor from HighLoov) upon timer reload. If it is appropriate to have the Timer Output make a permanent state change or

| Dit          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit          | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| [6] (cont'd) | <ul> <li>PWM DUAL OUTPUT Mode</li> <li>0 = Timer Output is forced Low (0) and Timer Quut Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to cont the number of cycles time delay before Timer Output and the Timer Output Complement is forced High (1).</li> <li>1 = Timer Output is forced High (1) and Tim@utput Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon Reload. When enabled to comt match and forced Low (0) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to cont the number of cycles time delay before Timer Output and the Timer Output Complement is forced to Low (0).</li> <li>CAPTURE RESTART Mode</li> <li>0 = Count is captured on the risg edge of the Timer Input signal.</li> <li>1 = Count is captured on the falgredge of the Time Input signal.</li> </ul> |

|              | COMPARATOR COUNTER Mode<br>When the timer is disabled, the fier Output signal is set to the value of this bit. When th<br>timer is enabled, the Timer Output signis complemented upon timer reload.<br>TRIGGERED ONE-SHOT Mode<br>0 = Timer counting is triggered on the rising edge of the Timer Input signal.<br>1 = Timer counting is triggered on the falling edge of the Timer Input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | <ul> <li>DEMODULATION Mode</li> <li>0 = Timer counting is triggered on the rising edge of the Timer Input signal. The current count is captured into PWM0 High and Low bytegisters on subsequent rising edges of the Timer Input signal.</li> <li>1 = Timer counting is triggered on the fallienting of the Timer Inputsignal. The current count is captured into PWMM igh and Low byte registeron subsequent falling edges of the Timer Input signal.</li> <li>The above functionality applies only if TPOLthil in Timer Control 2 Register is 0. If TPOLHI bit is 1 then timer counting is trigged on any edge of the Timer Input signal and the current count is captured on both edge he current count is captured into PWM0 registers on rising edges and PWM1 registers on falling edges of the Time Input signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Figure 18. Count Max Mode with Channel Compare

# 10.7. Multi-Channel Timer Control Register Definitions

This section defines the features bookingformulti-Channel Timer Control registers. <u>Multi-Channel Timer High and Low Byte Registerpage 130</u> <u>Multi-Channel Timer Road High and Low Byte Registerespage 130</u> <u>Multi-Channel Timer Board High and Low Byte Registerespage 131</u> <u>Multi-Channel Timer Subregister x (0, 1, or see)</u> page 132 <u>Multi-Channel Timer Control 0, Control 1 Registeresge 132</u> <u>Multi-Channel Timer Channel Status 0 and Status 1</u> steep issteres 135 <u>Multi-Channel Timer Channel-y Control Registeresge 137</u> <u>Multi-Channel Timer Channel-ghHigh Low Byte Registeres</u> page 139

## 10.7.1. Multi-Channe I Timer Address Map

Table 69 defines the byte address off**ise the function** Timer registers. For saving address space, a subaddressedsfor the Timer Control 1, Channel Status 0, Channel Status 1, Channel-y Control, and Channel-y High and Low byte registers. Only the Timer High and Lowe Bysteers and the Reload High and Low Byte registers can be directly accessed.

# 10.7.8. Multi-Channel Timer Channel-y Control Registers

Each channel has a control register tohenablemnel, selectintput/output polarity, enable channel interrupts and statechannel mode of operation.

Table 78. Multi-Channel Timer Channel Control Register (MCTCHyCTL)

| Bit                              | 7                                                                                                            | 6                                                                                                                                                       | 5                                                                                                                                      | 4                                                                                                                   | 3                                                                                                                                          | 2                                                                                          | 1                                                                                     | 0                                                                                                             |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| Field                            | CHEN                                                                                                         | CHPOL                                                                                                                                                   | CHIEN                                                                                                                                  | CHUE                                                                                                                | Reserved                                                                                                                                   | _                                                                                          | СНОР                                                                                  |                                                                                                               |  |  |

| Reset                            | 0                                                                                                            | 0                                                                                                                                                       | 0                                                                                                                                      | 0                                                                                                                   | 0                                                                                                                                          |                                                                                            |                                                                                       | 0                                                                                                             |  |  |

| R/W                              | R/W                                                                                                          | R/W                                                                                                                                                     | R/W                                                                                                                                    | R/W                                                                                                                 | R                                                                                                                                          | R/W                                                                                        | R/W                                                                                   | R/W                                                                                                           |  |  |

| Address                          | ress See note 2.                                                                                             |                                                                                                                                                         |                                                                                                                                        |                                                                                                                     |                                                                                                                                            |                                                                                            |                                                                                       |                                                                                                               |  |  |

| Notes:<br>1. y = A,<br>2. If 02H |                                                                                                              | nd 05H are ir                                                                                                                                           | the Subadd                                                                                                                             | ress Registe                                                                                                        | er, they are ac                                                                                                                            | cessible th                                                                                | rough Subre                                                                           | gister 2.                                                                                                     |  |  |

| Bit                              | Description                                                                                                  |                                                                                                                                                         |                                                                                                                                        |                                                                                                                     |                                                                                                                                            |                                                                                            |                                                                                       |                                                                                                               |  |  |

| [7]<br>CHEN                      |                                                                                                              | nable<br>el is disable<br>el is enable                                                                                                                  |                                                                                                                                        |                                                                                                                     |                                                                                                                                            |                                                                                            |                                                                                       |                                                                                                               |  |  |

|                                  | the channel<br>continue<br>When the channel<br>the channel<br>on reachin<br>PWM OUT<br>0 = Channel<br>Output | el is enabled<br>el Capture/<br>DUS COMPA<br>channel is d<br>el is enabled<br>og the Chan<br>PUT Operati<br>el Output is<br>is forced H<br>ching the Ti | d, the Chan<br>Compare Re<br>ARE Operati<br>lisabled, th<br>d, the Chan<br>nel Capture<br>on<br>forced Lov<br>igh on Cha<br>mer Reload | nel Output<br>egister valu<br>on<br>e Channel<br>nel Output<br>e/Compare<br>v when the<br>rel Capture<br>Register v | <b>Big</b> toggles<br>ue.<br>Out <b>puig</b> nal is<br>sig <b>trag</b> gles<br>Register val<br>channel is c<br>/Compare Re<br>value (modul | for one sy<br>s set to the<br>(from Low<br>ue.<br>disabled. W<br>egister val<br>o mode) oi | stem clock<br>value of th<br>to High or I<br>Vhen enable<br>ue match an<br>counting o | is bit. When<br>on reaching<br>is bit. When<br>High to Low)<br>ed, the Chann<br>nd forced Lov<br>Iown through |  |  |

# 16.2. ESPI Signals

The four ESPI signals are:

- Master-In/Slave-Out (MISO)

- Master-Out/Slave-In (MOSI)

- Serial Clock (SCK)

- Slave Select 5\$)

The following paragraphs discuss these signals as they operate in both MASTER and SLAVE modes.

# 16.2.1. Master-In/Slave-Out

The Master-In/Slave-Out (MISO) pin is ceedfaguan input in a Master device and as an output in a slave device. Data is transferrsignificant bit first. The MISO pin of a Slave device is placed in a high-impedate of the Slave is not selected. When the ESPI is not enabled, this signal is in-impiguance state. The direction of this pin is controlled by the MMEN bit of the ESPI Control Register.

# 16.2.2. Master-Out/Slave-In

The Master-Out/Slave-In (MOSI) pin is configured as an output in a Master device and an input in a slave device. Data is transferred most signification by the ESPI is not enabled, this signal is in a high-impedate of the direction of this pin is controlled by the MMEN bit of the ESPI Control Register.

# 16.2.3. Serial Clock

The Serial Clock (SCK) synchronizes data modvborten in and out of the Shift Register via the MOSI and MISO pins. In MASTAGe (MMEN = 1), the ESPI's Baud Rate Generator creates the serial clock and outlives its SCK pin to the slave devices. In SLAVE Mode, the SCK pin is an input.eStatewices ignore the SCK signal, unless their  $\overline{SS}$  pin is asserted.

The Master and Slave are each capable of exchanging a character of data during a sequence of NUMBITS clock cycles (see Tabden page 217). In both Master and Slave ESPI devices, data is shifted on once the deges CK and is spated on the opposite edge where data is stable. SCK phased as it does not be the PHASE and CLKPOL bits in the ESPI Control Register.

## 16.2.4. Slave Select

The Slave Select signal is a bidirection and signal with several modes of operation to support SPI and other synchronoust such a bip rotocols. The Slave Select mode is selected by the SSMD field of the Active Register. The direction of the select by the SSIO bit of the ESPI Mode Register signate to slave devices and is an output on the active evices flave devices ignore transactions on the bus unless their Slave Select in space tree. In SPI MASTER Mode, additional GPIO pins are required to provide Slaves Selecter is more than one slave device.

# 16.3. Operation

During a transfer, data is sent and secretilited eously by both the Master and Slave devices. Separate signals are requireds foir trate, receive data and the serial clock. When a transfer occurs, a multi-bit (toppidd) light aracter is shifted out one data pin and a multi-bit character is simultaneously shifted in on second data pin. An 8-bit shift register in the Master and an 8-bit sate firmed by slave are connected as a circular buffer. The ESPI Shift Register is buffer back-to-backaracter transfers in high-performance applications.

A transaction is initiated when the DataiRegistteen in the Master device. The value from the Data Register is draerds into the Shift Register the SPI transaction begins. At the end of each character transfreex tifttaesmit value has been written to the Data Register, the data and shift register areals wapped, which places the new transmit data into the Shift Register and the Shift Register contents (receive data) into the Data Register. At that point the Receive Distar Root Empty signal is asserted (RDRNE bit set in the Status Register). After seaf dow the receive data from the Data Register, the Transmit Data Register Empty signarities da (SEDRE bit set in the Status Register) to request the next minimizer. To support back-to-transfers without an intervening pause, the receive and transmit interrul pressent is deviced when the current character is being transferred.

The Master sources the Serial Clock (SCK) and Slave Select digmag (85e transfer.

Internal data movements (b) ware) to/from the b) is controlled by the Transmit Data Register Empty (TDRE) and Receive Data Register Not Empty (RDRNE) signals. These signals are read-only b) is sent to the interrupt controller. In many cas TDRE or RDRNE bits assert, an interrupt is sent to the interrupt controller. In many cas the software application is monly information in onections. In this case either the TDRE or RDRNE interrupts can be distand minimize software overhead. Unidirectional data transfer is supposed dirby the ESPIEN1,0 bits in the Control Register to 10 or 01.

transmitted, the hardware will automoded as skyrt the SSV and TEOF bits. The second method is for software exectly i clear the SSV bit alfeetransaction completes. If software clears the SSV bittly interies not necessary for software to also set the TEOF bit on the last transmit byte. After writing rams has tbyte, the end of the transaction can be detected by waiting for the last RDPRINE pin or monitoring the TFST bit in the ESPI Status Register.

The transmit underrun and eccevely run errors will not occur in an SPI mode Master. If the RDRNE and TDRE requests have not be exercised before the current byte transfer completes, SCLK will be paused until the exercise the second and written. The transmit underrun and receive overruns exercite occur in a Slave if the Slave s software does not keep up with the Master data rate. In this case the Shift Register in the Slave will be low with all 1s.

In the SPI mode, the SCK is active only that a htransfer with one SCK period per bit transferred. If the SPI bus has multiple stationary et belect lines to all or all but one of the Slaves must be controlled independently by software using GPIO pins. Figure 36 dis plays multiple character transfer in SPI mode.

Note: When character n is transferred via RegiShieft, software responds to the receive request for character n-1 and the transmit request for character n+1.

SS pin on the selected slave. Then, the **astered** where the clock and transmits data on the SCK and MOSI pins to the SCK and MOSI pins on the Slave (including those Slaves which are not enabled). The enabled slaved dtay out its MISO pin to the MISO Master pin.

When the ESPI is configured as a Ninhastleyfulti-Master SPI system, the Bosust be configured as an input. This signal on a device igored as a Master should remain High. If the Signal on the active Master conversion another Master is accessing this device as a Shale)llision error flag is set in the ESPI Status Register. The Slave select outputs on a Master in a Multi-Master system must come from GPIO pins.

### 16.3.4.3. SPI Slave Operation

The ESPI block is configured SLAVE Mode operation by time the MMEN bit = 0 in the ESPICTL register and setting the ission in the ESPIMODE register. The SSMD field of the ESPI Mode Register is senoted BO protocol mode. The PHASE, CLKPOL and WOR bits in the ESPICTL register than NUMBITS field in the ESPIMODE register must be set to be consistent with SPIedevices. Typically for an SPI Slave, SSPO = 0.

If the Slave has data to set the two aster, the data must be written to the Data Register before the transaction starts (first edge of SOK and sented). If the Data Register is not written prior to the Slavet to any state MISO pin outputs all 1s.

Due to the delay resulting synchronization of thereas SCK input signals to the internal system clock, the maximum SCK able that can be supported in SLAVE Mode is the system clock frequency divAde disyrate is controlled by the SPI Master. Figure 41 displays the ESPI configuration in SPI SLAVE Mode.

- 4. If this operation is a single-byte, the store asserts the NAK bit of the I Control Register so that after the first byte of data has been constructed by the I a Not Acknowledge instruction is sent costative.

- 5. The fC controller sends a start condition.

- 6. The fC controller sends the address and Read bit out via the SDA signal.

- 7. The fC slave acknowledges the address the slave SDA signable during the next High period of SCL.

If the slave does not acknowledge the address<sup>2</sup>Cbycten througher sets the NCKI bit in the<sup>2</sup>C Status Register, sets the ACK and clears the ACK bit in<sup>2</sup>Che I State Register. The software resptoted blotb Acknowledgeterimupt by setting the stop bit and clearing the TXI bit<sup>2</sup>C hoephtroller flushes the Transmit Data Register, sends a stop condition on the bus and clears the stop and NCKI bits. The transtion is complete and the virial posteps can be ignored.

- 8. The fC controller shifts in the first byte of data for shavehord the SDA signal.

- 9. The <sup>2</sup>C controller asserts the receive interrupt.

- 10. The software responds by reading Dateal Register. If the next data byte is to be the final byte, the software snetu the NAK bit of Control Register.

- 11. The fC controller sends a Not Acknowledge<sup>2</sup>Costavel if the next byte is the final byte; otherwise, it sends an Acknowledge.

- 12. If there are more bytes to transfercetmeroller returns to Step 7

- 13. A NAK interrupt (NCKI bit in I2CISTAT) is generated by the troller.

- 14. The software responds by setting the stop<sup>2</sup>CbiCoofttbeRegister.

- 15. A stop condition is sent to the ve.

17.2.5.7. Master Read Transaction with a 10-Bit Address

Figure 46 displays the read transaction format for a 10-bit addressed Slave.

| s | Slave Address<br>1st Byte | W=0 | A | Slave Address<br>2nd Byte | A | S | Slave Address<br>1st Byte | R=1 | Α | Data | A | Data | Ā | Р |  |

|---|---------------------------|-----|---|---------------------------|---|---|---------------------------|-----|---|------|---|------|---|---|--|

|---|---------------------------|-----|---|---------------------------|---|---|---------------------------|-----|---|------|---|------|---|---|--|

Figure 46. Data Transfer Format—Master Read Transaction with a 10-Bit Address

The first 7 bits transchild the first bytelane 0xx. The two x bits are the two most-significant bits of the 10-bit addresses The it of the first byte transferred is the write control bit.

Observe the following data transfer **prforedur** ead operation to a 10-bit addressed slave:

from the Shift Register at fis received from 20 dous. The 20 Shift Register is not accessible in the Register File addres suspace sed only to buffer incoming and outgoing data.

Writes by the software to the I2CDATA Rangeischercked if a slave Write transaction is underway (the Icontroller is in SLAVE Mounded data is being received).

| Bits    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | Data 7 | Data 6 | Data 5 | Data 4 | Data 3 | Data 2 | Data 1 | Data 0 |  |  |

| Reset   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | F50H   |        |        |        |        |        |        |        |  |  |

| Table 119. I <sup>2</sup> C Data Register (I2C | DATA = F50H) |

|------------------------------------------------|--------------|

|------------------------------------------------|--------------|

Bit Position Value Description

| [7:0] | — | I <sup>2</sup> C Data Byte |  |

|-------|---|----------------------------|--|

| DATA  |   |                            |  |

# 23.4.2. OCD Status Register

The OCD Status Register, shown in Table 165, reports status information about the curr state of the debugger and the system.

| Table 165. OCD Status Register (OCDSTAT | le 165. OCD Status Register | (OCDSTAT) |

|-----------------------------------------|-----------------------------|-----------|

|-----------------------------------------|-----------------------------|-----------|

| Bit         | 7                                                                                                                                                                                                                                                                                                                                      | 6    | 5    | 4 | 3        | 2 | 1 | 0 |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---|----------|---|---|---|--|--|--|--|

| Field       | IDLE                                                                                                                                                                                                                                                                                                                                   | HALT | RPEN |   | Reserved |   |   |   |  |  |  |  |

| Reset       | 0                                                                                                                                                                                                                                                                                                                                      | 0    | 0    |   | 0        |   |   |   |  |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                      | R    | R    | R |          |   |   |   |  |  |  |  |

| Bit         | t Description                                                                                                                                                                                                                                                                                                                          |      |      |   |          |   |   |   |  |  |  |  |

| [7]<br>IDLE | CPU Idle<br>This bit is set if the part <b>is</b> Debug mode (DBGMODE is 1) or if a BRK instruction has<br>occurred since the last time OCDCTL was written is can be used to determine if the CPU is<br>running or if it is idle.<br>0 = The eZ8 CPU is running.<br>1 = The eZ8 CPU is either stopped or looping on a BRK instruction. |      |      |   |          |   |   |   |  |  |  |  |

| [6]<br>HALT | HALT Mode<br>0 = The device is not in HALT Mode.<br>1 = The device is in HALT Mode.                                                                                                                                                                                                                                                    |      |      |   |          |   |   |   |  |  |  |  |

| [5]<br>RPEN | Read Protect Option Bit Enable<br>0 = The Read Protect option bit is disabled (Flash option bit is 1).<br>1 = The Read Protect option bit is enabl∉flash option bit is 0), disabling many OCD<br>commands.                                                                                                                             |      |      |   |          |   |   |   |  |  |  |  |

| [4:0]       | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                   |      |      |   |          |   |   |   |  |  |  |  |

## Z8 Encore! XP <sup>®</sup> F1680 Series Product Specification

353

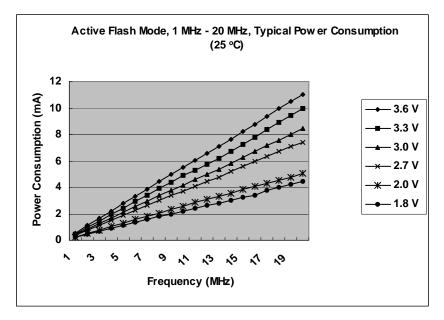

Figures 69 through 72 display the typical current consumption at voltages of 1.8 V, 2.0 2.7 V, 3.0 V, 3.3 V and 3.6 V, respectively, versus different system clock frequencies while operating at a temperature of 25" C.

Figure 69. Typical Active Flash Mode Supply Current (1–20MHz)

|                  |                                        |         | = 1.8 to 3<br>40°C to + |         | V <sub>DD</sub><br>T <sub>A</sub> = | = 2.7 to 3<br>0°C to +7 | 3.6V<br>70°C | _     |                                         |

|------------------|----------------------------------------|---------|-------------------------|---------|-------------------------------------|-------------------------|--------------|-------|-----------------------------------------|

| Symbol           | Parameter                              | Min     | Тур                     | Max     | Min                                 | Тур                     | Max          | Units | Conditions                              |

|                  | Output<br>Frequency                    | 10.6168 | 11.0592                 | 11.5016 | 10.78272                            | 11.0592                 | 11.33568     |       |                                         |

|                  | Divided-by-2<br>Output<br>Frequency    | 5.3084  | 5.5296                  | 5.7508  | 5.39136                             | 5.5296                  | 5.66784      | -     |                                         |

|                  | Divided-by-4<br>Output<br>Frequency    | 2.6542  | 2.7648                  | 2.8754  | 2.69568                             | 2.7648                  | 2.83392      |       | <del>2</del> .5% 2.7<br>to 3.6 V,       |

|                  | Divided-by-8<br>Output<br>Frequency    | 1.3271  | 1.3824                  | 1.4377  | 1.34784                             | 1.3824                  | 1.41696      | _     | 0–70°C;<br><b>≜%</b> 1.8 to             |

| F <sub>IPO</sub> | Divided-by-16<br>Output<br>Frequency   | 0.6636  | 0.6912                  | 0.7188  | 0.67392                             | 0.6912                  | 0.70848      | MHz   | 2.7 V,<br>0–70°C                        |

|                  | Divided-by-32<br>Output<br>Frequency   | 0.3318  | 0.3456                  | 0.3594  | 0.33696                             | 0.3456                  | 0.35424      | _     | <b>4</b> % 1.8 to<br>3.6 V,<br>−40−105° |

|                  | Divided-by-<br>128 Output<br>Frequency | 0.0829  | 0.0864                  | 0.0899  | 0.08424                             | 0.0864                  | 0.08856      | _     |                                         |

|                  | Divided-by-<br>256 Output<br>Frequency | 0.0415  | 0.0432                  | 0.0449  | 0.04212                             | 0.0432                  | 0.04428      | _     |                                         |

|                  | Duty Cycle of<br>Output                | 45      |                         | 55      | 45                                  |                         | 55           | %     |                                         |

Table 200. IPO Electrical Characteristics (Continued)

| Table 004 Law  | Valtere Deter | + Electrical ( | Characteriation |

|----------------|---------------|----------------|-----------------|

| Table 201. Low | voltade Detec | t Electrical ( |                 |

|                |               |                |                 |

|                                         |                       | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ |                       |       |            |  |  |

|-----------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|-----------------------|-------|------------|--|--|

|                                         | V <sub>DD</sub>       | V <sub>DD</sub> = 1.8 to 3.6 V                                                             |                       |       |            |  |  |

| Symbol Parameter                        | Min                   | Тур                                                                                        | Max                   | Units | Conditions |  |  |

| I <sub>DD</sub> LVD LVD Active Current  | _                     | _                                                                                          | 50                    | μA    |            |  |  |

| IDDQLVD LVD Quiescent Current           | -                     | 5                                                                                          | -                     | nA    |            |  |  |

| V <sub>TH</sub> Detected Source Voltage | V <sub>TP</sub> – 10% | V <sub>TP</sub> <sup>1</sup>                                                               | V <sub>TP</sub> + 10% | V     |            |  |  |

| $T_A =$ | -40°C to +1              |                                                                                                                         |             |                                                                                                                                |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| VD      | <sub>D</sub> = 1.8 to 3. |                                                                                                                         |             |                                                                                                                                |

| Min     | Тур                      | Max                                                                                                                     | Units       | Conditions                                                                                                                     |

| 2.4     | 2.5                      | 2.6                                                                                                                     | V           |                                                                                                                                |

| 50      | 1000                     | -                                                                                                                       | ns          |                                                                                                                                |

|         | $T_{A} = V_{D}$ Min 2.4  | $T_{A} = -40^{\circ} \text{C to} + 7$ $V_{DD} = 1.8 \text{ to } 3$ $Min \qquad \text{Typ}$ <b>2.4 \qquad <b>2.5</b></b> | 2.4 2.5 2.6 | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C$ $V_{DD} = 1.8 \text{ to } 3.6 \text{ V}$ $Min  Typ  Max  Units$ 2.4 2.5 2.6 V |

### Table 201. Low Voltage Detect Electrical Characteristics (Continued)

#### Table 202. Crystal Oscillator Characteristics

|                       |                                             | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ |        |                                |     |        |        |       |                |

|-----------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------|--------|--------------------------------|-----|--------|--------|-------|----------------|

|                       |                                             | $V_{DD} = 2.7 \text{ to } 3.6 \text{ V}$                                                      |        | V <sub>DD</sub> = 1.8 to 2.7 V |     | -      |        |       |                |

| Symbol                | Parameter                                   | Min                                                                                           | Тур    | Max                            | Min | Тур    | Max    | Units | Conditions     |

| I <sub>DD</sub> XTAL  | Crystal Oscillator<br>Active Supply Current | -                                                                                             | -      | 500                            | -   | -      | 300    | μA    |                |

| I <sub>DDQ</sub> XTAL | Crystal Oscillator<br>Quiescent Current     | -                                                                                             | 5      | -                              | -   | 5      | -      | nA    |                |

| S <sub>CLK</sub>      | Clk_out State in<br>Crystal Disable         | 1                                                                                             | 1      | 1                              | 1   | 1      | 1      |       |                |

| F <sub>XTAL</sub>     | External Crystal<br>Oscillator Frequency    | 1                                                                                             | -      | 20                             | 1   | -      | 20     | MHz   | See Figure 74. |

| T <sub>SET</sub>      | Startup Time After<br>Enable                | -                                                                                             | 10,000 | 30,000                         | -   | 10,000 | 30,000 | Cycle | !              |

|                       | Clk_out Duty Cycle                          | 40                                                                                            | 50     | 60                             | 40  | 50     | 60     | %     |                |

|                       | Clk_out Jitter                              | -                                                                                             | 1      | -                              | -   | 1      | -      | %     |                |