# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 37                                                           |

| Program Memory Size        | 24KB (24K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | ·                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 44-LQFP                                                      |

| Supplier Device Package    | 44-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2480an020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 118. | I2C Master/Slave Controller Registers                               |

|------------|---------------------------------------------------------------------|

| Table 119. | I2C Data Register (I2CDATA = F50H) 244                              |

| Table 120. | I2C Interrupt Status Register (I2CISTAT = F51H) 245                 |

| Table 121. | I2C Control Register (I2CCTL)                                       |

| Table 122. | I2C Baud Rate High Byte Register (I2CBRH = 53H) 248                 |

| Table 123. | I2C Baud Rate Low Byte Register (I2CBRL = F54H)                     |

| Table 124. | I2C State Register (I2CSTATE)—Description when DIAG = 1 250         |

| Table 125. | I2C State Register (I2CSTATE)—Description when $DIAG = 0 \dots 251$ |

| Table 126. | I2CSTATE_L                                                          |

| Table 127. | I2CSTATE_H                                                          |

| Table 128. | I2C Mode Register (I2C Mode = F56H) 253                             |

| Table 129. | I2C Slave Address Register (I2CSLVAD = 57H) 255                     |

| Table 130. | Comparator 0 Control Register (CMP0) 257                            |

| Table 131. | Comparator 1 Control Register (CMP1) 258                            |

| Table 132. | Z8 Encore! XP F1680 Series Flash Memory Configurations 262          |

| Table 133. | Flash Code Protection Using the Flash Option Bit                    |

| Table 134. | Flash Control Register (FCTL)                                       |

| Table 135. | Flash Status Register (FSTAT)                                       |

| Table 136. | Flash Page Select Register (FPS) 273                                |

| Table 137. | Flash Sector Protect Register (FPROT)                               |

| Table 138. | Flash Frequency High Byte Register (FFREQH)                         |

| Table 139. | Flash Frequency Low Byte Register (FFREQL) 275                      |

| Table 140. | Flash Option Bits at Program Memory Address 0000H 278               |

| Table 141. | Flash Option Bits at Program Memory Address 0001H 280               |

| Table 142. | Trim Bit Data Register (TRMDR) 281                                  |

| Table 143. | Trim Bit Address Register (TRMADR)                                  |

| Table 144. | Trim Bit Address Map                                                |

|            | Trim Bit Address Description                                        |

| Table 146. | Trim Option Bits at Address 0000H (TTEMP0) 282                      |

| Table 147. | Trim Option Bits at 0001H (TTEMP1) 283                              |

#### xxii

need to use this on-chip Program RAM to shadow Interrupt Service Routines (ISR). For details, see the <u>PRAM\_M</u> section on page 278.

# 3.2. Program Memory

The eZ8 CPU supports 64KB of Program Memory address space. The F1680 Series MCU contains 8KB to 24KB of on-chip Flash memory in the Program Memory address space, depending on the device.

In addition, the F1680 Series MCU contains up to 1 KB of on-chip Program RAM. The Program RAM is mapped in the Program Memory address space beyond the on-chip Flash memory. The Program RAM is entirely under user control and is meant to store interrupt service routines of high-frequency interrupts. Since interrupts bring the CPU out of low-power mode, it is important to ensure that interrupts that occur very often use as low a current as possible. For battery operated systems, Program RAM based handling of high-frequency interrupts provides power savings by keeping the Flash block disabled. Program RAM (PRAM) is optimized for low-current operation and can be easily boot-strapped with interrupt code at power up.

Reading from Program Memory addresses present outside the available Flash memory and PRAM addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the F1680 Series MCU.

| Program Memory<br>Address (Hex) | Function                        |  |  |  |  |

|---------------------------------|---------------------------------|--|--|--|--|

| Z8F2480 Device                  |                                 |  |  |  |  |

| 0000–0001                       | Flash option bits               |  |  |  |  |

| 0002–0003                       | Reset vector                    |  |  |  |  |

| 0004–0005                       | WDT interrupt vector            |  |  |  |  |

| 0006–0007                       | Illegal instruction trap        |  |  |  |  |

| 0008–0037                       | Interrupt vectors*              |  |  |  |  |

| 0038–003D                       | Oscillator fail traps*          |  |  |  |  |

| 003E-5FFF                       | Program Flash                   |  |  |  |  |

| E000–E3FF                       | 1KB PRAM                        |  |  |  |  |

|                                 | on page 69 for a list of inter- |  |  |  |  |

| rupt vectors and                | traps.                          |  |  |  |  |

#### Table 6. F1680 Series MCU Program Memory Maps

| Port   | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | AFS1[0]: 0                              |

|        |     | Reserved   |                                         | AFS1[0]: 1                              |

|        | PA1 | T0OUT      | Timer 0 Output                          | AFS1[1]: 0                              |

|        |     | Reserved   |                                         | AFS1[1]: 1                              |

|        | PA2 | DE0        | UART 0 Driver Enable                    | AFS1[2]: 0                              |

|        |     | Reserved   |                                         | AFS1[2]: 1                              |

| PA3    |     | CTS0       | UART 0 Clear to Send                    | AFS1[3]: 0                              |

|        |     | Reserved   |                                         | AFS1[3]: 1                              |

|        | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | AFS1[4]: 0                              |

|        |     | Reserved   |                                         | AFS1[4]: 1                              |

|        | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | AFS1[5]: 0                              |

|        |     | Reserved   |                                         | AFS1[5]: 1                              |

|        | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | AFS1[6]: 0                              |

|        |     | SCL        | I <sup>2</sup> C Serial Clock           | AFS1[6]: 1                              |

|        | PA7 | T1OUT      | Timer 1 Output                          | AFS1[7]: 0                              |

|        |     | SDA        | I <sup>2</sup> C Serial Data            | AFS1[7]: 1                              |

#### Table 18. Port Alternate Function Mapping, 28-Pin Parts<sup>1,2</sup>

Notes:

Because there are at most two choices of alternate functions for some pins in Ports A and B, the Alternate Function Set Register (AFS2) is implemented but not used to select the function. The alternate function selection must also be enabled, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

2. Because there is only one alternate function for each Port D and Port E pin, the Alternate Function Set registers are not implemented for Ports D and E. Enabling the alternate function selections automatically enables the associated alternate function, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

### 8.4.7. Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 49, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| Bits    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| Reset   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | FCDH |      |      |      |      |      |      |      |

#### Table 49. Interrupt Edge Select Register (IRQES)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:0]        | Interrupt Edge Select x                                                                     |

| IES <i>x</i> | 0 = An interrupt request is generated on the falling edge of the PAx input or PDx input.    |

|              | 1 = An interrupt request is generated on the rising edge of the PAx input or PDx input; $x$ |

|              | indicates the specific GPIO port pin number (0–7).                                          |

### 8.4.8. Shared Interrupt Select Register

The Shared Interrupt Select (IRQSS) Register, shown in Table 50, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

| Bits    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0        |

|---------|-------|-------|-------|-------|-------|-------|-------|----------|

| Field   | PA7VS | PA6CS | PA5CS | PAD4S | PAD3S | PAD2S | PAD1S | Reserved |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0        |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W      |

| Address | FCEH  |       |       |       |       |       |       |          |

Table 50. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VS | <ul> <li>PA7/LVD Selection</li> <li>0 = PA7 is used for the interrupt for PA7VS interrupt request.</li> <li>1 = The LVD is used for the interrupt for PA7VS interrupt request.</li> </ul>                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator 0 Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator 0 is used for the interrupt for PA6CS interrupt request.</li> </ul> |

# 9.1. Architecture

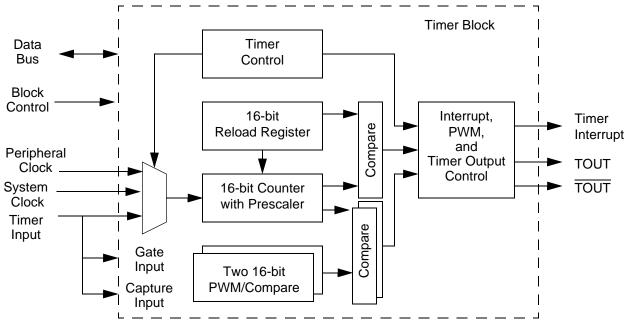

Figure 11 displays the architecture of the timers.

Figure 11. Timer Block Diagram

# 9.2. Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

### 9.2.1. Timer Clock Source

The timer clock source can come from either the peripheral clock or the system clock. Peripheral clock is based on a low frequency/low power 32kHz secondary oscillator that can be used with external watch crystal. Peripheral clock source is only available for driving Timer and Noise Filter operation. It is not supported for other peripherals.

For timer operation in STOP Mode, peripheral clock must be selected as the clock source. Peripheral clock can be selected as source for both ACTIVE and STOP Mode operation.

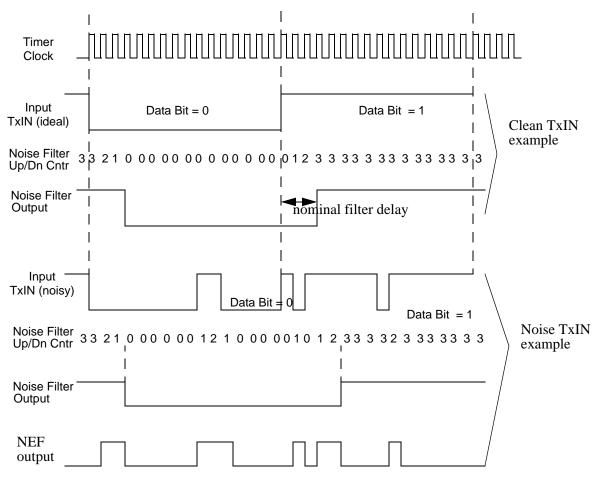

Figure 13. Noise Filter Operation

### 9.3. Timer Control Register Definitions

This section defines the features of the following Timer Control registers. <u>Timer 0–2 High and Low Byte Registers</u>: see page 109 <u>Timer Reload High and Low Byte Registers</u>: see page 109 <u>Timer 0–2 PWM0 High and Low Byte Registers</u>: see page 110 <u>Timer 0–2 PWM1 High and Low Byte Registers</u>: see page 111 <u>Timer 0–2 Control Registers</u>: see page 112 <u>Timer 0–2 Status Registers</u>: see page 118 <u>Timer 0–2 Noise Filter Control Register</u>: see page 119

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>CHIEN  | <ul> <li>Channel Interrupt Enable</li> <li>This bit enables generation of channel interrupt. A channel interrupt is generated whenever there is a capture/compare event on the Timer Channel.</li> <li>0 = Channel interrupt is disabled.</li> <li>1 = Channel interrupt is enabled.</li> </ul>                                                                                                                                                                                                      |

| [4]<br>CHUE   | <ul> <li>Channel Update Enable</li> <li>This bit determines whether writes to the Channel High and Low Byte registers are buffered when TEN = 1. Writes to these registers are not buffered when TEN = 0 regardless of the value of this bit.</li> <li>0 = Writes to the Channel High and Low Byte registers are buffered when TEN = 1 and only take affect on the next end of cycle count.</li> <li>1 = Writes to the Channel High and Low Byte registers are not buffered when TEN = 1.</li> </ul> |

| [3]           | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2:0]<br>CHOP | Channel Operation Method<br>This field determines the operating mode of the channel. For a detailed description of the<br>operating modes, see <u>Count Up/Down Mode</u> on page 123.<br>000 = One-Shot Compare operation.<br>001 = Continuous Compare operation.<br>010 = PWM Output operation.<br>011 = Capture operation.<br>100 - 111 = Reserved.                                                                                                                                                |

# **12.3. LIN-UART Control Register Definitions**

The LIN-UART control registers support the LIN-UART, the associated Infrared Encoder/ Decoder and the noise filter. For more information about the infrared operation, see the <u>Infrared Encoder/Decoder</u> section on page 182.

### 12.3.1. LIN-UART Transmit Data Register

Data bytes written to the LIN-UART Transmit Data Register, shown in Table 83, are shifted out on the TxD pin. The write-only LIN-UART Transmit Data Register shares a Register File address with the read-only LIN-UART Receive Data Register.

| Bit       | 7             | 6        | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------|---------------|----------|---|----|----|---|---|---|

| Field     |               |          | 1 | T> | ٢D |   |   | 1 |

| Reset     | Х             | Х        | Х | Х  | Х  | Х | Х | Х |

| R/W       | W             | W        | W | W  | W  | W | W | W |

| Address   | F40H, F48H    |          |   |    |    |   |   |   |

| Note: W = | Write; X = un | defined. |   |    |    |   |   |   |

| Bit       | Descriptio    | n        |   |    |    |   |   |   |

| DIL   | Description                                                           |

|-------|-----------------------------------------------------------------------|

| [7:0] | Transmit Data                                                         |

| TxD   | LIN–UART transmitter data byte to be shifted out through the TxD pin. |

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>OE   | <ul> <li>Receive Data and Autobaud Overrun Error</li> <li>This bit is set just as in normal UART operation if a receive data overrun error occurs. This bit is also set during LIN Slave autobaud if the BRG counter overflows before the end of the autobaud sequence. This indicates that the receive activity is not an autobaud character or the master baud rate is too slow. The ATB status bit will also be set in this case. This bit is cleared by reading the Receive Data Register.</li> <li>0 = No autobaud or data overrun error occurred.</li> <li>1 = An autobaud or data overrun error occurred.</li> </ul> |

| [4]<br>FE   | <ul> <li>Framing Error</li> <li>This bit indicates that a framing error (no stop bit following data reception) is detected. Reading the Receive Data Register clears this bit.</li> <li>0 = No framing error occurred.</li> <li>1 = A framing error occurred.</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |

| [3]<br>BRKD | <ul> <li>Break Detect</li> <li>This bit is set in LIN mode if:</li> <li>It is in Lin Sleep state and a break of at least 4 bit times occurred (Wake-up event) or</li> <li>It is in Slave Wait Break state and a break of at least 11 bit times occurred (Break event) or</li> <li>It is in Slave Active state and a break of at least 10 bit times occurs. Reading the Status 0 Register or the Receive Data Register clears this bit.</li> </ul>                                                                                                                                                                           |

|             | 0 = No LIN break occurred.<br>1 = LIN break occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the Transmit Data Register resets this bit.</li> <li>0 = Do not write to the Transmit Data Register.</li> <li>1 = The Transmit Data Register is ready to receive an additional byte for transmission.</li> </ul>                                                                                                                                                                                                                                           |

| [1]<br>TXE  | <ul> <li>Transmitter Empty</li> <li>This bit indicates that the Transmit Shift Register is empty and character transmission is completed.</li> <li>0 = Data is currently transmitting.</li> <li>1 = Transmission is complete.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    |

| [0]<br>ATB  | LIN Slave Autobaud Complete<br>This bit is set in LIN SLAVE Mode when an autobaud character is received. If the ABIEN bit is<br>set in the LIN Control Register, then a receive interrupt is generated when this bit is set.<br>Reading the Status 0 Register clears this bit. This bit will be 0 in LIN MASTER Mode.                                                                                                                                                                                                                                                                                                       |

### 14.3.2. ADC Raw Data High Byte Register

The ADC Raw Data High Byte Register, shown in Table 102, contains the upper 8 bits of raw data from the ADC output. Access to the ADC Raw Data High Byte register is read-only. This register is used for test only.

#### Table 102. ADC Raw Data High Byte Register (ADCRD\_H)

| Bits    | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|---------|---|---|---|-----|-----|---|---|---|

| Field   |   |   |   | ADC | RDH |   |   |   |

| Reset   |   |   |   | )   | <   |   |   |   |

| R/W     |   |   |   | F   | २   |   |   |   |

| Address |   |   |   | F7  | 1H  |   |   |   |

| Bit Position | Value<br>(H) | Description                                                                                                                                                                                |

|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]        | 00–FF        | ADC Raw Data High Byte<br>The data in this register is the raw data coming from the SAR Block. It will<br>change as the conversion is in progress. This register is used for testing only. |

### 14.3.3. ADC Data High Byte Register

The ADC Data High Byte Register, shown in Table 103, contains the upper eight bits of the ADC output. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Table 103 | . ADC Data | <b>High Byte</b> | Register | (ADCD_H) |

|-----------|------------|------------------|----------|----------|

|-----------|------------|------------------|----------|----------|

| Bits    | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|---------|---|---|---|-----|-----|---|---|---|

| Field   |   |   |   | ADC | CDH |   |   |   |

| Reset   |   |   |   | )   | <   |   |   |   |

| R/W     |   |   |   | F   | २   |   |   |   |

| Address |   |   |   | F7  | 2H  |   |   |   |

| Bit Position | Value<br>(H) | Description                                                                                                                   |

|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| [7:0]        | 00–FF        | <b>ADC High Byte</b><br>The last conversion output is held in the data registers until the next ADC conversion has completed. |

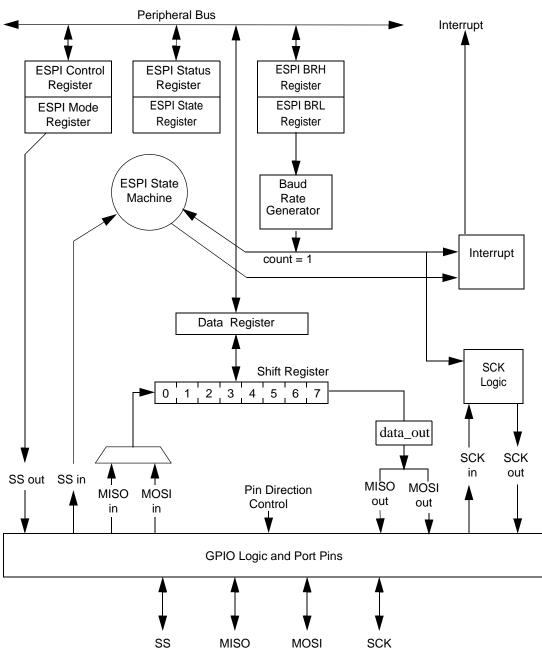

Figure 33. ESPI Block Diagram

### 17.2.3. Start and Stop Conditions

The Master generates the start and stop conditions to start or end a transaction. To start a transaction, the I<sup>2</sup>C controller generates a start condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the I<sup>2</sup>C controller generates a stop condition by creating a Low-to-High transition of the SDA signal while the SCL signal is High. These start and stop events occur when the start and stop bits in the I<sup>2</sup>C Control Register are written by software to begin or end a transaction. Any byte transfer currently under way including the Acknowledge phase finishes before the start or stop condition occurs.

### 17.2.4. Software Control of I<sup>2</sup>C Transactions

The I<sup>2</sup>C controller is configured via the I<sup>2</sup>C Control and I<sup>2</sup>C Mode registers. The MODE[1:0] field of the I<sup>2</sup>C Mode Register allows the configuration of the I<sup>2</sup>C controller for MASTER/SLAVE or SLAVE ONLY mode and configures the slave for 7-bit or 10-bit addressing recognition.

MASTER/SLAVE Mode can be used for:

- MASTER ONLY operation in a Single Master/One or More Slave I<sup>2</sup>C system

- MASTER/SLAVE in a Multimaster/multislave I<sup>2</sup>C system

- SLAVE ONLY operation in an I<sup>2</sup>C system

In SLAVE ONLY mode, the start bit of the I<sup>2</sup>C Control Register is ignored (software cannot initiate a master transaction by accident) and operation to SLAVE ONLY Mode is restricted thereby preventing accidental operation in MASTER Mode. The software controls I<sup>2</sup>C transactions by enabling the I<sup>2</sup>C controller interrupt in the interrupt controller or by polling the I<sup>2</sup>C Status Register.

To use interrupts, the  $I^2C$  interrupt must be enabled in the interrupt controller and followed by executing an EI instruction. The TXI bit in the  $I^2C$  Control Register must be set to enable transmit interrupts. An  $I^2C$  interrupt service routine then checks the  $I^2C$  Status Register to determine the cause of the interrupt.

To control transactions by polling, the TDRE, RDRF, SAM, ARBLST, SPRS and NCKI interrupt bits in the I<sup>2</sup>C Status Register should be polled. The TDRE bit asserts regardless of the state of the TXI bit.

### 17.2.5. Master Transactions

The following sections describe Master Read and Write transactions to both 7-bit and 10bit slaves.

- 14. The software responds by writing the data to be written out to the I<sup>2</sup>C Control Register.

- 15. The I<sup>2</sup>C controller shifts out the remainder of the second byte of the slave address (or ensuring data bytes, if looping) via the SDA signal.

- 16. The I<sup>2</sup>C slave sends an Acknowledge by pulling the SDA signal Low during the next High period of SCL. The I<sup>2</sup>C controller sets the ACK bit in the I<sup>2</sup>C Status Register. If the slave does not acknowledge, see the second paragraph of <u>Step 11</u>.

- 17. The I<sup>2</sup>C controller shifts the data out by the SDA signal. After the first bit is sent, the transmit interrupt asserts.

- 18. If more bytes remain to be sent, return to <u>Step 14</u>.

- 19. The software responds by asserting the stop bit of the  $I^2C$  Control Register.

- 20. The  $I^2C$  controller completes transmission of the data on the SDA signal.

- 21. The  $I^2C$  controller sends a stop condition to the  $I^2C$  bus.

**Note:** If the slave responds with a Not Acknowledge during the transfer, the  $I^2C$  controller asserts the NCKI bit, sets the ACKV bit, clears the ACK bit in the  $I^2C$  State Register and halts. The software terminates the transaction by setting either the stop bit (end transaction) or the start bit (end this transaction, start a new one). The Transmit Data Register is flushed automatically.

#### 17.2.5.6. Master Read Transaction with a 7-Bit Address

Figure 45 displays the data transfer format for a Read operation to a 7-bit addressed slave.

| S | Slave Address | R = 1 | А | Data | А | Data | А | P/S |

|---|---------------|-------|---|------|---|------|---|-----|

|---|---------------|-------|---|------|---|------|---|-----|

#### Figure 45. Data Transfer Format—Master Read Transaction with a 7-Bit Address

Observe the following steps for a Master Read operation to a 7-bit addressed slave:

- The software initializes the MODE field in the I<sup>2</sup>C Mode Register for MASTER/ SLAVE Mode with 7- or 10-bit addressing (the I<sup>2</sup>C bus protocol allows the mixing of slave address types). The MODE field selects the address width for this mode when addressed as a slave (but not for the remote slave). The software asserts the IEN bit in the I<sup>2</sup>C Control Register.

- 2. The software writes the I<sup>2</sup>C Data Register with a 7-bit slave address, plus the Read bit (which is set to 1).

- 3. The software asserts the start bit of the  $I^2C$  Control Register.

### 17.3.2. I<sup>2</sup>C Interrupt Status Register

The read-only  $I^2C$  Interrupt Status Register, shown in Table 120, indicates the cause of any current  $I^2C$  interrupt and provides status of the  $I^2C$  controller. When an interrupt occurs, one or more of the TDRE, RDRF, SAM, ARBLST, SPRS or NCKI bits is set. The GCA and RD bits do not generate an interrupt but rather provide status associated with the SAM bit interrupt.

| Bits        | 7                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                | 3                                                     | 2                                             | 1                                        | 0                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|------------------------------------------|-----------------------------------|

| Field       | TDRE                                                                                                                                                                                                                                                                                                                                                                                                      | RDRF                                         | SAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GCA                                                                              | RD                                                    | ARBLST                                        | SPRS                                     | NCKI                              |

| Reset       | 1                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                | 0                                                     | 0                                             | 0                                        | 0                                 |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                         | R                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R                                                                                | R                                                     | R                                             | R                                        | R                                 |

| Address     | F51H                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |                                                       |                                               |                                          |                                   |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                | n                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |                                                       |                                               |                                          |                                   |

| [7]<br>TDRE | <b>Transmit Data Register Empty</b><br>When the $I^2C$ controller is enabled, this bit is 1 when the $I^2C$ Data Register is empty. When set, this bit causes the $I^2C$ controller to generate an interrupt, except when the $I^2C$ controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit clears by writing to the I2CDATA Register. |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |                                                       |                                               | roller is                                |                                   |

| [6]<br>RDRF | <b>Receive Data Register Full</b><br>This bit is set = 1 when the $I^2C$ controller is enabled and the $I^2C$ controller has received a byte of data. When asserted, this bit causes the $I^2C$ controller to generate an interrupt. This bit clears by reading the I2CDATA Register.                                                                                                                     |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |                                                       |                                               |                                          |                                   |

| [5]<br>SAM  | This bit is s<br>that matche<br>the I <sup>2</sup> C Mod<br>on both add                                                                                                                                                                                                                                                                                                                                   | es the uniqued                               | e slave addr<br>. In 10-bit ac<br>When this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | er is enablec<br>ess or Gene<br>ddressing mo<br>bit is set, the                  | eral Call Add<br>ode, this bit                        | lress (if enal<br>is not set ur               | bled by the (<br>htil a match i          | GCE bit in<br>s achieved          |

| [4]<br>GCA  | This bit is s<br>either 7 or 7<br>recognition<br>updated fol<br>Address is                                                                                                                                                                                                                                                                                                                                | 10 bit SLAVI<br>of the Gene<br>lowing the fi | E Mode). Th<br>eral Call Add<br>rst address<br>d from a Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | n the Genera<br>le GCE bit ir<br>Iress and Sta<br>byte of each<br>art byte by th | the I <sup>2</sup> C Mo<br>art byte. This<br>SLAVE Mo | de Register<br>s bit clears v<br>de transacti | must be set<br>when IEN =<br>on. A Gener | to enable<br>0 and is<br>ral Call |

| [3]<br>RD   | from the Sla<br>condition of                                                                                                                                                                                                                                                                                                                                                                              | ave. This bit<br>ccurs (for bo               | matches the the the the the the the test of test o | ansfer of the<br>e least-signi<br>t and SLAVE<br>byte of each                    | ficant bit of t<br>E modes). T                        | the address<br>his bit clears                 | byte after th                            | ne start                          |

Table 120. I<sup>2</sup>C Interrupt Status Register (I2CISTAT = F51H)

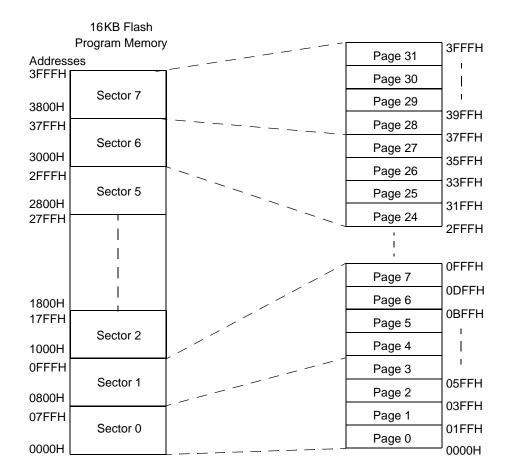

Figure 52. 16KB Flash Memory Arrangement

**Read Baud Reload Register (1BH).** The Read Baud Reload Register command returns the current value in the Baud Reload Register.

DBG  $\leftarrow$  1BH DBG  $\rightarrow$  BAUD[15:8] DBG  $\rightarrow$  BAUD[7:0]

Write Test Mode Register (F0H). The Write Test Mode Register command writes the data that follows to the Test Mode register.

DBG  $\leftarrow$  F0H DBG  $\leftarrow$  TESTMODE[7:0]

**Read Test Mode Register (F1H).** The Read Test Mode Register command returns the current value in the Test Mode register.

DBG  $\leftarrow$  F1H DBG  $\rightarrow$  TESTMODE[7:0]

**Write Option Bit Registers (F2H).** The Write Option Bit Registers command is used to write to the option bit configuration registers. The option bit configuration registers store the device configuration and are loaded from Flash every time the Z8 Encore! XP F1680 Series is reset. The registers may be temporarily written using this OCD command to test peripherals without having to program the Flash Information Area and resetting the Z8 Encore! XP F1680 Series. The ZilogUserSel bit selects between Zilog option bits (1) and user option bits (0).

```

DBG \leftarrow F2H

DBG \leftarrow {ZilogUserSel,1'b0,OptAddr[4:0]}

DBG \leftarrow OptData[7:0]

```

**Read Option Bit Registers (F3H).** The Read Option Bit Registers command is used to read the option bit registers that store the device configuration that is read out of flash when the Z8 Encore! XP F1680 Series is reset. The ZilogUserSel bit selects between reading Zilog option bits (1) or user option bits (0).

```

DBG \leftarrow F1H

DBG \leftarrow {ZilogUserSel,1'b0,OptAddr[4:0]}

DBG \rightarrow OptData[7:0]

```

# 23.4. On-Chip Debugger Control Register Definitions

This section defines the features of the following On-Chip Debugger Control registers.

OCD Control Register: see page 310

OCD Status Register: see page 312

Line Control Register: see page 313

Baud Reload Register: see page 314

Tables 178 through 185 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instructions are to be considered as a subset of more than one category. Within these tables, the source operand is identified as src, the destination operand is dst and a condition code is cc.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

|          |          |                                               |

#### Table 178. Arithmetic Instructions

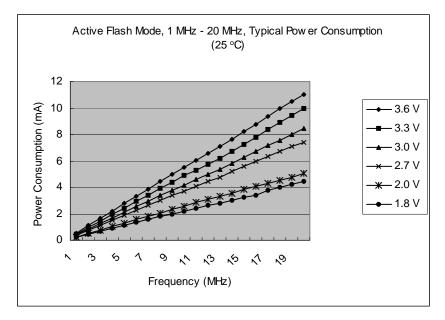

Figures 69 through 72 display the typical current consumption at voltages of 1.8 V, 2.0 V, 2.7 V, 3.0 V, 3.3 V and 3.6 V, respectively, versus different system clock frequencies while operating at a temperature of  $25^{\circ}$ C.

Figure 69. Typical Active Flash Mode Supply Current (1–20MHz)

control register, I2C 247 Control Registers 19 CP 332 CPC 332 CPCX 332 CPU and peripheral overview 4 CPU control instructions 333 CPX 332 current measurement architecture 186 operation 186 Customer Feedback Form 387

### D

DA 330, 332 data memory 21 data register, I2C 243 DC characteristics 350 debugger, on-chip 294 **DEC 332** decimal adjust 332 decrement 332 decrement and jump non-zero 335 decrement word 332 **DECW 332** destination operand 331 device, port availability 46 DI 333 direct address 330 disable interrupts 333 **DJNZ 335** dst 331

### Ε

EI 333 electrical characteristics 349 ADC 360 flash memory and timing 359 GPIO input data sample timing 366 watch-dog timer 359, 361 electrical noise 186 enable interrupt 333 ER 330 extended addressing register 330 external pin reset 37 eZ8 CPU features 4 eZ8 CPU instruction classes 331 eZ8 CPU instruction notation 330 eZ8 CPU instruction set 328 eZ8 CPU instruction summary 336

### F

FCTL register 272, 281 features, Z8 Encore! 1 first opcode map 347 FLAGS 331 flags register 331 flash controller 4 option bit configuration - reset 276 flash memory 262 arrangement 263, 264, 265 byte programming 269 code protection 267 configurations 262 control register definitions 271, 278 controller bypass 270 electrical characteristics and timing 359 flash control register 272, 281 flash option bits 268 flash status register 272 flow chart 266 frequency high and low byte registers 274 mass erase 270 operation 265 operation timing 267 page erase 270 page select register 273, 274 FPS register 273, 274 FSTAT register 272

### G

gated mode 114 general-purpose I/O 46 GPIO 4, 46 alternate functions 47 architecture 47 control register definitions 58

### Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification