# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 24KB (24K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2480hh020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Revision   | History                                                                                              |

|------------|------------------------------------------------------------------------------------------------------|

| List of Fi | gures xv                                                                                             |

|            | ables                                                                                                |

|            | 1. Overview                                                                                          |

| 1.1.       | Features                                                                                             |

| 1.1.       | Part Selection Guide                                                                                 |

| 1.21       |                                                                                                      |

| 1.3.       | Block Diagram                                                                                        |

| 1.4.       | An Overview of the eZ8 CPU and its Peripherals                                                       |

|            | 1.4.1. General-Purpose Input/Output                                                                  |

|            | 1.4.2. Flash Controller                                                                              |

|            | 1.4.3. Non-Volatile Data Storage                                                                     |

|            | 1.4.4. Internal Precision Oscillator                                                                 |

|            | 1.4.5. Crystal Oscillator                                                                            |

|            | 1.4.6. Secondary Oscillator                                                                          |

|            | 1.4.7. 10-Bit Analog-to-Digital Converter                                                            |

|            | 1.4.8. Low-Power Operational Amplifier                                                               |

|            | 1.4.9.       Analog Comparator       5         1.4.10.       Temperature Sensor       6              |

|            | 1.4.10. Temperature Sensor61.4.11. Low-Voltage Detector6                                             |

|            | 1.4.11. Low-voltage Detector       6         1.4.12. Enhanced SPI       6                            |

|            | 1.4.12. Enhanced SP1       6         1.4.13. UART with LIN       6                                   |

|            | 1.4.13. UART with Lin                                                                                |

|            | 1.4.15. Timers                                                                                       |

|            | 1.4.15. Timers       0         1.4.16. Multi-Channel Timer       7                                   |

|            | 1.4.10.         Wutu-Chamer Timer         7           1.4.17.         Interrupt Controller         7 |

|            | 1.4.18. Reset Controller         7                                                                   |

|            | 1.4.19. On-Chip Debugger         7                                                                   |

|            | 1.4.20. Direct LED Drive                                                                             |

| 1.5.       | Acronyms and Expansions                                                                              |

|            | 2. Pin Description                                                                                   |

| 2.1.       | Available Packages       10                                                                          |

|            | 6                                                                                                    |

| 2.2.       | Pin Configurations 10                                                                                |

| 2.3.       | Signal Descriptions                                                                                  |

| 2.4.       | Pin Characteristics                                                                                  |

## Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

| Table 208. | UART Timing Without CTS                                         | 370 |

|------------|-----------------------------------------------------------------|-----|

| Table 209. | Ordering Information for the Z8 Encore! XP F1680 Series of MCUs | 372 |

| Table 210. | Package and Pin Count Description                               | 376 |

used as Baud Rate Generator (BRG) when UART is enabled and configured as basic 16bit timers when UART is disabled.

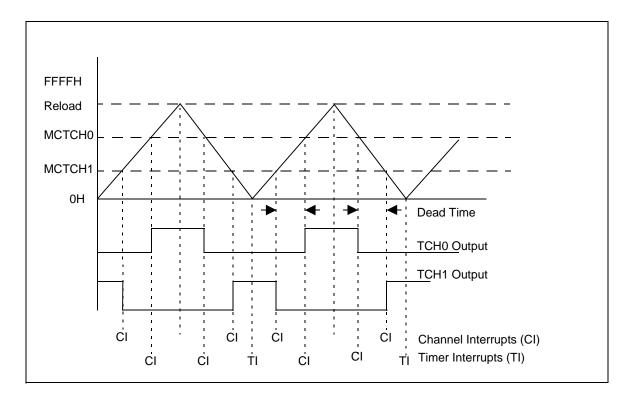

### 1.4.16. Multi-Channel Timer

The multi-channel timer has a 16-bit up/down counter and a 4-channel Capture/Compare/ PWM channel array. This timer enables the support of multiple synchronous Capture/ Compare/PWM channels based on a single timer.

### 1.4.17. Interrupt Controller

The Z8 Encore! XP F1680 Series products support up to thirty-one interrupt sources with twenty-four interrupt vectors. These interrupts consist of up to fifteen internal peripheral interrupts and up to sixteen GPIO pin interrupts. The interrupts have three levels of programmable-interrupt priority.

#### 1.4.18. Reset Controller

The F1680 Series MCU is reset using the  $\overline{\text{RESET}}$  pin, POR, WDT time-out, STOP Mode exit, or VBO warning signal. The  $\overline{\text{RESET}}$  pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

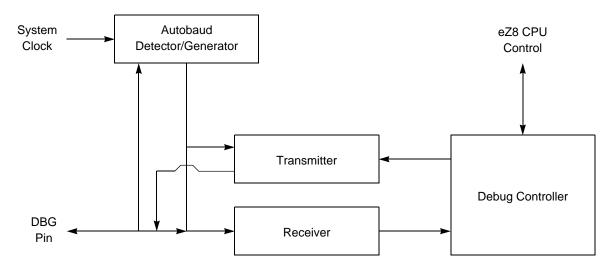

### 1.4.19. On-Chip Debugger

The F1680 Series MCU features an integrated OCD. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. The OCD uses one single-pin interface for communication with an external host.

### 1.4.20. Direct LED Drive

The Port C pins also provide a current synchronized output capable of driving an LED without requiring any external resistor. Up to eight LEDs are driven with individually programmable drive current level from 3 mA to 20mA.

need to use this on-chip Program RAM to shadow Interrupt Service Routines (ISR). For details, see the <u>PRAM\_M</u> section on page 278.

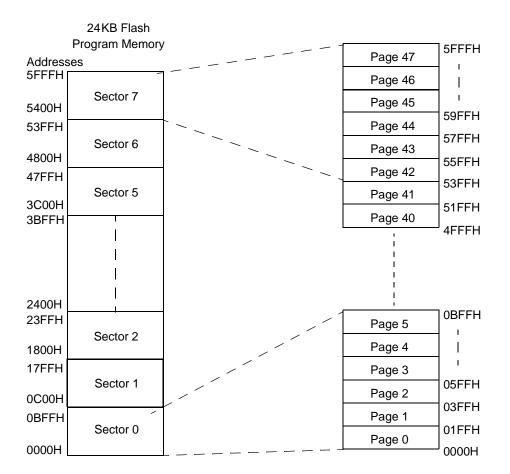

# 3.2. Program Memory

The eZ8 CPU supports 64KB of Program Memory address space. The F1680 Series MCU contains 8KB to 24KB of on-chip Flash memory in the Program Memory address space, depending on the device.

In addition, the F1680 Series MCU contains up to 1 KB of on-chip Program RAM. The Program RAM is mapped in the Program Memory address space beyond the on-chip Flash memory. The Program RAM is entirely under user control and is meant to store interrupt service routines of high-frequency interrupts. Since interrupts bring the CPU out of low-power mode, it is important to ensure that interrupts that occur very often use as low a current as possible. For battery operated systems, Program RAM based handling of high-frequency interrupts provides power savings by keeping the Flash block disabled. Program RAM (PRAM) is optimized for low-current operation and can be easily boot-strapped with interrupt code at power up.

Reading from Program Memory addresses present outside the available Flash memory and PRAM addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the F1680 Series MCU.

| Program Memory<br>Address (Hex) | Function                        |  |  |  |

|---------------------------------|---------------------------------|--|--|--|

| Z8F2480 Device                  |                                 |  |  |  |

| 0000–0001                       | Flash option bits               |  |  |  |

| 0002–0003                       | Reset vector                    |  |  |  |

| 0004–0005                       | WDT interrupt vector            |  |  |  |

| 0006–0007                       | Illegal instruction trap        |  |  |  |

| 0008–0037                       | Interrupt vectors*              |  |  |  |

| 0038–003D                       | Oscillator fail traps*          |  |  |  |

| 003E-5FFF                       | Program Flash                   |  |  |  |

| E000–E3FF                       | 1KB PRAM                        |  |  |  |

|                                 | on page 69 for a list of inter- |  |  |  |

| rupt vectors and                | traps.                          |  |  |  |

#### Table 6. F1680 Series MCU Program Memory Maps

# Chapter 5. Reset, Stop Mode Recovery and Low-Voltage Detection

The Reset Controller within the F1680 Series MCU controls Reset and Stop Mode Recovery operations and provides indication of low-voltage supply conditions. During the operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO) protection

- Watchdog Timer (WDT) time-out (when configured by the WDT\_RES Flash option bit to initiate a Reset)

- External **RESET** pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by each of the following:

- Watchdog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- Interrupt from a timer or comparator enabled for STOP Mode operation

The low-voltage detection circuitry on the device features the following:

- The low-voltage detection threshold level is user-defined

- It generates an interrupt when the supply voltage drops below a user-defined level

# 5.1. Reset Types

The F1680 Series MCU provides various types of Reset operation. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The System Reset is longer, if the external crystal oscillator is enabled by the Flash option bits allowing additional time for oscillator start-up.

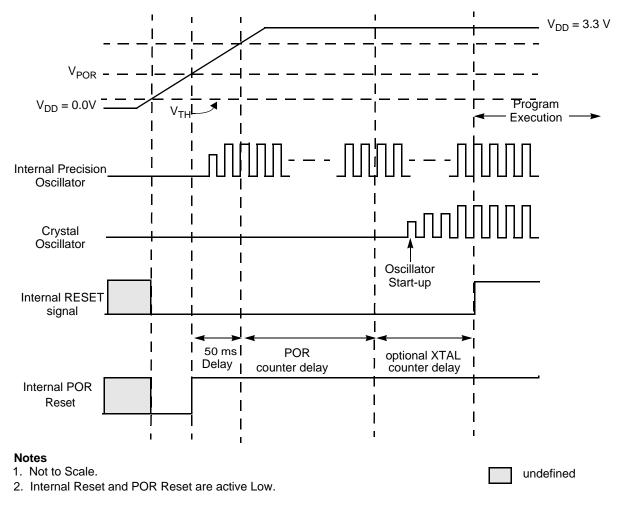

## 5.2.1. Power-On Reset

Each device in the Z8 Encore! XP F1680 Series contains an internal Power-On Reset (POR) circuit. The POR circuit monitors the supply voltage and holds the whole device in the Reset state until the supply voltage reaches a safe circuit operating level when the device is powered on.

After power on, the POR circuit keeps idle until the supply voltage drops below  $V_{TH}$  voltage. Figure 7 on page 35 displays this POR timing.

After the F1680 Series MCU exits the POR state, the eZ8 CPU fetches the Reset vector. Following this POR, the POR/VBO status bit in the Reset Status Register is set to 1.

For the POR threshold voltage ( $V_{POR}$ ) and POR start voltage  $V_{TH}$ , see the <u>Electrical</u> <u>Characteristics chapter on page 349</u>.

Figure 6. Power-On Reset Operation

## 8.4.3. Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) Register, shown in Table 39, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

| Bits    | 7        | 6                           | 5     | 4     | 3    | 2    | 1    | 0    |

|---------|----------|-----------------------------|-------|-------|------|------|------|------|

| Field   | Reserved | MCTI                        | U1RXI | U1TXI | PC3I | PC2I | PC1I | PC0I |

| Reset   | 0        | 0                           | 0     | 0     | 0    | 0    | 0    | 0    |

| R/W     | R/W      | R/W R/W R/W R/W R/W R/W R/W |       |       |      |      |      |      |

| Address | FC6H     |                             |       |       |      |      |      |      |

#### Table 39. Interrupt Request 2 Register (IRQ2)

| Bit                    | Description                                                                                                                                                                                                                                                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]                    | Reserved; must be 0.                                                                                                                                                                                                                                        |

| [6]                    | Multi-channel timer Interrupt Request                                                                                                                                                                                                                       |

| MCTI                   | <ul><li>0 = No interrupt request is pending for multi-channel timer.</li><li>1 = An interrupt request from multi-channel timer is awaiting service.</li></ul>                                                                                               |

| [5]<br>U1RXI           | <ul> <li>UART 1 Receiver Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 1 receiver.</li> <li>1 = An interrupt request from the UART 1 receiver is awaiting service.</li> </ul>                                                 |

| [4]<br>U1TXI           | <ul> <li>UART 1 Transmitter Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 1 transmitter.</li> <li>1 = An interrupt request from the UART 1 transmitter is awaiting service.</li> </ul>                                        |

| [3:0]<br>PC <i>x</i> l | <ul> <li>Port C Pin x Interrupt Request</li> <li>0 = No interrupt request is pending for GPIO Port C pin x.</li> <li>1 = An interrupt request from GPIO Port C pin x is awaiting service; x indicates the specific GPIO Port C pin number (0–3).</li> </ul> |

| Bits                      | 7                                                                        | 6                                                               | 5           | 4           | 3       | 2       | 1       | 0      |

|---------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-------------|---------|---------|---------|--------|

| Field                     | PA7VENL                                                                  | PA6C0ENL                                                        | PA5C1ENL    | PAD4ENL     | PAD3ENL | PAD2ENL | PAD1ENL | PA0ENL |

| Reset                     | 0                                                                        | 0                                                               | 0           | 0           | 0       | 0       | 0       | 0      |

| R/W                       | R/W                                                                      | R/W                                                             | R/W         | R/W         | R/W     | R/W     | R/W     | R/W    |

| Address                   |                                                                          | FC5H                                                            |             |             |         |         |         |        |

| Bit                       | Description                                                              |                                                                 |             |             |         |         |         |        |

| [7]<br>PA7VENL            | Port A B                                                                 | Port A Bit[7] or LVD Interrupt Request Enable Low Bit.          |             |             |         |         |         |        |

| [6]<br>PA6C0EN            |                                                                          | Port A Bit[6] or Comparator 0 Interrupt Request Enable Low Bit. |             |             |         |         |         |        |

| [5]<br>PA5C1EN            |                                                                          | Port A Bit[5] or Comparator 1 Interrupt Request Enable Low Bit. |             |             |         |         |         |        |

| [4:1]<br>PAD <i>x</i> ENL | Port A or Port D Bit[x] (x=1, 2, 3, 4) Interrupt Request Enable Low Bit. |                                                                 |             |             |         |         |         |        |

| [0]<br>PA0ENL             | Port A B                                                                 | it[0] Interrup                                                  | t Request E | nable Low E | Bit.    |         |         |        |

#### Table 45. IRQ1 Enable Low Bit Register (IRQ1ENL)

## 8.4.6. IRQ2 Enable High and Low Bit Registers

Table 46 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 47 and 48 form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register. Priority is generated by setting bits in each register.

| IRQ2ENH[x]                                       | IRQ2ENL[x] | Priority | Description |  |

|--------------------------------------------------|------------|----------|-------------|--|

| 0                                                | 0          | Disabled | Disabled    |  |

| 0                                                | 1          | Level 1  | Low         |  |

| 1                                                | 0          | Level 2  | Nominal     |  |

| 1                                                | 1          | Level 3  | High        |  |

| Note: An x indicates the register bits from 0–7. |            |          |             |  |

|  | Table 46. | IRQ2 | Enable | and | Priority | Encoding |

|--|-----------|------|--------|-----|----------|----------|

|--|-----------|------|--------|-----|----------|----------|

| Bit                     | Description                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| [5]<br>PA5CS            | <b>PA5/Comparator 1 Selection</b><br>0 = PA5 is used for the interrupt for PA5CS interrupt request.                         |

| FA0C3                   | 1 = The Comparator 1 is used for the interrupt for PASCS interrupt request.                                                 |

| [4:1]<br>PAD <i>x</i> S | PAx/PDx Selection<br>0 = PAx is used for the interrupt for PAx/PDx interrupt request                                        |

|                         | 1 = PDx is used for the interrupt for PAx/PDx interrupt request; an x indicates the specific GPIO port pin number $(1-4)$ . |

| [0]                     | Reserved; must be 0.                                                                                                        |

## 8.4.9. Interrupt Control Register

The Interrupt Control (IRQCTL) Register, shown in Table 51, contains the master enable bit for all interrupts.

| Bits    | 7    | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

|---------|------|---|---|---|----------|---|---|---|

| Field   | IRQE |   |   |   | Reserved |   |   |   |

| Reset   | 0    | 0 | 0 | 0 | 0        | 0 | 0 | 0 |

| R/W     | R/W  | R | R | R | R        | R | R | R |

| Address | FCFH |   |   |   |          |   |   |   |

Table 51. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | Interrupt Request Enable<br>This bit is set to 1 by executing an Enable Interrupts (EI) or IRET (Interrupt Return) instruction,<br>or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8<br>CPU acknowledgement of an interrupt request, a Reset, or by a direct register write of a 0 to<br>this bit.<br>0 = Interrupts are disabled.<br>1 = Interrupts are enabled. |

| [6:0]       | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                                                                                                  |

$PWM Period (s) = \frac{Reload Value \times Prescale}{Timer Clock Frequency (Hz)}$

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value - PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### 9.2.3.8. CAPTURE Mode

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM0 High and Low Byte registers. The Timer counts timer clocks up to the 16-bit reload value. The TPOL bit in the Timer Control 1 Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in Timer Control 0 Register is set to indicate the timer interrupt is due to an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in Timer Control 0 Register is cleared to indicate the timer interrupt is not due to an input capture event.

Observe the following steps to configure a timer for CAPTURE Mode and initiate the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer Control 2 Register to choose the timer clock source.

- 3. Write to the Timer Control 0 Register to set the timer interrupt configuration field TICONFIG.

106

## 9.2.4. Reading the Timer Count Values

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

## 9.2.5. Timer Output Signal Operation

The Timer Output is a GPIO port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

## 9.2.6. Timer Noise Filter

A Noise Filter circuit is included which filters noise on a Timer Input signal before the data is sampled by the block.

The Noise Filter has the following features:

- Synchronizes the receive input data to the Timer Clock

- NFEN (Noise Filter Enable) input selects whether the Noise Filter is bypassed (NFEN=0) or included (NFEN=1) in the receive data path

- NFCTL (Noise Filter Control) input selects the width of the up/down saturating counter digital filter. The available widths range from 4 bits to 11 bits

- The digital filter output has hysteresis

- Provides an active Low *saturated state* output (FiltSatB) which is used as an indication of the presence of noise

- Available for operation in STOP Mode

### 9.2.7. Architecture

Figure 12 displays how the Noise Filter is integrated with the Timer.

Figure 17. Count Up/Down Mode with PWM Channel Outputs and Deadband

## **10.6.2. Multiple Timer Intervals Generation**

Figure 18 shows a timing diagram featuring two constant time intervals, T0 and T1. The timer is in Count Modulo Mode with reload = FFFFH. Channels 0 and 1 are set up for CONTINUOUS COMPARE operation. After every channel compare interrupt, the channel Capture/Compare registers are updated in the interrupt service routine by adding a constant equal to the time interval required. This operation requires that the Channel Update Enable (CHUE) bit must be set in channels 0 and 1 so that writes to the Capture/ Compare registers take affect immediately.

Figure 53. 24KB Flash Memory Arrangement

## 20.2. Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for byte programming, Page Erase and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanisms operate on the page, sector and full-memory levels.

The Flow Chart in Figure 54 displays basic Flash Controller operation. The sections that follow provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase and Mass Erase) shown in Figure 54.

265

# Chapter 23. On-Chip Debugger

The Z8 Encore! XP F1680 Series device contains an integrated On-Chip Debugger (OCD) that provides advanced debugging features, including:

- Reading and writing of the Register File

- Reading and writing of Program and Data Memory

- Setting of breakpoints

- Executing eZ8 CPU instructions

## 23.1. Architecture

The OCD consists of four primary functional blocks:

- Transmitter

- Receiver

- Autobaud detector/generator

- Debug controller

Figure 55 displays the architecture of the On-Chip Debugger.

secutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of SCKSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## 24.1.2. Clock Failure Detection and Recovery

Clock failure detection and recovery are provided for the primary oscillator. Clock failure detection is provided for the Watchdog Timer oscillator.

#### 24.1.2.1. Primary Oscillator Failure

The Z8 Encore! XP F1680 Series devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available, if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the <u>Watchdog Timer</u> chapter on page 140.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the primary oscillator failure circuitry (i.e., clear the POFEN bit).

#### 24.1.2.2. Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar nonmaskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by clearing the WDFEN bit of the OSCCTL0 Register.

# Chapter 25. Crystal Oscillator

The products in the Z8 Encore! XP F1680 Series contain a primary on-chip crystal oscillator for use with external crystals with 1 MHz to 20MHz frequencies, plus a secondary 32K crystal oscillator. In addition, the external oscillator supports external RC networks with oscillation frequencies up to 4MHz. The 32K secondary crystal oscillator does not feature an external RC oscillator mode. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Additionally, the secondary 32K crystal oscillator can only be used to generate a clock for three timers.

Alternatively, the  $X_{IN}$  and  $X2_{IN}$  input pins can also accept a CMOS-level clock input signal (for  $X_{IN}$ , the frequency range is 32kHz–20MHz; for  $X2_{IN}$ , the range is below 4MHz). If an external clock generator is used, the  $X_{OUT}$  or  $X2_{OUT}$  pin must remain unconnected. The Z8 Encore! XP F1680 Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock; the frequency of the signal on the  $X2_{IN}$  determines the frequency of the timers.

**Note:** Although the X<sub>IN</sub> pin can be used as a primary system clock input for an external clock generator, the CLKIN pin is better suited for such use. For details, see the <u>System Clock</u> <u>Selection</u> section on page 315.

## 25.1. Operating Modes

The primary on-chip crystal oscillator supports three oscillator modes:

- Medium power for use with medium frequency crystals or ceramic resonators (1MHz to 8MHz)

- Maximum power for use with high-frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks or external clock input (<4MHz)

The primary on-chip crystal oscillator mode is selected using user-programmable Flash option bits. For information, see the <u>Flash Option Bits</u> section on page 276. The secondary 32kHz crystal oscillator supports two oscillator modes:

- NORMAL Mode for use with 32kHz crystals

- On-chip oscillator configured for use with external clock input

#### Table 179. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |  |  |  |

|----------|-------------|------------------------------------------------------|--|--|--|

| BCLR     | bit, dst    | Bit Clear                                            |  |  |  |

| BIT      | p, bit, dst | Bit Set or Clear                                     |  |  |  |

| BSET     | bit, dst    | Bit Set                                              |  |  |  |

| BSWAP    | dst         | Bit Swap                                             |  |  |  |

| CCF      |             | Complement Carry Flag                                |  |  |  |

| RCF      | —           | Reset Carry Flag                                     |  |  |  |

| SCF      |             | Set Carry Flag                                       |  |  |  |

| ТСМ      | dst, src    | Test Complement Under Mask                           |  |  |  |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |  |  |  |

| ТМ       | dst, src    | Test Under Mask                                      |  |  |  |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |  |  |  |

#### Table 180. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

#### Table 181. CPU Control Instructions

| Mnemonic | Operands | Instruction           |  |

|----------|----------|-----------------------|--|

| ATM      | _        | Atomic Execution      |  |

| CCF      | —        | Complement Carry Flag |  |

| DI       | —        | Disable Interrupts    |  |

| EI       | _        | Enable Interrupts     |  |

| HALT     | —        | HALT Mode             |  |

| NOP      | —        | No Operation          |  |

| RCF      | _        | Reset Carry Flag      |  |

| SCF      | —        | Set Carry Flag        |  |

| SRP      | src      | Set Register Pointer  |  |

Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

Figure 68. Second Op Code Map after 1FH

348

|                                               | VDD = 2.7V to 3.6V<br>TA = 0°C to +70°C<br>TA = -40°C to +105°C |     |     |        |                                            |

|-----------------------------------------------|-----------------------------------------------------------------|-----|-----|--------|--------------------------------------------|

| Parameter                                     | Min                                                             | Тур | Мах | Units  | Conditions                                 |

| Flash Byte Read Time                          | 100                                                             | _   | -   | ns     | $V_{DD} = 1.8 \text{ V to } 3.6 \text{ V}$ |

| Flash Byte Program Time                       | 20                                                              | _   | 40  | μs     |                                            |

| Flash Page Erase Time                         | 50                                                              | _   | _   | ms     |                                            |

| Flash Mass Erase Time                         | 50                                                              | _   | _   | ms     |                                            |

| Writes to Single Address Before<br>Next Erase | -                                                               | -   | 2   |        |                                            |

| Data Retention                                | 20                                                              | _   | _   | years  | 25°C                                       |

| Endurance                                     | 5,000                                                           | _   | _   | cycles | Program/erase cycles                       |

#### Table 193. Flash Memory Electrical Characteristics and Timing

### Table 194. Watchdog Timer Electrical Characteristics and Timing

|                      |                          | VDD = 1.8V to 3.6V<br>TA = 0°C to +70°C<br>TA = -40°C to +105°C |     |     |      |                       |

|----------------------|--------------------------|-----------------------------------------------------------------|-----|-----|------|-----------------------|

| Symbol               | Parameter                | Min                                                             | Тур | Max | Unit | Conditions            |

| T <sub>STARTUP</sub> |                          | _                                                               | _   | 10  | ms   | After pd disable only |

| I <sub>DD</sub> WDT  | WDT Active Current       | _                                                               | -   | 5   | μA   |                       |

| I <sub>DDQ</sub> WDT | WDT Quiescent Current    | _                                                               | 5   | _   | nA   |                       |

| F <sub>WDT</sub>     | WDT Oscillator Frequency | 2.5                                                             | 5   | 20  | kHz  |                       |

#### Table 195. Non-Volatile Data Storage

|                        | TA =   | 9 = 2.7V to 3<br>= 0°C to +7<br>-40°C to +7 | 0°C  |        |                                           |

|------------------------|--------|---------------------------------------------|------|--------|-------------------------------------------|

| Parameter              | Min    | Тур                                         | Max  | Units  | Conditions                                |

| NVDS Byte Read Time    | 34     | _                                           | 519  | μs     | With system clock at 20MHz                |

| NVDS Byte Program Time | 0.171  | _                                           | 39.7 | ms     | With system clock at 20MHz                |

| Data Retention         | 20     | _                                           | _    | years  | 25°C                                      |

| Endurance              | 50,000 | _                                           | _    | cycles | Cumulative write cycles for entire memory |

mode fault error 210 mode register 217 multi-master operation 207 operation 199 overrun error 210, 211 signals 199 single master, multiple slave system 208 single master, single slave system 208 status register 219 timing, PHASE = 0.202timing, PHASE=1 203 SPI controller signals 14 SPI mode (SPIMODE) 217 SPIBRH register 222 SPIBRL register 222 SPIDATA register 214 SPIMODE register 217 SPISTAT register 219 **SRA 335** src 331 SRL 335 **SRP 333** SS, SPI signal 199 stack pointer 331 **STOP 334** stop mode 42, 334 stop mode recovery sources 37, 39 using a GPIO port pin transition 39 using watch-dog timer time-out 38 **SUB 332** subtract 332 subtract - extended addressing 332 subtract with carry 332 subtract with carry - extended addressing 332 **SUBX 332 SWAP 335** swap nibbles 335 symbols, additional 331

#### Т

TCM 333 TCMX 333 test complement under mask 333 test complement under mask - extended addressing 333 test under mask 333 test under mask - extended addressing 333 timer signals 15 timers 84 architecture 85, 120 block diagram 85, 121 capture mode 97, 114, 115 capture/compare mode 102, 114 compare mode 100 continuous mode 90 counter mode 91, 92 gated mode 100, 114 operating mode 87 PWM mode 93, 95, 114, 115 reading the timer count values 106 reload high and low byte registers 109, 130, 131 timer control register definitions 108 timer output signal operation 106 timers 0-3 control registers 112, 113, 117, 118 high and low byte registers 109, 110, 111, 130 timing diagram, voltage measurement 188 TM 333 **TMX 333** transmit IrDA data 183 transmitting UART data-interrupt-driven method 147 transmitting UART data-polled method 146 TRAP 335 Trim Bit Address Option Bits 281 Trim Bit Address Space 282 Trim Bit Data Option Bits 281

### U

UART 4 architecture 144 baud rate generator 160 baud rates table 179, 180, 181 control register definitions 163 controller signals 14 data format 145 384