Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 24KB (24K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2480hj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 118. | I2C Master/Slave Controller Registers                               |

|------------|---------------------------------------------------------------------|

| Table 119. | I2C Data Register (I2CDATA = F50H) 244                              |

| Table 120. | I2C Interrupt Status Register (I2CISTAT = F51H) 245                 |

| Table 121. | I2C Control Register (I2CCTL)                                       |

| Table 122. | I2C Baud Rate High Byte Register (I2CBRH = 53H) 248                 |

| Table 123. | I2C Baud Rate Low Byte Register (I2CBRL = F54H)                     |

| Table 124. | I2C State Register (I2CSTATE)—Description when DIAG = 1 250         |

| Table 125. | I2C State Register (I2CSTATE)—Description when $DIAG = 0 \dots 251$ |

| Table 126. | I2CSTATE_L                                                          |

| Table 127. | I2CSTATE_H                                                          |

| Table 128. | I2C Mode Register (I2C Mode = F56H) 253                             |

| Table 129. | I2C Slave Address Register (I2CSLVAD = 57H) 255                     |

| Table 130. | Comparator 0 Control Register (CMP0) 257                            |

| Table 131. | Comparator 1 Control Register (CMP1) 258                            |

| Table 132. | Z8 Encore! XP F1680 Series Flash Memory Configurations 262          |

| Table 133. | Flash Code Protection Using the Flash Option Bit                    |

| Table 134. | Flash Control Register (FCTL)                                       |

| Table 135. | Flash Status Register (FSTAT)                                       |

| Table 136. | Flash Page Select Register (FPS) 273                                |

| Table 137. | Flash Sector Protect Register (FPROT)                               |

| Table 138. | Flash Frequency High Byte Register (FFREQH)                         |

| Table 139. | Flash Frequency Low Byte Register (FFREQL) 275                      |

| Table 140. | Flash Option Bits at Program Memory Address 0000H 278               |

| Table 141. | Flash Option Bits at Program Memory Address 0001H 280               |

| Table 142. | Trim Bit Data Register (TRMDR) 281                                  |

| Table 143. | Trim Bit Address Register (TRMADR)                                  |

| Table 144. | Trim Bit Address Map                                                |

|            | Trim Bit Address Description                                        |

| Table 146. | Trim Option Bits at Address 0000H (TTEMP0) 282                      |

| Table 147. | Trim Option Bits at 0001H (TTEMP1) 283                              |

### xxii

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                      | Active<br>Low or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up or<br>Pull-down                     | Schmitt<br>Trigger<br>Input | Open Drain<br>Output                                        | 5V<br>Tolerance                                                     |

|--------------------|-----------|-----------------------------------------|------------------------------------|--------------------|---------------------------------------------------------|-----------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|

| PE[6:0]            | I/O       | I                                       | N/A                                | Yes                | Programmable<br>pull-up                                 | Yes                         | Yes,<br>programmab<br>le                                    | Yes, 5V<br>tolerant<br>inputs<br>unless pull-<br>ups are<br>enabled |

| RESET/<br>PD0      | I/O       | I/O<br>(defaults<br><u>to</u><br>RESET) | Low (in<br>RESET<br>mode)          | Yes (PD0<br>only)  | Programmable<br>for PD0 <u>; always</u><br>On for RESET |                             | Programmab<br>le for PD0;<br>alw <u>ays On</u><br>for RESET | Yes, 5V<br>tolerant<br>inputs<br>unless pull-<br>ups are<br>enabled |

| V <sub>DD</sub>    | N/A       | N/A                                     | N/A                                | N/A                |                                                         |                             | N/A                                                         | N/A                                                                 |

| V <sub>SS</sub>    | N/A       | N/A                                     | N/A                                | N/A                |                                                         |                             | N/A                                                         | N/A                                                                 |

18

| Program Memory Address (Hex) | Function                                                                                  |

|------------------------------|-------------------------------------------------------------------------------------------|

| FE00–FE3F                    | Zilog option bits                                                                         |

| FE40-FE53                    | Part Number:<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH |

| FE54–FE5F                    | Reserved                                                                                  |

| FE60–FE7F                    | Zilog calibration data (only use the first two bytes FE60 and FE61)                       |

| FE80–FFFF                    | Reserved                                                                                  |

## Table 7. F1680 Series MCU Flash Memory Information Area Map

|               | <b>v</b>                                   | , ,           |                          |            |

|---------------|--------------------------------------------|---------------|--------------------------|------------|

| Address (Hex) | Register Description                       | Mnemonic      | Reset (Hex) <sup>1</sup> | Page #     |

| F17           | Timer 2 Control 1                          | T2CTL1        | 00                       | <u>113</u> |

| F28           | Timer 2 PWM1 High Byte                     | T2PWM1H       | 00                       | <u>111</u> |

| F29           | Timer 2 PWM1 Low Byte                      | T2PWM1L       | 00                       | <u>111</u> |

| F2A           | Timer 2 Control 2                          | T2CTL2        | 00                       | <u>117</u> |

| F2B           | Timer 2 Status                             | T2STA         | 00                       | <u>118</u> |

| F2E           | Timer 2 Noise Filter Control               | T2NFC         | 00                       | <u>119</u> |

| F2F–F3F       | Reserved                                   | —             | XX                       |            |

| LIN UART 0    |                                            |               |                          |            |

| F40           | LIN UART0 Transmit Data                    | U0TXD         | XX                       | <u>163</u> |

|               | LIN UART0 Receive Data                     | U0RXD         | XX                       | <u>164</u> |

| F41           | LIN UART0 Status 0—Standard UART Mode      | U0STAT0       | 0000011Xb                | <u>165</u> |

|               | LIN UART0 Status 0—LIN Mode                | U0STAT0       | 00000110b                | <u>166</u> |

| F42           | LIN UART0 Control 0                        | U0CTL0        | 00                       | <u>170</u> |

| F43           | LIN UART0 Control 1—Multiprocessor Control | U0CTL1        | 00                       | <u>172</u> |

|               | LIN UART0 Control 1—Noise Filter Control   | U0CTL1        | 00                       | <u>174</u> |

|               | LIN UART0 Control 1—LIN Control            | U0CTL1        | 00                       | <u>175</u> |

| F44           | LIN UART0 Mode Select and Status           | U0MDSTAT      | 00                       | <u>168</u> |

| F45           | UART0 Address Compare                      | <b>U0ADDR</b> | 00                       | <u>177</u> |

| F46           | UART0 Baud Rate High Byte                  | U0BRH         | FF                       | <u>177</u> |

| F47           | UART0 Baud Rate Low Byte                   | U0BRL         | FF                       | <u>178</u> |

| LIN UART 1    |                                            |               |                          |            |

| F48           | LIN UART1 Transmit Data                    | U1TXD         | XX                       | <u>163</u> |

|               | LIN UART1 Receive Data                     | U1RXD         | XX                       | <u>164</u> |

| F49           | LIN UART1 Status 0—Standard UART Mode      | U1STAT0       | 0000011Xb                | <u>165</u> |

|               | LIN UART1 Status 0—LIN Mode                | U1STAT0       | 00000110b                | <u>166</u> |

| F4A           | LIN UART1 Control 0                        | U1CTL0        | 00                       | <u>170</u> |

| Notoo         |                                            |               |                          |            |

### Table 8. Register File Address Map (Continued)

Notes:

1. XX=Undefined.

2. The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM.

# 7.4. Direct LED Drive

The Port C pins provide a current synchronized output capable of driving an LED without requiring an external resistor. The output synchronizes current at programmable levels of 3mA, 7mA, 13mA and 20mA. This mode is enabled through the Alternate Function subregister AFS1 and is programmable through the LED control registers. For proper function, the LED anode must be connected to  $V_{\text{DD}}$  and the cathode to the GPIO pin.

Using all Port C pins in LED drive mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see the <u>Electrical</u> <u>Characteristics chapter on page 349</u>.

# 7.5. Shared Reset Pin

On all the devices, the Port D0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO pin on power-up. This pin acts as a bidirectional input/open-drain output reset with an internal pull-up until user software reconfigures it as GPIO PD0. The Port D0 pin is output-only when in GPIO Mode, and must be configured as an output. PD0 supports the High Drive feature but not the Stop Mode Recovery feature.

# 7.6. Crystal Oscillator Override

For systems using the crystal oscillator, PA0 and PA1 is used to connect the crystal. When the main crystal oscillator is enabled (see the <u>Oscillator Control1 Register</u> section on page 320), the GPIO settings are overridden and PA0 and PA1 is disabled.

## 7.7. 32kHz Secondary Oscillator Override

For systems using a 32kHz secondary oscillator, PA2 and PA3 is used to connect a watch crystal. When the 32kHz secondary oscillator is enabled (see the <u>Oscillator Control1 Register</u> section on page 320), the GPIO settings are overridden and PA2 and PA3 is disabled.

## 7.8. 5V Tolerance

All GPIO pins, including those that share functionality with an ADC, crystal or comparator signals are 5V-tolerant and can handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

| Port   | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | AFS1[0]: 0                              |

|        |     | Reserved   |                                         | AFS1[0]: 1                              |

|        | PA1 | T0OUT      | Timer 0 Output                          | AFS1[1]: 0                              |

|        |     | Reserved   |                                         | AFS1[1]: 1                              |

|        | PA2 | DE0        | UART 0 Driver Enable                    | AFS1[2]: 0                              |

|        |     | Reserved   |                                         | AFS1[2]: 1                              |

| PA3    |     | CTS0       | UART 0 Clear to Send                    | AFS1[3]: 0                              |

|        |     | Reserved   |                                         | AFS1[3]: 1                              |

| PA4    |     | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | AFS1[4]: 0                              |

|        | _   | Reserved   |                                         | AFS1[4]: 1                              |

|        | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | AFS1[5]: 0                              |

|        |     | Reserved   |                                         | AFS1[5]: 1                              |

|        | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | AFS1[6]: 0                              |

|        |     | SCL        | I <sup>2</sup> C Serial Clock           | AFS1[6]: 1                              |

|        | PA7 | T1OUT      | Timer 1 Output                          | AFS1[7]: 0                              |

|        |     | SDA        | I <sup>2</sup> C Serial Data            | AFS1[7]: 1                              |

### Table 18. Port Alternate Function Mapping, 28-Pin Parts<sup>1,2</sup>

Notes:

Because there are at most two choices of alternate functions for some pins in Ports A and B, the Alternate Function Set Register (AFS2) is implemented but not used to select the function. The alternate function selection must also be enabled, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

2. Because there is only one alternate function for each Port D and Port E pin, the Alternate Function Set registers are not implemented for Ports D and E. Enabling the alternate function selections automatically enables the associated alternate function, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

## 7.11.14. LED Drive Level Registers

Two LED Drive Level registers consist of the LED Drive Level High Bit Register (LEDLVLH[7:0]) and the LED Drive Level Low Bit Register (LEDLVLL[7:0]), as shown in Tables 34 and 35. Two control bits, LEDLVLH[x] and LEDLVLL[x], are used to select one of four programmable current drive levels for each associated Port C[x] pin. Each Port C pin is individually programmable.

### Table 34. LED Drive Level High Bit Register (LEDLVLH)

| Bits    | 7   | 6    | 5   | 4    | 3    | 2   | 1   | 0   |

|---------|-----|------|-----|------|------|-----|-----|-----|

| Field   |     |      |     | LEDI | _VLH |     |     |     |

| Reset   | 0   | 0    | 0   | 0    | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Address |     | F83H |     |      |      |     |     |     |

### Table 35. LED Drive Level Low Bit Register (LEDLVLL)

| Bits    | 7   | 6    | 5   | 4   | 3    | 2   | 1   | 0   |

|---------|-----|------|-----|-----|------|-----|-----|-----|

| Field   |     |      |     | LED | LVLL |     |     |     |

| Reset   | 0   | 0    | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W  | R/W | R/W | R/W  | R/W | R/W | R/W |

| Address |     | F84H |     |     |      |     |     |     |

| Bit               | Description                                                                                                                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>LEDLVLH, | LED Drive Level High Bit<br>LED Drive Level Low Bit                                                                                                                                                                                                                |

| LEDLVLL           | These bits are used to set the LED drive current. {LEDLVLH[x], LEDLVLL[x]}, in which $x=Port C[0]$ to Port C[7]. Select one of the following four programmable current drive levels for each Port C pin.<br>00 = 3  mA<br>01 = 7  mA<br>10 = 13  mA<br>11 = 20  mA |

## 8.4.1. Interrupt Request 0 Register

The Interrupt Request 0 (IRQ0) Register, shown in Table 37, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

| Bits    | 7    | 6   | 5   | 4     | 3     | 2    | 1    | 0    |

|---------|------|-----|-----|-------|-------|------|------|------|

| Field   | T2I  | T1I | TOI | UORXI | U0TXI | I2CI | SPII | ADCI |

| Reset   | 0    | 0   | 0   | 0     | 0     | 0    | 0    | 0    |

| R/W     | R/W  | R/W | R/W | R/W   | R/W   | R/W  | R/W  | R/W  |

| Address | FCOH |     |     |       |       |      |      |      |

## Table 37. Interrupt Request 0 Register (IRQ0)

| Bit          | Description                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>T2I   | <ul> <li>Timer 2 Interrupt Request</li> <li>0 = No interrupt request is pending for Timer 2.</li> <li>1 = An interrupt request from Timer 2 is awaiting service.</li> </ul>                                          |

| [6]<br>T1I   | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service.                                                                   |

| [5]<br>T0I   | <ul> <li>Timer 0 Interrupt Request</li> <li>0 = No interrupt request is pending for Timer 0.</li> <li>1 = An interrupt request from Timer 0 is awaiting service.</li> </ul>                                          |

| [4]<br>U0RXI | <ul> <li>UART 0 Receiver Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 0 receiver.</li> <li>1 = An interrupt request from the UART 0 receiver is awaiting service.</li> </ul>          |

| [3]<br>U0TXI | <ul> <li>UART 0 Transmitter Interrupt Request</li> <li>0 = No interrupt request is pending for the UART 0 transmitter.</li> <li>1 = An interrupt request from the UART 0 transmitter is awaiting service.</li> </ul> |

| [2]<br>I2CI  | <ul> <li>I<sup>2</sup>C Interrupt Request</li> <li>0 = No interrupt request is pending for the I<sup>2</sup>C.</li> <li>1 = An interrupt request from I<sup>2</sup>C is awaiting service.</li> </ul>                 |

| [1]<br>SPII  | <ul> <li>SPI Interrupt Request</li> <li>0 = No interrupt request is pending for the SPI.</li> <li>1 = An interrupt request from the SPI is awaiting service.</li> </ul>                                              |

| [0]<br>ADCI  | <ul> <li>ADC Interrupt Request</li> <li>0 = No interrupt request is pending for the ADC.</li> <li>1 = An interrupt request from the ADC is awaiting service.</li> </ul>                                              |

| Bit                     | Description                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| [5]<br>PA5CS            | <b>PA5/Comparator 1 Selection</b><br>0 = PA5 is used for the interrupt for PA5CS interrupt request.                         |

| FA0C3                   | 1 = The Comparator 1 is used for the interrupt for PASCS interrupt request.                                                 |

| [4:1]<br>PAD <i>x</i> S | PAx/PDx Selection<br>0 = PAx is used for the interrupt for PAx/PDx interrupt request                                        |

|                         | 1 = PDx is used for the interrupt for PAx/PDx interrupt request; an x indicates the specific GPIO port pin number $(1-4)$ . |

| [0]                     | Reserved; must be 0.                                                                                                        |

## 8.4.9. Interrupt Control Register

The Interrupt Control (IRQCTL) Register, shown in Table 51, contains the master enable bit for all interrupts.

| Bits    | 7    | 6 | 5 | 4  | 3         | 2 | 1 | 0 |  |  |

|---------|------|---|---|----|-----------|---|---|---|--|--|

| Field   | IRQE |   |   |    | Reserved  |   |   |   |  |  |

| Reset   | 0    | 0 | 0 | 0  | 0         | 0 | 0 | 0 |  |  |

| R/W     | R/W  | R | R | R  | R R R R R |   |   |   |  |  |

| Address |      |   |   | FC | FH        |   |   |   |  |  |

Table 51. Interrupt Control Register (IRQCTL)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | Interrupt Request Enable<br>This bit is set to 1 by executing an Enable Interrupts (EI) or IRET (Interrupt Return) instruction,<br>or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8<br>CPU acknowledgement of an interrupt request, a Reset, or by a direct register write of a 0 to<br>this bit.<br>0 = Interrupts are disabled.<br>1 = Interrupts are enabled. |

| [6:0]       | Reserved; must be 0.                                                                                                                                                                                                                                                                                                                                                                                                  |

Observe the following steps to configure a timer for CAPTURE RESTART Mode and initiate the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode. Setting the mode also involves writing to TMODE[3] bit in the TxCTL0 Register

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer Control 2 Register to choose the timer clock source.

- 3. Write to the Timer Control 0 Register to set the timer interrupt configuration field TICONFIG.

- 4. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 6. Clear the Timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts are generated by either a Capture Event or a Reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, then the interrupt is generated by a Reload.

- 7. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt will be generated for both input capture and reload events. If required, configure the timer interrupt to be generated only at the Input Capture event or the reload event by setting TICONFIG field of the Timer Control 0 Register.

- 8. Configure the associated GPIO port pin for the Timer Input alternate function.

- 9. Write to the Timer Control 1 Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from Timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{Timer Clock Frequency (Hz)}$

# 11.2.1. Watchdog Timer Reload High and Low Byte Registers

The Watchdog Timer Reload High and Low Byte (WDTH, WDTL) registers, shown in Tables 81 and 82, form the 16-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes; this 16-bit reload value is {WDTH[7:0], WDTL[7:0]}. Writing to these registers following the unlock sequence sets the appropriate reload value. Reading from these registers returns the current WDT count value.

### Table 81. Watchdog Timer Reload High Byte Register (WDTH = FF2H)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | WDTH |     |     |     |     |     |     |  |  |  |

| Reset   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |      |     | FF  | 2H  |     |     |     |  |  |  |

Table 82. Watchdog Timer Reload Low Byte Register

(WDTL = FF3H)

| Bit     | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | WDTL |     |     |     |     |     |     |  |  |  |

| Reset   | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |      |     | FF  | 3H  |     |     |     |  |  |  |

| Description                                                                                                |

|------------------------------------------------------------------------------------------------------------|

| Watchdog Timer Reload High and Low Bytes                                                                   |

| WDTH: The WDT Reload High Byte is the most significant byte, or bits [15:8] of the 16-bit WDT              |

| reload value.                                                                                              |

| WDTL: The WDT Reload Low Byte is the least significant byte, or bits [7:0] of the 16-bit WDT reload value. |

|                                                                                                            |

Wake-up message if it requires the master to initiate a LIN message frame. Following the Wake-up message, the master wakes up and initiates a new message. A Wake-up message is accomplished by pulling the bus Low for at least 250  $\mu$ s but less than 5 ms. Transmitting a 00H character is one way to transmit the Wake-up message.

If the CPU is in STOP Mode, the LIN-UART is not active and the Wake-up message must be detected by a GPIO edge detect Stop Mode Recovery. The duration of the Stop Mode Recovery sequence can preclude making an accurate measurement of the Wake-up message duration.

If the CPU is in HALT or OPERATIONAL mode, the LIN-UART (if enabled) times the duration of the Wake-up and provides an interrupt following the end of the break sequence if the duration is  $\geq$  3 bit times. The total duration of the Wake-up message in bit times can be obtained by reading the RxBreakLength field in the Mode Select and Status register. After a Wake-up message has been detected, the LIN-UART can be placed (by software) either into LIN Master or LIN Slave Wait for Break states as appropriate. If the break duration exceeds 15 bit times, the RxBreakLength field contains the value Fh. If the LIN-UART is disabled, Wake-up message is detected via a port pin interrupt and timed by software. If the device is in STOP Mode, the High to Low transition on the port pin will bring the device out of STOP Mode.

The LIN Sleep state is selected by software setting LinState[1:0] = 00. The decision to move from an active state to sleep state is based on the LIN messages as interpreted by software.

### 12.1.10.5. LIN Slave Operation

LIN SLAVE Mode is selected by setting LMST = 0, LSLV = 1, ABEN = 1 or 0 and LinState[1:0] = 01b (Wait for Break state). The LIN slave detects the start of a new message by the break which appears to the Slave as a break of at least 11 bit times in duration. The LIN-UART detects the break and generates an interrupt to the CPU. The duration of the break is observable in the RxBreakLength field of the Mode Select and Status register. A break of less than 11 bit times in duration does not generate a break interrupt when the LIN-UART is in Wait for Break state. If the break duration exceeds 15 bit times, the RxBreakLength field contains the value Fh.

Following the break, the LIN-UART hardware automatically transits to the *Autobaud* state, where it autobauds by timing the duration of the first 8 bit times of the Synch character as defined in the LIN standard. The duration of the autobaud period is measured by the BRG Counter which will update every 8th system clock cycle between the start bit and the beginning of bit 7 of the autobaud sequence. At the end of the autobaud period, the duration measured by the BRG counter (auto baud period divided by 8) is automatically transferred to the Baud Reload High and Low registers if the ABEN bit of the LIN control register is set. If the BRG Counter overflows before reaching the start of bit 7 in the autobaud sequence the Autobaud Overrun Error interrupt occurs, the OE bit in the Status 0 Register is set and the Baud Reload registers are not updated. To autobaud within 2% of the master's baud rate, the slave system clock must be a minimum of 100 times the baud

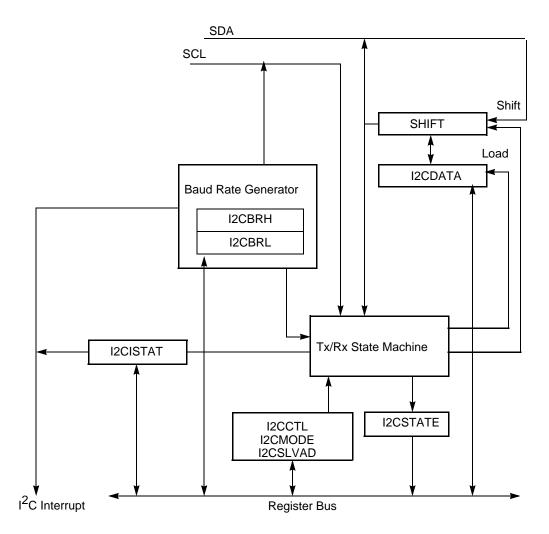

# 17.1.1. I<sup>2</sup>C Master/Slave Controller Registers

Table 118 summarizes the I<sup>2</sup>C Master/Slave controller's software-accessible registers.

| Name                              | Abbreviation | Description                               |

|-----------------------------------|--------------|-------------------------------------------|

| I <sup>2</sup> C Data             | I2CDATA      | Transmit/Receive Data Register.           |

| I <sup>2</sup> C Interrupt Status | I2CISTAT     | Interrupt status register.                |

| I <sup>2</sup> C Control          | I2CCTL       | Control Register—basic control functions. |

Table 118. I<sup>2</sup>C Master/Slave Controller Registers

PS025015-1212

the return from the subroutine, the read byte resides in working register R0 and the read status byte resides in working register R1. The bit fields of this status byte are defined in Table 160. Also, the user code should pop the address byte off the stack.

The read routine uses 16 bytes of stack space in addition to the 1 byte of address pushed by you. Sufficient memory must be available for this stack usage. Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between  $71 \mu s$  and  $258 \mu s$  (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a  $6\mu$ s execution time. The status byte returned by the NVDS read routine is zero for successful read. If the status byte is nonzero, there is a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have an error.

| Bits             | 7 | 6        | 5 | 4  | 3        | 2  | 1      | 0        |

|------------------|---|----------|---|----|----------|----|--------|----------|

| Field            |   | Reserved |   | DE | Reserved | FE | IGADDR | Reserved |

| Default<br>Value | 0 | 0        | 0 | 0  | 0        | 0  | 0      | 0        |

| Table 160. | Read | Status Byt | е |

|------------|------|------------|---|

|------------|------|------------|---|

| Bit           | Description                                                                                                                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]         | Reserved; must be 0.                                                                                                                                                                                                                                                     |

| [4]<br>DE     | <b>Data Error</b><br>When reading a NVDS address, if an error is found in the latest data corresponding to the NVDS address, this bit is set to 1. NVDS source code steps forward until it finds valid data at this address.                                             |

| [3]           | Reserved; must be 0.                                                                                                                                                                                                                                                     |

| [2]<br>FE     | Flash Error<br>If a Flash error is detected, this bit is set to 1.                                                                                                                                                                                                       |

| [1]<br>IGADDR | Illegal Address<br>When NVDS byte reads occur from invalid addresses (those exceeding the NVDS array size),<br>this bit is set to 1.<br>Note: When the NVDS array size is 256 bytes, there is no address exceeding the size: therefore the<br>IGADDR bit cannot be used. |

| [0]           | Reserved; must be 0.                                                                                                                                                                                                                                                     |

## 22.2.3. Power Failure Protection

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed. For this protection to function, the VBO must be enabled (see the <u>Low-Power</u>

|                  |                                                                                           |     |             |               | • • |   |     |     |   |   |        |        |

|------------------|-------------------------------------------------------------------------------------------|-----|-------------|---------------|-----|---|-----|-----|---|---|--------|--------|

| Assembly         |                                                                                           |     | ress<br>ode | Op<br>Code(s) |     |   | Fla | ags |   |   | Fetch  | Instr. |

| Mnemonic         | Symbolic Operation                                                                        | dst | src         | (Hex)         | С   | Ζ | S   | V   | D | Н | Cycles | Cycles |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r   | r           | 52            |     | * | *   | 0   | _ | - | 2      | 3      |

|                  |                                                                                           | r   | lr          | 53            |     |   |     |     |   |   | 2      | 4      |

|                  |                                                                                           | R   | R           | 54            |     |   |     |     |   |   | 3      | 3      |

|                  |                                                                                           | R   | IR          | 55            |     |   |     |     |   |   | 3      | 4      |

|                  |                                                                                           | R   | IM          | 56            | _   |   |     |     |   |   | 3      | 3      |

|                  |                                                                                           | IR  | IM          | 57            |     |   |     |     |   |   | 3      | 4      |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER  | ER          | 58            | -   | * | *   | 0   | - | - | 4      | 3      |

|                  |                                                                                           | ER  | IM          | 59            | _   |   |     |     |   |   | 4      | 3      |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |     |             | 2F            | _   | _ | _   | _   | _ | _ | 1      | 2      |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |             | E2            | _   | * | *   | 0   | _ | - | 2      | 2      |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |             | E2            | _   | * | *   | 0   | _ | _ | 2      | 2      |

| BRK              | Debugger Break                                                                            |     |             | 00            | _   | - | -   | _   | - | - | 1      | 1      |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |             | E2            | -   | * | *   | 0   | - | - | 2      | 2      |

| BSWAP dst        | dst[7:0] ← dst[0:7]                                                                       | R   |             | D5            | Х   | * | *   | 0   | - | - | 2      | 2      |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r           | F6            |     | - | -   | -   | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            |     |   |     |     |   |   | 3      | 4      |

| BTJNZ bit, src,  |                                                                                           |     | r           | F6            |     | - | -   | -   | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            |     |   |     |     |   |   | 3      | 4      |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r           | F6            | -   | - | -   | —   | - | - | 3      | 3      |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr          | F7            |     |   |     |     |   |   | 3      | 4      |

| CALL dst         | $SP \leftarrow SP - 2$                                                                    | IRR |             | D4            | -   | _ | -   | _   | _ | - | 2      | 6      |

|                  |                                                                                           | DA  |             | D6            | -   |   |     |     |   |   | 3      | 3      |

| CCF              | $C \leftarrow -C$                                                                         |     |             | EF            | *   | — | _   | -   | - |   | 1      | 2      |

## Table 186. eZ8 CPU Instruction Summary (Continued)

Flags notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

337

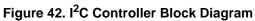

The currents in Table 190 represent the power consumption without any peripherals active (unless otherwise noted). For design guidance, total power consumption will be the sum of all active peripheral currents plus the appropriate current characteristics shown below.

| T <sub>A</sub> = 0°C to +70°C<br>T <sub>A</sub> = -40°C to +105°C |                                                       |     |                      |     |       |                                                                                                                    |  |  |

|-------------------------------------------------------------------|-------------------------------------------------------|-----|----------------------|-----|-------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                                                            | Parameter                                             | Min | Typical <sup>1</sup> | Max | Units | Conditions <sup>2</sup>                                                                                            |  |  |

| I <sub>DDA1</sub>                                                 | Active Mode Device<br>Current Executing from<br>Flash |     | 8.5                  |     | mA    | Typical: 20MHz <sup>3, 4, 5, 6</sup> ,<br>V <sub>DD</sub> = 3V, Flash, 25°C                                        |  |  |

| I <sub>DDA2</sub>                                                 | Active Mode Device<br>Current Executing from<br>PRAM  |     | 6                    |     | mA    | Typical: 20MHz <sup>3, 4, 5, 6</sup> ,<br>V <sub>DD</sub> = 3V, PRAM, 25°C                                         |  |  |

| I <sub>DDH</sub>                                                  | Halt Mode Device Current                              |     | TBD                  |     | mA    | Typical: 20MHz <sup>3, 4, 5</sup> , V <sub>DD</sub><br>typical, 25°C                                               |  |  |

| I <sub>DDS1</sub>                                                 | Stop Mode Device Current                              |     | 2.5                  |     | μA    | Typical: WDT, V <sub>DD</sub> typical,<br>25 °C, all peripherals<br>including VBO disabled <sup>3, 4, 6</sup>      |  |  |

| I <sub>DDS2</sub>                                                 | Stop Mode Device Current                              |     | <1                   |     | μA    | Typical: V <sub>DD</sub> typical, 25°C,<br>all peripherals disabled<br>including VBO and<br>WDT <sup>3, 4, 6</sup> |  |  |

### Table 190. Supply Current Characteristics

Notes

1. These values are provided for design guidance only and are not tested in production.

2. Typical conditions are defined as 3.3 V at 25°C, unless otherwise noted.

3. All internal pull ups are disabled and all push-pull outputs are unloaded.

4. All open-drain outputs are pulled up to  $V_{DD}/AV_{DD}$  and are at a High state.

5. System clock source is an external square wave clock signal driven through the CLK-IN pin.

6. All inputs are at  $V_{DD}/AV_{DD}$  or  $V_{SS}/AV_{SS}$  as appropriate.

Figure 73 displays the STOP Mode supply current versus ambient temperature and  $V_{DD}$  level with all peripherals disabled.

## Idd Stop Current vs. Vdd with Temperature

Figure 73. STOP Mode Current Consumption as a Function of  $V_{DD}$  with Temperature as a Parameter; all Peripherals Disabled

356

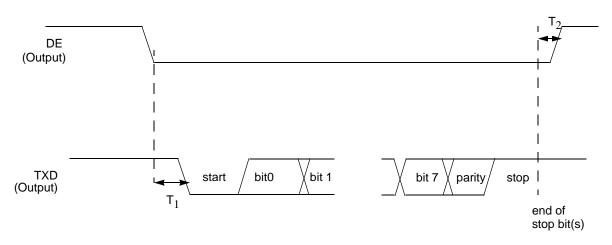

| Table 208. UART T | iming Without CTS |

|-------------------|-------------------|

|-------------------|-------------------|

| Parameter Abbreviation |                                                                        | Delay (ns)                    |            |

|------------------------|------------------------------------------------------------------------|-------------------------------|------------|

|                        | Abbreviation                                                           | Min                           | Мах        |

| UART                   |                                                                        |                               |            |

| T <sub>1</sub>         | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub><br>period | 1 bit time |

| T <sub>2</sub>         | End of stop bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                           |            |

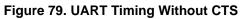

# 31.1. Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F1680SH020SG is an 8-bit, 20MHz Flash Motor Controller with 16KB of Program memory in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

377

# Index

## Numerics

10-bit ADC 4

## Α

absolute maximum ratings 349 AC characteristics 357 ADC 332 block diagram 187 electrical characteristics and timing 360 overview 186 ADC Channel Register 1 (ADCCTL) 189 ADC Data High Byte Register (ADCDH) 191 ADC Data Low Bit Register (ADCDL) 192, 193, 194.195 **ADCX 332** ADD 332 add - extended addressing 332 add with carry 332 add with carry - extended addressing 332 additional symbols 331 address space 19 **ADDX 332** analog block/PWM signal synchronization 188 analog signals 15 analog-to-digital converter overview 186 AND 334 **ANDX 334** architecture voltage measurements 186 arithmetic instructions 332 assembly language syntax 329

## В

B 331 b 330 baud rate generator, UART 160 BCLR 333 binary number suffix 331 BIT 333 bit 330 clear 333 manipulation instructions 333 set 333 set or clear 333 swap 333 test and jump 335 test and jump if non-zero 335 test and jump if zero 335 bit jump and test if non-zero 335 bit swap 335 block diagram 3 block transfer instructions 333 **BRK 335 BSET 333** BSWAP 333, 335 **BTJ 335** BTJNZ 335 **BTJZ 335**

## С

calibration and compensation, motor control measurements 189 CALL procedure 335 capture mode 114, 115 capture/compare mode 114 cc 330 CCF 333 characteristics, electrical 349 clear 334 clock phase (SPI) 201 **CLR 334 COM 334** compare - extended addressing 332 compare with carry 332 compare with carry - extended addressing 332 complement 334 complement carry flag 333 condition code 330 control register definition, UART 163