Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I²C, IrDA, LINbus, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 24KB (24K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2480ph020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

need to use this on-chip Program RAM to shadow Interrupt Service Routines (ISR). For details, see the <u>PRAM\_M</u> section on page 278.

# 3.2. Program Memory

The eZ8 CPU supports 64KB of Program Memory address space. The F1680 Series MCU contains 8KB to 24KB of on-chip Flash memory in the Program Memory address space, depending on the device.

In addition, the F1680 Series MCU contains up to 1 KB of on-chip Program RAM. The Program RAM is mapped in the Program Memory address space beyond the on-chip Flash memory. The Program RAM is entirely under user control and is meant to store interrupt service routines of high-frequency interrupts. Since interrupts bring the CPU out of low-power mode, it is important to ensure that interrupts that occur very often use as low a current as possible. For battery operated systems, Program RAM based handling of high-frequency interrupts provides power savings by keeping the Flash block disabled. Program RAM (PRAM) is optimized for low-current operation and can be easily boot-strapped with interrupt code at power up.

Reading from Program Memory addresses present outside the available Flash memory and PRAM addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the F1680 Series MCU.

| Program Memory<br>Address (Hex) | Function                        |  |  |

|---------------------------------|---------------------------------|--|--|

| Z8F2480 Device                  |                                 |  |  |

| 0000–0001                       | Flash option bits               |  |  |

| 0002–0003                       | Reset vector                    |  |  |

| 0004–0005                       | WDT interrupt vector            |  |  |

| 0006–0007                       | Illegal instruction trap        |  |  |

| 0008–0037                       | Interrupt vectors*              |  |  |

| 0038–003D                       | Oscillator fail traps*          |  |  |

| 003E-5FFF                       | Program Flash                   |  |  |

| E000–E3FF                       | 1KB PRAM                        |  |  |

|                                 | on page 69 for a list of inter- |  |  |

| rupt vectors and                | traps.                          |  |  |

#### Table 6. F1680 Series MCU Program Memory Maps

|               | <b>C</b>                                   | , ,           |                          |            |

|---------------|--------------------------------------------|---------------|--------------------------|------------|

| Address (Hex) | Register Description                       | Mnemonic      | Reset (Hex) <sup>1</sup> | Page #     |

| F17           | Timer 2 Control 1                          | T2CTL1        | 00                       | <u>113</u> |

| F28           | Timer 2 PWM1 High Byte                     | T2PWM1H       | 00                       | <u>111</u> |

| F29           | Timer 2 PWM1 Low Byte                      | T2PWM1L       | 00                       | <u>111</u> |

| F2A           | Timer 2 Control 2                          | T2CTL2        | 00                       | <u>117</u> |

| F2B           | Timer 2 Status                             | T2STA         | 00                       | <u>118</u> |

| F2E           | Timer 2 Noise Filter Control               | T2NFC         | 00                       | <u>119</u> |

| F2F–F3F       | Reserved                                   | —             | XX                       |            |

| LIN UART 0    |                                            |               |                          |            |

| F40           | LIN UART0 Transmit Data                    | U0TXD         | XX                       | <u>163</u> |

|               | LIN UART0 Receive Data                     | U0RXD         | XX                       | <u>164</u> |

| F41           | LIN UART0 Status 0—Standard UART Mode      | U0STAT0       | 0000011Xb                | <u>165</u> |

|               | LIN UART0 Status 0—LIN Mode                | U0STAT0       | 00000110b                | <u>166</u> |

| F42           | LIN UART0 Control 0                        | U0CTL0        | 00                       | <u>170</u> |

| F43           | LIN UART0 Control 1—Multiprocessor Control | U0CTL1        | 00                       | <u>172</u> |

|               | LIN UART0 Control 1—Noise Filter Control   | U0CTL1        | 00                       | <u>174</u> |

|               | LIN UART0 Control 1—LIN Control            | U0CTL1        | 00                       | <u>175</u> |

| F44           | LIN UART0 Mode Select and Status           | U0MDSTAT      | 00                       | <u>168</u> |

| F45           | UART0 Address Compare                      | <b>U0ADDR</b> | 00                       | <u>177</u> |

| F46           | UART0 Baud Rate High Byte                  | U0BRH         | FF                       | <u>177</u> |

| F47           | UART0 Baud Rate Low Byte                   | U0BRL         | FF                       | <u>178</u> |

| LIN UART 1    |                                            |               |                          |            |

| F48           | LIN UART1 Transmit Data                    | U1TXD         | XX                       | <u>163</u> |

|               | LIN UART1 Receive Data                     | U1RXD         | XX                       | <u>164</u> |

| F49           | LIN UART1 Status 0—Standard UART Mode      | U1STAT0       | 0000011Xb                | <u>165</u> |

|               | LIN UART1 Status 0—LIN Mode                | U1STAT0       | 00000110b                | <u>166</u> |

| F4A           | LIN UART1 Control 0 U1CTL0 00 <u>1</u>     |               |                          |            |

| Notoo         |                                            |               |                          |            |

#### Table 8. Register File Address Map (Continued)

Notes:

1. XX=Undefined.

2. The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM.

| Port   | Pin | Mnemonic   | Alternate Function Description          | Alternate<br>Function Set<br>Register AFS1 |

|--------|-----|------------|-----------------------------------------|--------------------------------------------|

| Port A | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | AFS1[0]: 0                                 |

|        |     | Reserved   |                                         | AFS1[0]: 1                                 |

|        | PA1 | TOOUT      | Timer 0 Output                          | AFS1[1]: 0                                 |

|        |     | Reserved   |                                         | AFS1[1]: 1                                 |

|        | PA2 | DE0        | UART 0 Driver Enable                    | AFS1[2]: 0                                 |

|        |     | Reserved   |                                         | AFS1[2]: 1                                 |

|        | PA3 | CTS0       | UART 0 Clear to Send                    | AFS1[3]: 0                                 |

|        |     | Reserved   |                                         | AFS1[3]: 1                                 |

|        | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | AFS1[4]: 0                                 |

|        |     |            |                                         | AFS1[4]: 1                                 |

|        | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | AFS1[5]: 0                                 |

|        |     |            |                                         | AFS1[5]: 1                                 |

|        | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | AFS1[6]: 0                                 |

|        |     | Reserved   |                                         | AFS1[6]: 1                                 |

|        | PA7 | T1OUT      | Timer 1 Output                          | AFS1[7]: 0                                 |

|        |     | Reserved   |                                         | AFS1[7]: 1                                 |

#### Table 19. Port Alternate Function Mapping, 40-/44-Pin Parts<sup>1,2</sup>

Notes:

Because there are at most two choices of alternate functions for some pins in Ports A–C, the Alternate Function Set Register (AFS2) is implemented but not used to select the function. The alternate function selection must also be enabled, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

Because there is only one alternate function for each Port D and Port E pin, the Alternate Function Set registers are not implemented for Ports D and E. Enabling the alternate function selections automatically enables the associated alternate function, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

3. This timer function is only available in the 44-pin package; its alternate functions are reserved in the 40-pin package.

| Port   | Pin | Mnemonic           | Alternate Function Description                 | Alternate<br>Function Set<br>Register AFS1 |

|--------|-----|--------------------|------------------------------------------------|--------------------------------------------|

| Port D | PD0 | RESET              | External Reset                                 | N/A                                        |

|        | PD1 | C1INN              | Comparator 1 Input (N)                         |                                            |

|        | PD2 | C1INP              | Comparator 1 Input (P)                         |                                            |

|        | PD3 | CTS1/C1OUT         | UART 1 Clear to Send or Comparator 1<br>Output |                                            |

|        | PD4 | RXD1/IRRX1         | UART 1/IrDA 1 Receive Data                     |                                            |

|        | PD5 | TXD1/IRTX1         | UART 1/IrDA 1 Transmit Data                    |                                            |

|        | PD6 | DE1                | UART 1 Driver Enable                           |                                            |

|        | PD7 | COOUT              | Comparator 0 Output                            |                                            |

| Port E | PE0 | T4IN <sup>3</sup>  |                                                | N/A                                        |

|        |     | Reserved           |                                                |                                            |

|        | PE1 | SCL                | I <sup>2</sup> C Serial Clock                  |                                            |

|        |     | Reserved           |                                                |                                            |

|        | PE2 | SDA                | I <sup>2</sup> C Serial Data                   |                                            |

|        |     | Reserved           |                                                |                                            |

|        | PE3 | T4CHA <sup>3</sup> |                                                |                                            |

|        |     | Reserved           |                                                |                                            |

|        | PE4 | T4CHB <sup>3</sup> |                                                |                                            |

|        |     | Reserved           |                                                |                                            |

|        | PE5 | T4CHC <sup>3</sup> |                                                |                                            |

|        |     | Reserved           |                                                |                                            |

|        | PE6 | T4CHD <sup>3</sup> |                                                |                                            |

|        |     | Reserved           |                                                |                                            |

### Table 19. Port Alternate Function Mapping, 40-/44-Pin Parts<sup>1,2</sup> (Continued)

Notes:

- Because there are at most two choices of alternate functions for some pins in Ports A–C, the Alternate Function Set Register (AFS2) is implemented but not used to select the function. The alternate function selection must also be enabled, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

- Because there is only one alternate function for each Port D and Port E pin, the Alternate Function Set registers are not implemented for Ports D and E. Enabling the alternate function selections automatically enables the associated alternate function, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

- 3. This timer function is only available in the 44-pin package; its alternate functions are reserved in the 40-pin package.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### 8.3.4. Software Interrupt Assertion

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that the interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### 8.4. Interrupt Control Register Definitions

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap and the Watchdog Oscillator Fail Trap, the Interrupt Control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests. Table 54 provides an example initialization sequence for configuring Timer 0 in DEMOD-ULATION Mode and initiating operation.

| Register   | Value | Comment                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T0CTL0     | C0H   | TMODE[3:0] = 1100B selects DEMODULATION Mode.                                                                                                                                                                                                                                                                                                                                                                                   |

| T0CTL1     | 04H   | TICONFIG[1:0] = $10B$ enables interrupt only on Capture events.                                                                                                                                                                                                                                                                                                                                                                 |

| T0CTL2     | 11H   | <ul> <li>CSC = 0 selects the Timer Input from the GPIO pin.</li> <li>PWMD[2:0] = 000B has no effect.</li> <li>INPCAP = 0 has no effect.</li> <li>TEN = 0 disables the timer.</li> <li>PRES[2:0] = 000B sets prescaler to divide by 1.</li> <li>TPOLHI,TPOL = 10 enables trigger and Capture on both rising and falling edges of Timer Input.</li> <li>TCLKS = 1 enables 32kHz peripheral clock as timer clock source</li> </ul> |

| ТОН        | 00H   | Timer starting value = 0001H.                                                                                                                                                                                                                                                                                                                                                                                                   |

| TOL        | 01H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TORH       | ABH   | Timer reload value = ABCDH                                                                                                                                                                                                                                                                                                                                                                                                      |

| TORL       | CDH   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TOPWMOH    | 00H   | Initial PWM0 value = 0000H                                                                                                                                                                                                                                                                                                                                                                                                      |

| TOPWMOL    | 00H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T0PWM1H    | 00H   | Initial PWM1 value = 0000H                                                                                                                                                                                                                                                                                                                                                                                                      |

| T0PWM1H    | 00H   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TONFC      | C0H   | NFEN = 1 enables noise filter<br>NFCTL = 100B enables 8-bit up/down counter                                                                                                                                                                                                                                                                                                                                                     |

| PAADDR     | 02H   | Selects Port A Alternate Function control register.                                                                                                                                                                                                                                                                                                                                                                             |

| PACTL[1:0] | 11B   | PACTL[0] enables Timer 0 Input alternate function.<br>PACTL[1] enables Timer 0 Output alternate function.                                                                                                                                                                                                                                                                                                                       |

| IRQ0ENH[5] | 0B    | Disables the Timer 0 interrupt.                                                                                                                                                                                                                                                                                                                                                                                                 |

| IRQ0ENL[5] | 0B    |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T0CTL1     | 84H   | TEN = 1 enables the timer. All other bits remain in their appropriate settings.                                                                                                                                                                                                                                                                                                                                                 |

| Notes:     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 54. DEMODULATION Mode Initialization Example

Notes: After receiving the input trigger (rising or falling edge), Timer 0 will:

1. Start counting on the timer clock.

2. Upon receiving a Timer 0 Input rising edge, save the Capture value in the T0PWM0 registers, generate an interrupt, and continue to count.

3. Upon receiving a Timer 0 Input falling edge, save the Capture value in the T0PWM1 registers, generate an interrupt, and continue to count.

4. After the timer count to ABCD clocks, set the reload event flag and reset the Timer count to the start value.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:1]<br>PWMD | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of timer clock cycles time delay before the Timer Output and the Timer Output Complement is forced to their active state.<br>000 = No delay<br>001 = 2 cycles delay<br>010 = 4 cycles delay<br>011 = 8 cycles delay<br>100 = 16 cycles delay<br>101 = 32 cycles delay<br>110 = 64 cycles delay |

|               | 111 = 128 cycles delay                                                                                                                                                                                                                                                                                                                                                            |

| [0]<br>INPCAP | Input Capture Event<br>This bit indicates if the last timer interrupt is due to a Timer Input Capture Event.<br>0 = Previous timer interrupt is not a result of Timer Input Capture Event.<br>1 = Previous timer interrupt is a result of Timer Input Capture Event.                                                                                                              |

## 9.3.5.2. Timer 0–2 Control 1 Register

The Timer 0–2 Control 1 (TxCTL1) registers enable and disable the timers, set the prescaler value and determine the timer operating mode. See Table 64.

| Bit     | 7                | 6    | 5   | 4    | 3   | 2     | 1   | 0   |  |

|---------|------------------|------|-----|------|-----|-------|-----|-----|--|

| Field   | TEN              | TPOL |     | PRES |     | TMODE |     |     |  |

| Reset   | 0                | 0    | 0   | 0    | 0   | 0     | 0   | 0   |  |

| R/W     | R/W              | R/W  | R/W | R/W  | R/W | R/W   | R/W | R/W |  |

| Address | F07H, F0FH, F17H |      |     |      |     |       |     |     |  |

#### Table 64. Timer 0–2 Control 1 Register (TxCTL1)

BitDescription[7]Timer Enable

TEN

0 = Timer is disabled.

1 = Timer enabled to count.

113

| Bit              | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:3]            | Prescale Value                                                                                                                                                                                                                                                                                                                                                                              |

| PRES             | The timer input clock is divided by 2PRES, where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This insures proper clock division each time the Timer is restarted.<br>000 = Divide by 1<br>001 = Divide by 2<br>010 = Divide by 4<br>011 = Divide by 8                                                                                              |

|                  | 100 = Divide by 16                                                                                                                                                                                                                                                                                                                                                                          |

|                  | 101 = Divide by 32<br>110 = Divide by 64                                                                                                                                                                                                                                                                                                                                                    |

|                  | 111 = Divide by  128                                                                                                                                                                                                                                                                                                                                                                        |

| [2:0]<br>TMODE[2 | Timer Mode<br>1:0] This field, along with the TMODE[3] bit in the TxCTL0 Register, determines the operating<br>mode of the timer. TMODE[3:0] selects among the following modes:<br>0000 = ONE-SHOT Mode<br>0001 = CONTINUOUS Mode<br>0010 = COUNTER Mode<br>0011 = PWM SINGLE OUTPUT Mode<br>0100 = CAPTURE Mode<br>0101 = COMPARE Mode<br>0110 = GATED Mode<br>0111 = CAPTURE/COMPARE Mode |

|                  | 1000 = PWM DUAL OUTPUT Mode<br>1001 = CAPTURE RESTART Mode<br>1010 = COMPARATOR COUNTER Mode                                                                                                                                                                                                                                                                                                |

|                  | 1011 = TRIGGERED ONE-SHOT Mode<br>1100 = DEMODULATION Mode                                                                                                                                                                                                                                                                                                                                  |

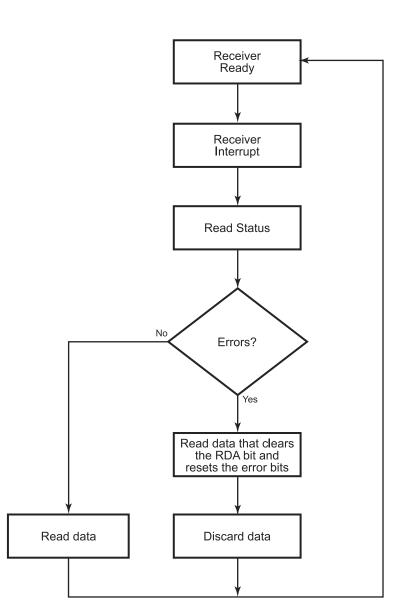

Figure 24. LIN-UART Receiver Interrupt Service Routine Flow

### 12.1.11.5. Baud Rate Generator Interrupts

If the BRGCTL bit of the Multiprocessor Control Register (LIN-UART Control 1 Register with MSEL = 000b) is set and the REN bit of the Control 0 Register is 0. The LIN-UART Receiver interrupt asserts when the LIN-UART Baud Rate Generator reloads. This action allows the Baud Rate Generator to function as an additional counter, if the LIN-UART receiver functionality is not employed. The transmitter can be enabled in this mode.

159

the  $V_{REF}$  pin. When RBUF is disabled, the ADC must have the reference voltage supplied externally through the  $V_{REF}$  pin. RBUF is controlled by the REFEN bit in the ADC Control Register.

# 14.2.4. Internal Voltage Reference Generator

The Internal Voltage Reference Generator provides the voltage, VR2, for the RBUF. VR2 is 1.6V.

## 14.2.5. Calibration and Compensation

You can calibrate and store the values into Flash, or the user code can perform a manual offset calibration. There is no provision for manual gain calibration.

# 14.3. ADC Control Register Definitions

The registers that control analog-to-digital conversion functions are defined in this section.

# 14.3.1. ADC Control Register 0

The ADC Control Register 0, shown in Table 101, initiates the A/D conversion and provides ADC status information.

| Bits    | 7     | 6          | 5     | 4     | 3          | 2   | 1   | 0   |

|---------|-------|------------|-------|-------|------------|-----|-----|-----|

| Field   | START | INTREF_SEL | REFEN | ADCEN | ANAIN[3:0] |     |     |     |

| Reset   | 0     | 0          | 0     | 0     | 0          | 0   | 0   | 0   |

| R/W     | R/W1  | R/W        | R/W   | R/W   | R/W        | R/W | R/W | R/W |

| Address | F70h  |            |       |       |            |     |     |     |

| Bit Position | Value<br>(H) | Description                                                                                           |

|--------------|--------------|-------------------------------------------------------------------------------------------------------|

| [7]<br>START | 0            | ADC Start/Busy<br>Writing a 0 has no effect.                                                          |

|              |              | Reading a 0 indicates the ADC is available to begin a conversion.                                     |

|              | 1            | Writing a 1 starts a conversion.<br>Reading a 1 indicates that a conversion is currently in progress. |

| [6]          | 0            | Select 1.6 V as internal reference.                                                                   |

| INTREF_SEL   | 1            | Select AVDD as internal reference.                                                                    |

11. The I<sup>2</sup>C slave sends an Acknowledge (by pulling the SDA signal Low) during the next High period of SCL. The I<sup>2</sup>C controller sets the ACK bit in the I<sup>2</sup>C Status Register.

If the slave does not acknowledge the address byte, the I<sup>2</sup>C controller sets the NCKI bit in the I<sup>2</sup>C Status Register, sets the ACKV bit and clears the ACK bit in the I<sup>2</sup>C State Register. The software responds to the Not Acknowledge interrupt by setting the stop bit and clearing the TXI bit. The I<sup>2</sup>C controller flushes the Transmit Data Register, sends a stop condition on the bus and clears the stop and NCKI bits. The transaction is complete and the following steps can be ignored.

- 12. The I<sup>2</sup>C controller loads the contents of the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C controller shifts the data out via the SDA signal. After the first bit is sent, the transmit interrupt asserts.

- 14. If more bytes remain to be sent, return to <u>Step 9</u>.

- 15. When there is no more data to be sent, the software responds by setting the stop bit of the I<sup>2</sup>C Control Register (or the start bit to initiate a new transaction).

- 16. If no additional transaction is queued by the master, the software can clear the TXI bit of the I<sup>2</sup>C Control Register.

- 17. The  $I^2C$  controller completes transmission of the data on the SDA signal.

- 18. The  $I^2C$  controller sends a stop condition to the  $I^2C$  bus.

▶ Note: If the slave terminates the transaction early by responding with a Not Acknowledge during the transfer, the I<sup>2</sup>C controller asserts the NCKI interrupt and halts. The software must terminate the transaction by setting either the stop bit (end transaction) or the start bit (end this transaction, start a new one). In this case, it is not necessary for software to set the FLUSH bit of the I2CCTL Register to flush the data that was previously written but not transmitted. The I<sup>2</sup>C controller hardware automatically flushes transmit data in the not acknowledge case.

#### 17.2.5.5. Master Write Transaction with a 10-Bit Address

Figure 44 displays the data transfer format from a Master to a 10-bit addressed slave.

| S | Slave Address<br>1st Byte | W = 0 | А | Slave Address<br>2nd Byte | А | Data | A | Data | A/Ā | F/S |  |

|---|---------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|--|

|---|---------------------------|-------|---|---------------------------|---|------|---|------|-----|-----|--|

Figure 44. Data Transfer Format—Master Write Transaction with a 10-Bit Address

- 14. The software responds by writing the data to be written out to the I<sup>2</sup>C Control Register.

- 15. The I<sup>2</sup>C controller shifts out the remainder of the second byte of the slave address (or ensuring data bytes, if looping) via the SDA signal.

- 16. The I<sup>2</sup>C slave sends an Acknowledge by pulling the SDA signal Low during the next High period of SCL. The I<sup>2</sup>C controller sets the ACK bit in the I<sup>2</sup>C Status Register. If the slave does not acknowledge, see the second paragraph of <u>Step 11</u>.

- 17. The I<sup>2</sup>C controller shifts the data out by the SDA signal. After the first bit is sent, the transmit interrupt asserts.

- 18. If more bytes remain to be sent, return to <u>Step 14</u>.

- 19. The software responds by asserting the stop bit of the  $I^2C$  Control Register.

- 20. The  $I^2C$  controller completes transmission of the data on the SDA signal.

- 21. The  $I^2C$  controller sends a stop condition to the  $I^2C$  bus.

**Note:** If the slave responds with a Not Acknowledge during the transfer, the  $I^2C$  controller asserts the NCKI bit, sets the ACKV bit, clears the ACK bit in the  $I^2C$  State Register and halts. The software terminates the transaction by setting either the stop bit (end transaction) or the start bit (end this transaction, start a new one). The Transmit Data Register is flushed automatically.

### 17.2.5.6. Master Read Transaction with a 7-Bit Address

Figure 45 displays the data transfer format for a Read operation to a 7-bit addressed slave.

| S | Slave Address | R = 1 | А | Data | А | Data | А | P/S |

|---|---------------|-------|---|------|---|------|---|-----|

|---|---------------|-------|---|------|---|------|---|-----|

#### Figure 45. Data Transfer Format—Master Read Transaction with a 7-Bit Address

Observe the following steps for a Master Read operation to a 7-bit addressed slave:

- The software initializes the MODE field in the I<sup>2</sup>C Mode Register for MASTER/ SLAVE Mode with 7- or 10-bit addressing (the I<sup>2</sup>C bus protocol allows the mixing of slave address types). The MODE field selects the address width for this mode when addressed as a slave (but not for the remote slave). The software asserts the IEN bit in the I<sup>2</sup>C Control Register.

- 2. The software writes the I<sup>2</sup>C Data Register with a 7-bit slave address, plus the Read bit (which is set to 1).

- 3. The software asserts the start bit of the  $I^2C$  Control Register.

# 17.3.2. I<sup>2</sup>C Interrupt Status Register

The read-only  $I^2C$  Interrupt Status Register, shown in Table 120, indicates the cause of any current  $I^2C$  interrupt and provides status of the  $I^2C$  controller. When an interrupt occurs, one or more of the TDRE, RDRF, SAM, ARBLST, SPRS or NCKI bits is set. The GCA and RD bits do not generate an interrupt but rather provide status associated with the SAM bit interrupt.

| Bits        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                               | 3                              | 2                               | 1                               | 0                           |  |  |  |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------|---------------------------------|---------------------------------|-----------------------------|--|--|--|--|--|--|--|--|

| Field       | TDRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RDRF                                                                                                                                                                                                                                                                                                                                                                                                      | SAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GCA                                                             | RD                             | ARBLST                          | SPRS                            | NCKI                        |  |  |  |  |  |  |  |  |

| Reset       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                               | 0                              | 0                               | 0                               | 0                           |  |  |  |  |  |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R                                                               | R                              | R                               | R                               | R                           |  |  |  |  |  |  |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F5                                                              | 1H                             |                                 |                                 |                             |  |  |  |  |  |  |  |  |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                |                                 |                                 |                             |  |  |  |  |  |  |  |  |

| [7]<br>TDRE | When the l <sup>2</sup> this bit caus shifting in d                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Transmit Data Register Empty</b><br>When the $I^2C$ controller is enabled, this bit is 1 when the $I^2C$ Data Register is empty. When set, this bit causes the $I^2C$ controller to generate an interrupt, except when the $I^2C$ controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit clears by writing to the I2CDATA Register. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                |                                 |                                 |                             |  |  |  |  |  |  |  |  |

| [6]<br>RDRF | <b>Receive Data Register Full</b><br>This bit is set = 1 when the $l^2C$ controller is enabled and the $l^2C$ controller has received a byte of data. When asserted, this bit causes the $l^2C$ controller to generate an interrupt. This bit clears by reading the I2CDATA Register.                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                |                                 |                                 |                             |  |  |  |  |  |  |  |  |

| [5]<br>SAM  | This bit is s<br>that matche<br>the I <sup>2</sup> C Mod<br>on both add                                                                                                                                                                                                                                                                                                                                                                                                                                     | es the uniqued                                                                                                                                                                                                                                                                                                                                                                                            | e slave addr<br>. In 10-bit ac<br>When this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | er is enablec<br>ess or Gene<br>ddressing mo<br>bit is set, the | eral Call Add<br>ode, this bit | lress (if enal<br>is not set ur | bled by the (<br>htil a match i | GCE bit in<br>s achieved    |  |  |  |  |  |  |  |  |

| [4]<br>GCA  | <b>General Call Address</b><br>This bit is set in SLAVE Mode when the General Call Address or Start byte is recognized (in either 7 or 10 bit SLAVE Mode). The GCE bit in the $I^2C$ Mode Register must be set to enable recognition of the General Call Address and Start byte. This bit clears when IEN = 0 and is updated following the first address byte of each SLAVE Mode transaction. A General Call Address is distinguished from a Start byte by the value of the RD bit (RD = 0 for General Call |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                |                                 |                                 |                             |  |  |  |  |  |  |  |  |