# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | I²C, IrDA, LINbus, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 24KB (24K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 3K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f2480sh020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

| Table 178. | Arithmetic Instructions                                                       |

|------------|-------------------------------------------------------------------------------|

| Table 179. | Bit Manipulation Instructions 333                                             |

| Table 180. | Block Transfer Instructions 333                                               |

| Table 181. | CPU Control Instructions                                                      |

| Table 182. | Logical Instructions                                                          |

| Table 183. | Load Instructions                                                             |

| Table 184. | Program Control Instructions 335                                              |

| Table 185. | Rotate and Shift Instructions                                                 |

| Table 186. | eZ8 CPU Instruction Summary 336                                               |

| Table 187. | Op Code Map Abbreviations 346                                                 |

| Table 188. | Absolute Maximum Ratings* 349                                                 |

| Table 189. | DC Characteristics                                                            |

| Table 190. | Supply Current Characteristics                                                |

| Table 191. | AC Characteristics                                                            |

| Table 192. | Power-On Reset and Voltage Brown-Out Electrical Characteristics<br>and Timing |

| Table 193. | Flash Memory Electrical Characteristics and Timing 359                        |

| Table 194. | Watchdog Timer Electrical Characteristics and Timing 359                      |

| Table 195. | Non-Volatile Data Storage 359                                                 |

| Table 196. | Analog-to-Digital Converter Electrical Characteristics and Timing 360         |

| Table 197. | Comparator Electrical Characteristics                                         |

| Table 198. | Temperature Sensor Electrical Characteristics                                 |

| Table 199. | Low Power Operational Amplifier Characteristics                               |

| Table 200. | IPO Electrical Characteristics                                                |

| Table 201. | Low Voltage Detect Electrical Characteristics                                 |

| Table 202. | Crystal Oscillator Characteristics                                            |

| Table 203. | Low Power 32kHz Secondary Oscillator Characteristics                          |

| Table 204. | GPIO Port Input Timing                                                        |

| Table 205. | GPIO Port Output Timing                                                       |

| Table 206. | On-Chip Debugger Timing 368                                                   |

| Table 207. | UART Timing with CTS                                                          |

### xxiv

|                 | Table 0. Negister The Address Ma |          |                          |            |

|-----------------|----------------------------------|----------|--------------------------|------------|

| Address (Hex)   | Register Description             | Mnemonic | Reset (Hex) <sup>1</sup> | Page #     |

| Multi-Channel   | Timer                            |          |                          |            |

| FA0             | MCT High Byte                    | MCTH     | 00                       | <u>130</u> |

| FA1             | MCT Low Byte                     | MCTL     | 00                       | <u>130</u> |

| FA2             | MCT Reload High Byte             | MCTRH    | FF                       | <u>131</u> |

| FA3             | MCT Reload Low Byte              | MCTRL    | FF                       | <u>131</u> |

| FA4             | MCT Subaddress                   | MCTSA    | XX                       | <u>132</u> |

| FA5             | MCT Subregister 0                | MCTSR0   | XX                       | <u>132</u> |

| FA6             | MCT Subregister 1                | MCTSR1   | XX                       | <u>132</u> |

| FA7             | MCT Subregister 2                | MCTSR2   | XX                       | <u>132</u> |

| FA8–FBF         | Reserved                         | —        | XX                       |            |

| Interrupt Contr | oller                            |          |                          |            |

| FC0             | Interrupt Request 0              | IRQ0     | 00                       | <u>73</u>  |

| FC1             | IRQ0 Enable High Bit             | IRQ0ENH  | 00                       | <u>76</u>  |

| FC2             | IRQ0 Enable Low Bit              | IRQ0ENL  | 00                       | <u>77</u>  |

| FC3             | Interrupt Request 1              | IRQ1     | 00                       | <u>74</u>  |

| FC4             | IRQ1 Enable High Bit             | IRQ1ENH  | 00                       | <u>78</u>  |

| FC5             | IRQ1 Enable Low Bit              | IRQ1ENL  | 00                       | <u>79</u>  |

| FC6             | Interrupt Request 2              | IRQ2     | 00                       | <u>75</u>  |

| FC7             | IRQ2 Enable High Bit             | IRQ2ENH  | 00                       | <u>80</u>  |

| FC8             | IRQ2 Enable Low Bit              | IRQ2ENL  | 00                       | <u>81</u>  |

| FC9–FCC         | Reserved                         | —        | XX                       |            |

| FCD             | Interrupt Edge Select            | IRQES    | 00                       | <u>82</u>  |

| FCE             | Shared Interrupt Select          | IRQSS    | 00                       | <u>82</u>  |

| FCF             | Interrupt Control                | IRQCTL   | 00                       | <u>83</u>  |

| GPIO Port A     |                                  |          |                          |            |

| FD0             | Port A Address                   | PAADDR   | 00                       | <u>58</u>  |

| FD1             | Port A Control                   | PACTL    | 00                       | <u>60</u>  |

|                 |                                  |          |                          |            |

### Table 8. Register File Address Map (Continued)

Notes:

1. XX=Undefined.

2. The Reserved space can be configured as General-Purpose Register File RAM depending on the user option bits (see the <u>User Option Bits</u> chapter on page 277) and the on-chip PRAM size (see the <u>Ordering Information</u> chapter on page 372). If the PRAM is programmed as General-Purpose Register File RAM on Reserved space, the starting address always begins immediately after the end of General-Purpose Register File RAM.

# Chapter 5. Reset, Stop Mode Recovery and Low-Voltage Detection

The Reset Controller within the F1680 Series MCU controls Reset and Stop Mode Recovery operations and provides indication of low-voltage supply conditions. During the operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO) protection

- Watchdog Timer (WDT) time-out (when configured by the WDT\_RES Flash option bit to initiate a Reset)

- External **RESET** pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by each of the following:

- Watchdog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- Interrupt from a timer or comparator enabled for STOP Mode operation

The low-voltage detection circuitry on the device features the following:

- The low-voltage detection threshold level is user-defined

- It generates an interrupt when the supply voltage drops below a user-defined level

## 5.1. Reset Types

The F1680 Series MCU provides various types of Reset operation. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The System Reset is longer, if the external crystal oscillator is enabled by the Flash option bits allowing additional time for oscillator start-up.

eZ8 CPU services the Timer interrupt request following the normal Stop Mode Recovery sequence.

### 5.3.3. Stop Mode Recovery Using Comparator Interrupt

If Comparator enabled for STOP Mode operation interrupts during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status Register, the stop bit is set to 1. If the F1680 Series MCU is configured to respond to interrupts, the eZ8 CPU services the comparator interrupt request following the normal Stop Mode Recovery sequence.

### 5.3.4. Stop Mode Recovery Using GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. In the Reset Status Register, the stop bit is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin until the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

### 5.3.5. Stop Mode Recovery Using External RESET Pin

When the F1680 Series MCU is in STOP Mode and the external  $\overrightarrow{\text{RESET}}$  pin is driven Low, a System Reset occurs. Because of a glitch filter operating on the  $\overrightarrow{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For details, see the <u>Electrical Characteristics chapter on page 349</u>.

## 5.4. Low-Voltage Detection

In addition to the VBO Reset described earlier, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. For more details about the available Low-Voltage Detection (LVD) threshold levels, see the <u>Trim Option Bits at</u> <u>Address 0000H (TTEMP0)</u> section on page 282.

When the supply voltage drops below the LVD threshold, the LVD bit of the RSTSTAT Register is set to 1. This bit remains 1 until the low-voltage condition elapses. Reading or

| Port   | Pin | Mnemonic       | Alternate Function Description                 | Alternate Function<br>Set Register AFS1 |

|--------|-----|----------------|------------------------------------------------|-----------------------------------------|

| Port C | PC0 | Reserved       |                                                | AFS1[0]: 0                              |

|        |     | ANA4/C0INP/LED | ADC or Comparator 0 Input (P), or LED drive    | AFS1[0]: 1                              |

|        | PC1 | MISO           | SPI Master In/Slave Out                        | AFS1[1]: 0                              |

|        |     | ANA5/C0INN/LED | ADC or Comparator 0 Input (N), or LED<br>Drive | AFS1[1]: 1                              |

|        | PC2 | SS             | SPI Slave Select                               | AFS1[2]: 0                              |

|        |     | ANA6/LED       | ADC Analog Input or LED Drive                  | AFS1[2]: 1                              |

|        | PC3 | COOUT          | Comparator 0 Output                            | AFS1[3]: 0                              |

|        |     | LED            | LED drive                                      | AFS1[3]: 1                              |

|        | PC4 | MOSI           | SPI Master Out/Slave In                        | AFS1[4]: 0                              |

|        |     | LED            | LED Drive                                      | AFS1[4]: 1                              |

|        | PC5 | SCK            | SPI Serial Clock                               | AFS1[5]: 0                              |

|        |     | LED            | LED Drive                                      | AFS1[5]: 1                              |

|        | PC6 | T2IN/T2OUT     | Timer 2 Input/Timer 2 Output Complement        | AFS1[6]: 0                              |

|        |     | LED            | LED Drive                                      | AFS1[6]: 1                              |

|        | PC7 | T2OUT          | Timer 2 Output                                 | AFS1[7]: 0                              |

|        |     | LED            | LED Drive                                      | AFS1[7]: 1                              |

| Port D | PD0 | RESET          | External Reset                                 | N/A                                     |

### Table 18. Port Alternate Function Mapping, 28-Pin Parts<sup>1,2</sup> (Continued)

Notes:

Because there are at most two choices of alternate functions for some pins in Ports A and B, the Alternate Function Set Register (AFS2) is implemented but not used to select the function. The alternate function selection must also be enabled, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

2. Because there is only one alternate function for each Port D and Port E pin, the Alternate Function Set registers are not implemented for Ports D and E. Enabling the alternate function selections automatically enables the associated alternate function, as described in the <u>Port A–E Alternate Function Subregisters</u> section on page 61.

## 8.4.7. Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 49, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| Bits    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| Reset   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | FCDH |      |      |      |      |      |      |      |

### Table 49. Interrupt Edge Select Register (IRQES)

| Bit          | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| [7:0]        | Interrupt Edge Select x                                                                     |

| IES <i>x</i> | 0 = An interrupt request is generated on the falling edge of the PAx input or PDx input.    |

|              | 1 = An interrupt request is generated on the rising edge of the PAx input or PDx input; $x$ |

|              | indicates the specific GPIO port pin number (0–7).                                          |

## 8.4.8. Shared Interrupt Select Register

The Shared Interrupt Select (IRQSS) Register, shown in Table 50, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

| Bits    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0        |

|---------|-------|-------|-------|-------|-------|-------|-------|----------|

| Field   | PA7VS | PA6CS | PA5CS | PAD4S | PAD3S | PAD2S | PAD1S | Reserved |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0        |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W      |

| Address | FCEH  |       |       |       |       |       |       |          |

Table 50. Shared Interrupt Select Register (IRQSS)

| Bit          | Description                                                                                                                                                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VS | <ul> <li>PA7/LVD Selection</li> <li>0 = PA7 is used for the interrupt for PA7VS interrupt request.</li> <li>1 = The LVD is used for the interrupt for PA7VS interrupt request.</li> </ul>                   |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator 0 Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator 0 is used for the interrupt for PA6CS interrupt request.</li> </ul> |

System clock is only for operation in ACTIVE and HALT modes. System clock is software selectable in Oscillator Control Module as external high-frequency crystal or internal precision oscillator. The TCLKS field in the Timer Control 2 Register selects the timer clock source.

**Caution:** When the timer is operating on a peripheral clock, the timer clock is asynchronous to the CPU clock. To ensure error-free operation, disable the timer before modifying its operation (also include changing the timer clock source). Therefore, any write to the timer control registers cannot be performed when the timer is enabled and a peripheral clock is used.

When the timer uses a peripheral clock and the timer is enabled, any read from TxH or TxL is not recommended, because the results can be unpredictable. Disable the timer first, then read it. If the timer works in the CAPTURE, CAPTURE/COMPARE, CAPTURE RESTART or DEMODULATION modes, any read from TxPWM0H, TxPWM0L, TxPWM1H, TxPWM1L or TxSTAT must be performed after a capture interrupt occurs; otherwise, results can be unpredictable. The INPCAP bit of the Timer Control 0 Register is the same as these PWM registers. When the timer uses the main clock, you can write/ read all timer registers at any time.

### 9.2.2. Low-Power Modes

Timers can operate in both HALT Mode and STOP Mode.

### 9.2.2.1. Operation in HALT Mode

When the eZ8 CPU enters HALT Mode, the timer will continue to operate if enabled. To minimize current in HALT Mode, the timer can be disabled by clearing the TEN control bit. The noise filter, if enabled, will also continue to operate in HALT Mode and rejects any noise on the timer input pin.

### 9.2.2.2. Operation in STOP Mode

When the eZ8 CPU enters STOP Mode, the timer continues to operate if enabled and peripheral clock is chosen as the clock source. In STOP Mode, the timer interrupt (if enabled) automatically initiates a Stop Mode Recovery and generates an interrupt request. In the Reset Status Register, the stop bit is set to 1. Also, timer interrupt request bit in Interrupt Request 0 register is set. Following completion of the Stop Mode Recovery, if interrupts are enabled, the CPU responds to the interrupt request by fetching the timer interrupt vector. The noise filter, if enabled, will also continue to operate in STOP Mode and rejects any noise on the timer input pin.

In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| Bit     | 7   | 6   | 5   | 4        | 3        | 2   | 1   | 0   |

|---------|-----|-----|-----|----------|----------|-----|-----|-----|

| Field   |     |     |     | TF       | RH       |     |     |     |

| Reset   | 1   | 1   | 1   | 1        | 1        | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W      | R/W      | R/W | R/W | R/W |

| Address |     |     |     | F02H, F0 | AH, F12H |     |     |     |

Table 57. Timer 0–2 Reload High Byte Register (TxRH)

| Table 58. Timer 0–2 Reload Low Byte Register (TxRL) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Bit     | 7                | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   |                  |     |     | TF  | RL  |     |     |     |

| Reset   | 1                | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W              | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F03H, F0BH, F13H |     |     |     |     |     |     |     |

| Bit         | Description                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]       | Timer Reload Register High and Low                                                                                                                                                                                             |

| TRH,<br>TRL | These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value is used to set the maximum count value which initiates a timer reload to 0001H. In COMPARE Mode, these two bytes form the 16-bit Compare value. |

### 9.3.3. Timer 0-2 PWM0 High and Low Byte Registers

The Timer 0–2 PWM0 High and Low Byte (TxPWM0H and TxPWM0L) registers, shown in Tables 59 and 60, are used for Pulse Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE, CAPTURE/COMPARE and DEMODULATION Modes. When the timer is enabled, writes to these registers are buffered, and loading of the registers is delayed until a timer reload to 0001H occurs – that is, unless PWM0UE = 1.

| Bit     | 7     | 6                | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-------|------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | PWM0H |                  |     |     |     |     |     |     |  |  |  |

| Reset   | 0     | 0                | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W   | R/W              | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |       | F04H, F0CH, F14H |     |     |     |     |     |     |  |  |  |

Table 59. Timer 0–2 PWM0 High Byte Register (TxPWM0H)

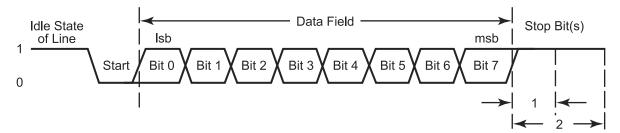

Figure 20. LIN-UART Asynchronous Data Format without Parity

Figure 21. LIN-UART Asynchronous Data Format with Parity

## 12.1.2. Transmitting Data using the Polled Method

Observe the following steps to transmit data using the polled-operating method:

- 1. Write to the LIN-UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the LIN-UART pin functions by configuring the associated GPIO port pins for alternate-function operation.

- 3. If MULTIPROCESSOR Mode is appropriate, write to the LIN-UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the MULTIPROCESSOR Mode Select bit (MPEN) to enable MULTIPROCES-SOR Mode.

- 5. Write to the LIN-UART Control 0 Register to:

- a. Set the Transmit Enable bit (TEN) to enable the LIN-UART for data transmission.

- b. If parity is appropriate and MULTIPROCESSOR Mode is not enabled, set the parity enable bit (PEN) and select either even-or-odd parity (PSEL).

- c. Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

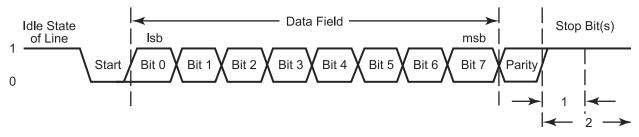

# Chapter 13. Infrared Encoder/Decoder

The Z8 Encore! XP F1680 Series products contain a fully-functional, high-performance UART to infrared encoder/decoder (endec). The infrared endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! and IrDA Physical Layer Specification and version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## 13.1. Architecture

Figure 27 displays the architecture of the infrared endec.

Figure 27. Infrared Data Communication System Block Diagram

# 13.2. Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared

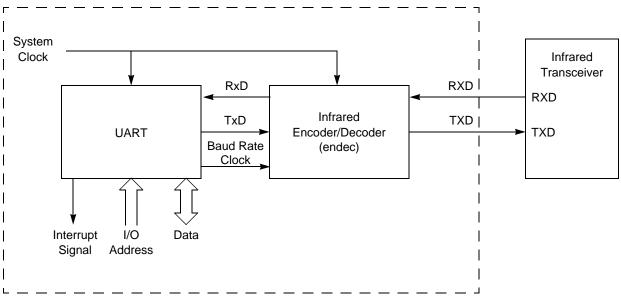

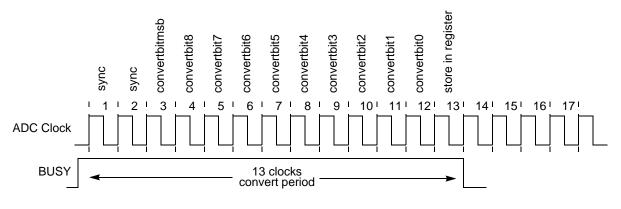

Figure 31. ADC Timing Diagram

## 14.2.2. ADC Interrupt

The ADC can generate an interrupt request when a conversion is completed. An interrupt request that is pending when the ADC is disabled is not automatically cleared. See Figure 32.

## 14.2.3. Reference Buffer

The reference buffer, RBUF, supplies the reference voltage for the ADC. When enabled, the internal voltage reference generator supplies the ADC and this voltage is available on

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>TEOF | <ul> <li>Transmit End of Frame</li> <li>This bit is used in MASTER Mode to indicate that the data in the Transmit Data Register is the last byte of the transfer or frame. When the last byte has been sent SS (and SSV) will change state and TEOF will automatically clear.</li> <li>0 = The data in the Transmit Data Register is not the last character in the message.</li> <li>1 = The data in the Transmit Data Register is the last character in the message.</li> </ul> |

| [0]<br>SSV  | Slave Select Value<br>When SSIO = 1, writes to this register will control the value output on the $\overline{SS}$ pin. For more details, see the SSMD field of the <u>ESPI Mode Register</u> on page 217.                                                                                                                                                                                                                                                                        |

## 16.4.3. ESPI Control Register

The ESPI Control Register, shown in Table 111, configures the ESPI for transmit and receive operations.

| Bits    | 7     | 6       | 5      | 4     | 3      | 2   | 1    | 0       |  |  |  |  |

|---------|-------|---------|--------|-------|--------|-----|------|---------|--|--|--|--|

| Field   | DIRQE | ESPIEN1 | BRGCTL | PHASE | CLKPOL | WOR | MMEN | ESPIEN0 |  |  |  |  |

| Reset   | 0     | 0       | 0      | 0     | 0      | 0   | 0    | 0       |  |  |  |  |

| R/W     | R/W   | R/W     | R/W    | R/W   | R/W    | R/W | R/W  | R/W     |  |  |  |  |

| Address |       | F62H    |        |       |        |     |      |         |  |  |  |  |

### Table 111. ESPI Control Register

#### Bit Description

[7] Data Interrupt Request Enable

DIRQE This bit is used to disable or enable data (TDRE and RDRNE) interrupts. Disabling the data interrupts is needed to control data transfer by polling. Error interrupts are not disabled. To block all ESPI interrupt sources, clear the ESPI interrupt enable bit in the Interrupt Controller.

0 = TDRE and RDRNE assertions do not cause an interrupt. Use this setting if controlling data transfer by software polling of TDRE and RDRNE. The TUND, COL, ABT and ROVR bits will cause an interrupt.

1 = TDRE and RDRNE assertions will cause an interrupt. TUND, COL, ABT and ROVR will also cause interrupts. Use this setting when controlling data transfer via interrupt handlers.

246

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>ARBLST | Arbitration Lost<br>This bit is set when the I <sup>2</sup> C controller is enabled in MASTER Mode and loses arbitration<br>(outputs a 1 on SDA and receives a 0 on SDA). The ARBLST bit clears when the I2CISTAT<br>Register is read.                                                                                                                                                                                                                                                                                     |

| [1]<br>SPRS   | <b>Stop/Restart Condition Interrupt</b><br>This bit is set when the I <sup>2</sup> C controller is enabled in SLAVE Mode and detects a stop or restart condition during a transaction directed to this slave. This bit clears when the I2CISTAT Register is read. Read the RSTR bit of the I2CSTATE Register to determine whether the interrupt was caused by a stop or restart condition.                                                                                                                                 |

| [0]<br>NCKI   | <b>NAK Interrupt</b><br>In MASTER Mode, this bit is set when a Not Acknowledge condition is received or sent and<br>neither the start nor the stop bit is active. In MASTER Mode, this bit can only be cleared by<br>setting the start or stop bits. In SLAVE Mode, this bit is set when a Not Acknowledge condition<br>is received (Master reading data from Slave), indicating the master is finished reading. A stop<br>or restart condition follows. In SLAVE Mode this bit clears when the I2CISTAT Register is read. |

## 23.2.6. Automatic Reset

The Z8 Encore! XP F1680 Series devices have the capability to switch clock sources during operation. If the Autobaud is set and the clock source is switched, the Autobaud value becomes invalid. A new Autobaud value must be configured with the new clock frequency.

The oscillator control logic has clock switch detection. If a clock switch is detected and the Autobaud is set, the device will automatically send a Serial Break for 4096 clocks. This will reset the Autobaud and indicate to the host that a new Autobaud character should be sent.

## 23.2.7. Transmit Flow Control

Transmit flow control is implemented by the use of a remote start bit. When transmit flow control is enabled, the transmitter will wait for the remote host to send the start bit. Transmit flow control is useful in applications where receive overruns can occur.

The remote host can transmit a remote start bit by sending the character FFH. The transmitter will append its data after the start bit. Due to the *wire-and* nature of the open drain bus, the start bit sent by the remote host and the data bits sent by the Z8 Encore! XP F1680 Series device appear as one character; see Figure 61.

| Receiving<br>Device    |      | ST                          |     |     |    |    |    |    |    |    |    |

|------------------------|------|-----------------------------|-----|-----|----|----|----|----|----|----|----|

| Transmitting<br>Device |      |                             | D0  | D1  | D2 | D3 | D4 | D5 | D6 | D7 | SP |

|                        |      |                             |     |     |    |    |    |    |    |    |    |

| Single Wire<br>Bus     |      | ST                          | D0  | D1  | D2 | D3 | D4 | D5 | D6 | D7 | SP |

|                        | SP = | = Start<br>= Stop<br>D7 = D | bit | its |    |    |    |    |    |    |    |

Figure 61. Start Bit Flow Control

## 23.2.8. Breakpoints

Execution breakpoints are generated using the BRK instruction (op code 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If breakpoints are enabled, the OCD idles the eZ8 CPU and enters DEBUG mode. If breakpoints are not

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

If breakpoints are enabled, the OCD can be configured to automatically enter DEBUG mode, or to loop on the break instruction. If the OCD is configured to loop on the BRK instruction, then the CPU remains able to service interrupt requests.

The loop on a BRK instruction can service interrupts in the background. For interrupts to be serviced in the background, there cannot be any breakpoints in the interrupt service routine. Otherwise, the CPU stops on the breakpoint in the interrupt routine. For interrupts to be serviced in the background, interrupts must also be enabled. Interrupts are typically disabled during critical sections of code where interrupts do not occur (such as adjusting the stack pointer or modifying shared data).

Through the OCD, host debugger software can poll the IDLE bit of the OCDSTAT Register to determine if the OCD is looping on a BRK instruction. When the host must stop the CPU on the BRK instruction on which it is looping, the host must not set the DBGMODE bit of the OCDCTL register. The CPU may have vectored to an interrupt service routine. Instead, the host clears the BRKLOOP bit, thereby allowing the CPU to finish the interrupt service routine and return to the BRK instruction. When the CPU returns to the BRK instruction on which it was previously looping, it automatically sets the DBGMODE bit and enters DEBUG mode.

The majority of the OCD commands remain disabled when the eZ8 CPU is looping on a BRK instruction. The eZ8 CPU must be in DEBUG mode before these commands can be issued.

### 23.2.8.1. Breakpoints in Flash Memory

The BRK instruction is op code 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the appropriate address, overwriting the current instruction. To remove a breakpoint, erase the corresponding page of Flash memory and reprogram with the original data.

### 23.2.9. OCDCNTR Register

The On-Chip Debugger contains a multipurpose 16-bit Counter Register. It can be used for the following:

- Count system clock cycles between breakpoints

- Generate a BRK when it counts down to 0

- Generate a BRK when its value matches the Program Counter

When configured as a counter, the OCDCNTR Register starts counting when the On-Chip Debugger exits DEBUG mode and stops counting when it enters DEBUG mode again or

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 1.6V but remains above the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 1.6V.

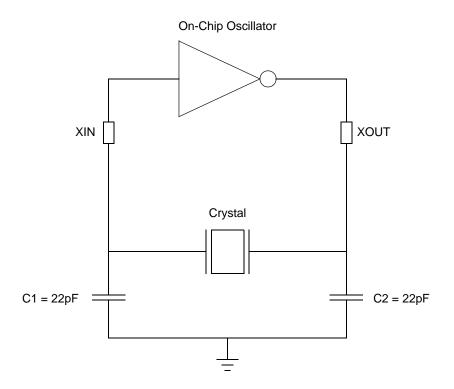

## 25.4. Secondary Crystal Oscillator Operation

Figure 65 displays the recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 32 kHz. The recommended 32 kHz crystal specifications are provided in Table 173. Printed circuit board layout must add no more than 4pF of stray capacitance to either the X<sub>IN</sub> or X<sub>OUT</sub> pins. If oscillation does not occur, reduce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

Figure 65. Recommended 32kHz Crystal Oscillator Configuration

|   |                           |                            |                              |                                |                             |                             | Lo                            | ower Nil                      | ble (He                       | x)                             |                            |                   |                           |                           |                  |                           |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|-----------------------------|-----------------------------|-------------------------------|-------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|---------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                           | 5                           | 6                             | 7                             | 8                             | 9                              | А                          | В                 | С                         | D                         | Е                | F                         |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br><b>ADD</b><br>r1,lr2    | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM          | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br><b>ADC</b><br>R2,R1  | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM          | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                   |                           |                           |                  | See 2nd<br>Op Code<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br><b>SUB</b><br>r1,lr2    | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM          | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1, 2<br>ATM               |

| 3 | 2.2<br><b>DEC</b><br>R1   | 2.3<br><b>DEC</b><br>IR1   | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br>SBC<br>R2,R1         | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM          | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                   |                           |                           |                  |                           |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br>OR<br>r1,r2           | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1   | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM    | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                   |                           |                           |                  |                           |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br><b>AND</b><br>R2,R1  | 3.4<br>AND<br>IR2,R1        | 3.3<br>AND<br>R1,IM           | 3.4<br>AND<br>IR1,IM          | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.2<br>WDT                |

| 6 | 2.2<br><b>COM</b><br>R1   | 2.3<br><b>COM</b><br>IR1   | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1  | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM   | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.2<br><b>STOP</b>        |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1   | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM    | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.2<br>HALT               |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,lrr2 | 2.9<br><b>LDEI</b><br>lr1,lrr2 | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br>LDX<br>lr1,ER2       | 3.4<br>LDX                    | 3.5<br><b>LDX</b><br>IRR2,IR1 | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br>LDX<br>rr1,r2,X         |                            |                   |                           |                           |                  | 1.2<br>DI                 |

| 9 | 2.2<br>RL<br>R1           | 2.3<br>RL<br>IR1           | 2.5<br>LDE<br>r2,lrr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1        | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br>LDX<br>IR2,IRR1        | 3.3<br>LEA<br>r1,r2,X         | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                   |                           |                           |                  | 1.2<br>El                 |

| A | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM    | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.4<br>RET                |

| В | 2.2<br><b>CLR</b><br>R1   | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM   | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.5<br>IRET               |

| С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1    | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X   | 3.2<br>PUSHX<br>ER2           |                                |                            |                   |                           |                           |                  | 1.2<br>RCF                |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6                         | 2.2<br>BSWAP<br>R1          | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X   | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                   |                           |                           |                  | 1.2<br>SCF                |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br>BIT<br>p,b,r1         | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1   | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM    | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                   |                           |                           |                  | 1.2<br>CCF                |

| F | 2.2<br>SWAP<br>R1         | 2.3<br>SWAP<br>IR1         | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br>MULT<br>RR1          | 3.3<br>LD<br>R2,IR1         | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b>             |                               | , ,                            | V                          | V                 | V                         | ▼                         | V                |                           |

### Figures 67 and 68 provide information about each of the eZ8 CPUinstructions.

Figure 67. First Op Code Map

|                      | _                                                                                        |                 | = 0°C to +7<br>–40°C to +1 |     |       |            |

|----------------------|------------------------------------------------------------------------------------------|-----------------|----------------------------|-----|-------|------------|

|                      |                                                                                          | V <sub>DI</sub> | <sub>D</sub> = 1.8 to 3.   |     |       |            |

| Symbol               | Parameter                                                                                | Min             | Тур                        | Max | Units | Conditions |

| V <sub>TH_PRO</sub>  | Detected Source Voltage for Flash<br>Protection                                          | 2.4             | 2.5                        | 2.6 | V     |            |

| T <sub>DELAY</sub>   | Delay from source voltage falling lower than $V_{TP}$ to $I_{VD\_OUT}$ output logic High | 50              | 1000                       | -   | ns    |            |

| Note: <sup>1</sup> V | TP is a user-set threshold voltage to be detected                                        | ed.             |                            |     |       |            |

### Table 201. Low Voltage Detect Electrical Characteristics (Continued)

### Table 202. Crystal Oscillator Characteristics

|                       |                                             |                               | T<br>T <sub>A</sub> |        |                                |        |        |       |                |

|-----------------------|---------------------------------------------|-------------------------------|---------------------|--------|--------------------------------|--------|--------|-------|----------------|

|                       | -                                           | V <sub>DD</sub> = 2.7 to 3.6V |                     |        | V <sub>DD</sub> = 1.8 to 2.7 V |        |        | -     |                |

| Symbol                | Parameter                                   | Min                           | Тур                 | Max    | Min                            | Тур    | Max    | Units | Conditions     |

| I <sub>DD</sub> XTAL  | Crystal Oscillator<br>Active Supply Current | -                             | _                   | 500    | _                              | _      | 300    | μA    |                |

| I <sub>DDQ</sub> XTAL | Crystal Oscillator<br>Quiescent Current     | _                             | 5                   | _      | _                              | 5      | -      | nA    |                |

| S <sub>CLK</sub>      | Clk_out State in<br>Crystal Disable         | 1                             | 1                   | 1      | 1                              | 1      | 1      |       |                |

| F <sub>XTAL</sub>     | External Crystal<br>Oscillator Frequency    | 1                             | _                   | 20     | 1                              | _      | 20     | MHz   | See Figure 74. |

| T <sub>SET</sub>      | Startup Time After<br>Enable                | _                             | 10,000              | 30,000 | _                              | 10,000 | 30,000 | Cycle |                |

|                       | Clk_out Duty Cycle                          | 40                            | 50                  | 60     | 40                             | 50     | 60     | %     |                |

|                       | Clk_out Jitter                              | -                             | 1                   | _      | -                              | 1      | -      | %     |                |

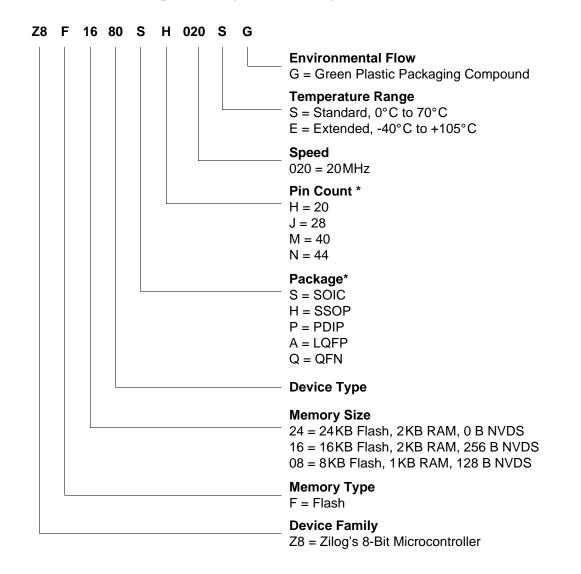

# 31.1. Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F1680SH020SG is an 8-bit, 20MHz Flash Motor Controller with 16KB of Program memory in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

Z8 Encore! XP<sup>®</sup> F1680 Series Product Specification

data, SPI 213, 214 flash control (FCTL) 272, 281 flash high and low byte (FFREQH and FRE-EQL) 274 flash page select (FPS) 273, 274 flash status (FSTAT) 272 GPIO port A-H address (PxADDR) 59 GPIO port A-H alternate function sub-registers 61 GPIO port A-H control address (PxCTL) 60 GPIO port A-H data direction sub-registers 60 I2C baud rate high (I2CBRH) 250, 255 I2C control (I2CCTL) 247 I2C status 251 I2C status (I2CSTAT) 251 mode, SPI 217 OCD control 309 OCD status 312 SPI baud rate high byte (SPIBRH) 222 SPI baud rate low byte (SPIBRL) 222 SPI data (SPIDATA) 214 SPI status (SPISTAT) 219 status, SPI 219 UARTx baud rate high byte (UxBRH) 177 UARTx baud rate low byte (UxBRL) 178 UARTx Control 0 (UxCTL0) 170, 177 UARTx control 1 (UxCTL1) 119, 172, 174, 175 UARTx receive data (UxRXD) 164 UARTx status 0 (UxSTAT0) 165, 166 UARTx status 1 (UxSTAT1) 168 UARTx transmit data (UxTXD) 163 watch-dog timer control (WDTCTL) 257, 258, 319, 320 watchdog timer control (WDTCTL) 40 watch-dog timer reload high byte (WDTH) 143 register pair 330 register pointer 331 registers ADC channel 1 189 ADC data high byte 191 ADC data low bit 192, 193, 194, 195 reset

carry flag 333 sources 33 RET 335 return 335 RL 335 RLC 335 rotate and shift instructions 335 rotate left 335 rotate left through carry 335 rotate right 335 rotate right through carry 335 RP 331 RR 330, 335 rr 330 RRC 335

### S

SBC 332 **SCF 333 SCK 199** SDA and SCL (IrDA) signals 225 second opcode map after 1FH 348 serial clock 199 serial peripheral interface (SPI) 197 set carry flag 333 set register pointer 333 shift right arithmetic 335 shift right logical 335 signal descriptions 14 slave data transfer formats (I2C) 231, 239 slave select 200 software trap 335 source operand 331 SP 331 SPI architecture 197 baud rate generator 212 baud rate high and low byte register 221 clock phase 201 configured as slave 210 control register definitions 213 data register 213, 214 error detection 210 interrupts 211

and stop mode characteristics 32