Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

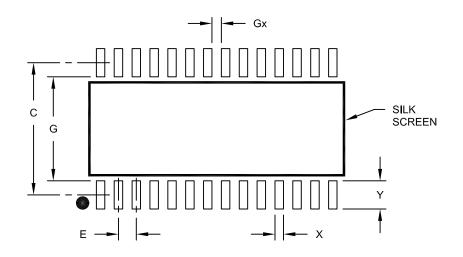

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f23k22-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2 Register Definitions: Reset Control

### REGISTER 4-1: RCON: RESET CONTROL REGISTER

| R/W-0/0          | R/W-q/u               | U-0                                                  | R/W-1/q                  | R-1/q           | R-1/q                             | R/W-q/u                         | R/W-0/q       |

|------------------|-----------------------|------------------------------------------------------|--------------------------|-----------------|-----------------------------------|---------------------------------|---------------|

| IPEN             | SBOREN <sup>(1)</sup> | _                                                    | RI                       | TO              | PD                                | POR <sup>(2)</sup>              | BOR           |

| bit 7            | ·                     |                                                      |                          |                 | •                                 | ·                               | bit (         |

| Legend:          |                       |                                                      |                          |                 |                                   |                                 |               |

| R = Readable     | e bit                 | W = Writable                                         | bit                      | U = Unimplei    | mented bit, read                  | d as '0'                        |               |

| '1' = Bit is set |                       | '0' = Bit is cle                                     | eared                    | •               |                                   | R/Value at all c                | ther Resets   |

| x = Bit is unk   | nown                  | u = unchang                                          | jed                      | q = depends     | on condition                      |                                 |               |

| bit 7            | IPEN: Interru         | ot Priority Ena                                      | ble bit                  |                 |                                   |                                 |               |

|                  |                       | iority levels or                                     |                          |                 |                                   |                                 |               |

|                  |                       |                                                      |                          | IC16CXXX Co     | mpatibility mode                  | e)                              |               |

| bit 6            | SBOREN: BO            | OR Software E                                        | nable bit <sup>(1)</sup> |                 |                                   |                                 |               |

|                  | If BOREN<1:           |                                                      |                          |                 |                                   |                                 |               |

|                  | 1 = BOR is er         |                                                      |                          |                 |                                   |                                 |               |

|                  | 0 = BOR is di         |                                                      |                          |                 |                                   |                                 |               |

|                  |                       | <u>0&gt; = 00, 10                               </u> |                          |                 |                                   |                                 |               |

| bit 5            | Unimplemen            | ted: Read as                                         | '0'                      |                 |                                   |                                 |               |

| bit 4            | RI: RESET IN          | struction Flag                                       | bit                      |                 |                                   |                                 |               |

|                  | 0 = The RES           |                                                      | was executed             | · ·             | nware or Power<br>evice Reset (mu | -on Reset)<br>ust be set in fin | mware after a |

| bit 3            | TO: Watchdo           | g Time-out Fla                                       | ag bit                   |                 |                                   |                                 |               |

|                  |                       | ower-up, CLRW                                        |                          | or SLEEP instr  | ruction                           |                                 |               |

| bit 2            | PD: Power-de          | own Detection                                        | Flag bit                 |                 |                                   |                                 |               |

|                  |                       |                                                      | the CLRWDT in            |                 |                                   |                                 |               |

|                  |                       |                                                      | SLEEP instruc            | ction           |                                   |                                 |               |

| bit 1            |                       | on Reset Stat                                        |                          |                 |                                   |                                 |               |

|                  |                       | r-on Reset occ                                       |                          | cot in coffward | offer a Rower                     | on Reset occur                  | c)            |

| bit 0            | <b>BOR:</b> Brown-    |                                                      |                          | Set in Soltware |                                   | on Reset occur                  | 5)            |

|                  |                       |                                                      |                          | (set by firmwa  | re only)                          |                                 |               |

|                  |                       |                                                      |                          |                 |                                   | or Brown-out R                  | eset occurs)  |

| Note 1: Wi       | nen CONFIG2L[         | 2:1] = 01, the                                       | n the SBOREN             | Reset state is  | s '1'; otherwise,                 | it is '0'.                      |               |

|                  | e actual Reset        |                                                      |                          | • • • •         | levice Reset. S                   |                                 | lowing this   |

register and Section 4.7 "Reset State of Registers" for additional information.

**3:** See Table 4-1.

**Note 1:** Brown-out Reset is indicated when BOR is '0' and POR is '1' (assuming that both POR and BOR were set to '1' by firmware immediately after POR).

2: It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

### 5.4 Data Memory Organization

Note: The operation of some aspects of data memory are changed when the PIC18 extended instruction set is enabled. See Section 5.7 "Data Memory and the Extended Instruction Set" for more information.

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. Figures 5-5 through 5-7 show the data memory organization for the PIC18(L)F2X/4XK22 devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register (BSR). **Section 5.4.2 "Access Bank"** provides a detailed description of the Access RAM.

### 5.4.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits of a location's address; the instruction itself includes the 8 Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory; the eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figures 5-5 through 5-7.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory maps in Figures 5-5 through 5-7 indicate which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

### 7.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 24.0 "Special Features of the CPU" for additional information.

### 7.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT). The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

### 7.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to the Data EEPROM Memory parameters in **Section 27.0** "**Electrical Specifications**" for write cycle limits. If this is the case, then an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note: If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification.

| -    |        |               |                                         |

|------|--------|---------------|-----------------------------------------|

|      | CLRF   | EEADR         | ; Start at address 0                    |

|      | CLRF   | EEADRH        | ; if > 256 bytes EEPROM                 |

|      | BCF    | EECON1, CFGS  | ; Set for memory                        |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM                   |

|      | BCF    | INTCON, GIE   | ; Disable interrupts                    |

|      | BSF    | EECON1, WREN  | ; Enable writes                         |

| Loop |        |               | ; Loop to refresh array                 |

|      | BSF    | EECON1, RD    | ; Read current address                  |

|      | MOVLW  | 55h           | ;                                       |

|      | MOVWF  | EECON2        | ; Write 55h                             |

|      | MOVLW  | 0AAh          | i                                       |

|      | MOVWF  | EECON2        | ; Write OAAh                            |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write             |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete            |

|      | BRA    | \$-2          |                                         |

|      | INCFSZ | EEADR, F      | ; Increment address                     |

|      | BRA    | LOOP          | ; Not zero, do it again                 |

|      | INCFSZ | EEADRH, F     | ; if > 256 bytes, Increment address     |

|      | BRA    | LOOP          | ; if > 256 bytes, Not zero, do it again |

|      | BCF    | EECON1, WREN  | ; Disable writes                        |

|      |        |               |                                         |

|      | BSF    | INTCON, GIE   | ; Enable interrupts                     |

### EXAMPLE 7-3: DATA EEPROM REFRESH ROUTINE

|          | Port Function Priority by Port Pin |                        |                        |                      |                      |  |  |  |  |  |  |

|----------|------------------------------------|------------------------|------------------------|----------------------|----------------------|--|--|--|--|--|--|

| Port bit | PORTA                              | PORTB                  | PORTC                  | PORTD <sup>(2)</sup> | PORTE <sup>(2)</sup> |  |  |  |  |  |  |

| 5        | SRNQ                               | CCP3 <sup>(3)</sup>    | SDO1                   | P1B                  |                      |  |  |  |  |  |  |

|          | C2OUT                              | P3A <sup>(3)</sup>     | RC5                    | RD5                  |                      |  |  |  |  |  |  |

|          | RA5                                | P2B <sup>(1)(4)</sup>  |                        |                      |                      |  |  |  |  |  |  |

|          |                                    | RB5                    |                        |                      |                      |  |  |  |  |  |  |

| 6        | OSC2                               | PGC                    | TX1/CK1                | TX2/CK2              |                      |  |  |  |  |  |  |

|          | CLKO                               | TX2/CK2 <sup>(1)</sup> | CCP3 <sup>(1)(7)</sup> | P1C                  |                      |  |  |  |  |  |  |

|          | RA6                                | RB6                    | P3A <sup>(1)(7)</sup>  | RD6                  |                      |  |  |  |  |  |  |

|          |                                    | ICDCK                  | RC6                    |                      |                      |  |  |  |  |  |  |

| 7        | RA7                                |                        |                        |                      |                      |  |  |  |  |  |  |

|          | OSC1                               | PGD                    | RX1/DT1                | RX2/DT2              |                      |  |  |  |  |  |  |

|          | RA7                                | RX2/DT2 <sup>(1)</sup> | P3B <sup>(1)</sup>     | P1D                  |                      |  |  |  |  |  |  |

|          |                                    | RB7                    | RC7                    | RD7                  |                      |  |  |  |  |  |  |

|          |                                    | ICDDT                  |                        |                      |                      |  |  |  |  |  |  |

### TABLE 10-4: PORT PIN FUNCTION PRIORITY (CONTINUED)

Note 1: PIC18(L)F2XK22 devices.

2: PIC18(L)F4XK22 devices.

3: Function default pin.

4: Function default pin (28-pin devices).

5: Function default pin (40/44-pin devices).

6: Function alternate pin.

7: Function alternate pin (28-pin devices).

8: Function alternate pin (40/44-pin devices)

| Function                | TRIS<br>Setting                                                                                                                                                                  | ANSEL<br>Setting                                                                                                                                                                                                                                                                                                                                                 | Pin<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RB6                     | 0                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LATB<6> data output; not affected by analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                         | 1                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PORTB<6> data input; disabled when analog input<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IOC2                    | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Interrupt-on-change pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| TX2 <sup>(3)</sup>      | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EUSART asynchronous transmit data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CK2 <sup>(3)</sup>      | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EUSART synchronous serial clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                         | 1                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EUSART synchronous serial clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PGC                     | x                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In-Circuit Debugger and ICSP <sup>™</sup> programming clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RB7                     | 0                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LATB<7> data output; not affected by analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                         | 1                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PORTB<7> data input; disabled when analog input<br>enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IOC3                    | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Interrupt-on-change pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| RX2 <sup>(2), (3)</sup> | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EUSART asynchronous receive data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| DT2 <sup>(2), (3)</sup> | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EUSART synchronous serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                         | 1                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EUSART synchronous serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| PGD                     | x                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | In-Circuit Debugger and ICSP <sup>™</sup> programming data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                         | x                                                                                                                                                                                | —                                                                                                                                                                                                                                                                                                                                                                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | In-Circuit Debugger and ICSP <sup>™</sup> programming data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                         | Function           RB6           IOC2           TX2 <sup>(3)</sup> CK2 <sup>(3)</sup> PGC           RB7           IOC3           RX2 <sup>(2), (3)</sup> DT2 <sup>(2), (3)</sup> | Function         TRIS<br>Setting           RB6         0           1         1           IOC2         1           TX2 <sup>(3)</sup> 1           CK2 <sup>(3)</sup> 1           PGC         x           RB7         0           IOC3         1           RX2 <sup>(2)</sup> , (3)         1           DT2 <sup>(2)</sup> , (3)         1           PGD         x | Function         TRIS<br>Setting         ANSEL<br>Setting           RB6         0            1          1           IOC2         1            TX2 <sup>(3)</sup> 1            CK2 <sup>(3)</sup> 1            PGC         x            RB7         0            IOC3         1            IOC3         1            IOC3         1            PGC         1            PGC         X            IOC3         1            IOC3         1            PGD         X | Function         TRIS<br>Setting         ANSEL<br>Setting         Pin<br>Type           RB6         0         —         0           1         —         0         1           IOC2         1         —         1           IOC2         1         —         1           TX2 <sup>(3)</sup> 1         —         0           CK2 <sup>(3)</sup> 1         —         0           PGC         x         —         1           RB7         0         —         0           1         —         1         —           RB7         0         —         0           1         —         1         —           RB7         0         —         0           1         —         1         —           IOC3         1         —         1           DT2 <sup>(2)</sup> , (3)         1         —         0           1         —         1         —           PGD         x         —         0 | $\begin{tabular}{ c c c c c c } \hline Function & TRIS Setting & Pin Type & Buffer Type \\ \hline Function & 0 & & 0 & DIG \\ \hline 1 & & 1 & TTL \\ \hline 10C2 & 1 & & 1 & TTL \\ \hline 10C2 & 1 & & 1 & TTL \\ \hline 10C2 & 1 & & 0 & DIG \\ \hline CK2^{(3)} & 1 & & 0 & DIG \\ \hline 1 & & 1 & ST \\ \hline PGC & x & & 1 & ST \\ \hline PGC & x & & 1 & ST \\ \hline RB7 & 0 & & 0 & DIG \\ \hline 1 & & 1 & TTL \\ \hline 10C3 & 1 & & 1 & TTL \\ \hline RX2^{(2), (3)} & 1 & & 1 & ST \\ \hline DT2^{(2), (3)} & 1 & & 1 & ST \\ \hline PGD & x & & 0 & DIG \\ \hline \hline 1 & & 1 & ST \\ \hline \end{tabular}$ |  |  |  |

TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

### 14.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is selected (CCPxM<3:0> = 1011), and a match of the TMRxH:TMRxL and the CCPRxH:CCPRxL registers occurs, all CCPx and ECCPx modules will immediately:

- Set the CCP interrupt flag bit CCPxIF

- CCP5 will start an ADC conversion, if the ADC is enabled

On the next TimerX rising clock edge:

• A Reset of TimerX register pair occurs – TMRxH:TMRxL = 0x0000,

This Special Event Trigger mode does not:

- Assert control over the CCPx or ECCPx pins.

- Set the TMRxIF interrupt bit when the TMRxH:TMRxL register pair is reset. (TMRxIF gets set on a TimerX overflow.)

If the value of the CCPRxH:CCPRxL registers are modified when a match occurs, the user should be aware that the automatic reset of TimerX occurs on the next rising edge of the clock. Therefore, modifying the CCPRxH:CCPRxL registers before this reset occurs will allow the TimerX to continue without being reset, inadvertently resulting in the next event being advanced or delayed.

The Special Event Trigger mode allows the CCPRxH:CCPRxL register pair to effectively provide a 16-bit programmable period register for TimerX.

#### Register Bit 4 Name Bit 7 Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0 on Page CCP1CON P1M<1:0> DC1B<1.0>CCP1M<3:0> 198 P2M<1:0> CCP2CON DC2B<1.0> CCP2M<3:0> 198 CCP3CON P3M<1:0> DC3B<1:0> CCP3M<3:0> 198 CCP4CON DC4B<1:0> CCP4M<3:0> 198 CCP5CON CCP5M<3:0> DC5B<1:0> 198 CCPR1H Capture/Compare/PWM Register 1 High Byte (MSB) CCPR1L Capture/Compare/PWM Register 1 Low Byte (LSB) CCPR2H Capture/Compare/PWM Register 2 High Byte (MSB) \_\_\_\_ CCPR2L Capture/Compare/PWM Register 2 Low Byte (LSB) \_ CCPR3H Capture/Compare/PWM Register 3 High Byte (MSB) \_ CCPR3L Capture/Compare/PWM Register 3 Low Byte (LSB) CCPR4H Capture/Compare/PWM Register 4 High Byte (MSB) \_\_\_\_ CCPR4L Capture/Compare/PWM Register 4 Low Byte (LSB) CCPR5H Capture/Compare/PWM Register 5 High Byte (MSB) \_\_\_\_ CCPR5L Capture/Compare/PWM Register 5 Low Byte (LSB) CCPTMRS0 C3TSEL<1:0> C2TSEL<1:0> C1TSEL<1:0> \_\_\_\_\_ 201 CCPTMRS1 C5TSEL<1:0> C4TSEL<1:0> 201 INTCON RBIE TMR0IF **INTOIF GIE/GIEH** PEIE/GIEL TMR0IE **INTOIE** RBIF 109 IPR1 ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMR1IP 121

### TABLE 14-5: REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

### 14.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

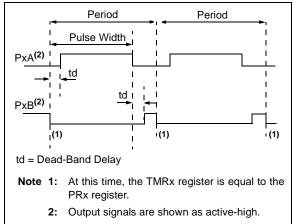

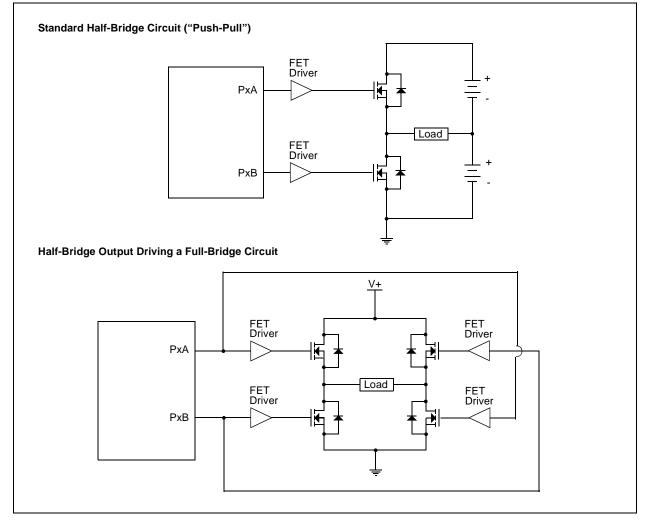

### 14.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 14-9). This mode can be used for half-bridge applications, as shown in Figure 14-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in halfbridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 14.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

### FIGURE 14-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 14-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

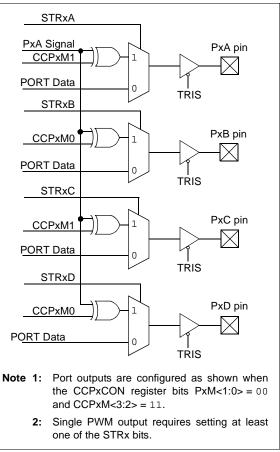

### 14.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate Steering Enable bits (STRxA, STRxB, STRxC and/or STRxD) of the PSTRxCON register, as shown in Table 14-13.

| Note: | The associated TRIS bits must be set to      |

|-------|----------------------------------------------|

|       | output ('0') to enable the pin output driver |

|       | in order to see the PWM signal on the pin.   |

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the PxD, PxC, PxB and PxA pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 14.4.3 "Enhanced PWM Auto-shutdown Mode"**. An autoshutdown event will only affect pins that have PWM outputs enabled.

#### FIGURE 14-18: SIMPLIFIED STEERING BLOCK DIAGRAM

### 14.4.6.1 Steering Synchronization

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the PxA, PxB, PxC and PxD pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 14-19 and 14-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

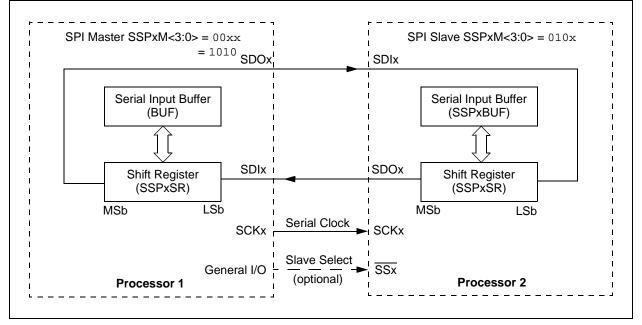

The MSSPx consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit, WCOL of the SSPxCON1 register, will be

set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSPx interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

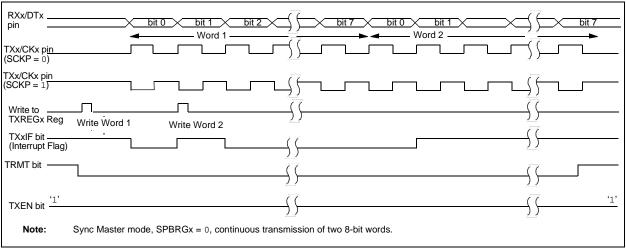

- 16.5.1.5 Synchronous Master Transmission Setup:

- 1. Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by 3. setting bits SYNC, SPEN and CSRC. Set the TRIS bits corresponding to the RXx/DTx and TXx/CKx I/O pins.

FIGURE 16-10:

- 4. Disable Receive mode by clearing bits SREN and CREN.

- Enable Transmit mode by setting the TXEN bit. 5.

- 6. If 9-bit transmission is desired, set the TX9 bit.

- 7. If interrupts are desired, set the TXxIE, GIE/ GIEH and PEIE/GIEL interrupt enable bits.

- If 9-bit transmission is selected, the ninth bit 8. should be loaded in the TX9D bit.

- Start transmission by loading data to the 9. TXREGx register.

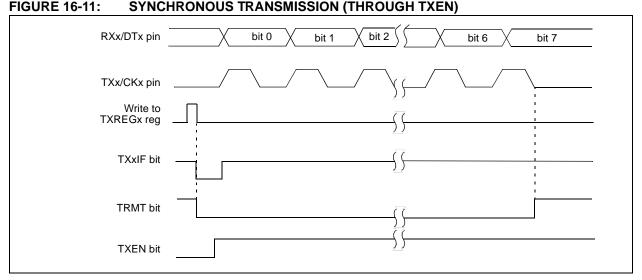

### **FIGURE 16-11:**

SYNCHRONOUS TRANSMISSION

| R/P-1      | U-0                                                              | R/P-1                                                                | R/P-1          | R/P-1                              | R/P-1            | R/P-1        | R/P-1  |

|------------|------------------------------------------------------------------|----------------------------------------------------------------------|----------------|------------------------------------|------------------|--------------|--------|

| MCLRE      |                                                                  | P2BMX                                                                | T3CMX          | HFOFST                             | CCP3MX           | PBADEN       | CCP2MX |

| bit 7      |                                                                  |                                                                      | ·              | ·                                  |                  |              | bit (  |

| Legend:    |                                                                  |                                                                      |                |                                    |                  |              |        |

| R = Reada  | able bit                                                         | P = Program                                                          | nable bit      | U = Unimpler                       | nented bit, read | d as '0'     |        |

| -n = Value | when device is un                                                | programmed                                                           |                | x = Bit is unki                    | nown             |              |        |

| bit 7      |                                                                  | R Pin Enable                                                         |                |                                    |                  |              |        |

|            |                                                                  | enabled; RE3                                                         |                |                                    |                  |              |        |

| bit 6      | Unimplemen                                                       | ted: Read as '                                                       | 0'             |                                    |                  |              |        |

| bit 5      | <b>P2BMX:</b> P2B<br>1 = P2B is on<br>P2B is on<br>0 = P2B is on | RD2 <sup>(2)</sup>                                                   |                |                                    |                  |              |        |

| bit 4      | <b>T3CMX:</b> Time<br>1 = T3CKI is 0<br>0 = T3CKI is 0           |                                                                      | MUX bit        |                                    |                  |              |        |

| bit 3      | 1 = HFINTOS                                                      |                                                                      | ng the CPU wi  | thout waiting fo                   |                  | to stabilize |        |

| bit 2      | 0 = CCP3 inp                                                     | CP3 MUX bit<br>ut/output is mu<br>ut/output is mu<br>ut/output is mu | ltiplexed with | RC6 <sup>(1)</sup>                 |                  |              |        |

| bit 1      | 1 = ANSELB<                                                      |                                                                      | 1, PORTB<5:    | 0> pins are cor<br>0> pins are cor |                  |              |        |