Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f23k22-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | Pin N | lumber |      | <b>D</b> <sup>2</sup> 11 | Pin  | Buffer |                                                     |

|------|-------|--------|------|--------------------------|------|--------|-----------------------------------------------------|

| PDIP | TQFP  | QFN    | UQFN | Pin Name                 | Туре | Туре   | Description                                         |

| 21   | 40    | 40     | 36   | RD2/P2B/AN22             |      | •      |                                                     |

|      |       |        |      | RD2                      | I/O  | ST     | Digital I/O                                         |

|      |       |        |      | P2B <sup>(1)</sup>       | 0    | CMOS   | Enhanced CCP2 PWM output.                           |

|      |       |        |      | AN22                     | I    | Analog | Analog input 22.                                    |

| 22   | 41    | 41     | 37   | RD3/P2C/SS2/AN23         |      |        |                                                     |

|      |       |        |      | RD3                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P2C                      | 0    | CMOS   | Enhanced CCP2 PWM output.                           |

|      |       |        |      | SS2                      | I    | TTL    | SPI slave select input (MSSP).                      |

|      |       |        |      | AN23                     | I    | Analog | Analog input 23.                                    |

| 27   | 2     | 2      | 2    | RD4/P2D/SDO2/AN24        |      |        |                                                     |

|      |       |        |      | RD4                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P2D                      | 0    | CMOS   | Enhanced CCP2 PWM output.                           |

|      |       |        |      | SDO2                     | 0    | -      | SPI data out (MSSP).                                |

|      |       |        |      | AN24                     | I    | Analog | Analog input 24.                                    |

| 28   | 3     | 3      | 3    | RD5/P1B/AN25             |      |        |                                                     |

|      |       |        |      | RD5                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P1B                      | 0    | CMOS   | Enhanced CCP1 PWM output.                           |

|      |       |        |      | AN25                     | I    | Analog | Analog input 25.                                    |

| 29   | 4     | 4      | 4    | RD6/P1C/TX2/CK2/AN26     |      |        |                                                     |

|      |       |        |      | RD6                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P1C                      | 0    | CMOS   | Enhanced CCP1 PWM output.                           |

|      |       |        |      | TX2                      | 0    | —      | EUSART asynchronous transmit.                       |

|      |       |        |      | CK2                      | I/O  | ST     | EUSART synchronous clock (see related RXx/<br>DTx). |

|      |       |        |      | AN26                     | I    | Analog | Analog input 26.                                    |

| 30   | 5     | 5      | 5    | RD7/P1D/RX2/DT2/AN27     |      | •      |                                                     |

|      |       |        |      | RD7                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P1D                      | 0    | CMOS   | Enhanced CCP1 PWM output.                           |

|      |       |        |      | RX2                      | I    | ST     | EUSART asynchronous receive.                        |

|      |       |        |      | DT2                      | I/O  | ST     | EUSART synchronous data (see related TXx/<br>CKx).  |

|      |       |        |      | AN27                     | I    | Analog | Analog input 27.                                    |

| 8    | 25    | 25     | 23   | RE0/P3A/CCP3/AN5         |      | •      |                                                     |

|      |       |        |      | RE0                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P3A <sup>(2)</sup>       | 0    | CMOS   | Enhanced CCP3 PWM output.                           |

|      |       |        |      | CCP3 <sup>(2)</sup>      | I/O  | ST     | Capture 3 input/Compare 3 output/PWM 3 outpu        |

|      |       |        |      | AN5                      | I    | Analog | Analog input 5.                                     |

| 9    | 26    | 26     | 24   | RE1/P3B/AN6              |      |        |                                                     |

|      |       |        |      | RE1                      | I/O  | ST     | Digital I/O.                                        |

|      |       |        |      | P3B                      | 0    | CMOS   | Enhanced CCP3 PWM output.                           |

|      |       |        |      | AN6                      |      | Analog | Analog input 6.                                     |

#### TABLE 1-3: PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

| IRCF<2:0>  | INTSRC | MFIOSEL | Selected Oscillator | Selected Oscillator Stable when: |  |  |  |  |  |  |  |

|------------|--------|---------|---------------------|----------------------------------|--|--|--|--|--|--|--|

| 000        | 0      | x       | LFINTOSC            | LFIOFS = 1                       |  |  |  |  |  |  |  |

| 000        | 1      | 0       | HFINTOSC            | HFIOFS = 1                       |  |  |  |  |  |  |  |

| 000        | 1      | 1       | MFINTOSC            | MFIOFS = 1                       |  |  |  |  |  |  |  |

| 010 or 001 | x      | 0       | HFINTOSC            | HFIOFS = 1                       |  |  |  |  |  |  |  |

| 010 or 001 | x      | 1       | MFINTOSC            | MFIOFS = 1                       |  |  |  |  |  |  |  |

| 011 - 111  | x      | x       | HFINTOSC            | HFIOFS = 1                       |  |  |  |  |  |  |  |

#### TABLE 3-2: INTERNAL OSCILLATOR FREQUENCY STABILITY BITS

## 9.8 Register Definitions: Interrupt Control

| R/W-0        | R/W-0                                                                          | R/W-0                                                          | R/W-0                               | R/W-0                          | R/W-0              | R/W-0             | R/W-x |

|--------------|--------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|--------------------------------|--------------------|-------------------|-------|

| GIE/GIE      | H PEIE/GIEL                                                                    | TMR0IE                                                         | INTOIE                              | RBIE                           | TMR0IF             | INT0IF            | RBIF  |

| bit 7        |                                                                                |                                                                |                                     |                                |                    |                   | bit ( |

|              |                                                                                |                                                                |                                     |                                |                    |                   |       |

| Legend:      |                                                                                |                                                                |                                     |                                |                    |                   |       |

| R = Readab   |                                                                                | W = Writable b                                                 | it                                  | •                              | ented bit, read as |                   |       |

| -n = Value a | it POR                                                                         | '1' = Bit is set                                               |                                     | '0' = Bit is clea              | ired               | x = Bit is unknow | vn    |

| bit 7        | When IPEN =<br>1 = Enables a<br>0 = Disables a<br>When IPEN =                  | II unmasked inter<br>III interrupts inclu-<br><u>1:</u>        | rupts<br>ding peripherals           | 5                              |                    |                   |       |

|              | 0 = Disables a                                                                 | II high priority inte<br>III interrupts inclue                 | ding low priority                   | ,                              |                    |                   |       |

| bit 6        | When IPEN =<br>1 = Enables a<br>0 = Disables a<br>When IPEN =<br>1 = Enables a | II unmasked perip<br>II peripheral inter                       | oheral interrupts<br>rupts<br>rupts | 5                              |                    |                   |       |

| bit 5        | 1 = Enables th                                                                 | 0 Overflow Interr<br>ne TMR0 overflow<br>he TMR0 overflow      | ,<br>v interrupt                    |                                |                    |                   |       |

| bit 4        | 1 = Enables th                                                                 | External Interrupt<br>ne INT0 external i<br>he INT0 external   | nterrupt                            |                                |                    |                   |       |

| bit 3        | 1 = Enables th                                                                 | nterrupt-On-Cha<br>ne IOCx port char<br>he IOCx port cha       | nge interrupt                       | rrupt Enable bit <sup>(2</sup> | 2)                 |                   |       |

| bit 2        | 1 = TMR0 reg                                                                   | 0 Overflow Interr<br>ister has overflow<br>ister did not overf | ved (must be cle                    | eared by softwar               | e)                 |                   |       |

| bit 1        | 1 = The INT0                                                                   | External Interrupt<br>external interrupt<br>external interrupt | occurred (must                      | t be cleared by s              | oftware)           |                   |       |

| bit 0        | <b>RBIF:</b> Port B I<br>1 = At least or                                       | nterrupt-On-Chai                                               | nge (IOCx) Inte<br>> (RB<7:4>) pi   | ns changed state               | e (must be cleare  | d by software)    |       |

| Note 1:      | A mismatch condition                                                           |                                                                |                                     | it. Reading POR                | TB will end the    |                   |       |

| 2:           | RB port change inte                                                            | rrupto olgo roqui                                              | o tha individual                    | nin IOCB anable                | 96                 |                   |       |

### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| R/W-0        | R/W-0                                             | R/W-0                                                            | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |  |  |

|--------------|---------------------------------------------------|------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|--------|--|--|

| OSCFIE       | C1IE                                              | C2IE                                                             | EEIE           | BCL1IE           | HLVDIE          | TMR3IE          | CCP2IE |  |  |

| bit 7        |                                                   |                                                                  |                |                  |                 |                 | bit (  |  |  |

| Legend:      |                                                   |                                                                  |                |                  |                 |                 |        |  |  |

| R = Readab   | le bit                                            | W = Writable                                                     | bit            | U = Unimple      | mented bit, rea | d as '0'        |        |  |  |

| -n = Value a | t POR                                             | '1' = Bit is set                                                 |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |  |  |

| bit 7        | <b>OSCFIE:</b> Osc<br>1 = Enabled<br>0 = Disabled | illator Fail Inte                                                | rrupt Enable I | bit              |                 |                 |        |  |  |

| bit 6        | C1IE: Compa<br>1 = Enabled<br>0 = Disabled        | rator C1 Interro                                                 | upt Enable bit | t                |                 |                 |        |  |  |

| bit 5        | <b>C2IE:</b> Compa<br>1 = Enabled<br>0 = Disabled | rator C2 Interro                                                 | upt Enable bit | t                |                 |                 |        |  |  |

| bit 4        | EEIE: Data E<br>1 = Enabled<br>0 = Disabled       | EPROM/Flash                                                      | Write Operat   | ion Interrupt Er | nable bit       |                 |        |  |  |

| bit 3        | BCL1IE: MSS<br>1 = Enabled<br>0 = Disabled        | SP1 Bus Collisi                                                  | on Interrupt E | Enable bit       |                 |                 |        |  |  |

| bit 2        | HLVDIE: Low<br>1 = Enabled<br>0 = Disabled        | -Voltage Detec                                                   | t Interrupt En | able bit         |                 |                 |        |  |  |

| bit 1        | <b>TMR3IE:</b> TMI<br>1 = Enabled<br>0 = Disabled | <b>TMR3IE:</b> TMR3 Overflow Interrupt Enable bit<br>1 = Enabled |                |                  |                 |                 |        |  |  |

| bit 0        | <b>CCP2IE:</b> CCI<br>1 = Enabled<br>0 = Disabled | P2 Interrupt En                                                  | able bit       |                  |                 |                 |        |  |  |

#### REGISTER 9-10: PIE2: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 2

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. All pins of the I/O ports are multiplexed with one or more alternate functions from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has five registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

- ANSEL register (analog input control)

- SLRCON register (port slew rate control)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

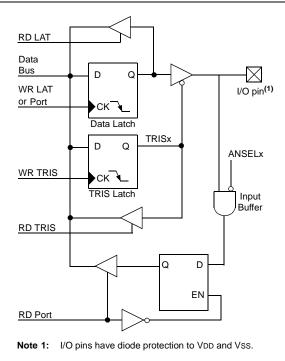

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

#### FIGURE 10-1: GENERIC I/O PORT OPERATION

### 10.1 PORTA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the PORT latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs, and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as analog is selected by setting the ANSELA<5, 3:0> bits in the ANSELA register which is the default setting after a Power-on Reset.

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CM1CON0 and CM2CON0 registers.

Note: On a Power-on Reset, RA5 and RA<3:0> are configured as analog inputs and read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the drivers of the PORTA pins, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| MOVLB | 0xF    | ; | Set BSR for banked SFRs |

|-------|--------|---|-------------------------|

| CLRF  | PORTA  | ; | Initialize PORTA by     |

|       |        | ; | clearing output         |

|       |        | ; | data latches            |

| CLRF  | LATA   | ; | Alternate method        |

|       |        | ; | to clear output         |

|       |        | ; | data latches            |

| MOVLW | E0h    | ; | Configure I/O           |

| MOVWF | ANSELA | ; | for digital inputs      |

| MOVLW | OCFh   | ; | Value used to           |

|       |        | ; | initialize data         |

|       |        | ; | direction               |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs   |

|       |        | ; | RA<5:4> as outputs      |

|       |        |   | _                       |

### TABLE 10-11: PORTD I/O SUMMARY

| Pin Name            | Function           | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type   | Description                                              |

|---------------------|--------------------|-----------------|---------------|-------------|------------------|----------------------------------------------------------|

| RD0/SCK2/SCL2/AN20  | RD0                | 0               | 0             | 0           | DIG              | LATD<0> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<0> data input; disabled when analog input enabled. |

|                     | SCK2               | 0               | 0             | 0           | DIG              | MSSP2 SPI Clock output.                                  |

|                     |                    | 1               | 0             | I           | ST               | MSSP2 SPI Clock input.                                   |

|                     | SCL2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C Clock output.                     |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C Clock input.                      |

|                     | AN20               | 1               | 1             | I           | AN               | Analog input 20.                                         |

| RD1/CCP4/SDI2/SDA2/ | RD1                | 0               | 0             | 0           | DIG              | LATD<1> data output; not affected by analog input.       |

| AN21                |                    | 1               | 0             | I           | ST               | PORTD<1> data input; disabled when analog input enabled. |

|                     | CCP4               | 0               | 0             | 0           | DIG              | Compare 4 output/PWM 4 output.                           |

|                     |                    | 1               | 0             | I           | ST               | Capture 4 input.                                         |

|                     | SDI2               | 1               | 0             | I           | ST               | MSSP2 SPI data input.                                    |

|                     | SDA2               | 0               | 0             | 0           | DIG              | MSSP2 I <sup>2</sup> C data output.                      |

|                     |                    | 1               | 0             | I           | l <sup>2</sup> C | MSSP2 I <sup>2</sup> C data input.                       |

|                     | AN21               | 1               | 1             | I           | AN               | Analog input 21.                                         |

| RD2/P2B/AN22        | RD2                | 0               | 0             | 0           | DIG              | LATD<2> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<2> data input; disabled when analog input enabled. |

|                     | P2B <sup>(1)</sup> | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 2.                              |

|                     | AN22               | 1               | 1             | I           | AN               | Analog input 22.                                         |

| RD3/P2C/SS2/AN23    | RD3                | 0               | 0             | 0           | DIG              | LATD<3> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<3> data input; disabled when analog input enabled. |

|                     | P2C                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 4.                              |

|                     | SS2                | 1               | 0             | Ι           | TTL              | MSSP2 SPI slave select input.                            |

|                     | AN23               | 1               | 1             | I           | AN               | Analog input 23.                                         |

| RD4/P2D/SDO2/AN24   | RD4                | 0               | 0             | 0           | DIG              | LATD<4> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<4> data input; disabled when analog input enabled. |

|                     | P2D                | 0               | 0             | 0           | DIG              | Enhanced CCP2 PWM output 3.                              |

|                     | SDO2               | 0               | 0             | 0           | DIG              | MSSP2 SPI data output.                                   |

|                     | AN24               | 1               | 1             | I           | AN               | Analog input 24.                                         |

| RD5/P1B/AN25        | RD5                | 0               | 0             | 0           | DIG              | LATD<5> data output; not affected by analog input.       |

|                     |                    | 1               | 0             | I           | ST               | PORTD<5> data input; disabled when analog input enabled. |

|                     | P1B                | 0               | 0             | 0           | DIG              | Enhanced CCP1 PWM output 2.                              |

|                     | AN25               | 1               | 1             | I           | AN               | Analog input 25.                                         |

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

### 12.13 Register Definitions: Timer1/3/5 Control

### REGISTER 12-1: TXCON: TIMER1/3/5 CONTROL REGISTER

| R/W-0/u                           | R/W-0/u                                                                                                                           | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0/u                                                             | R/W-0/u                                         | R/W-0/u                         | R/W-0/0            | R/W-0/u      |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------|---------------------------------|--------------------|--------------|

| TMRx                              | CS<1:0>                                                                                                                           | TxCKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S<1:0>                                                              | TxSOSCEN                                        | TxSYNC                          | TxRD16             | TMRxON       |

| bit 7                             |                                                                                                                                   | ÷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     | · · · ·                                         |                                 |                    | bit 0        |

|                                   |                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

| Legend:                           | a hit                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - i+                                                                |                                                 | antad hit raad                  |                    |              |

| R = Readabl<br>u = Bit is unc     |                                                                                                                                   | W = Writable<br>x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 | ented bit, read<br>t POR and BO |                    | othar Basata |

| u = Bit is und<br>(1' = Bit is se | -                                                                                                                                 | x = Bit is unknown is clear the second sec |                                                                     |                                                 | I FOR and BO                    | R/ Value at all    |              |

| 1 - Dit 13 36                     | ι                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

| bit 7-6                           | TMRxCS<1:                                                                                                                         | <b>0&gt;:</b> Timer1/3/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock Source                                                        | Select bits                                     |                                 |                    |              |

| bit 5-4                           | 10 = Timer1/2<br><u>If TxSO</u><br>Externa<br><u>If TxSO</u><br>Crystal<br>01 = Timer1/2<br>00 = Timer1/2<br><b>TxCKPS&lt;1:(</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CKI pin (on the<br>SCI/SOSCO<br>e is system clo<br>e is instruction | e rising edge)<br>pins<br>ock (Fosc)            | ts                              |                    |              |

|                                   | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres<br>00 = 1:1 Pres                                                                  | scale value<br>scale value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |                                                 |                                 |                    |              |

| bit 3                             | TxSOSCEN:                                                                                                                         | Secondary Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | cillator Enable                                                     | Control bit                                     |                                 |                    |              |

|                                   |                                                                                                                                   | ed Secondary of<br>ed Secondary of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                 |                                 |                    |              |

| bit 2                             | TMRxCS<1:0                                                                                                                        | 0 > = 1X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     | Synchronization                                 | n Control bit                   |                    |              |

|                                   |                                                                                                                                   | synchronize exte<br>nize external clo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     | ut<br>system clock (F                           | OSC)                            |                    |              |

|                                   | <u>TMRxCS&lt;1:(</u><br>This bit is ign                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 uses the int                                                      | ernal clock whe                                 | n TMRxCS<1:(                    | <b>)&gt; =</b> 1X. |              |

| bit 1                             | 1 = Enables                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rite of Timer1/                                                     | bit<br>'3/5 in one 16-bi<br>'3/5 in two 8-bit ( | •                               |                    |              |

| bit 0                             | 1 = Enables<br>0 = Stops Ti                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

|        | 0. KEO   |           |               |                 |                       |                |         |         |                            |

|--------|----------|-----------|---------------|-----------------|-----------------------|----------------|---------|---------|----------------------------|

| Name   | Bit 7    | Bit 6     | Bit 5         | Bit 4           | Bit 3                 | Bit 2          | Bit 1   | Bit 0   | Reset<br>Values on<br>Page |

| ANSELB | _        | —         | ANSB5         | ANSB4           | ANSB3                 | ANSB2          | ANSB1   | ANSB0   | 150                        |

| ANSELC | ANSC7    | ANSC6     | ANSC5         | ANSC4           | ANSC3                 | ANSC2          | _       | _       | 150                        |

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE        | INTOIE          | RBIE                  | TMR0IF         | INT0IF  | RBIF    | 109                        |

| IPR1   | _        | ADIP      | RC1IP         | TX1IP           | SSP1IP                | CCP1IP         | TMR2IP  | TMR1IP  | 121                        |

| IPR2   | OSCFIP   | C1IP      | C2IP          | EEIP            | BCL1IP                | HLVDIP         | TMR3IP  | CCP2IP  | 122                        |

| IPR3   | SSP2IP   | BCL2IP    | RC2IP         | TX2IP           | CTMUIP                | TMR5GIP        | TMR3GIP | TMR1GIP | 123                        |

| IPR5   | —        | _         | —             |                 | _                     | TMR6IP         | TMR5IP  | TMR4IP  | 124                        |

| PIE1   | _        | ADIE      | RC1IE         | TX1IE           | SSP1IE                | CCP1IE         | TMR2IE  | TMR1IE  | 117                        |

| PIE2   | OSCFIE   | C1IE      | C2IE          | EEIE            | BCL1IE                | HLVDIE         | TMR3IE  | CCP2IE  | 118                        |

| PIE3   | SSP2IE   | BCL2IE    | RC2IE         | TX2IE           | CTMUIE                | TMR5GIE        | TMR3GIE | TMR1GIE | 119                        |

| PIE5   |          | _         |               | _               | —                     | TMR6IE         | TMR5IE  | TMR4IE  | 120                        |

| PIR1   |          | ADIF      | RC1IF         | TX1IF           | SSP1IF                | CCP1IF         | TMR2IF  | TMR1IF  | 112                        |

| PIR2   | OSCFIF   | C1IF      | C2IF          | EEIF            | BCL1IF                | HLVDIF         | TMR3IF  | CCP2IF  | 113                        |

| PIR3   | SSP2IF   | BCL2IF    | RC2IF         | TX2IF           | CTMUIF                | TMR5GIF        | TMR3GIF | TMR1GIF | 114                        |

| PIR5   |          | _         |               | _               | —                     | TMR6IF         | TMR5IF  | TMR4IF  | 116                        |

| PMD0   | UART2MD  | UART1MD   | TMR6MD        | TMR5MD          | TMR4MD                | TMR3MD         | TMR2MD  | TMR1MD  | 52                         |

| T1CON  | TMR1C    | S<1:0>    | T1CK          | PS<1:0>         | T1SOSCEN              | T1SYNC         | T1RD16  | TMR10N  | 166                        |

| T1GCON | TMR1GE   | T1GPOL    | T1GTM         | T1GSPM          | T1GGO/DONE            | T1GVAL         | T1GSS   | S<1:0>  | 167                        |

| T3CON  | TMR3C    | S<1:0>    | T3CK          | PS<1:0>         | T3SOSCEN              | T3SYNC         | T3RD16  | TMR3ON  | 166                        |

| T3GCON | TMR3GE   | T3GPOL    | T3GTM         | T3GSPM          | T3GGO/DONE            | T3GVAL         | T3GSS   | S<1:0>  | 167                        |

| T5CON  | TMR5C    | S<1:0>    | T5CKI         | PS<1:0>         | T5SOSCEN              | T5SYNC         | T5RD16  | TMR5ON  | 166                        |

| T5GCON | TMR5GE   | T5GPOL    | T5GTM         | T5GSPM          | T5GGO/DONE            | T5GVAL         | T5GSS   | S<1:0>  | 167                        |

| TMR1H  |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR1 Reg | gister  |         | _                          |

| TMR1L  |          |           | Least S       | ignificant Byte | of the 16-bit TMR1    | Register       |         |         | _                          |

| TMR3H  |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR3 Reg | gister  |         | _                          |

| TMR3L  |          |           | Least S       | ignificant Byte | of the 16-bit TMR3    | Register       |         |         |                            |

| TMR5H  |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR5 Reg | gister  |         | _                          |

| TMR5L  |          |           | Least S       | ignificant Byte | of the 16-bit TMR5    | Register       |         |         | _                          |

| TRISB  | TRISB7   | TRISB6    | TRISB5        | TRISB4          | TRISB3                | TRISB2         | TRISB1  | TRISB0  | 151                        |

| TRISC  | TRISC7   | TRISC6    | TRISC5        | TRISC4          | TRISC3                | TRISC2         | TRISC1  | TRISC0  | 151                        |

#### TABLE 12-6: REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

#### TABLE 12-7: CONFIGURATION REGISTERS ASSOCIATED WITH TIMER1/3/5