Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f23k22-i-so |

TABLE 1-3: PIC18(L)F4XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

|      | Pin N                            | lumber |      | 5: 11                 | Pin      | Buffer |                                                      |

|------|----------------------------------|--------|------|-----------------------|----------|--------|------------------------------------------------------|

| PDIP | TQFP                             | QFN    | UQFN | Pin Name              | Туре     | Туре   | Description                                          |

| 37   | 14                               | 14     | 12   | RB4/IOC0/T5G/AN11     |          | •      |                                                      |

|      |                                  |        |      | RB4                   | I/O      | TTL    | Digital I/O.                                         |

|      |                                  |        |      | IOC0                  | 1        | TTL    | Interrupt-on-change pin.                             |

|      |                                  |        |      | T5G                   | I        | ST     | Timer5 external clock gate input.                    |

|      |                                  |        |      | AN11                  | ı        | Analog | Analog input 11.                                     |

| 38   | 15                               | 15     | 13   | RB5/IOC1/P3A/CCP3/T3C | KI/T1G/A | N13    |                                                      |

|      |                                  |        |      | RB5                   | I/O      | TTL    | Digital I/O.                                         |

|      |                                  |        |      | IOC1                  | 1        | TTL    | Interrupt-on-change pin.                             |

|      |                                  |        |      | P3A <sup>(1)</sup>    | 0        | CMOS   | Enhanced CCP3 PWM output.                            |

|      |                                  |        |      | CCP3 <sup>(1)</sup>   | I/O      | ST     | Capture 3 input/Compare 3 output/PWM 3 output.       |

|      |                                  |        |      | T3CKI <sup>(2)</sup>  | I        | ST     | Timer3 clock input.                                  |

|      |                                  |        |      | T1G                   | I        | ST     | Timer1 external clock gate input.                    |

|      |                                  |        |      | AN13                  | 1        | Analog | Analog input 13.                                     |

| 39   | 16                               | 16     | 14   | RB6/IOC2/PGC          |          |        |                                                      |

|      |                                  |        |      | RB6                   | I/O      | TTL    | Digital I/O.                                         |

|      |                                  |        |      | IOC2                  | 1        | TTL    | Interrupt-on-change pin.                             |

|      |                                  |        |      | PGC                   | I/O      | ST     | In-Circuit Debugger and ICSP™ programming clock pin. |

| 40   | 17                               | 17     | 15   | RB7/IOC3/PGD          |          |        |                                                      |

|      |                                  |        |      | RB7                   | I/O      | TTL    | Digital I/O.                                         |

|      |                                  |        |      | IOC3                  | 1        | TTL    | Interrupt-on-change pin.                             |

|      |                                  |        |      | PGD                   | I/O      | ST     | In-Circuit Debugger and ICSP™ programming data pin.  |

| 15   | 32                               | 34     | 30   | RC0/P2B/T3CKI/T3G/T1C | KI/SOSC  | 0      |                                                      |

|      |                                  |        |      | RC0                   | I/O      | ST     | Digital I/O.                                         |

|      |                                  |        |      | P2B <sup>(2)</sup>    | 0        | CMOS   | Enhanced CCP1 PWM output.                            |

|      |                                  |        |      | Т3СКІ <sup>(1)</sup>  | ı        | ST     | Timer3 clock input.                                  |

|      |                                  |        |      | T3G                   | ı        | ST     | Timer3 external clock gate input.                    |

|      |                                  |        |      | T1CKI                 | ı        | ST     | Timer1 clock input.                                  |

|      |                                  |        |      | sosco                 | 0        | _      | Secondary oscillator output.                         |

| 16   | 35                               | 35     | 31   | RC1/P2A/CCP2/SOSCI    | l .      |        |                                                      |

|      |                                  |        |      | RC1                   | I/O      | ST     | Digital I/O.                                         |

|      |                                  |        |      | P2A <sup>(1)</sup>    | 0        | CMOS   | Enhanced CCP2 PWM output.                            |

|      |                                  |        |      | CCP2 <sup>(1)</sup>   | I/O      | ST     | Capture 2 input/Compare 2 output/PWM 2 output.       |

|      |                                  |        |      | SOSCI                 | ı        | Analog | Secondary oscillator input.                          |

| 17   | 36                               | 36     | 32   | RC2/CTPLS/P1A/CCP1/T  |          | U      | 1 2                                                  |

|      |                                  |        |      | RC2                   | I/O      | ST     | Digital I/O.                                         |

|      |                                  |        |      | CTPLS                 | 0        | _      | CTMU pulse generator output.                         |

|      |                                  |        |      | P1A                   | 0        | CMOS   | Enhanced CCP1 PWM output.                            |

|      |                                  |        |      | CCP1                  | I/O      | ST     | Capture 1 input/Compare 1 output/PWM 1 output.       |

|      |                                  |        |      | T5CKI                 | ı        | ST     | Timer5 clock input.                                  |

|      |                                  |        |      | AN14                  | i        | Analog | Analog input 14.                                     |

|      | AN14 I Analog   Analog input 14. |        |      |                       |          |        |                                                      |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3/P3A and CCP2/P2A when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

#### 2.7.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31.25 kHz internal clock source. The LFINTOSC is not tunable, but is designed to be stable across temperature and voltage. See **Section 27.0** "Electrical **Specifications**" for the LFINTOSC accuracy specifications.

The output of the LFINTOSC can be a clock source to the primary clock or the INTOSC clock (see Figure 2-1). The LFINTOSC is also the clock source for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

## 2.7.2 FREQUENCY SELECT BITS (IRCF)

The HFINTOSC (16 MHz) and MFINTOSC (500 MHz) outputs connect to a divide circuit that provides frequencies of 16 MHz to 31.25 kHz. These divide circuit frequencies, along with the 31.25 kHz LFINTOSC output, are multiplexed to provide a single INTOSC clock output (see Figure 2-1). The IRCF<2:0> bits of the OSCCON register, the MFIOSEL bit of the OSCCON2 register and the INTSRC bit of the OSCTUNE register, select the output frequency of the internal oscillators. One of eight frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz (default after Reset)

- 500 kHz (MFINTOSC or HFINTOSC)

- 250 kHz (MFINTOSC or HFINTOSC)

- 31 kHz (LFINTOSC, MFINTOSC or HFINTOSC)

#### 2.7.3 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block outputs (HFINTOSC/MFINTOSC) for 16 MHz/500 kHz. However, this frequency may drift as VDD or temperature changes. It is possible to adjust the HFINTOSC/MFINTOSC frequency by modifying the value of the TUN<5:0> bits in the OSCTUNE register. This has no effect on the LFINTOSC clock source frequency.

Tuning the HFINTOSC/MFINTOSC source requires knowing when to make the adjustment, in which direction it should be made and, in some cases, how large a change is needed. Three possible compensation techniques are discussed in the following sections. However, other techniques may be used.

## 2.7.3.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

### 2.7.3.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

## 2.7.3.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1, Timer3 or Timer5 clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by any one of the following:

- · an interrupt

- a Reset

- a Watchdog Time-out

This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or the Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

The instruction immediately following the SLEEP instruction is executed on all exits by interrupt from Idle or Sleep modes. Code execution then branches to the interrupt vector if the GIE/GIEH bit of the INTCON register is set, otherwise code execution continues without branching (see **Section 9.0 "Interrupts"**).

A fixed delay of interval TCSD following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 24.3 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by any one of the following:

- executing a SLEEP instruction

- executing a CLRWDT instruction

- the loss of the currently selected clock source when the Fail-Safe Clock Monitor is enabled

- modifying the IRCF bits in the OSCCON register when the internal oscillator block is the device clock source

#### 3.5.3 EXIT BY RESET

Exiting Sleep and Idle modes by Reset causes code execution to restart at address '0'. See **Section 4.0** "**Reset**" for more details.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator.

## 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC, INTOSC, and INTOSCIO modes). However, a fixed delay of interval Tcsp following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

### REGISTER 3-3: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

|-------|-----|-----|-----|--------|--------|--------|-------|

| _     | _   | _   | _   | CTMUMD | CMP2MD | CMP1MD | ADCMD |

| bit 7 |     |     |     |        |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-4 **Unimplemented:** Read as '0'

bit 3 CTMUMD: CTMU Peripheral Module Disable Control bit

1 = Module is disabled, Clock Source is disconnected, module does not draw digital power

0 = Module is enabled, Clock Source is connected, module draws digital power

bit 2 CMP2MD: Comparator C2 Peripheral Module Disable Control bit

1 = Module is disabled, Clock Source is disconnected, module does not draw digital power

0 = Module is enabled, Clock Source is connected, module draws digital power

bit 1 CMP1MD: Comparator C1 Peripheral Module Disable Control bit

1 = Module is disabled, Clock Source is disconnected, module does not draw digital power

0 = Module is enabled, Clock Source is connected, module draws digital power

bit 0 ADCMD: ADC Peripheral Module Disable Control bit

1 = Module is disabled, Clock Source is disconnected, module does not draw digital power

0 = Module is enabled, Clock Source is connected, module draws digital power

## 7.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to **Section 24.0** "**Special Features of the CPU**" for additional information.

## 7.7 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT). The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

### 7.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to the Data EEPROM Memory parameters in **Section 27.0** "Electrical **Specifications**" for write cycle limits. If this is the case, then an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

Note:

If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification.

#### **EXAMPLE 7-3: DATA EEPROM REFRESH ROUTINE**

```

CLRF

EEADR

; Start at address 0

CLRF

EEADRH

; if > 256 bytes EEPROM

BCF

EECON1, CFGS

; Set for memory

EECON1, EEPGD

; Set for Data EEPROM

BCF

BCF

INTCON, GIE

; Disable interrupts

BSF

EECON1, WREN

; Enable writes

qool

; Loop to refresh array

EECON1, RD

BSF

; Read current address

M.TVOM

55h

MOVWF

EECON2

; Write 55h

MOVLW

0AAh

MOVWF

EECON2

; Write OAAh

BSF

EECON1, WR

; Set WR bit to begin write

BTFSC

EECON1. WR

; Wait for write to complete

BRA

$-2

; Increment address

INCFSZ

EEADR, F

BRA

LOOP

; Not zero, do it again

TNCFS7

EEADRH, F

; if > 256 bytes, Increment address

BRA

LOOP

; if > 256 bytes, Not zero, do it again

BCF

EECON1, WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

### 11.0 TIMERO MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- Readable and writable registers

- Dedicated 8-bit, software programmable prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- · Interrupt-on-overflow

The ToCON register (Register 11-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 11-1. Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

## 11.1 Register Definitions: Timer0 Control

#### REGISTER 11-1: TOCON: TIMERO CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1     | R/W-1 |

|--------|--------|-------|-------|-------|-------|-----------|-------|

| TMR0ON | T08BIT | T0CS  | T0SE  | PSA   |       | TOPS<2:0> |       |

| bit 7  |        |       |       |       |       |           | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7 TMR0ON: Timer0 On/Off Control bit

1 = Enables Timer00 = Stops Timer0

bit 6 T08BIT: Timer0 8-bit/16-bit Control bit

1 = Timer0 is configured as an 8-bit timer/counter 0 = Timer0 is configured as a 16-bit timer/counter

bit 5 Tocs: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

bit 3 PSA: Timer0 Prescaler Assignment bit

1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

${\tt 0 = Timer 0\ prescaler\ is\ assigned.\ Timer 0\ clock\ input\ comes\ from\ prescaler\ output.}$

bit 2-0 **T0PS<2:0>**: Timer0 Prescaler Select bits

111 = 1:256 prescale value 110 = 1:128 prescale value

101 = 1:64 prescale value

100 = 1:32 prescale value

011 = 1:16 prescale value

010 = 1:8 prescale value

001 = 1:4 prescale value

000 = 1:2 prescale value

## 12.12 Peripheral Module Disable

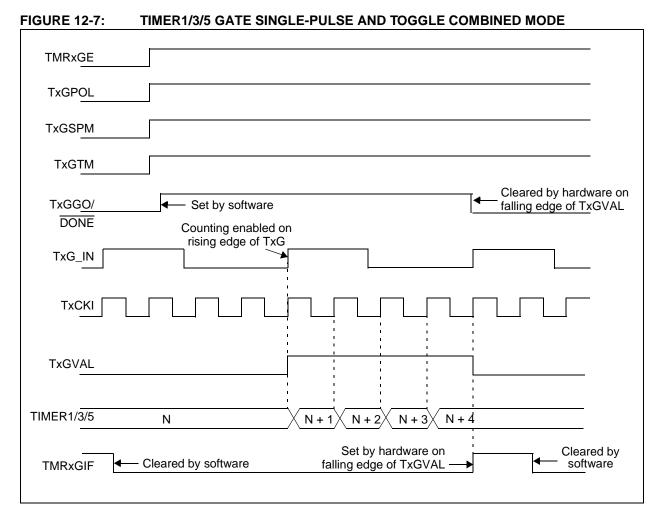

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the PMD0 Register. See **Section 3.0** "**Power-Managed Modes**" for more information.

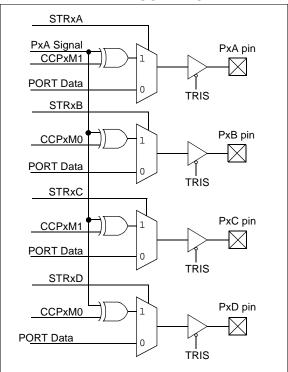

#### 14.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate Steering Enable bits (STRxA, STRxB, STRxC and/or STRxD) of the PSTRxCON register, as shown in Table 14-13.

**Note:** The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the PxD, PxC, PxB and PxA pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 14.4.3** "Enhanced PWM Auto-shutdown Mode". An auto-shutdown event will only affect pins that have PWM outputs enabled.

## FIGURE 14-18: SIMPLIFIED STEERING BLOCK DIAGRAM

Note 1: Port outputs are configured as shown when the CCPxCON register bits PxM<1:0> = 00 and CCPxM<3:2> = 11.

2: Single PWM output requires setting at least one of the STRx bits.

#### 14.4.6.1 Steering Synchronization

The STRxSYNC bit of the PSTRxCON register gives the user two selections of when the steering event will happen. When the STRxSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the PxA, PxB, PxC and PxD pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRxSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figures 14-19 and 14-20 illustrate the timing diagrams of the PWM steering depending on the STRxSYNC setting.

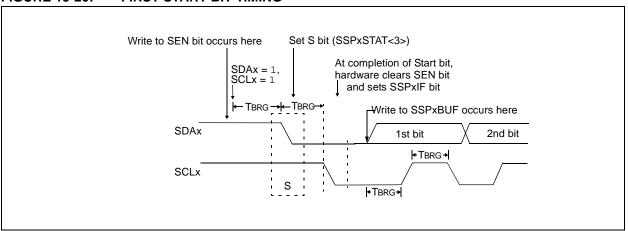

## 15.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 15-26), the user sets the Start Enable bit, SEN, of the SSPxCON2 register. If the SDAx and SCLx pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCLx and SDAx are both sampled high when the Baud Rate Generator times out (TBRG), the SDAx pin is driven low. The action of the SDAx being driven low while SCLx is high is the Start condition and causes the S bit of the SSPxSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count.

When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDAx line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDAx and SCLx pins are already sampled low, or if during the Start condition, the SCLx line is sampled low before the SDAx line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLxIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C Specification states that a bus collision cannot occur on a Start.

FIGURE 15-26: FIRST START BIT TIMING

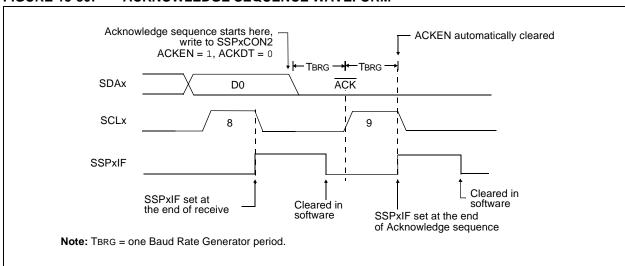

## 15.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN, of the SSPxCON2 register. When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 15-30).

### 15.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

#### 15.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN, of the SSPxCON2 register. At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 15-31).

### 15.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## REGISTER 15-5: SSPxCON3: SSPx CONTROL REGISTER 3 (CONTINUED)

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

- 1 = Following the 8th falling edge of SCLx for a received data byte; slave hardware clears the CKP bit of the SSPxCON1 register and SCLx is held low.

- 0 = Data holding is disabled

- Note 1: For daisy-chained SPI operation; allows the user to ignore all but the last received byte. SSPxOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

- 2: This bit has no effect in Slave modes for which Start and Stop condition detection is explicitly listed as enabled.

- 3: The ACKTIM Status bit is active only when the AHEN bit or DHEN bit is set.

#### REGISTER 15-6: SSPxMSK: SSPx MASK REGISTER

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-1 **MSK<7:1>:** Mask bits

1 = The received address bit n is compared to SSPxADD<n> to detect I<sup>2</sup>C address match

0 = The received address bit n is not used to detect I<sup>2</sup>C address match

bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address

$I^2C$  Slave mode, 10-bit address (SSPxM<3:0> = 0111 or 1111):

1 = The received address bit 0 is compared to SSPxADD<0> to detect I<sup>2</sup>C address match

0 = The received address bit 0 is not used to detect  $I^2C$  address match

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

## 17.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is  $3~\mathrm{k}\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D

acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### **EQUATION 17-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega 3.0V VDD$

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $5\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED} \left( 1 - \frac{1}{2047} \right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED}\left(1-e^{\frac{-TC}{RC}}\right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right)$$

; combining [1] and [2]

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

=  $-13.5pF(1k\Omega + 700\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.20\mu s$

Therefore:

$$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.45\mu s

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

TABLE 25-2: PIC18(L)F2X/4XK22 INSTRUCTION SET (CONTINUED)

| Mnemo     | nic,    | Beautottee                     | 0          | 16-  | Bit Instr | uction W | ord/ | Status      | Neter |

|-----------|---------|--------------------------------|------------|------|-----------|----------|------|-------------|-------|

| Opera     | nds     | Description                    | Cycles     | MSb  |           |          | LSb  | Affected    | Notes |

| BIT-ORIEN | TED OP  | ERATIONS                       |            |      |           |          |      |             |       |

| BCF       | f, b, a | Bit Clear f                    | 1          | 1001 | bbba      | ffff     | ffff | None        | 1, 2  |

| BSF       | f, b, a | Bit Set f                      | 1          | 1000 | bbba      | ffff     | ffff | None        | 1, 2  |

| BTFSC     | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011 | bbba      | ffff     | ffff | None        | 3, 4  |

| BTFSS     | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None        | 3, 4  |

| BTG       | f, b, a | Bit Toggle f                   | 1          | 0111 | bbba      | ffff     | ffff | None        | 1, 2  |

| CONTROL   | OPERA   | TIONS                          |            |      |           |          |      |             |       |

| ВС        | n       | Branch if Carry                | 1 (2)      | 1110 | 0010      | nnnn     | nnnn | None        |       |

| BN        | n       | Branch if Negative             | 1 (2)      | 1110 | 0110      | nnnn     | nnnn | None        |       |

| BNC       | n       | Branch if Not Carry            | 1 (2)      | 1110 | 0011      | nnnn     | nnnn | None        |       |

| BNN       | n       | Branch if Not Negative         | 1 (2)      | 1110 | 0111      | nnnn     | nnnn | None        |       |

| BNOV      | n       | Branch if Not Overflow         | 1 (2)      | 1110 | 0101      | nnnn     | nnnn | None        |       |

| BNZ       | n       | Branch if Not Zero             | 1 (2)      | 1110 | 0001      | nnnn     | nnnn | None        |       |

| BOV       | n       | Branch if Overflow             | 1 (2)      | 1110 | 0100      | nnnn     | nnnn | None        |       |

| BRA       | n       | Branch Unconditionally         | 2          | 1101 | 0nnn      | nnnn     | nnnn | None        |       |

| BZ        | n       | Branch if Zero                 | 1 (2)      | 1110 | 0000      | nnnn     | nnnn | None        |       |

| CALL      | k, s    | Call subroutine 1st word       | 2          | 1110 | 110s      | kkkk     | kkkk | None        |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |             |       |

| CLRWDT    | _       | Clear Watchdog Timer           | 1          | 0000 | 0000      | 0000     | 0100 | TO, PD      |       |

| DAW       | _       | Decimal Adjust WREG            | 1          | 0000 | 0000      | 0000     | 0111 | С           |       |

| GOTO      | k       | Go to address 1st word         | 2          | 1110 | 1111      | kkkk     | kkkk | None        |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |             |       |

| NOP       | _       | No Operation                   | 1          | 0000 | 0000      | 0000     | 0000 | None        |       |

| NOP       | _       | No Operation                   | 1          | 1111 | xxxx      | xxxx     | xxxx | None        | 4     |

| POP       | _       | Pop top of return stack (TOS)  | 1          | 0000 | 0000      | 0000     | 0110 | None        |       |

| PUSH      | _       | Push top of return stack (TOS) | 1          | 0000 | 0000      | 0000     | 0101 | None        |       |

| RCALL     | n       | Relative Call                  | 2          | 1101 | 1nnn      | nnnn     | nnnn | None        |       |

| RESET     |         | Software device Reset          | 1          | 0000 | 0000      | 1111     | 1111 | All         |       |

| RETFIE    | S       | Return from interrupt enable   | 2          | 0000 | 0000      | 0001     | 000s | GIE/GIEH,   |       |

|           |         |                                |            |      |           |          |      | PEIE/GIEL   |       |

| RETLW     | k       | Return with literal in WREG    | 2          | 0000 | 1100      | kkkk     | kkkk | None        |       |

| RETURN    | S       | Return from Subroutine         | 2          | 0000 | 0000      | 0001     | 001s | <u>None</u> |       |

| SLEEP     | _       | Go into Standby mode           | 1          | 0000 | 0000      | 0000     | 0011 | TO, PD      |       |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>4:</sup> Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

### MOVSS Move Indexed to Indexed

Syntax: MOVSS  $[z_s]$ ,  $[z_d]$ Operands:  $0 \le z_s \le 127$   $0 \le z_d \le 127$

Operation:  $((FSR2) + z_s) \rightarrow ((FSR2) + z_d)$

Status Affected: None

Encoding: 1st word (source) 2nd word (dest.)

Description

| INOTIC |      |      |                   |

|--------|------|------|-------------------|

|        |      |      |                   |

|        |      |      |                   |

| 1110   | 1011 | 1zzz | ZZZZc             |

| 1111   |      |      |                   |

| 1111   | XXXX | XZZZ | zzzz <sub>d</sub> |

The contents of the source register are moved to the destination register. The addresses of the source and destination registers are determined by adding the 7-bit literal offsets ' $z_s$ ' or ' $z_d$ ',

respectively, to the value of FSR2. Both registers can be located anywhere in the 4096-byte data memory space

(000h to FFFh).

The  ${\tt MOVSS}$  instruction cannot use the PCL, TOSU, TOSH or TOSL as the

destination register.

If the resultant source address points to an indirect addressing register, the value returned will be 00h. If the resultant destination address points to an indirect addressing register, the instruction will execute as a NOP.

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1     | Q2          | Q3          | Q4          |

|--------|-------------|-------------|-------------|

| Decode | Determine   | Determine   | Read        |

|        | source addr | source addr | source reg  |

| Decode | Determine   | Determine   | Write       |

|        | dest addr   | dest addr   | to dest reg |

Example: MOVSS [05h], [06h]

Before Instruction

FSR2 = 80h Contents of 85h = 33h Contents of 86h = 11h

After Instruction

FSR2 = 80h Contents of 85h = 33h Contents of 86h = 33h PUSHL Store Literal at FSR2, Decrement FSR2

Syntax: PUSHL k

Operands:  $0 \le k \le 255$ Operation:  $k \to (FSR2)$ ,

$FSR2 - 1 \rightarrow FSR2$

Status Affected: None

Encoding: 1111 1010 kkkk kkkk

Description: The 8-bit literal 'k' is written to the data memory address specified by FSR2. FSR2

is decremented by 1 after the operation. This instruction allows users to push values

onto a software stack.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2       | Q3      | Q4          |

|--------|----------|---------|-------------|

| Decode | Read 'k' | Process | Write to    |

|        |          | data    | destination |

Example: PUSHL 08h

Before Instruction

FSR2H:FSR2L = 01ECh Memory (01ECh) = 00h

After Instruction

FSR2H:FSR2L = 01EBh Memory (01ECh) = 08h

## 27.7 DC Characteristics: Secondary Oscillator Supply Current, PIC18(L)F2X/4XK22

| PIC18LF      | PIC18LF2X/4XK22        |     |     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                     |            |                              |  |  |  |

|--------------|------------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------|------------------------------|--|--|--|

| PIC18F2      | PIC18F2X/4XK22         |     |     | <b>erating</b><br>nperatu                                                                                                                  | Conditions (unle<br>re -40°C ≤ TA ≤ |            | tated)                       |  |  |  |

| Param<br>No. | Device Characteristics | Тур | Max | Units                                                                                                                                      | Conditions                          |            |                              |  |  |  |

| D135         |                        | 0.9 | 18  | μΑ                                                                                                                                         | -40°C                               | VDD = 1.8V | Fosc = 32 kHz                |  |  |  |

|              |                        | 1.0 | 18  | μΑ                                                                                                                                         | +25°C                               |            | (SEC_IDLE mode, SOSC source) |  |  |  |

|              |                        | 1.1 | _   | μΑ                                                                                                                                         | +60°C                               |            | 303C source)                 |  |  |  |

|              |                        | 1.3 | 20  | μΑ                                                                                                                                         | +85°C                               |            |                              |  |  |  |

|              |                        | 2.3 | 22  | μΑ                                                                                                                                         | +125°C                              |            |                              |  |  |  |

| D136         |                        | 1.3 | 20  | μΑ                                                                                                                                         | -40°C                               | VDD = 3.0V |                              |  |  |  |

|              |                        | 1.4 | 20  | μΑ                                                                                                                                         | +25°C                               |            |                              |  |  |  |

|              |                        | 1.5 | —   | μΑ                                                                                                                                         | +60°C                               |            |                              |  |  |  |

|              |                        | 1.8 | 22  | μΑ                                                                                                                                         | +85°C                               |            |                              |  |  |  |

|              |                        | 2.9 | 25  | μΑ                                                                                                                                         | +125°C                              |            |                              |  |  |  |

| D137         |                        | 12  | 30  | μΑ                                                                                                                                         | -40°C                               | VDD = 2.3V | Fosc = 32 kHz                |  |  |  |

|              |                        | 13  | 30  | μΑ                                                                                                                                         | +25°C                               |            | (SEC_IDLE mode, SOSC source) |  |  |  |

|              |                        | 14  | 30  | μΑ                                                                                                                                         | +85°C                               |            | 303C source)                 |  |  |  |

|              |                        | 16  | 45  | μΑ                                                                                                                                         | +125°C                              |            |                              |  |  |  |

| D138         |                        | 13  | 35  | μΑ                                                                                                                                         | -40°C                               | VDD = 3.0V |                              |  |  |  |

|              |                        | 14  | 35  | μΑ                                                                                                                                         | +25°C                               |            |                              |  |  |  |

|              |                        | 16  | 35  | μΑ                                                                                                                                         | +85°C                               |            |                              |  |  |  |

|              |                        | 18  | 50  | μΑ                                                                                                                                         | +125°C                              |            |                              |  |  |  |

| D139         |                        | 14  | 40  | μΑ                                                                                                                                         | -40°C                               | VDD = 5.0V |                              |  |  |  |

|              |                        | 15  | 40  | μΑ                                                                                                                                         | +25°C                               |            |                              |  |  |  |

|              |                        | 16  | 40  | μΑ                                                                                                                                         | +85°C                               |            |                              |  |  |  |

|              |                        | 18  | 60  | μΑ                                                                                                                                         | +125°C                              |            |                              |  |  |  |

Note 1: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

Test condition: All Peripheral Module Control bits in PMD0, PMD1 and PMD2 set to '1'.

2: The test conditions for all IDD measurements in active operation mode are:

All I/O pins set as outputs driven to Vss;

$\overline{MCLR} = VDD;$

SOSCI / SOSCO = complementary external square wave, from rail-to-rail.

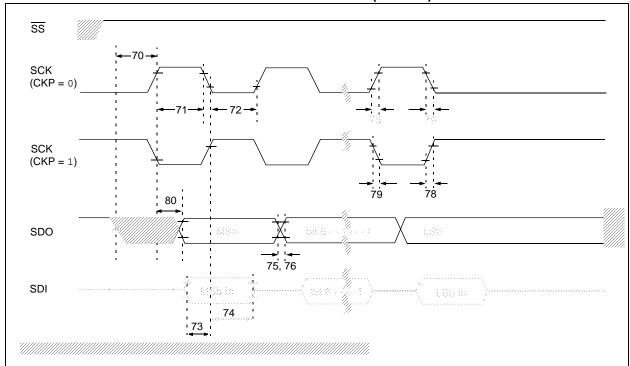

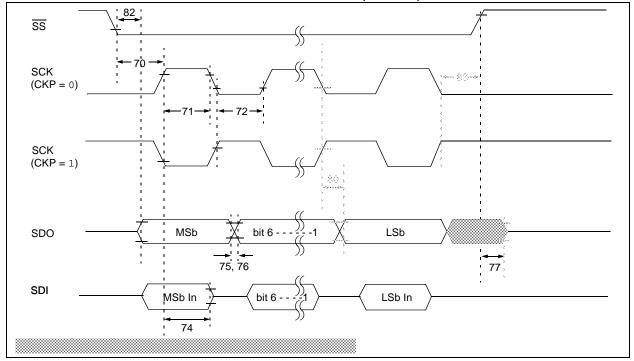

FIGURE 27-13: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

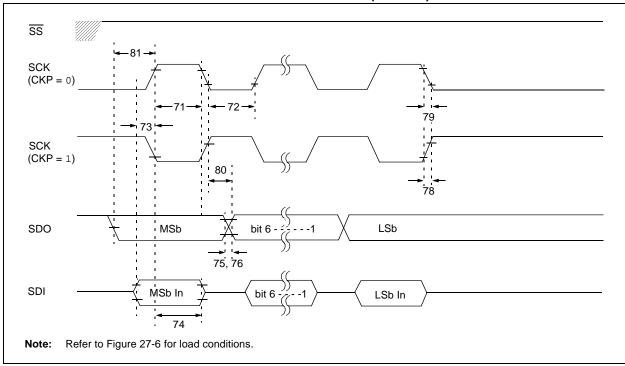

FIGURE 27-14: EXAMPLE SPI MASTER MODE TIMING (CKE = 1)

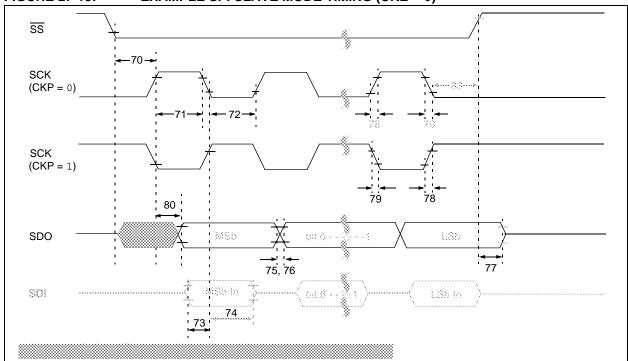

FIGURE 27-15: EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)

FIGURE 27-16: EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

TABLE 27-21: A/D CONVERTER CHARACTERISTICS:PIC18(L)F2X/4XK22

| PIC18(L)F2X/4XK22 |               |                                                   | Standard Op<br>Operating ter | _    | •         | inless of<br>at +25° | otherwise stated)<br>C |

|-------------------|---------------|---------------------------------------------------|------------------------------|------|-----------|----------------------|------------------------|

| Param.<br>No.     | Symbol        | Characteristic                                    | Min                          | Тур  | Max       | Units                | Conditions             |

| A01               | NR            | Resolution                                        | _                            | _    | 10        | bits                 | $\Delta VREF = 3.0V$   |

| A03               | EIL           | Integral Linearity Error                          | _                            | ±0.5 | ±1        | LSb                  | $\Delta$ VREF = 3.0V   |

| A04               | EDL           | Differential Linearity Error                      | _                            | ±0.5 | ±1        | LSb                  | $\Delta VREF = 3.0V$   |

| A06               | EOFF          | Offset Error                                      | _                            | ±0.7 | ±2        | LSb                  | $\Delta VREF = 3.0V$   |

| A07               | Egn           | Gain Error                                        | _                            | ±0.7 | ±2        | LSb                  | $\Delta VREF = 3.0V$   |

| A08               | ETOTL         | Total Error                                       | _                            | ±0.8 | ±3        | LSb                  | $\Delta VREF = 3.0V$   |

| A20               | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL)        | 2                            | _    | VDD       | V                    |                        |

| A21               | VREFH         | Reference Voltage High                            | VDD/2                        | _    | VDD + 0.3 | V                    |                        |

| A22               | VREFL         | Reference Voltage Low                             | Vss - 0.3V                   | _    | VDD/2     | V                    |                        |

| A25               | VAIN          | Analog Input Voltage                              | VREFL                        | _    | VREFH     | V                    |                        |

| A30               | ZAIN          | Recommended Impedance of<br>Analog Voltage Source | _                            | _    | 3         | kΩ                   |                        |

Note: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

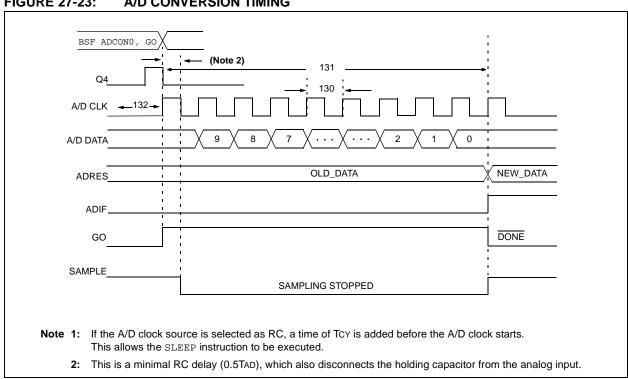

#### FIGURE 27-23: A/D CONVERSION TIMING

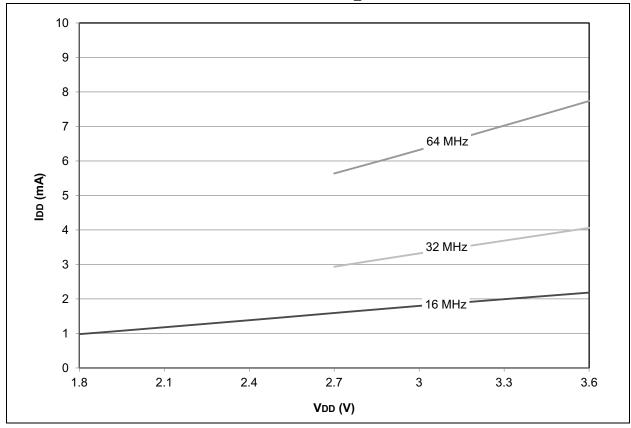

FIGURE 28-56: PIC18LF2X/4XK22 TYPICAL IDD: PRI\_RUN EC with PLL

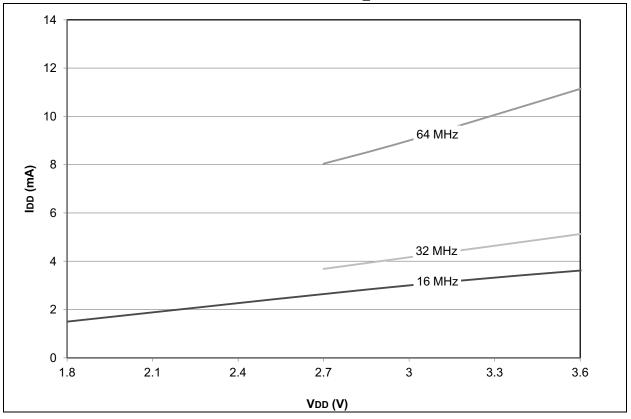

FIGURE 28-57: PIC18LF2X/4XK22 MAXIMIUM IDD: PRI\_RUN EC with PLL

## 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |           | MILLIMETERS |      |  |

|------------------------|-------|-----------|-------------|------|--|

| Dimension Limits       |       | MIN       | NOM         | MAX  |  |

| Number of Pins         | N     | 28        |             |      |  |

| Pitch                  | е     | 0.40 BSC  |             |      |  |

| Overall Height         | Α     | 0.45      | 0.50        | 0.55 |  |

| Standoff               | A1    | 0.00      | 0.02        | 0.05 |  |

| Contact Thickness      | A3    | 0.127 REF |             |      |  |

| Overall Width          | Е     | 4.00 BSC  |             |      |  |

| Exposed Pad Width      | E2    | 2.55      | 2.65        | 2.75 |  |

| Overall Length         | О     | 4.00 BSC  |             |      |  |

| Exposed Pad Length     | D2    | 2.55      | 2.65        | 2.75 |  |

| Contact Width          | b     | 0.15      | 0.20        | 0.25 |  |

| Contact Length         | Г     | 0.30      | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | K     | 0.20      | -           | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2