Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f23k22t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.2 Other Special Features

- Memory Endurance: The Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles up to 10K for program memory and 100K for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

- Extended Instruction Set: The PIC18(L)F2X/ 4XK22 family introduces an optional extension to the PIC18 instruction set, which adds eight new instructions and an Indexed Addressing mode. This extension, enabled as a device configuration option, has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

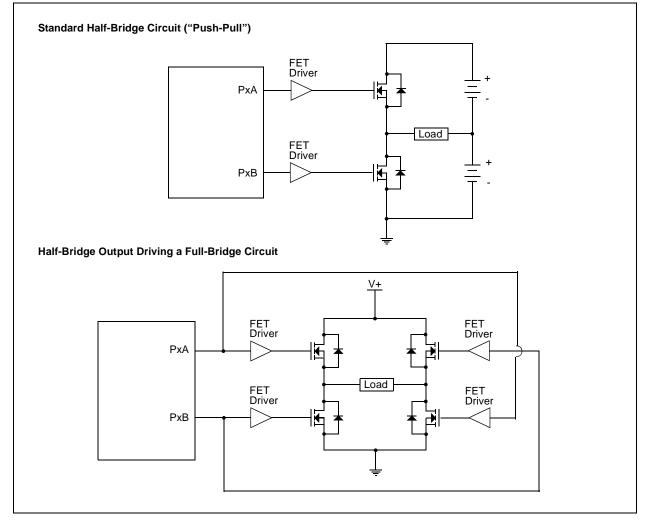

- Enhanced CCP module: In PWM mode, this module provides one, two or four modulated outputs for controlling half-bridge and full-bridge drivers. Other features include:

- Auto-Shutdown, for disabling PWM outputs on interrupt or other select conditions

- Auto-Restart, to reactivate outputs once the condition has cleared

- Output steering to selectively enable one or more of four outputs to provide the PWM signal.

- Enhanced Addressable EUSART: This serial communication module is capable of standard RS-232 operation and provides support for the LIN bus protocol. Other enhancements include automatic baud rate detection and a 16-bit Baud Rate Generator for improved resolution. When the microcontroller is using the internal oscillator block, the EUSART provides stable operation for applications that talk to the outside world without using an external crystal (or its accompanying power requirement).

- **10-bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduce code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit postscaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 27.0 "Electrical Specifications" for time-out periods.

- Charge Time Measurement Unit (CTMU)

- SR Latch Output:

# 1.3 Details on Individual Family Members

Devices in the PIC18(L)F2X/4XK22 family are available in 28-pin and 40/44-pin packages. The block diagram for the device family is shown in Figure 1-1.

The devices have the following differences:

- 1. Flash program memory

- 2. Data Memory SRAM

- 3. Data Memory EEPROM

- 4. A/D channels

- 5. I/O ports

- 6. ECCP modules (Full/Half Bridge)

- 7. Input Voltage Range/Power Consumption

All other features for devices in this family are identical. These are summarized in Table 1-1.

The pinouts for all devices are listed in the pin summary tables: Table 2 and Table 3, and I/O description tables: Table 1-2 and Table 1-3.

# 2.2 Oscillator Control

The OSCCON, OSCCON2 and OSCTUNE registers (Register 2-1 to Register 2-3) control several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

- Main System Clock Selection (SCS)

- Primary Oscillator Circuit Shutdown (PRISD)

- Secondary Oscillator Enable (SOSCGO)

- Primary Clock Frequency 4x multiplier (PLLEN)

- Internal Frequency selection bits (IRCF, INTSRC)

- Clock Status bits (OSTS, HFIOFS, MFIOFS, LFIOFS. SOSCRUN, PLLRDY)

- Power management selection (IDLEN)

## 2.2.1 MAIN SYSTEM CLOCK SELECTION

The System Clock Select bits, SCS<1:0>, select the main clock source. The available clock sources are

- Primary clock defined by the FOSC<3:0> bits of CONFIG1H. The primary clock can be the primary oscillator, an external clock, or the internal oscillator block.

- Secondary clock (secondary oscillator)

- Internal oscillator block (HFINTOSC, MFINTOSC and LFINTOSC).

The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared to select the primary clock on all forms of Reset.

### 2.2.2 INTERNAL FREQUENCY SELECTION

The Internal Oscillator Frequency Select bits (IRCF<2:0>) select the frequency output of the internal oscillator block. The choices are the LFINTOSC source (31.25 kHz), the MFINTOSC source (31.25 kHz, 250 kHz or 500 kHz) and the HFINTOSC source (16 MHz) or one of the frequencies derived from the HFINTOSC postscaler (31.25 kHz to 8 MHz). If the internal oscillator block is supplying the main clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the output frequency of the internal oscillator is set to the default frequency of 1 MHz.

# 2.2.3 LOW FREQUENCY SELECTION

When a nominal output frequency of 31.25 kHz is selected (IRCF<2:0> = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit of the OSCTUNE register and MFIOSEL bit of the OSCCON2 register. See Figure 2-2 and Register 2-1 for specific 31.25 kHz selection. This option allows users to select a 31.25 kHz clock (MFINTOSC or HFINTOSC) that can be tuned using the TUN<5:0> bits in OSCTUNE register, while maintaining power savings with a very low clock speed. LFINTOSC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor, regardless of the setting of INTSRC and MFIOSEL bits

This option allows users to select the tunable and more precise HFINTOSC as a clock source, while maintaining power savings with a very low clock speed.

# 2.2.4 POWER MANAGEMENT

The IDLEN bit of the OSCCON register determines whether the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

TABLE 2-4: REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7    | Bit 6     | Bit 5     | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|-----------|-----------|---------|---------|--------|--------|--------|---------------------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE    | INT0IE  | RBIE    | TMR0IF | INTOIF | RBIF   | 109                 |

| IPR2    | OSCFIP   | C1IP      | C2IP      | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 122                 |

| OSCCON  | IDLEN    |           | IRCF<2:0> |         | OSTS    | HFIOFS | SCS    | 30     |                     |

| OSCCON2 | PLLRDY   | SOSCRUN   | —         | MFIOSEL | SOSCGO  | PRISD  | MFIOFS | LFIOFS | 31                  |

| OSCTUNE | INTSRC   | PLLEN     |           |         | TUN<5:( | )>     |        |        | 35                  |

| PIE2    | OSCFIE   | C1IE      | C2IE      | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 118                 |

| PIR2    | OSCFIF   | C1IF      | C2IF      | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 113                 |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by clock sources.

TABLE 2-5: CONFIGURATION REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name     | Bit 7 | Bit 6 | Bit 5    | Bit 4 Bit 3 |           | Bit 2  | Bit 1      | Bit 0  | Register<br>on Page |

|----------|-------|-------|----------|-------------|-----------|--------|------------|--------|---------------------|

| CONFIG1H | IESO  | FCMEN | PRICLKEN | PLLCFG      |           |        | 345        |        |                     |

| CONFIG2L | —     | —     | _        | BORV        | BORV<1:0> |        | BOREN<1:0> |        | 346                 |

| CONFIG3H | MCLRE | _     | P2BMX    | T3CMX       | HFOFST    | CCP3MX | PBADEN     | CCP2MX | 348                 |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for clock sources.

# PIC18(L)F2X/4XK22

| R/W-0           | R/W-0         | U-0                                                | R/W-0          | R/W-0            | R/W-0                               | R/W-0           | R/W-0  |  |  |  |  |

|-----------------|---------------|----------------------------------------------------|----------------|------------------|-------------------------------------|-----------------|--------|--|--|--|--|

| MSSP2MD         | MSSP1MD       | _                                                  | CCP5MD         | CCP4MD           | CCP3MD                              | CCP2MD          | CCP1MD |  |  |  |  |

| bit 7           |               |                                                    |                |                  |                                     |                 | bit (  |  |  |  |  |

| Legend:         |               |                                                    |                |                  |                                     |                 |        |  |  |  |  |

| R = Readable    | bit           | W = Writable                                       | bit            | U = Unimpler     | mented bit, read                    | d as '0'        |        |  |  |  |  |

| -n = Value at F | POR           | '1' = Bit is set                                   |                | '0' = Bit is cle | ared                                | x = Bit is unkr | nown   |  |  |  |  |

| bit 7           | MSSP2MD: N    | ISSP2 Periphe                                      | eral Module Di | sable Control I  | bit                                 |                 |        |  |  |  |  |

|                 | 1 = Module is | s disabled, Clo                                    | ck Source is d | lisconnected, r  | nodule does no<br>lule draws digita | 0 1             | ower   |  |  |  |  |

| bit 6           | MSSP1MD: N    | ISSP1 Periphe                                      | eral Module Di | sable Control I  | bit                                 |                 |        |  |  |  |  |

|                 |               |                                                    |                |                  | nodule does no<br>lule draws digita | • •             | ower   |  |  |  |  |

| bit 5           | Unimplemen    | ted: Read as '                                     | 0'             |                  |                                     |                 |        |  |  |  |  |

| bit 4           | CCP5MD: CC    | P5 Peripheral                                      | Module Disab   | ole Control bit  |                                     |                 |        |  |  |  |  |

|                 |               |                                                    |                |                  | nodule does no<br>lule draws digita | 0 1             | ower   |  |  |  |  |

| bit 3           | CCP4MD: CC    | CCP4MD: CCP4 Peripheral Module Disable Control bit |                |                  |                                     |                 |        |  |  |  |  |

|                 |               |                                                    |                |                  | nodule does no<br>lule draws digita |                 | ower   |  |  |  |  |

| bit 2           | CCP3MD: CC    | P3 Peripheral                                      | Module Disab   | le Control bit   |                                     |                 |        |  |  |  |  |

|                 |               |                                                    |                | ,                | nodule does no<br>lule draws digita | 0 1             | ower   |  |  |  |  |

| bit 1           | CCP2MD: CC    | P2 Peripheral                                      | Module Disab   | le Control bit   |                                     |                 |        |  |  |  |  |

|                 |               |                                                    |                |                  | nodule does no<br>lule draws digita | • .             | ower   |  |  |  |  |

| bit 0           | CCP1MD: CC    | P1 Peripheral                                      | Module Disab   | ole Control bit  |                                     |                 |        |  |  |  |  |

|                 |               |                                                    |                |                  | nodule does no<br>lule draws digita | 0 1             | ower   |  |  |  |  |

|                 |               |                                                    |                |                  |                                     |                 |        |  |  |  |  |

| R/W-1         | R/W-1                                           | R/W-1                       | R/W-1            | R/W-1            | R/W-1            | R/W-1           | R/W-1  |

|---------------|-------------------------------------------------|-----------------------------|------------------|------------------|------------------|-----------------|--------|

| OSCFIP        | C1IP                                            | C2IP                        | EEIP             | BCL1IP           | HLVDIP           | TMR3IP          | CCP2IP |

| bit 7         | ÷                                               | ·                           |                  | •                |                  | •               | bit (  |

| Legend:       |                                                 |                             |                  |                  |                  |                 |        |

| R = Readabl   | e bit                                           | W = Writable                | bit              | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at | POR                                             | '1' = Bit is set            | :                | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

| bit 7         | <b>OSCFIP:</b> O<br>1 = High pr<br>0 = Low pri  | •                           | rrupt Priority I | bit              |                  |                 |        |

| bit 6         | <b>C1IP:</b> Comp<br>1 = High pr<br>0 = Low pri |                             | upt Priority bit |                  |                  |                 |        |

| bit 5         | <b>C2IP:</b> Comp<br>1 = High pr<br>0 = Low pri |                             | upt Priority bit | :                |                  |                 |        |

| bit 4         | EEIP: Data<br>1 = High pr<br>0 = Low pri        | •                           | Write Operat     | ion Interrupt Pr | iority bit       |                 |        |

| bit 3         | <b>BCL1IP:</b> M3<br>1 = High pr<br>0 = Low pri |                             | ion Interrupt F  | Priority bit     |                  |                 |        |

| bit 2         | <b>HLVDIP:</b> Lo<br>1 = High pr<br>0 = Low pri |                             | ct Interrupt Pri | ority bit        |                  |                 |        |

| bit 1         | -                                               | MR3 Overflow In<br>iority   | terrupt Priority | / bit            |                  |                 |        |

| bit 0         |                                                 | CP2 Interrupt Pri<br>iority | ority bit        |                  |                  |                 |        |

### REGISTER 9-15: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

## TABLE 10-14: PORTE I/O SUMMARY

| Pin              | Function            | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type                                     | Description                                                                             |

|------------------|---------------------|-----------------|------------------|-------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|

| RE0/P3A/CCP3/AN5 | RE0                 | 0               | 0                | 0           | DIG                                                | LATE<0> data output; not affected by analog input.                                      |

|                  |                     | 1               | 0                | I           | ST                                                 | PORTE<0> data input; disabled when analog input<br>enabled.                             |

|                  | P3A <sup>(1)</sup>  | 0               | 0                | 0           | DIG                                                | Enhanced CCP3 PWM output.                                                               |

|                  | CCP3 <sup>(1)</sup> | 0               | 0                | 0           | DIG                                                | Compare 3 output/PWM 3 output.                                                          |

|                  |                     | 1               | 0                | I           | ST                                                 | Capture 3 input.                                                                        |

|                  | AN5                 |                 |                  |             |                                                    | Analog input 5.                                                                         |

| RE1/P3B/AN6      | 0                   | 0               | 0                | DIG         | LATE<1> data output; not affected by analog input. |                                                                                         |

|                  |                     | 1               | 0                | I           | ST                                                 | PORTE<1> data input; disabled when analog input<br>enabled.                             |

|                  | P3B                 | 0               | 0                | 0           | DIG                                                | Enhanced CCP3 PWM output.                                                               |

|                  | AN6                 | 1               | 1                | -           | AN                                                 | Analog input 6.                                                                         |

| RE2/CCP5/AN7     | RE2                 | 0               | 0                | 0           | DIG                                                | LATE<2> data output; not affected by analog input.                                      |

|                  |                     | 1               | 0                | Ι           | ST                                                 | PORTE<2> data input; disabled when analog input<br>enabled.                             |

|                  | CCP5                | 0               | 0                | 0           | DIG                                                | Compare 5 output/PWM 5 output.                                                          |

|                  |                     | 1               | 0                | -           | ST                                                 | Capture 5 input.                                                                        |

|                  | AN7                 | 1               | 1                | -           | AN                                                 | Analog input 7.                                                                         |

| RE3/VPP/MCLR     | RE3                 | _               | _                | Ι           | ST                                                 | PORTE<3> data input; enabled when Configuration bit<br>MCLRE = 0.                       |

|                  | Vpp                 | _               | —                | Р           | AN                                                 | Programming voltage input; always available                                             |

|                  | MCLR                | _               | _                | Ι           | ST                                                 | Active-low Master Clear (device Reset) input; enabled when configuration bit MCLRE = 1. |

Legend:AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS =<br/>CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

**Note 1:** Alternate pin assignment for P3A/CCP3 when Configuration bit CCP3MX is clear.

| Name                 | Bit 7   | Bit 6   | Bit 5           | Bit 4           | Bit 3              | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|---------|---------|-----------------|-----------------|--------------------|-----------------------|-----------------------|-----------------------|---------------------|

| IPR2                 | OSCFIP  | C1IP    | C2IP            | EEIP            | BCL1IP             | HLVDIP                | TMR3IP                | CCP2IP                | 122                 |

| IPR4                 | —       | —       | —               | —               | _                  | CCP5IP                | CCP4IP                | CCP3IP                | 124                 |

| PIE1                 | —       | ADIE    | RC1IE           | TX1IE           | SSP1IE             | CCP1IE                | TMR2IE                | TMR1IE                | 117                 |

| PIE2                 | OSCFIE  | C1IE    | C2IE            | EEIE            | BCL1IE             | HLVDIE                | TMR3IE                | CCP2IE                | 118                 |

| PIE4                 | —       | —       | —               | —               |                    | CCP5IE                | CCP4IE                | CCP3IE                | 120                 |

| PIR1                 | —       | ADIF    | RC1IF           | TX1IF           | SSP1IF             | CCP1IF                | TMR2IF                | TMR1IF                | 112                 |

| PIR2                 | OSCFIF  | C1IF    | C2IF            | EEIF            | BCL1IF             | HLVDIF                | TMR3IF                | CCP2IF                | 113                 |

| PIR4                 | —       | —       | —               | —               | —                  | CCP5IF                | CCP4IF                | CCP3IF                | 115                 |

| PMD0                 | UART2MD | UART1MD | TMR6MD          | TMR5MD          | TMR4MD             | TMR3MD                | TMR2MD                | TMR1MD                | 52                  |

| PMD1                 | MSSP2MD | MSSP1MD | —               | CCP5MD          | CCP4MD             | CCP3MD                | CCP2MD                | CCP1MD                | 53                  |

| T1CON                | TMR10   | CS<1:0> | T1CKP           | S<1:0>          | T1SOSCEN           | T1SYNC                | T1RD16                | TMR10N                | 166                 |

| T1GCON               | TMR1GE  | T1GPOL  | T1GTM           | T1GSPM          | T1GGO/DONE         | T1GVAL                | T1GSS<1:0>            |                       | 167                 |

| T3CON                | TMR30   | CS<1:0> | T3CKP           | S<1:0>          | T3SOSCEN           | T3SYNC                | T3RD16                | T3RD16 TMR3ON         |                     |

| T3GCON               | TMR3GE  | T3GPOL  | T3GTM           | T3GSPM          | T3GGO/DONE         | T3GVAL                | T3GSS                 | 167                   |                     |

| T5CON                | TMR50   | CS<1:0> | T5CKP           | S<1:0>          | T5SOSCEN           | T5SYNC                | T5RD16                | TMR5ON                | 166                 |

| T5GCON               | TMR5GE  | T5GPOL  | T5GTM           | T5GSPM          | T5GGO/DONE         | T5GVAL                | T5GSS                 | S<1:0>                | 167                 |

| TMR1H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR1 R          | egister               |                       | _                   |

| TMR1L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR1    | Register              |                       |                       |                     |

| TMR3H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR3 R          | egister               |                       | _                   |

| TMR3L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR3    | Register              |                       |                       | _                   |

| TMR5H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR5 R          | egister               |                       | _                   |

| TMR5L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR5    | Register              |                       |                       | _                   |

| TRISA                | TRISA7  | TRISA6  | TRISA5          | TRISA4          | TRISA3             | TRISA2                | TRISA1                | TRISA0                | 151                 |

| TRISB                | TRISB7  | TRISB6  | TRISB5          | TRISB4          | TRISB3             | TRISB2                | TRISB1                | TRISB0                | 151                 |

| TRISC                | TRISC7  | TRISC6  | TRISC5          | TRISC4          | TRISC3             | TRISC2                | TRISC1                | TRISC0                | 151                 |

| TRISD <sup>(1)</sup> | TRISD7  | TRISD6  | TRISD5          | TRISD4          | TRISD3             | TRISD2                | TRISD1                | TRISD0                | 151                 |

| TRISE                | WPUE3   | _       | —               | _               | —                  | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                 |

| TABLE 14-5: | <b>REGISTERS ASSOCIATED WITH COMPARE (</b> | CONTINUED) | ) |

|-------------|--------------------------------------------|------------|---|

|-------------|--------------------------------------------|------------|---|

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

Note 1: These registers/bits are available on PIC18(L)F4XK22 devices.

TABLE 14-6: CONFIGURATION REGISTERS ASSOCIATED WITH COMPARE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|---------------------|

| CONFIG3H | MCLRE | _     | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                 |

Legend: — = Unimplemented location, read as '0'. Shaded bits are not used by Compare mode.

- 6. Configure and start the 8-bit TimerX resource:

- Clear the TMRxIF interrupt flag bit of the PIR2 or PIR4 register. See Note 1 below.

- Configure the TxCKPS bits of the TxCON register with the Timer prescale value.

- Enable the Timer by setting the TMRxON bit of the TxCON register.

- 7. Enable PWM output pin:

- Wait until the Timer overflows and the TMRxIF bit of the PIR2 or PIR4 register is set. See Note 1 below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

| Note 1: | In order to send a complete duty cycle         |

|---------|------------------------------------------------|

|         | and period on the first PWM output, the        |

|         | above steps must be included in the            |

|         | setup sequence. If it is not critical to start |

|         | with a complete PWM signal on the first        |

|         | output, then step 6 may be ignored.            |

# 14.3.3 PWM TIMER RESOURCE

The PWM standard mode makes use of one of the 8-bit Timer2/4/6 timer resources to specify the PWM period.

Configuring the CxTSEL<1:0> bits in the CCPTMRS0 or CCPTMRS1 register selects which Timer2/4/6 timer is used.

# 14.3.4 PWM PERIOD

The PWM period is specified by the PRx register of 8-bit TimerX. The PWM period can be calculated using the formula of Equation 14-1.

# EQUATION 14-1: PWM PERIOD

$PWM Period = [(PRx) + 1] \bullet 4 \bullet Tosc \bullet$ (TMRx Prescale Value)

Note 1: Tosc = 1/Fosc

When TMRx is equal to PRx, the following three events occur on the next increment cycle:

- TMRx is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPRxL into CCPRxH.

Note: The Timer postscaler (see Section 13.0 "Timer2/4/6 Module") is not used in the determination of the PWM frequency.

# 14.3.5 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPRxL register and DCxB<1:0> bits of the CCPxCON register. The CCPRxL contains the eight MSbs and the DCxB<1:0> bits of the CCPxCON register contain the two LSbs. CCPRxL and DCxB<1:0> bits of the CCPxCON register can be written to at any time. The duty cycle value is not latched into CCPRxH until after the period completes (i.e., a match between PRx and TMRx registers occurs). While using the PWM, the CCPRxH register is read-only.

Equation 14-2 is used to calculate the PWM pulse width.

Equation 14-3 is used to calculate the PWM duty cycle ratio.

# EQUATION 14-2: PULSE WIDTH

$$Pulse Width = (CCPRxL:CCPxCON < 5:4>) \bullet$$

TOSC • (TMRx Prescale Value)

# EQUATION 14-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxL:CCPxCON < 5:4>)}{4(PRx + 1)}$

The CCPRxH register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMRx register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the TimerX prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH and 2-bit latch, then the CCPx pin is cleared (see Figure 14-4).

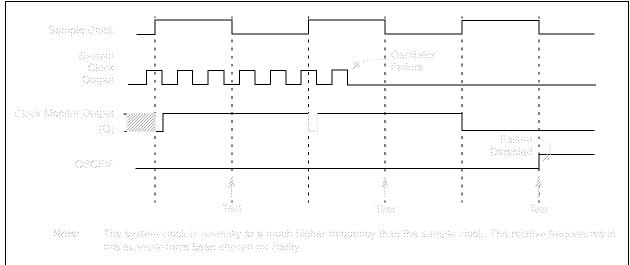

## 14.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 14-9). This mode can be used for half-bridge applications, as shown in Figure 14-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in halfbridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 14.4.5 "Programmable Dead-Band Delay Mode"** for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

#### FIGURE 14-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

## FIGURE 14-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

# 16.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 16-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 16.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 16-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREGx register.

#### 16.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTAx register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTAx register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTAx register enables the EUSART and automatically configures the TXx/CKx I/O pin as an output. If the TXx/CKx pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF transmitter interrupt flag is set when the TXEN enable bit is set.

## 16.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREGx register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREGx is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREGx until the Stop bit of the previous character has been transmitted. The pending character in the TXREGx is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREGx.

#### 16.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the CKTXP bit of the BAUDCONx register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the CKTXP bit to '1' will invert the transmit data resulting in low true idle and data bits. The CKTXP bit controls transmit data polarity only in Asynchronous mode. In Synchronous mode the CKTXP bit has a different function.

#### 16.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR1/PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREGx. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREGx. The TXxIF flag bit is not cleared immediately upon writing TXREGx. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXREGx write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE1/PIE3 register. However, the TXxIF flag bit will be set whenever the TXREGx is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXREGx.

| R/W-0           | R-1                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0           | R/W-0            | U-0                           | R/W-0            | R/W-0             |  |  |  |  |

|-----------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-------------------------------|------------------|-------------------|--|--|--|--|

| ABDOVF          | RCIDL                                                          | DTRXP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CKTXP           | BRG16            | —                             | WUE              | ABDEN             |  |  |  |  |

| bit 7           |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  | bit (             |  |  |  |  |

|                 |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

| Legend:         | 1.5                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               | (0)              |                   |  |  |  |  |

| R = Readable    |                                                                | W = Writable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Dit             | -                | nented bit, read a            |                  |                   |  |  |  |  |

| -n = Value at I | POR                                                            | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | '0' = Bit is cle | ared                          | x = Bit is unkn  | IOWN              |  |  |  |  |

| bit 7           |                                                                | to-Baud Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Overflow bit    |                  |                               |                  |                   |  |  |  |  |

|                 | Asynchronou                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | d timer overflowe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ed              |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | d timer did not o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | verflow         |                  |                               |                  |                   |  |  |  |  |

|                 | <u>Synchronous</u><br>Don't care                               | <u>mode</u> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                  |                               |                  |                   |  |  |  |  |

| bit 6           |                                                                | ive Idle Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |                               |                  |                   |  |  |  |  |

|                 | Asynchronou                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                  |                               |                  |                   |  |  |  |  |

|                 | 1 = Receiver                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 | 0 = Start bit h<br>Synchronous                                 | as been detecte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | d and the rece  | eiver is active  |                               |                  |                   |  |  |  |  |

|                 | Don't care                                                     | <u>mode</u> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                  |                               |                  |                   |  |  |  |  |

| bit 5           | DTRXP: Data                                                    | Receive Polarit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | y Select bit    |                  |                               |                  |                   |  |  |  |  |

|                 | <u>Asynchronou</u>                                             | <u>s mode</u> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | lata (RXx) is inv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | ,                |                               |                  |                   |  |  |  |  |

|                 | 0 = Receive of Synchronous                                     | lata (RXx) is not<br>mode <sup>.</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Inverted (activ | /e-nign)         |                               |                  |                   |  |  |  |  |

|                 |                                                                | x) is inverted (ac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tive-low)       |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | x) is not inverted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                  |                               |                  |                   |  |  |  |  |

| bit 4           | CKTXP: Cloc                                                    | k/Transmit Polar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rity Select bit |                  |                               |                  |                   |  |  |  |  |

|                 | Asynchronou                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | for transmit (TX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,               |                  |                               |                  |                   |  |  |  |  |

|                 | 0 = Idle state for transmit (TXx) is high<br>Synchronous mode: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0             |                  | mpled on the risi             | 0 0              |                   |  |  |  |  |

|                 | 0 = Data char                                                  | nges on the risin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | g edge of the   | clock and is sar | npled on the falli            | ng edge of the c | clock             |  |  |  |  |

| bit 3           |                                                                | it Baud Rate Ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                               |                  |                   |  |  |  |  |

|                 |                                                                | aud Rate Genera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  | GX)                           |                  |                   |  |  |  |  |

| bit 2           |                                                                | ted: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | ,                |                               |                  |                   |  |  |  |  |