Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f23k22t-i-ss |

- Two Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) modules:

- Supports RS-485, RS-232 and LIN

- RS-232 operation using internal oscillator

- Auto-Wake-up on Break

- Auto-Baud Detect

TABLE 1: PIC18(L)F2X/4XK22 FAMILY TYPES

|                | _                | gram<br>nory                  |                 | ata<br>nory       |        | S <sup>(2)</sup>                      |     | (e)                   | (e)                   | MSSP |                  |        | J.         |      |         |          |             | 7            |

|----------------|------------------|-------------------------------|-----------------|-------------------|--------|---------------------------------------|-----|-----------------------|-----------------------|------|------------------|--------|------------|------|---------|----------|-------------|--------------|

| Device         | Flash<br>(Bytes) | # Single-Word<br>Instructions | SRAM<br>(Bytes) | EEPROM<br>(Bytes) | 1/0(1) | 10-bit<br>A/D Channels <sup>(2)</sup> | doo | ECCP<br>(Full-Bridge) | ECCP<br>(Half-Bridge) | IdS  | 1 <sup>2</sup> C | EUSART | Comparator | СТМU | BOR/LVD | SR Latch | 8-bit Timer | 16-bit Timer |

| PIC18(L)F23K22 | 8K               | 4096                          | 512             | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F24K22 | 16K              | 8192                          | 768             | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F25K22 | 32K              | 16384                         | 1536            | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F26K22 | 64k              | 32768                         | 3896            | 1024              | 25     | 19                                    | 2   | 1                     | 2                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F43K22 | 8K               | 4096                          | 512             | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F44K22 | 16K              | 8192                          | 768             | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F45K22 | 32K              | 16384                         | 1536            | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F46K22 | 64k              | 32768                         | 3896            | 1024              | 36     | 30                                    | 2   | 2                     | 1                     | 2    | 2                | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

Note 1: One pin is input only.

<sup>2:</sup> Channel count includes internal FVR and DAC channels.

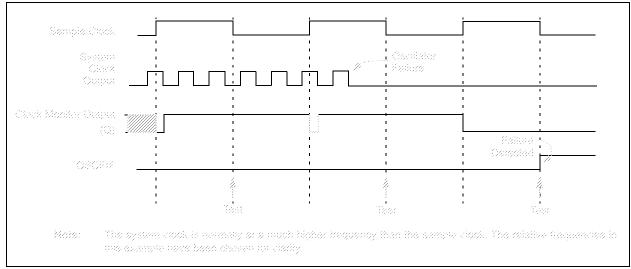

FIGURE 2-11: FSCM TIMING DIAGRAM

TABLE 2-4: REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7    | Bit 6     | Bit 5     | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|---------|----------|-----------|-----------|---------|---------|--------|--------|--------|------------------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE    | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 109              |

| IPR2    | OSCFIP   | C1IP      | C2IP      | EEIP    | BCL1IP  | HLVDIP | TMR3IP | CCP2IP | 122              |

| OSCCON  | IDLEN    |           | IRCF<2:0> |         |         | HFIOFS | SCS    | 30     |                  |

| OSCCON2 | PLLRDY   | SOSCRUN   | _         | MFIOSEL | SOSCGO  | PRISD  | MFIOFS | LFIOFS | 31               |

| OSCTUNE | INTSRC   | PLLEN     |           |         | TUN<5:0 | )>     |        |        | 35               |

| PIE2    | OSCFIE   | C1IE      | C2IE      | EEIE    | BCL1IE  | HLVDIE | TMR3IE | CCP2IE | 118              |

| PIR2    | OSCFIF   | C1IF      | C2IF      | EEIF    | BCL1IF  | HLVDIF | TMR3IF | CCP2IF | 113              |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used by clock sources.

TABLE 2-5: CONFIGURATION REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name     | Bit 7 | Bit 6 | Bit 5    | Bit 4  | Bit 3     | Bit 2 Bit 1 |        | Bit 0  | Register on Page |

|----------|-------|-------|----------|--------|-----------|-------------|--------|--------|------------------|

| CONFIG1H | IESO  | FCMEN | PRICLKEN | PLLCFG |           | 345         |        |        |                  |

| CONFIG2L | _     | _     | _        | BORV   | BORV<1:0> |             | N<1:0> | PWRTEN | 346              |

| CONFIG3H | MCLRE | -     | P2BMX    | T3CMX  | HFOFST    | CCP3MX      | PBADEN | CCP2MX | 348              |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for clock sources.

## 4.5 Brown-out Reset (BOR)

PIC18(L)F2X/4XK22 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> bits of the CONFIG2L Configuration register. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below VBOR for greater than TBOR will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT. If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling BOR Reset does not automatically enable the PWRT.

The BOR circuit has an output that feeds into the POR circuit and rearms the POR within the operating range of the BOR. This early rearming of the POR ensures that the device will remain in Reset in the event that VDD falls below the operating range of the BOR circuitry.

### 4.5.1 DETECTING BOR

When BOR is enabled, the  $\overline{\text{BOR}}$  bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of  $\overline{\text{BOR}}$  alone. A more reliable method is to simultaneously check the state of both  $\overline{\text{POR}}$  and  $\overline{\text{BOR}}$ . This assumes that the  $\overline{\text{POR}}$  and  $\overline{\text{BOR}}$  bits are reset to '1' by software immediately after any POR event. If  $\overline{\text{BOR}}$  is '0' while  $\overline{\text{POR}}$  is '1', it can be reliably assumed that a BOR event has occurred.

#### 4.5.2 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the SBOREN control bit of the RCON register. Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to the environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even                                     | when     | BOR    | is    | under    | software      |  |  |  |  |  |

|-------|------------------------------------------|----------|--------|-------|----------|---------------|--|--|--|--|--|

|       | contro                                   | I, the B | OR Res | set v | oltage l | evel is still |  |  |  |  |  |

|       | set by the BORV<1:0> Configuration bits. |          |        |       |          |               |  |  |  |  |  |

|       | It can                                   | not be c | hanged | d by  | softwar  | e.            |  |  |  |  |  |

#### 4.5.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

#### 4.5.4 MINIMUM BOR ENABLE TIME

Enabling the BOR also enables the Fixed Voltage Reference (FVR) when no other peripheral requiring the FVR is active. The BOR becomes active only after the FVR stabilizes. Therefore, to ensure BOR protection, the FVR settling time must be considered when enabling the BOR in software or when the BOR is automatically enabled after waking from Sleep. If the BOR is disabled, in software or by reentering Sleep before the FVR stabilizes, the BOR circuit will not sense a BOR condition. The FVRST bit of the VREFCON0 register can be used to determine FVR stability.

## 9.9 INTn Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared by software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP and INT2IP of the INTCON3 register. There is no priority bit associated with INT0. It is always a high priority interrupt source.

## 9.10 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE of the INTCON register. Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP of the INTCON2 register. See **Section 11.0 "Timer0 Module"** for further details on the Timer0 module.

## 9.11 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF of the INTCON register. The interrupt can be enabled/ disabled by setting/clearing enable bit, RBIE of the INTCON register. Pins must also be individually enabled with the IOCB register. Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP of the INTCON2 register.

## 9.12 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see **Section 5.2.1** "Fast Register Stack"), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### **EXAMPLE 9-1:** SAVING STATUS, WREG AND BSR REGISTERS IN RAM

```

; W TEMP is in virtual bank

MOVWF

W TEMP

MOVFF

STATUS, STATUS_TEMP

; STATUS_TEMP located anywhere

MOVFF

BSR, BSR_TEMP

; BSR_TMEP located anywhere

; USER ISR CODE

MOVFF

BSR TEMP, BSR

; Restore BSR

MOVF

W TEMP, W

; Restore WREG

MOVFF

STATUS_TEMP, STATUS

; Restore STATUS

```

## REGISTER 12-2: TXGCON: TIMER1/3/5 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u | R-x/x  | R/W-0/u | R/W-0/u |

|---------|---------|---------|---------|------------|--------|---------|---------|

| TMRxGE  | TxGPOL  | TxGTM   | TxGSPM  | TxGGO/DONE | TxGVAL | TxGSS   | S<1:0>  |

| bit 7   |         |         |         |            |        |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHC = Bit is cleared by hardware

bit 7 TMRxGE: Timer1/3/5 Gate Enable bit

If TMRxON = 0: This bit is ignored If TMRxON = 1:

bit 6

1 = Timer1/3/5 counting is controlled by the Timer1/3/5 gate function 0 = Timer1/3/5 counts regardless of Timer1/3/5 gate function

TxGPOL: Timer1/3/5 Gate Polarity bit

1 = Timer1/3/5 gate is active-high (Timer1/3/5 counts when gate is high) 0 = Timer1/3/5 gate is active-low (Timer1/3/5 counts when gate is low)

bit 5 TxGTM: Timer1/3/5 Gate Toggle Mode bit

1 = Timer1/3/5 Gate Toggle mode is enabled

0 = Timer1/3/5 Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer1/3/5 gate flip-flop toggles on every rising edge.

bit 4 TxGSPM: Timer1/3/5 Gate Single-Pulse Mode bit

1 = Timer1/3/5 gate Single-Pulse mode is enabled and is controlling Timer1/3/5 gate

0 = Timer1/3/5 gate Single-Pulse mode is disabled

bit 3 TxGGO/DONE: Timer1/3/5 Gate Single-Pulse Acquisition Status bit

1 = Timer1/3/5 gate single-pulse acquisition is ready, waiting for an edge

0 = Timer1/3/5 gate single-pulse acquisition has completed or has not been started

This bit is automatically cleared when TxGSPM is cleared.

bit 2 TxGVAL: Timer1/3/5 Gate Current State bit

Indicates the current state of the Timer1/3/5 gate that could be provided to TMRxH:TMRxL.

Unaffected by Timer1/3/5 Gate Enable (TMRxGE).

bit 1-0 TxGSS<1:0>: Timer1/3/5 Gate Source Select bits

00 = Timer1/3/5 Gate pin

01 = Timer2/4/6 Match PR2/4/6 output (See Table 12-5 for proper timer match selection)

10 = Comparator 1 optionally synchronized output (sync\_C1OUT)

11 = Comparator 2 optionally synchronized output (sync\_C2OUT)

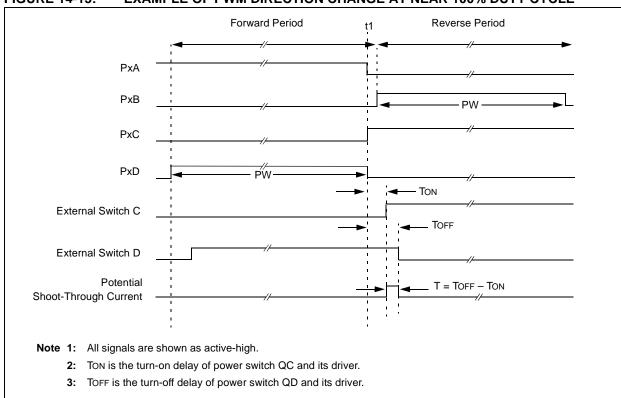

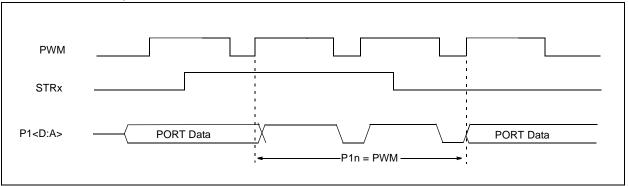

FIGURE 14-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

## 14.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the ECCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator Cx (async\_CxOUT)

- Setting the CCPxASE bit in firmware

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 14.4.4 "Auto-Restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD].

The state of each pin pair is determined by the PSSxAC<1:0> and PSSxBD<1:0> bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

#### 14.4.7 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

The CCPxM<1:0> bits of the CCPxCON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (PxA/PxC and PxB/PxD). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enable is not recommended since it may result in damage to the application circuits.

The PxA, PxB, PxC and PxD output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit.

The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMRxIF bit of the PIR1, PIR2 or PIR5 register being set as the second PWM period begins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the Off state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

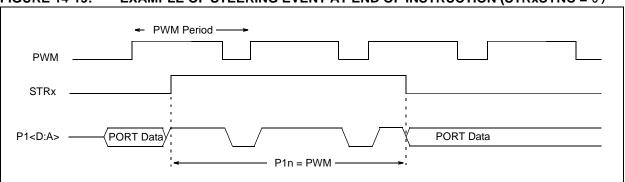

FIGURE 14-19: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRxSYNC = 0)

FIGURE 14-20: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRxSYNC = 1)

## REGISTER 14-2: CCPxCON: ENHANCED CCPx CONTROL REGISTER

| R/x-0 | R/W-0              | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|--------------------|-------|-------|------------|-------|-------|-------|--|--|--|

| PxM<  | PxM<1:0> DCxB<1:0> |       |       | CCPxM<3:0> |       |       |       |  |  |  |

| bit 7 |                    |       |       |            |       |       | bit 0 |  |  |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Reset'1' = Bit is set'0' = Bit is cleared

bit 7-6 **PxM<1:0>**: Enhanced PWM Output Configuration bits

If CCPxM<3:2> = 00, 01, 10: (Capture/Compare modes)

xx = PxA assigned as Capture/Compare input; PxB, PxC, PxD assigned as port pins

Half-Bridge ECCP Modules<sup>(1)</sup>:

If CCPxM<3:2> = 11: (PWM modes)

0x = Single output; PxA modulated; PxB assigned as port pin

1x = Half-Bridge output; PxA, PxB modulated with dead-band control

Full-Bridge ECCP Modules(1):

If CCPxM<3:2> = 11: (PWM modes)

00 = Single output; PxA modulated; PxB, PxC, PxD assigned as port pins

01 = Full-Bridge output forward; PxD modulated; PxA active; PxB, PxC inactive

10 = Half-Bridge output; PxA, PxB modulated with dead-band control; PxC, PxD assigned as port pins

11 = Full-Bridge output reverse; PxB modulated; PxC active; PxA, PxD inactive

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

Note 1: See Table 14-1 to determine full-bridge and half-bridge ECCPs for the device being used.

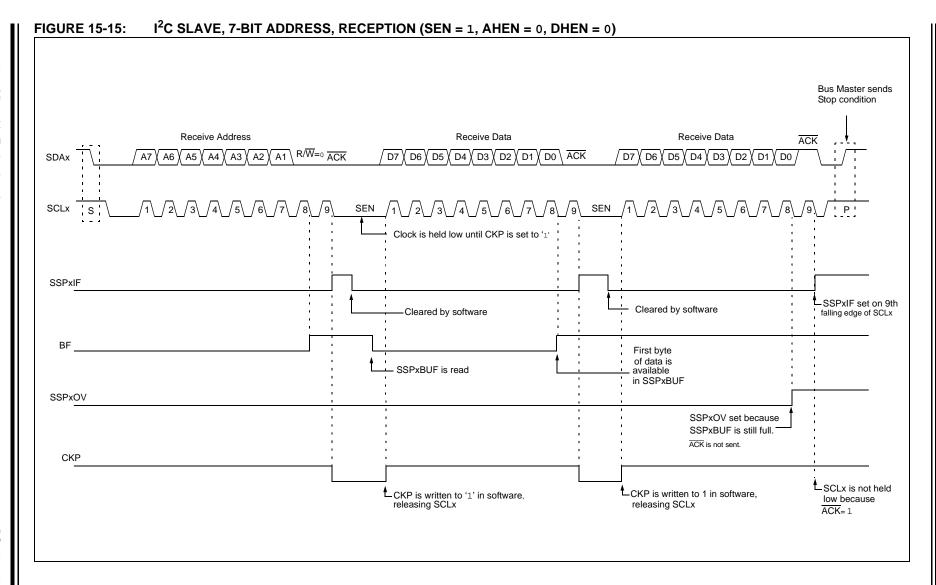

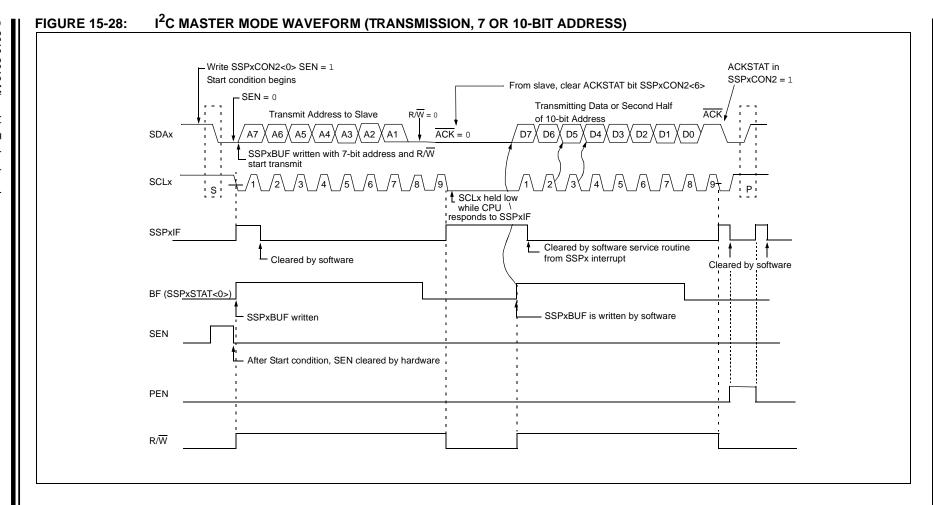

## 15.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSPxCON3 register enables additional clock stretching and interrupt generation after the 8th falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSPxIF interrupt is set.

Figure 15-19 displays a standard waveform of a 7-bit Address Slave Transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the 8th falling edge of the SCLx line the CKP bit is cleared and SSPxIF interrupt is generated.

- 4. Slave software clears SSPxIF.

- Slave software reads ACKTIM bit of SSPxCON3 register, and R/W and D/A of the SSPxSTAT register to determine the source of the interrupt.

- Slave reads the address value from the SSPxBUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets ACKDT bit of the SSPxCON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCLx.

- 9. Master clocks in the ACK value from the slave.

- Slave hardware automatically clears the CKP bit and sets SSPxIF after the ACK if the R/W bit is set.

- 11. Slave software clears SSPxIF.

- 12. Slave loads value to transmit to the master into SSPxBUF setting the BF bit.

**Note:** SSPxBUF cannot be loaded until after the ACK.

- 13. Slave sets CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the 9th SCLx pulse.

- 15. Slave hardware copies the  $\overline{ACK}$  value into the ACKSTAT bit of the SSPxCON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

Note: Master must send a not ACK on the last byte to ensure that the slave releases the SCLx line to receive a Stop.

### 16.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode would typically be used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RXx/DTx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREGx register.

### 16.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTAx register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTAx register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTAx register enables the EUSART. The RXx/DTx I/O pin must be configured as an input by setting the corresponding TRIS control bit. If the RXx/DTx pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

#### 16.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 16.1.2.5 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCxIF interrupt flag bit of the PIR1/PIR3 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREGx register.

Note: If the receive FIFO is overrun, no additional characters will be received until the overrun condition is cleared. See Section 16.1.2.6 "Receive Overrun Error" for more information on overrun errors.

#### 16.1.2.3 Receive Data Polarity

The polarity of the receive data can be controlled with the DTRXP bit of the BAUDCONx register. The default state of this bit is '0' which selects high true receive idle and data bits. Setting the DTRXP bit to '1' will invert the receive data resulting in low true idle and data bits. The DTRXP bit controls receive data polarity only in Asynchronous mode. In Synchronous mode the DTRXP bit has a different function.

### 16.5.1.6 Synchronous Master Reception

Data is received at the RXx/DTx pin. The RXx/DTx pin output driver must be disabled by setting the corresponding TRIS bits when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTAx register) or the Continuous Receive Enable bit (CREN of the RCSTAx register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RXx/DTx pin on the trailing edge of the TXx/CKx clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCxIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREGx. The RCxIF bit remains set as long as there are un-read characters in the receive FIFO.

### 16.5.1.7 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TXx/CKx line. The TXx/CKx pin output driver must be disabled by setting the associated TRIS bit when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.5.1.8 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREGx is read to access the FIFO. When this happens the OERR bit of the RCSTAx register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREGx.

If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTAx register or by clearing the SPEN bit which resets the EUSART.

#### 16.5.1.9 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTAx register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTAx register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREGx.

# 16.5.1.10 Synchronous Master Reception Setup:

- Initialize the SPBRGHx, SPBRGx register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC. Disable RXx/DTx and TXx/CKx output drivers by setting the corresponding TRIS bits.

- 4. Ensure bits CREN and SREN are clear.

- If using interrupts, set the GIE/GIEH and PEIE/ GIEL bits of the INTCON register and set RCxIE.

- 6. If 9-bit reception is desired, set bit RX9.

- Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCxIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCxIE was set.

- Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREGx register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTAx register or by clearing the SPEN bit which resets the EUSART.

#### 17.2.10 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- · Configure pin as analog

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- Select ADC input channel

- · Select result format

- · Select acquisition delay

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Software delay required if ACQT bits are set to zero delay. See Section 17.4 "A/D Acquisition Requirements".

#### **EXAMPLE 17-1: A/D CONVERSION**

```

;This code block configures the ADC

; for polling, Vdd and Vss as reference, Frc

clock and ANO input.

;Conversion start & polling for completion

; are included.

MOVLW

B'10101111' ; right justify, Frc,

MOVWF ADCON2 ; & 12 TAD ACQ time

MOVLW B'00000000' ;ADC ref = Vdd,Vss

MOVWF

ADCON1 ;

TRISA,0 ;Set RAO to input ANSEL,0 ;Set RAO to analog

BSF

;Set RAO to analog

BSF

B'00000001' ;ANO, ADC on

MOVLW

MOVWF

ADCON0

ADCON0,GO ;Start conversion

BSF

ADCPoll:

BTFSC

ADCON0,GO ; Is conversion done?

BRA

ADCPoll ; No, test again

; Result is complete - store 2 MSbits in

; RESULTHI and 8 LSbits in RESULTLO

MOVFF

ADRESH, RESULTHI

MOVFF

ADRESL, RESULTLO

```

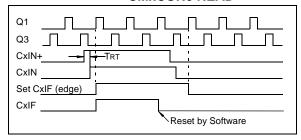

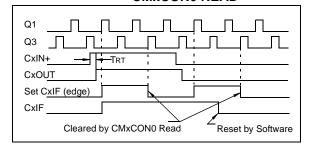

## 18.4 Comparator Interrupt Operation

The comparator interrupt flag will be set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusiveor gate (see Figure 18-2). The first latch is updated with the comparator output value, when the CMxCON0 register is read or written. The value is latched on the third cycle of the system clock, also known as Q3. This first latch retains the comparator value until another read or write of the CMxCON0 register occurs or a Reset takes place. The second latch is updated with the comparator output value on every first cycle of the system clock, also known as Q1. When the output value of the comparator changes, the second latch is updated and the output values of both latches no longer match one another, resulting in a mismatch condition. The latch outputs are fed directly into the inputs of an exclusive-or gate. This mismatch condition is detected by the exclusive-or gate and sent to the interrupt circuitry. The mismatch condition will persist until the first latch value is updated by performing a read of the CMxCON0 register or the comparator output returns to the previous state.

- Note 1: A write operation to the CMxCON0 register will also clear the mismatch condition because all writes include a read operation at the beginning of the write cycle.

- **2:** Comparator interrupts will operate correctly regardless of the state of CxOE.

When the mismatch condition occurs, the comparator interrupt flag is set. The interrupt flag is triggered by the edge of the changing value coming from the exclusive-or gate. This means that the interrupt flag can be reset once it is triggered without the additional step of reading or writing the CMxCON0 register to clear the mismatch latches. When the mismatch registers are cleared, an interrupt will occur upon the comparator's return to the previous state, otherwise no interrupt will be generated.

Software will need to maintain information about the status of the comparator output, as read from the CMxCON0 register, or CM2CON1 register, to determine the actual change that has occurred. See Figures 18-3 and 18-4.

The CxIF bit of the PIR2 register is the comparator interrupt flag. This bit must be reset by software by clearing it to '0'. Since it is also possible to write a '1' to this register, an interrupt can be generated.

In mid-range Compatibility mode the CxIE bit of the PIE2 register and the PEIE/GIEL and GIE/GIEH bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR2 register will still be set if an interrupt condition occurs.

## 18.4.1 PRESETTING THE MISMATCH LATCHES

The comparator mismatch latches can be preset to the desired state before the comparators are enabled. When the comparator is off the CxPOL bit controls the CxOUT level. Set the CxPOL bit to the desired CxOUT non-interrupt level while the CxON bit is cleared. Then, configure the desired CxPOL level in the same instruction that the CxON bit is set. Since all register writes are performed as a read-modify-write, the mismatch latches will be cleared during the instruction read phase and the actual configuration of the CxON and CxPOL bits will be occur in the final write phase.

FIGURE 18-3: COMPARATOR INTERRUPT TIMING W/O CMxCON0 READ

FIGURE 18-4: COMPARATOR INTERRUPT TIMING WITH CMxCON0 READ

- Note 1: If a change in the CMxCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF interrupt flag of the PIR2 register may not get set.

- 2: When either comparator is first enabled, bias circuitry in the comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1 μs for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

### REGISTER 20-2: SRCON1: SR LATCH CONTROL REGISTER 1

| R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|-------|--------|--------|--------|

| SRSPE | SRSCKE | SRSC2E | SRSC1E | SRRPE | SRRCKE | SRRC2E | SRRC1E |

| bit 7 |        |        |        |       |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented C = Clearable only bit-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SRSPE: SR Latch Peripheral Set Enable bit

1 = SRI pin status sets SR latch

0 = SRI pin status has no effect on SR latch

bit 6 SRSCKE: SR Latch Set Clock Enable bit

1 = Set input of SR latch is pulsed with DIVSRCLK

0 = Set input of SR latch is not pulsed with DIVSRCLK

bit 5 SRSC2E: SR Latch C2 Set Enable bit

1 = C2 Comparator output sets SR latch

0 = C2 Comparator output has no effect on SR latch

bit 4 SRSC1E: SR Latch C1 Set Enable bit

1 = C1 Comparator output sets SR latch

0 = C1 Comparator output has no effect on SR latch

bit 3 SRRPE: SR Latch Peripheral Reset Enable bit

1 = SRI pin resets SR latch

0 = SRI pin has no effect on SR latch

bit 2 SRRCKE: SR Latch Reset Clock Enable bit

1 = Reset input of SR latch is pulsed with DIVSRCLK

0 = Reset input of SR latch is not pulsed with DIVSRCLK

bit 1 SRRC2E: SR Latch C2 Reset Enable bit

1 = C2 Comparator output resets SR latch

0 = C2 Comparator output has no effect on SR latch

bit 0 SRRC1E: SR Latch C1 Reset Enable bit

1 = C1 Comparator output resets SR latch

0 = C1 Comparator output has no effect on SR latch

#### TABLE 20-2: REGISTERS ASSOCIATED WITH THE SR LATCH

| Name   | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|--------|------------|--------|--------|--------|--------|--------|--------|----------------------------|

| SRCON0 | SRLEN  | SRCLK<2:0> |        |        | SRQEN  | SRNQEN | SRPS   | SRPR   | 329                        |

| SRCON1 | SRSPE  | SRSCKE     | SRSC2E | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 330                        |

| TRISA  | TRISA7 | TRISA6     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 151                        |

| TRISB  | TRISB7 | TRISB6     | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 151                        |

| WPUB   | WPUB7  | WPUB6      | WPUB5  | WPUB4  | WPUB3  | WPUB2  | WPUB1  | WPUB0  | 152                        |

**Legend:** Shaded bits are not used with this module.

# 24.0 SPECIAL FEATURES OF THE CPU

PIC18(L)F2X/4XK22 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- · Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Code Protection

- · ID Locations

- In-Circuit Serial Programming™

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in Section 2.0 "Oscillator Module (With Fail-Safe Clock Monitor)".

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18(L)F2X/4XK22 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

### 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The WR bit in the EECON1 register starts a self-timed write to the Configuration register. In Normal operation mode, a TBLWT instruction with the TBLPTR pointing to the Configuration register sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.6 "Writing to Flash Program Memory".

TABLE 25-2: PIC18(L)F2X/4XK22 INSTRUCTION SET (CONTINUED)

| Mnemo     | nic,    | Bassintan                      | 0          | 16-  | Bit Instr | uction W | ord/ | Status      | Neter |

|-----------|---------|--------------------------------|------------|------|-----------|----------|------|-------------|-------|

| Opera     | nds     | Description                    | Cycles     | MSb  |           |          | LSb  | Affected    | Notes |

| BIT-ORIEN | ITED OP | ERATIONS                       |            |      |           |          |      |             |       |

| BCF       | f, b, a | Bit Clear f                    | 1          | 1001 | bbba      | ffff     | ffff | None        | 1, 2  |

| BSF       | f, b, a | Bit Set f                      | 1          | 1000 | bbba      | ffff     | ffff | None        | 1, 2  |

| BTFSC     | f, b, a | Bit Test f, Skip if Clear      | 1 (2 or 3) | 1011 | bbba      | ffff     | ffff | None        | 3, 4  |

| BTFSS     | f, b, a | Bit Test f, Skip if Set        | 1 (2 or 3) | 1010 | bbba      | ffff     | ffff | None        | 3, 4  |

| BTG       | f, b, a | Bit Toggle f                   | 1          | 0111 | bbba      | ffff     | ffff | None        | 1, 2  |

| CONTROL   | OPERA   | TIONS                          |            |      |           |          |      |             |       |

| ВС        | n       | Branch if Carry                | 1 (2)      | 1110 | 0010      | nnnn     | nnnn | None        |       |

| BN        | n       | Branch if Negative             | 1 (2)      | 1110 | 0110      | nnnn     | nnnn | None        |       |

| BNC       | n       | Branch if Not Carry            | 1 (2)      | 1110 | 0011      | nnnn     | nnnn | None        |       |

| BNN       | n       | Branch if Not Negative         | 1 (2)      | 1110 | 0111      | nnnn     | nnnn | None        |       |

| BNOV      | n       | Branch if Not Overflow         | 1 (2)      | 1110 | 0101      | nnnn     | nnnn | None        |       |

| BNZ       | n       | Branch if Not Zero             | 1 (2)      | 1110 | 0001      | nnnn     | nnnn | None        |       |

| BOV       | n       | Branch if Overflow             | 1 (2)      | 1110 | 0100      | nnnn     | nnnn | None        |       |

| BRA       | n       | Branch Unconditionally         | 2          | 1101 | 0nnn      | nnnn     | nnnn | None        |       |

| BZ        | n       | Branch if Zero                 | 1 (2)      | 1110 | 0000      | nnnn     | nnnn | None        |       |

| CALL      | k, s    | Call subroutine 1st word       | 2          | 1110 | 110s      | kkkk     | kkkk | None        |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |             |       |

| CLRWDT    | _       | Clear Watchdog Timer           | 1          | 0000 | 0000      | 0000     | 0100 | TO, PD      |       |

| DAW       | _       | Decimal Adjust WREG            | 1          | 0000 | 0000      | 0000     | 0111 | С           |       |

| GOTO      | k       | Go to address 1st word         | 2          | 1110 | 1111      | kkkk     | kkkk | None        |       |

|           |         | 2nd word                       |            | 1111 | kkkk      | kkkk     | kkkk |             |       |

| NOP       | _       | No Operation                   | 1          | 0000 | 0000      | 0000     | 0000 | None        |       |

| NOP       | _       | No Operation                   | 1          | 1111 | xxxx      | xxxx     | xxxx | None        | 4     |

| POP       | _       | Pop top of return stack (TOS)  | 1          | 0000 | 0000      | 0000     | 0110 | None        |       |

| PUSH      | _       | Push top of return stack (TOS) | 1          | 0000 | 0000      | 0000     | 0101 | None        |       |

| RCALL     | n       | Relative Call                  | 2          | 1101 | 1nnn      | nnnn     | nnnn | None        |       |

| RESET     |         | Software device Reset          | 1          | 0000 | 0000      | 1111     | 1111 | All         |       |

| RETFIE    | S       | Return from interrupt enable   | 2          | 0000 | 0000      | 0001     | 000s | GIE/GIEH,   |       |

|           |         |                                |            |      |           |          |      | PEIE/GIEL   |       |

| RETLW     | k       | Return with literal in WREG    | 2          | 0000 | 1100      | kkkk     | kkkk | None        |       |

| RETURN    | S       | Return from Subroutine         | 2          | 0000 | 0000      | 0001     | 001s | <u>None</u> |       |

| SLEEP     | _       | Go into Standby mode           | 1          | 0000 | 0000      | 0000     | 0011 | TO, PD      |       |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>4:</sup> Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

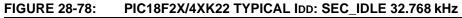

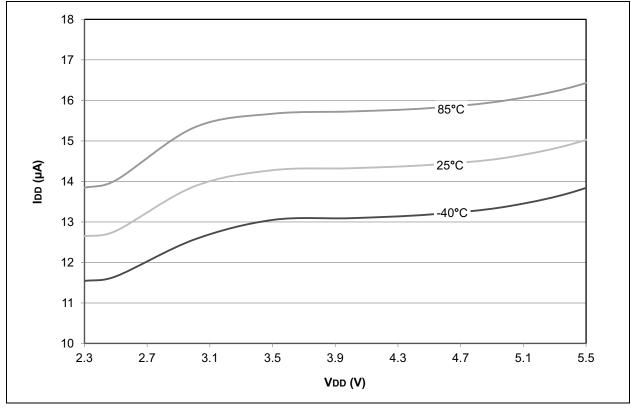

FIGURE 28-79: PIC18F2X/4XK22 MAXIMUM IDD: SEC\_IDLE 32.768 kHz

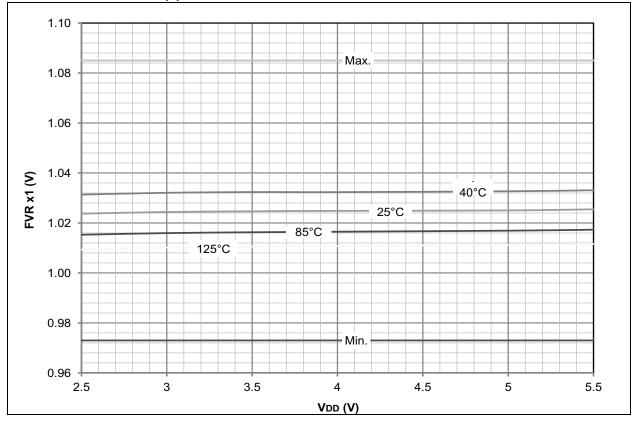

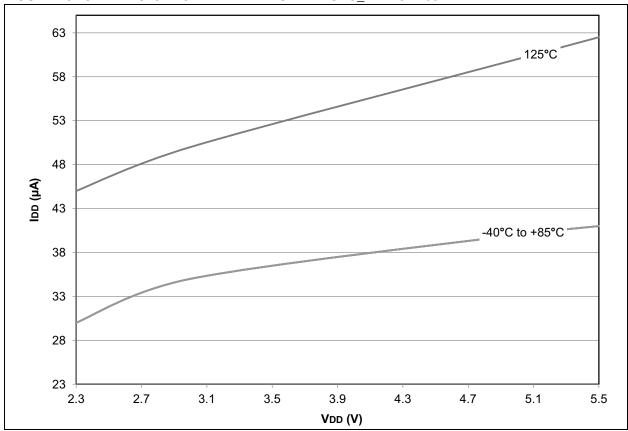

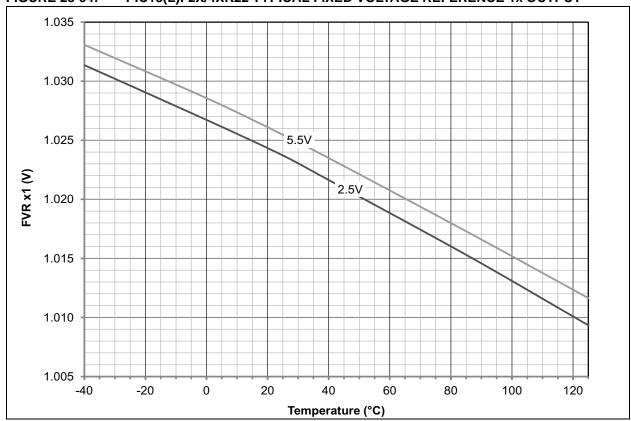

FIGURE 28-95: PIC18(L)F2X/4XK22 TYPICAL FIXED VOLTAGE REFERENCE 1x OUTPUT