Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

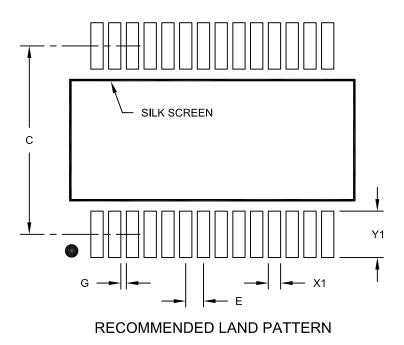

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k22-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.8 PLL Frequency Multiplier

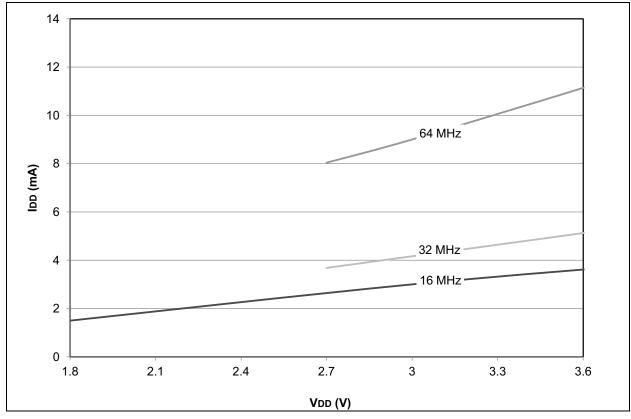

A Phase-Locked Loop (PLL) circuit is provided as an option for users who wish to use a lower frequency oscillator circuit or to clock the device up to its highest rated frequency from the crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals or users who require higher clock speeds from an internal oscillator.

#### 2.8.1 PLL IN EXTERNAL OSCILLATOR MODES

The PLL can be enabled for any of the external oscillator modes using the OSC1/OSC2 pins by either setting the PLLCFG bit (CONFIG1H<4>), or setting the PLLEN bit (OSCTUNE<6>). The PLL is designed for input frequencies of 4 MHz up to 16 MHz. The PLL then multiplies the oscillator output frequency by four to produce an internal clock frequency up to 64 MHz. Oscillator frequencies below 4 MHz should not be used with the PLL.

#### 2.8.2 PLL IN HFINTOSC MODES

The 4x frequency multiplier can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator. When enabled, the PLL multiplies the HFINTOSC by four to produce clock rates up to 64 MHz.

Unlike external clock modes, when internal clock modes are enabled, the PLL can only be controlled through software. The PLLEN control bit of the OSCTUNE register is used to enable or disable the PLL operation when the HFINTOSC is used.

The PLL is designed for input frequencies of 4 MHz up to 16 MHz.

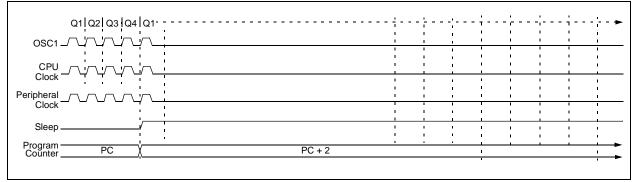

#### 3.3 Sleep Mode

The Power-Managed Sleep mode in the PIC18(L)F2X/ 4XK22 devices is identical to the legacy Sleep mode offered in all other PIC microcontroller devices. It is entered by clearing the IDLEN bit of the OSCCON register and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-4) and all clock source Status bits are cleared.

Entering the Sleep mode from either Run or Idle mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the LFINTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 3-5), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 24.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

#### 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected by the SCS<1:0> bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the LFINTOSC source will continue to operate. If the SOSC oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out, or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TCSD while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS<1:0> bits.

#### FIGURE 3-4: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

## 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory is executed on blocks of 64 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

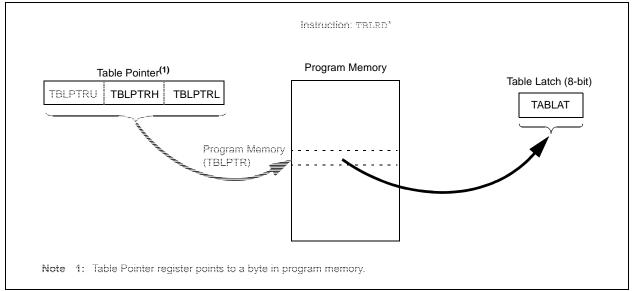

### 6.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

The table read operation retrieves one byte of data directly from program memory and places it into the TABLAT register. Figure 6-1 shows the operation of a table read.

The table write operation stores one byte of data from the TABLAT register into a write block holding register. The procedure to write the contents of the holding registers into program memory is detailed in **Section 6.6 "Writing to Flash Program Memory"**. Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. Tables containing data, rather than program instructions, are not required to be word aligned. Therefore, a table can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

#### FIGURE 6-1: TABLE READ OPERATION

| R/W-0        | R/W-0                                             | R/W-0             | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|---------------------------------------------------|-------------------|----------------|------------------|-----------------|-----------------|--------|

| OSCFIE       | C1IE                                              | C2IE              | EEIE           | BCL1IE           | HLVDIE          | TMR3IE          | CCP2IE |

| bit 7        |                                                   |                   |                |                  |                 |                 | bit (  |

| Legend:      |                                                   |                   |                |                  |                 |                 |        |

| R = Readab   | le bit                                            | W = Writable      | bit            | U = Unimple      | mented bit, rea | d as '0'        |        |

| -n = Value a | t POR                                             | '1' = Bit is set  |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |

| bit 7        | <b>OSCFIE:</b> Osc<br>1 = Enabled<br>0 = Disabled | illator Fail Inte | rrupt Enable I | bit              |                 |                 |        |

| bit 6        | C1IE: Compa<br>1 = Enabled<br>0 = Disabled        | rator C1 Interro  | upt Enable bit | t                |                 |                 |        |

| bit 5        | <b>C2IE:</b> Compa<br>1 = Enabled<br>0 = Disabled | rator C2 Interro  | upt Enable bit | t                |                 |                 |        |

| bit 4        | EEIE: Data E<br>1 = Enabled<br>0 = Disabled       | EPROM/Flash       | Write Operat   | ion Interrupt Er | nable bit       |                 |        |

| bit 3        | BCL1IE: MSS<br>1 = Enabled<br>0 = Disabled        | SP1 Bus Collisi   | on Interrupt E | Enable bit       |                 |                 |        |

| bit 2        | HLVDIE: Low<br>1 = Enabled<br>0 = Disabled        | -Voltage Detec    | t Interrupt En | able bit         |                 |                 |        |

| bit 1        | <b>TMR3IE:</b> TMI<br>1 = Enabled<br>0 = Disabled | R3 Overflow In    | terrupt Enable | e bit            |                 |                 |        |

| bit 0        | <b>CCP2IE:</b> CCI<br>1 = Enabled<br>0 = Disabled | P2 Interrupt En   | able bit       |                  |                 |                 |        |

#### REGISTER 9-10: PIE2: PERIPHERAL INTERRUPT ENABLE (FLAG) REGISTER 2

#### 10.5 PORTD Registers

| Note: | PORTD is only available on 40-pin and |

|-------|---------------------------------------|

|       | 44-pin devices.                       |

PORTD is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., disable the output driver). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

All of the PORTD pins are multiplexed with analog and digital peripheral modules. See Table 10-11.

**Note:** On a Power-on Reset, these pins are configured as analog inputs.

EXAMPLE 10-4: INITIALIZING PORTD

| MOVLB<br>CLRF | 0xF<br>PORTD | ; Set BSR for banked SFRs<br>; Initialize PORTD by<br>; clearing output |

|---------------|--------------|-------------------------------------------------------------------------|

|               |              | ; data latches                                                          |

| CLRF          | LATD         | ; Alternate method                                                      |

|               |              | ; to clear output                                                       |

|               |              | ; data latches                                                          |

| MOVLW         | OCFh         | ; Value used to                                                         |

|               |              | ; initialize data                                                       |

|               |              | ; direction                                                             |

| MOVWF         | TRISD        | ; Set RD<3:0> as inputs                                                 |

|               |              | ; RD<5:4> as outputs                                                    |

|               |              | ; RD<7:6> as inputs                                                     |

| MOVLW         | 30h          | ; Value used to                                                         |

|               |              | ; enable digital inputs                                                 |

| MOVWF         | ANSELD       | ; RD<3:0> dig input enable                                              |

|               |              | ; RC<7:6> dig input enable                                              |

|               |              |                                                                         |

#### 10.5.1 PORTD OUTPUT PRIORITY

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are briefly described here. For additional information, refer to the appropriate section in this data sheet.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the higher priority. Table 10-4 lists the PORTD pin functions from the highest to the lowest priority.

Analog input functions, such as ADC, comparator and SR latch inputs, are not shown in the priority lists.

These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below.

| U-0             | U-0                               | R/W-1 | R/W-1 | R/W-1                                    | R/W-1 | R/W-1 | R/W-1 |  |  |

|-----------------|-----------------------------------|-------|-------|------------------------------------------|-------|-------|-------|--|--|

| —               | —                                 | ANSB5 | ANSB4 | ANSB3                                    | ANSB2 | ANSB1 | ANSB0 |  |  |

| bit 7           |                                   |       |       |                                          |       |       | bit 0 |  |  |

|                 |                                   |       |       |                                          |       |       |       |  |  |

| Legend:         |                                   |       |       |                                          |       |       |       |  |  |

| R = Readable b  | Readable bit W = Writable bit     |       |       | U = Unimplemented bit, read as '0'       |       |       |       |  |  |

| -n = Value at P | n = Value at POR (1' = Bit is set |       |       | 0' = Bit is cleared $x = Bit is unknown$ |       |       |       |  |  |

| -               |                                   |       |       |                                          |       |       |       |  |  |

#### **REGISTER 10-4:** ANSELB – PORTB ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 ANSB<5:0>: RB<5:0> Analog Select bit 1 = Digital input buffer disabled 0 = Digital input buffer enabled

### REGISTER 10-5: ANSELC – PORTC ANALOG SELECT REGISTER

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0 | U-0   |

|-------|-------|-------|-------|-------|-------|-----|-------|

| ANSC7 | ANSC6 | ANSC5 | ANSC4 | ANSC3 | ANSC2 | —   | —     |

| bit 7 |       |       |       |       |       |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-2 ANSC<7:2>: RC<7:2> Analog Select bit 1 = Digital input buffer disabled 0 = Digital input buffer enabled

bit 1-0 Unimplemented: Read as '0'

#### REGISTER 10-6: ANSELD – PORTD ANALOG SELECT REGISTER

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1      | R/W-1 | R/W-1 |

|-------|-------|-------|-------|-------|------------|-------|-------|

| ANSD7 | ANSD6 | ANSD5 | ANSD4 | ANSD3 | ANSD2 ANSD |       | ANSD0 |

| bit 7 |       |       |       |       |            |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 ANSD<7:0>: RD<7:0> Analog Select bit

1 = Digital input buffer disabled

0 = Digital input buffer enabled

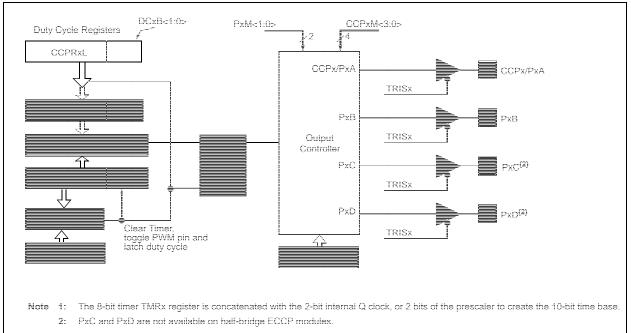

### 14.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- ECCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

- Single PWM with PWM Steering mode

To select an Enhanced PWM Output mode, the PxM<1:0> bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 14-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 14-12 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 14-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

#### 15.5.3 SLAVE TRANSMISSION

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCLx pin is held low (see **Section 15.5.6 "Clock Stretching"** for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCLx pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes Idle and waits for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be released by setting bit CKP.

An MSSPx interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 15.5.3.1 Slave Mode Bus Collision

A slave receives a Read request and begins shifting data out on the SDAx line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCLxIF bit of the PIRx register is set. Once a bus collision is detected, the slave goes Idle and waits to be addressed again. User software can use the BCLxIF bit to handle a slave bus collision.

#### 15.5.3.2 7-bit Transmission

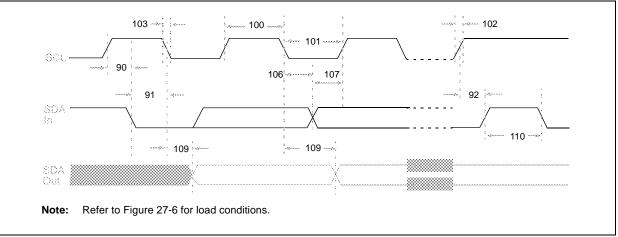

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 15-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDAx and SCLx.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Matching address with R/W bit set is received by the slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCLx, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

**Note 1:** If the master ACKs the clock will be stretched.

**2:** ACKSTAT is the only bit updated on the rising edge of SCLx (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

### 17.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 17-5. The maximum recommended impedance for analog sources is  $3 \ k\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D

acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

3.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 5µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad :[1] V_{CHOLD} charged to within 1/2 lsb

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{CHOLD} \qquad :[2] V_{CHOLD} charge response to VAPPLIED

$$V_{APPLIED}\left(1 - e^{-\frac{TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \qquad :combining [1] and [2]$$

Solving for Tc:

$$T_{C} = -C_{HOLD}(RIC + RSS + RS) ln(1/2047)$$

$$= -13.5pF(Ik\Omega + 700\Omega + 10k\Omega) ln(0.0004885)$$

$$= 1.20\mu s$$$$$$$$

$TACQ = 5\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$ = 7.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

#### EXAMPLE 19-1: SETUP FOR CTMU CALIBRATION ROUTINES

```

#include "pl8cxxx.h"

void setup(void)

{ //CTMUCONH/1 - CTMU Control registers

CTMUCONH = 0x00; //make sure CTMU is disabled

CTMUCONL = 0x90;

//CTMU continues to run when emulator is stopped,CTMU continues

//to run in idle mode, Time Generation mode disabled, Edges are blocked

//No edge sequence order, Analog current source not grounded, trigger

//output disabled, Edge2 polarity = positive level, Edge2 source =

//source 0, Edgel polarity = positive level, Edgel source = source 0,

//CTMUICON - CTMU Current Control Register

CTMUICON = 0x01; //0.55uA, Nominal - No Adjustment

//Set up AD converter;

TRISA=0x04;

//set channel 2 as an input

// Configure AN2 as an analog channel

ANSELAbits ANSA2=1;

TRISAbits.TRISA2=1;

// ADCON2

ADCON2bits.ADFM=1; // Results format 1= Right justified

ADCON2bits.ACQT=1; // Acquition time 7 = 20TAD 2 = 4TAD 1=2TAD

ADCON2bits.ADCS=2; // Clock conversion bits 6= FOSC/64 2=FOSC/

// Clock conversion bits 6= FOSC/64 2=FOSC/32

ADCON2bits.ADCS=2;

// ADCON1

ADCON1bits.PVCFG0 =0;

// Vref+ = AVdd

ADCON1bits.NVCFG1 =0;

// Vref- = AVss

// ADCON0

// Select ADC channel

ADCON0bits.CHS=2;

ADCON0bits.ADON=1; // Turn on ADC

}

```

#### 19.3.2 CAPACITANCE CALIBRATION

There is a small amount of capacitance from the internal A/D Converter sample capacitor as well as stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken by making sure the desired capacitance to be measured has been removed. The measurement is then performed using the following steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time *t*.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances:

$$C_{\text{OFFSET}} = C_{\text{STRAY}} + C_{\text{AD}} = (I \cdot t) / V$$

where *I* is known from the current source measurement step, *t* is a fixed delay and *V* is measured by performing an A/D conversion.

This measured value is then stored and used for calculations of time measurement or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known. CAD is approximately 4 pF.

An iterative process may need to be used to adjust the time, t, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of t may be determined by setting COFFSET to a theoretical value, then solving for t. For example, if CSTRAY is theoretically calculated to be 11 pF, and V is expected to be 70% of VDD, or 2.31V, then t would be:

or 63 µs.

See Example 19-3 for a typical routine for CTMU capacitance calibration.

| SRCLK<2:0> | Divider | Fosc = 20 MHz | Fosc = 16 MHz | Fosc = 8 MHz | Fosc = 4 MHz | Fosc = 1 MHz |

|------------|---------|---------------|---------------|--------------|--------------|--------------|

| 111        | 512     | 25.6 μs       | 32 μs         | 64 μs        | 128 μs       | 512 μs       |

| 110        | 256     | 12.8 μs       | 16 μs         | 32 µs        | 64 μs        | 256 μs       |

| 101        | 128     | 6.4 μs        | 8 μs          | 16 μs        | 32 μs        | 128 μs       |

| 100        | 64      | 3.2 μs        | 4 μs          | 8 μs         | 16 μs        | 64 μs        |

| 011        | 32      | 1.6 μs        | 2 μs          | 4 μs         | 8 μs         | 32 μs        |

| 010        | 16      | 0.8 μs        | 1 μs          | 2 μs         | 4 μs         | 16 μs        |

| 001        | 8       | 0.4 μs        | 0.5 μs        | 1 μs         | 2 μs         | 8 μs         |

| 000        | 4       | 0.2 μs        | 0.25 μs       | 0.5 μs       | 1 μs         | 4 μs         |

### TABLE 20-1: DIVSRCLK FREQUENCY TABLE

| DECFSZ               | Decrement f, skip if 0                                                                                                                                                                                                                                     |                                                                                                                                                            | DCF                                                                                                                                                                                                                                               | SNZ    | Decrement f, skip if not 0                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |                                                                                                                                                                                                                            |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:              | DECFSZ                                                                                                                                                                                                                                                     | f {,d {,a}}                                                                                                                                                |                                                                                                                                                                                                                                                   | Synta  | x:                                         | DCFSNZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | f {,d {,a}}                        |                                                                                                                                                                                                                            |

| Operands:            | $\begin{array}{l} 0\leq f\leq 255\\ d\in [0,1]\\ a\in [0,1] \end{array}$                                                                                                                                                                                   |                                                                                                                                                            |                                                                                                                                                                                                                                                   | Opera  | ands:                                      | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |                                                                                                                                                                                                                            |

| Operation:           | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                     |                                                                                                                                                            |                                                                                                                                                                                                                                                   | Opera  | ation:                                     | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                    |                                                                                                                                                                                                                            |

| Status Affected:     | None                                                                                                                                                                                                                                                       |                                                                                                                                                            |                                                                                                                                                                                                                                                   | Status | Affected:                                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |                                                                                                                                                                                                                            |

| Encoding:            | 0010                                                                                                                                                                                                                                                       | 11da ff:                                                                                                                                                   | ff ffff                                                                                                                                                                                                                                           | Enco   | ding:                                      | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11da fff                           | f ffff                                                                                                                                                                                                                     |

| Description:         | decremente<br>placed in W<br>placed back<br>If the result<br>which is alr<br>and a NOP i<br>it a 2-cycle<br>If 'a' is '0', ti<br>If 'a' is '1', ti<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 25<br>Bit-Oriente | instruction.<br>he Access Ba<br>he BSR is use<br>nd the extend<br>led, this instru-<br>Literal Offset $J$<br>never f $\leq$ 95 (5<br><b>5.2.3 "Byte-Or</b> | the result is<br>ne result is<br>(default).<br>it instruction,<br>is discarded<br>stead, making<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br><b>:iented and</b><br><b>is in Indexed</b> | Desci  | iption:                                    | The contents of register 'f' are decremented. If 'd' is '0', the result placed in W. If 'd' is '1', the result placed back in register 'f' (default). If the result is not '0', the next instruction, which is already fetched discarded and a NOP is executed instead, making it a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected in the Access Bank is selected GPR bank.<br>If 'a' is '0' and the extended instruction oper in Indexed Literal Offset Addressi mode whenever $f \le 95$ (5Fh). See Section 25.2.3 "Byte-Oriented a Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                                    | the result is<br>the result is<br>(default).<br>next<br>dy fetched, is<br>kecuted<br>de<br>the is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See<br>iented and<br>s in Indexed |

| Words:               | 1                                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                                                                                                                                                                                                                   |        |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | set Mode" for                      | details.                                                                                                                                                                                                                   |

| Cycles:              | 1(2)                                                                                                                                                                                                                                                       |                                                                                                                                                            |                                                                                                                                                                                                                                                   | Word   | s:                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                                                                                                                                                                                                            |

|                      |                                                                                                                                                                                                                                                            | /cles if skip ar<br>a 2-word instru                                                                                                                        |                                                                                                                                                                                                                                                   | Cycle  | S:                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cycles if skip a<br>a 2-word instr |                                                                                                                                                                                                                            |

| Q Cycle Activity:    | 0.0                                                                                                                                                                                                                                                        | 0.0                                                                                                                                                        | <u>.</u>                                                                                                                                                                                                                                          | 0.01   | cle Activity:                              | by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                            |

| Q1<br>Decode         | Q2<br>Read                                                                                                                                                                                                                                                 | Q3<br>Process                                                                                                                                              | Q4<br>Write to                                                                                                                                                                                                                                    | u 0,   | Q1                                         | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3                                 | Q4                                                                                                                                                                                                                         |

| Decode               | register 'f'                                                                                                                                                                                                                                               | Data                                                                                                                                                       | destination                                                                                                                                                                                                                                       | [      | Decode                                     | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Process                            | Write to                                                                                                                                                                                                                   |

| lf skip:             |                                                                                                                                                                                                                                                            |                                                                                                                                                            | •                                                                                                                                                                                                                                                 |        |                                            | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Data                               | destination                                                                                                                                                                                                                |

| Q1                   | Q2                                                                                                                                                                                                                                                         | Q3                                                                                                                                                         | Q4                                                                                                                                                                                                                                                | lf ski | p:                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |                                                                                                                                                                                                                            |

| No                   | No                                                                                                                                                                                                                                                         | No                                                                                                                                                         | No                                                                                                                                                                                                                                                | r      | Q1                                         | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3                                 | Q4                                                                                                                                                                                                                         |

| operation            | operation                                                                                                                                                                                                                                                  | operation                                                                                                                                                  | operation                                                                                                                                                                                                                                         |        | No                                         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No                                 | No                                                                                                                                                                                                                         |

| If skip and followe  |                                                                                                                                                                                                                                                            |                                                                                                                                                            | <b>.</b>                                                                                                                                                                                                                                          | lf oki | operation                                  | operation<br>d by 2-word in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | operation                          | operation                                                                                                                                                                                                                  |

| Q1                   | Q2                                                                                                                                                                                                                                                         | Q3                                                                                                                                                         | Q4                                                                                                                                                                                                                                                | II SKI | Q1                                         | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3                                 | Q4                                                                                                                                                                                                                         |

| No<br>operation      | No<br>operation                                                                                                                                                                                                                                            | No<br>operation                                                                                                                                            | No<br>operation                                                                                                                                                                                                                                   | Γ      | No                                         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No                                 | No                                                                                                                                                                                                                         |

| No                   | No                                                                                                                                                                                                                                                         | No                                                                                                                                                         | No                                                                                                                                                                                                                                                |        | operation                                  | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation                          | operation                                                                                                                                                                                                                  |

| operation            | operation                                                                                                                                                                                                                                                  | operation                                                                                                                                                  | operation                                                                                                                                                                                                                                         | -      | No                                         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No                                 | No                                                                                                                                                                                                                         |

|                      | •                                                                                                                                                                                                                                                          | •                                                                                                                                                          |                                                                                                                                                                                                                                                   |        | operation                                  | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation                          | operation                                                                                                                                                                                                                  |

| Example:             | HERE<br>CONTINUE                                                                                                                                                                                                                                           | DECFSZ<br>GOTO                                                                                                                                             | CNT, 1, 1<br>LOOP                                                                                                                                                                                                                                 | Exam   | <u>ple</u> :                               | ZERO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | :                                  | IP, 1, 0                                                                                                                                                                                                                   |

| Before Instru        |                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                   |        | Defere laste                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | :                                  |                                                                                                                                                                                                                            |

| PC<br>After Instruct | ion                                                                                                                                                                                                                                                        | S (HERE)                                                                                                                                                   |                                                                                                                                                                                                                                                   |        | Before Instruc<br>TEMP<br>After Instructio | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ?                                  |                                                                                                                                                                                                                            |

| CNT<br>If CNT        | = CNT - 1<br>= 0;                                                                                                                                                                                                                                          |                                                                                                                                                            |                                                                                                                                                                                                                                                   | ,      | TEMP                                       | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TEMP – 1,                          |                                                                                                                                                                                                                            |

|                      | ; = Áddress<br>≠ 0;                                                                                                                                                                                                                                        | S (CONTINUE                                                                                                                                                | Ε)                                                                                                                                                                                                                                                |        | If TEMP<br>PC                              | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0;<br>Address (2                   |                                                                                                                                                                                                                            |