Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k22-e-mv |

- Two Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) modules:

- Supports RS-485, RS-232 and LIN

- RS-232 operation using internal oscillator

- Auto-Wake-up on Break

- Auto-Baud Detect

TABLE 1: PIC18(L)F2X/4XK22 FAMILY TYPES

|                | Program Data<br>Memory Memory |                               | S <sup>(2)</sup> | 9                 |        | (e) (e)                               |     | MSSP                  |                       | J.  |     |        |            | L    | 7       |          |             |              |

|----------------|-------------------------------|-------------------------------|------------------|-------------------|--------|---------------------------------------|-----|-----------------------|-----------------------|-----|-----|--------|------------|------|---------|----------|-------------|--------------|

| Device         | Flash<br>(Bytes)              | # Single-Word<br>Instructions | SRAM<br>(Bytes)  | EEPROM<br>(Bytes) | 1/0(1) | 10-bit<br>A/D Channels <sup>(2)</sup> | doo | ECCP<br>(Full-Bridge) | ECCP<br>(Half-Bridge) | IdS | l²C | EUSART | Comparator | СТМU | BOR/LVD | SR Latch | 8-bit Timer | 16-bit Timer |

| PIC18(L)F23K22 | 8K                            | 4096                          | 512              | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F24K22 | 16K                           | 8192                          | 768              | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F25K22 | 32K                           | 16384                         | 1536             | 256               | 25     | 19                                    | 2   | 1                     | 2                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F26K22 | 64k                           | 32768                         | 3896             | 1024              | 25     | 19                                    | 2   | 1                     | 2                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F43K22 | 8K                            | 4096                          | 512              | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F44K22 | 16K                           | 8192                          | 768              | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F45K22 | 32K                           | 16384                         | 1536             | 256               | 36     | 30                                    | 2   | 2                     | 1                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

| PIC18(L)F46K22 | 64k                           | 32768                         | 3896             | 1024              | 36     | 30                                    | 2   | 2                     | 1                     | 2   | 2   | 2      | 2          | Υ    | Υ       | Υ        | 3           | 4            |

Note 1: One pin is input only.

<sup>2:</sup> Channel count includes internal FVR and DAC channels.

### REGISTER 2-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| R-0/0  | R-0/q   | U-0 | R/W-0/0 | R/W-0/u               | R/W-1/1 | R-x/u  | R-0/0  |

|--------|---------|-----|---------|-----------------------|---------|--------|--------|

| PLLRDY | SOSCRUN | _   | MFIOSEL | SOSCGO <sup>(1)</sup> | PRISD   | MFIOFS | LFIOFS |

| bit 7  |         |     |         |                       |         |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' q = depends on condition

'1' = Bit is set 0' = Bit is cleared x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

bit 7 PLLRDY: PLL Run Status bit

1 = System clock comes from 4xPLL

0 = System clock comes from an oscillator, other than 4xPLL

bit 6 SOSCRUN: SOSC Run Status bit

1 = System clock comes from secondary SOSC

0 = System clock comes from an oscillator, other than SOSC

bit 5 **Unimplemented:** Read as '0'.

bit 4 MFIOSEL: MFINTOSC Select bit

1 = MFINTOSC is used in place of HFINTOSC frequencies of 500 kHz, 250 kHz and 31.25 kHz

0 = MFINTOSC is not used

bit 3 SOSCGO<sup>(1)</sup>: Secondary Oscillator Start Control bit

1 = Secondary oscillator is enabled.

0 = Secondary oscillator is shut off if no other sources are requesting it.

bit 2 PRISD: Primary Oscillator Drive Circuit Shutdown bit

1 = Oscillator drive circuit on

0 = Oscillator drive circuit off (zero power)

bit 1 MFIOFS: MFINTOSC Frequency Stable bit

1 = MFINTOSC is stable0 = MFINTOSC is not stable

bit 0 LFIOFS: LFINTOSC Frequency Stable bit

1 = LFINTOSC is stable

0 = LFINTOSC is not stable

**Note 1:** The SOSCGO bit is only reset on a POR Reset.

#### 2.7.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31.25 kHz internal clock source. The LFINTOSC is not tunable, but is designed to be stable across temperature and voltage. See **Section 27.0** "Electrical **Specifications**" for the LFINTOSC accuracy specifications.

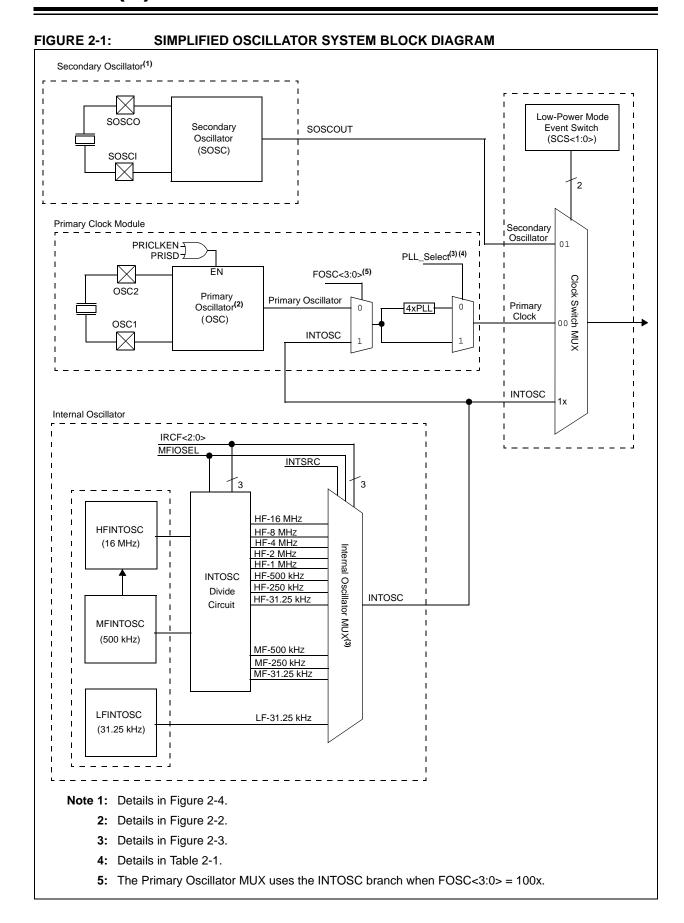

The output of the LFINTOSC can be a clock source to the primary clock or the INTOSC clock (see Figure 2-1). The LFINTOSC is also the clock source for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

## 2.7.2 FREQUENCY SELECT BITS (IRCF)

The HFINTOSC (16 MHz) and MFINTOSC (500 MHz) outputs connect to a divide circuit that provides frequencies of 16 MHz to 31.25 kHz. These divide circuit frequencies, along with the 31.25 kHz LFINTOSC output, are multiplexed to provide a single INTOSC clock output (see Figure 2-1). The IRCF<2:0> bits of the OSCCON register, the MFIOSEL bit of the OSCCON2 register and the INTSRC bit of the OSCTUNE register, select the output frequency of the internal oscillators. One of eight frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz (default after Reset)

- 500 kHz (MFINTOSC or HFINTOSC)

- 250 kHz (MFINTOSC or HFINTOSC)

- 31 kHz (LFINTOSC, MFINTOSC or HFINTOSC)

#### 2.7.3 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block outputs (HFINTOSC/MFINTOSC) for 16 MHz/500 kHz. However, this frequency may drift as VDD or temperature changes. It is possible to adjust the HFINTOSC/MFINTOSC frequency by modifying the value of the TUN<5:0> bits in the OSCTUNE register. This has no effect on the LFINTOSC clock source frequency.

Tuning the HFINTOSC/MFINTOSC source requires knowing when to make the adjustment, in which direction it should be made and, in some cases, how large a change is needed. Three possible compensation techniques are discussed in the following sections. However, other techniques may be used.

## 2.7.3.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

## 2.7.3.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

# 2.7.3.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1, Timer3 or Timer5 clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

#### 5.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

## 5.2 Register Definitions: Stack Pointer

### REGISTER 5-1: STKPTR: STACK POINTER REGISTER

| R/C-0                 | R/C-0                 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-----------------------|-----------------------|-----|-------|-------|-------------|-------|-------|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | _   |       |       | STKPTR<4:0> | •     |       |

| bit 7                 |                       |     |       |       |             |       | bit 0 |

| Legend:           |                  |                      |                        |

|-------------------|------------------|----------------------|------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | C = Clearable only bit |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown     |

bit 7 **STKFUL:** Stack Full Flag bit<sup>(1)</sup>

1 = Stack became full or overflowed

0 = Stack has not become full or overflowed

bit 6 **STKUNF:** Stack Underflow Flag bit<sup>(1)</sup>

1 = Stack Underflow occurred0 = Stack Underflow did not occur

bit 5 **Unimplemented:** Read as '0'

bit 4-0 STKPTR<4:0>: Stack Pointer Location bits

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

#### 5.2.0.1 Stack Full and Underflow Resets

Device Resets on Stack Overflow and Stack Underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

## 5.2.1 FAST REGISTER STACK

A fast register stack is provided for the Status, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high priority interrupts are enabled, the stack registers cannot be used reliably to return from low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten. In these cases, users must save the key registers by software during a low priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the Status, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the Status, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

## 5.6.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

# 5.7 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

## 5.7.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

# 5.7.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 5-11.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 25.2.1** "Extended Instruction Syntax".

TABLE 10-8: PORTC I/O SUMMARY (CONTINUED)

| Pin Name          | Function                 | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type | Description                                              |

|-------------------|--------------------------|-----------------|---------------|-------------|----------------|----------------------------------------------------------|

| RC5/SDO1/AN17     | RC5                      | 0               | 0             | 0           | DIG            | LATC<5> data output; not affected by analog input.       |

|                   |                          | 1               | 0             | I           | ST             | PORTC<5> data input; disabled when analog input enabled. |

|                   | SDO1                     | 0               | 0             | 0           | DIG            | MSSP1 SPI data output.                                   |

|                   | AN17                     | 1               | 1             | I           | AN             | Analog input 17.                                         |

| RC6/P3A/CCP3/TX1/ | RC6                      | 0               | 0             | 0           | DIG            | LATC<6> data output; not affected by analog input.       |

| CK1/AN18          |                          | 1               | 0             | I           | ST             | PORTC<6> data input; disabled when analog input enabled. |

|                   | P3A <sup>(2), (3)</sup>  | 0               | 0             | 0           | CMOS           | Enhanced CCP3 PWM output 1.                              |

|                   | CCP3 <sup>(2), (3)</sup> | 0               | 0             | 0           | DIG            | Compare 3 output/PWM 3 output.                           |

|                   |                          | 1               | 0             | I           | ST             | Capture 3 input.                                         |

|                   | TX1                      | 1               | 0             | 0           | DIG            | EUSART asynchronous transmit data output.                |

|                   | CK1                      | 1               | 0             | 0           | DIG            | EUSART synchronous serial clock output.                  |

|                   |                          | 1               | 0             | I           | ST             | EUSART synchronous serial clock input.                   |

|                   | AN18                     | 1               | 1             | I           | AN             | Analog input 18.                                         |

| RC7/P3B/RX1/DT1/  | RC7                      | 0               | 0             | 0           | DIG            | LATC<7> data output; not affected by analog input.       |

| AN19              |                          | 1               | 0             | I           | ST             | PORTC<7> data input; disabled when analog input enabled. |

|                   | P3B                      | 0               | 0             | 0           | CMOS           | Enhanced CCP3 PWM output 2.                              |

|                   | RX1                      | 1               | 0             | I           | ST             | EUSART asynchronous receive data in.                     |

|                   | DT1                      | 1               | 0             | 0           | DIG            | EUSART synchronous serial data output.                   |

|                   |                          | 1               | 0             | I           | ST             | EUSART synchronous serial data input.                    |

|                   | AN19                     | 1               | 1             | I           | AN             | Analog input 19.                                         |

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

- 2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

- 3: Function on PORTD and PORTE for PIC18FXXK22 devices.

## 12.13 Register Definitions: Timer1/3/5 Control

### REGISTER 12-1: TXCON: TIMER1/3/5 CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u     | R/W-0/u | R/W-0/u  | R/W-0/u | R/W-0/0 | R/W-0/u |

|---------|---------|-------------|---------|----------|---------|---------|---------|

| TMRxC   | S<1:0>  | TxCKPS<1:0> |         | TxSOSCEN | TxSYNC  | TxRD16  | TMRxON  |

| bit 7   |         |             |         |          |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 TMRxCS<1:0>: Timer1/3/5 Clock Source Select bits

11 = Reserved. Do not use.

10 = Timer1/3/5 clock source is pin or oscillator:

If TxSOSCEN = 0:

External clock from TxCKI pin (on the rising edge)

If TxSOSCEN = 1:

Crystal oscillator on SOSCI/SOSCO pins

01 = Timer1/3/5 clock source is system clock (Fosc)

00 = Timer1/3/5 clock source is instruction clock (Fosc/4)

bit 5-4 TxCKPS<1:0>: Timer1/3/5 Input Clock Prescale Select bits

11 = 1:8 Prescale value

10 = 1:4 Prescale value

01 = 1:2 Prescale value

00 = 1:1 Prescale value

bit 3 TxSOSCEN: Secondary Oscillator Enable Control bit

1 = Dedicated Secondary oscillator circuit enabled

0 = Dedicated Secondary oscillator circuit disabled

bit 2 TxSYNC: Timer1/3/5 External Clock Input Synchronization Control bit

$\underline{\mathsf{TMRxCS}} < 1:0 > = 1X$

1 = Do not synchronize external clock input

0 = Synchronize external clock input with system clock (Fosc)

$\underline{\mathsf{TMRxCS}} < 1:0 > = 0X$

This bit is ignored. Timer 1/3/5 uses the internal clock when TMRxCS<1:0> = 1x.

bit 1 TxRD16: 16-Bit Read/Write Mode Enable bit

1 = Enables register read/write of Timer1/3/5 in one 16-bit operation

0 = Enables register read/write of Timer1/3/5 in two 8-bit operation

bit 0 TMRxON: Timer1/3/5 On bit

1 = Enables Timer1/3/5

$0 = \text{Stops Timer} \frac{1}{3}$

Clears Timer1/3/5 Gate flip-flop

## 15.4 I<sup>2</sup>C Mode Operation

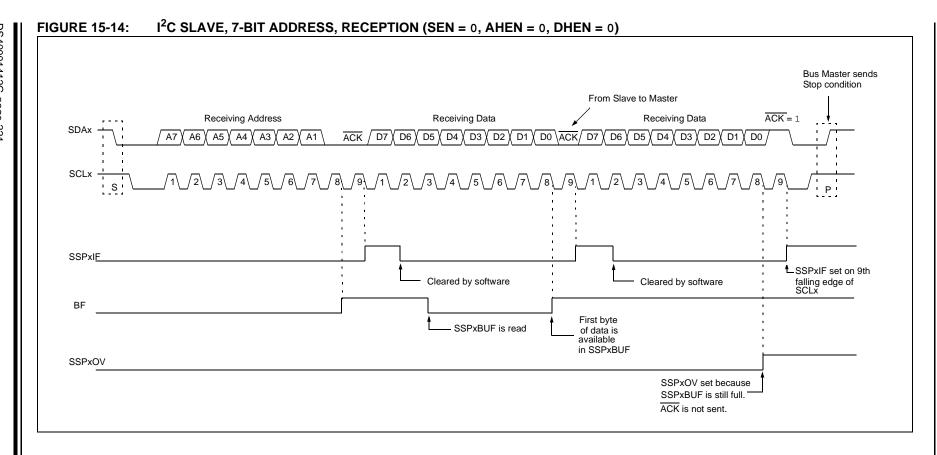

All MSSPx I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and 2 interrupt flags interface the module with the PIC microcontroller and user software. Two pins, SDAx and SCLx, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

#### 15.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the 8th falling edge of the SCLx line, the device outputting data on the SDAx changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCLx, is provided by the master. Data is valid to change while the SCLx signal is low, and sampled on the rising edge of the clock. Changes on the SDAx line while the SCLx line is high define special conditions on the bus, explained below.

## 15.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Phillips  $I^2C$  specification.

## 15.4.3 SDAx AND SCLx PINS

Selection of any I<sup>2</sup>C mode with the SSPxEN bit set, forces the SCLx and SDAx pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

## 15.4.4 SDAx HOLD TIME

The hold time of the SDAx pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDAx is held valid after the falling edge of SCLx. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

TABLE 15-1: I<sup>2</sup>C BUS TERMS

| TERM                | Description                                                                                                                                                                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                      |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                       |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                            |

| Slave               | The device addressed by the master.                                                                                                                                                 |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                   |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                 |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                              |

| Idle                | No master is controlling the bus, and both SDAx and SCLx lines are high.                                                                                                            |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                        |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                        |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                 |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                |

| Read Request        | Master sends an address byte with the R/W bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus holds SCLx low to stall communication.                                                                                                                     |

| Bus Collision       | Any time the SDAx line is sampled low by the module while it is outputting and expected high state.                                                                                 |

#### **REGISTER 15-3:** SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0 | R/C/HS-0 | R/W-0  | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|----------|--------|-------|------------|-------|-------|-------|--|--|

| WCOL     | SSPxOV   | SSPxEN | CKP   | SSPxM<3:0> |       |       |       |  |  |

| bit 7    |          |        |       |            |       |       | bit 0 |  |  |

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared HS = Bit is set by hardware C = User cleared

bit 7 WCOL: Write Collision Detect bit

Master mode:

- 1 = A write to the SSPxBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

- 0 = No collision

Slave mode:

- 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

- SSPxOV: Receive Overflow Indicator bit<sup>(1)</sup>

In SPI mode:

bit 6

- 1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPxBUF, even if only transmitting data, to avoid setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register (must be cleared in software).

- 0 = No overflow

In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPxBUF register is still holding the previous byte. SSPxOV is a "don't care" in Transmit mode (must be cleared in software).

- bit 5 SSPxEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output In SPI mode:

- $\overline{1}$  = Enables serial port and configures SCKx, SDOx, SDIx and  $\overline{SSx}$  as the source of the serial port pins<sup>(2)</sup>

- 0 = Disables serial port and configures these pins as I/O port pins

In I<sup>2</sup>C mode:

- 1 = Enables the serial port and configures the SDAx and SCLx pins as the source of the serial port pins (3)

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4 CKP: Clock Polarity Select bit

In SPI mode:

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

In I2C Slave mode:

SCLx release contro

1 = Enable clock

0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

In I<sup>2</sup>C Master mode:

Unused in this mode

## REGISTER 15-3: SSPxCON1: SSPx CONTROL REGISTER 1 (CONTINUED)

bit 3-0 SSPxM<3:0>: Synchronous Serial Port Mode Select bits 0000 = SPI Master mode, clock = Fosc/4 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64 0011 = SPI Master mode, clock = TMR2 output/2 0100 = SPI Slave mode, clock = SCKx pin, SSx pin control enabled 0101 = SPI Slave mode, clock = SCKx pin,  $\overline{SSx}$  pin control disabled,  $\overline{SSx}$  can be used as I/O pin  $0110 = I^2C$  Slave mode, 7-bit address  $0111 = I^2C$  Slave mode, 10-bit address  $1000 = I^2C$  Master mode, clock = Fosc /  $(4 * (SSPxADD+1))^{(4)}$ 1001 = Reserved 1010 = SPI Master mode, clock = Fosc/(4 \* (SSPxADD+1))  $1011 = I^2C$  firmware controlled Master mode (slave idle) 1100 = Reserved 1101 = Reserved 1110 = I<sup>2</sup>C Slave mode, 7-bit address with Start and Stop bit interrupts enabled 1111 = I<sup>2</sup>C Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- Note 1: In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register.

- 2: When enabled, these pins must be properly configured as input or output.

- 3: When enabled, the SDAx and SCLx pins must be configured as inputs.

- 4: SSPxADD values of 0, 1 or 2 are not supported for I<sup>2</sup>C mode.

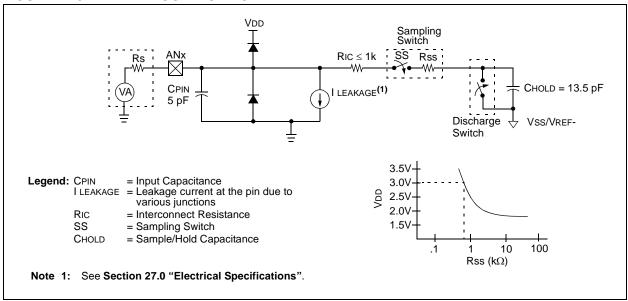

FIGURE 17-5: ANALOG INPUT MODEL

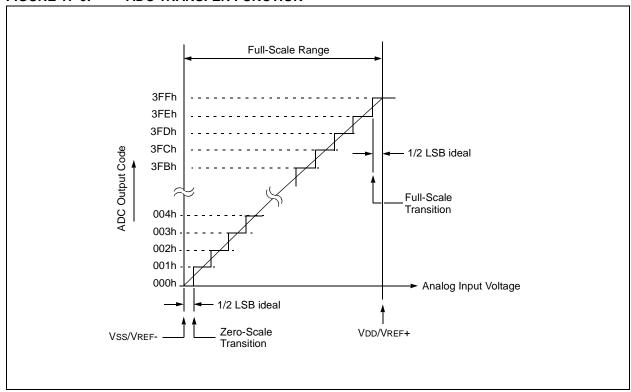

## FIGURE 17-6: ADC TRANSFER FUNCTION

TABLE 18-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name     | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3                  | Bit 2     | Bit 1     | Bit 0  | Register on Page |

|----------|----------|-----------|--------|--------|------------------------|-----------|-----------|--------|------------------|

| ANSELA   | _        | _         | ANSA5  | _      | ANSA3                  | ANSA2     | ANSA1     | ANSA0  | 149              |

| ANSELB   | _        | _         | ANSB5  | ANSB4  | ANSB3                  | ANSB2     | ANSB1     | ANSB0  | 150              |

| CM2CON1  | MC1OUT   | MC2OUT    | C1RSEL | C2RSEL | C1HYS                  | C2HYS     | C1SYNC    | C2SYNC | 309              |

| CM1CON0  | C1ON     | C1OUT     | C1OE   | C1POL  | C1SP                   | C1R       | C1CH<1:0> |        | 308              |

| CM2CON0  | C2ON     | C2OUT     | C2OE   | C2POL  | C2SP                   | C2SP      |           | 308    |                  |

| VREFCON1 | DACEN    | DACLPS    | DACOE  | _      | - DACPSS<1:0> - DACNSS |           |           | 335    |                  |

| VREFCON2 | _        | _         | _      |        |                        | DACR<4:0> | >         |        | 336              |

| VREFCON0 | FVREN    | FVRST     | FVRS   | <1:0>  | _                      | _         | _         | _      | 332              |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE                   | TMR0IF    | INT0IF    | RBIF   | 109              |

| IPR2     | OSCFIP   | C1IP      | C2IP   | EEIP   | BCL1IP                 | HLVDIP    | TMR3IP    | CCP2IP | 122              |

| PIE2     | OSCFIE   | C1IE      | C2IE   | EEIE   | BCL1IE                 | HLVDIE    | TMR3IE    | CCP2IE | 118              |

| PIR2     | OSCFIF   | C1IF      | C2IF   | EEIF   | BCL1IF                 | HLVDIF    | TMR3IF    | CCP2IF | 113              |

| PMD2     | _        | _         | _      | _      | CTMUMD                 | CMP2MD    | CMP1MD    | ADCMD  | 54               |

| TRISA    | TRISA7   | TRISA6    | TRISA5 | TRISA4 | TRISA3                 | TRISA2    | TRISA1    | TRISA0 | 151              |

| TRISB    | TRISB7   | TRISB6    | TRISB5 | TRISB4 | TRISB3                 | TRISB2    | TRISB1    | TRISB0 | 151              |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used by the comparator module.

The module uses the edge Status bits to control the current source output to external analog modules (such as the A/D Converter). Current is only supplied to external modules when only one (but not both) of the Status bits is set, and shuts current off when both bits are either set or cleared. This allows the CTMU to measure current only during the interval between edges. After both Status bits are set, it is necessary to clear them before another measurement is taken. Both bits should be cleared simultaneously, if possible, to avoid re-enabling the CTMU current source.

In addition to being set by the CTMU hardware, the edge Status bits can also be set by software. This is also the user's application to manually enable or disable the current source. Setting either one (but not both) of the bits enables the current source. Setting or clearing both bits at once disables the source.

#### 19.1.5 INTERRUPTS

The CTMU sets its interrupt flag (PIR3<2>) whenever the current source is enabled, then disabled. An interrupt is generated only if the corresponding interrupt enable bit (PIE3<2>) is also set. If edge sequencing is not enabled (i.e., Edge 1 must occur before Edge 2), it is necessary to monitor the edge Status bits and determine which edge occurred last and caused the interrupt.

#### 19.2 CTMU Module Initialization

The following sequence is a general guideline used to initialize the CTMU module:

- Select the current source range using the IRNG bits (CTMUICON<1:0>).

- Adjust the current source trim using the ITRIM bits (CTMUICON<7:2>).

- Configure the edge input sources for Edge 1 and Edge 2 by setting the EDG1SEL and EDG2SEL bits (CTMUCONL<3:2 and 6:5>).

- Configure the input polarities for the edge inputs using the EDG1POL and EDG2POL bits (CTMUCONL<4,7>). The default configuration is for negative edge polarity (high-to-low transitions).

- Enable edge sequencing using the EDGSEQEN bit (CTMUCONH<2>). By default, edge sequencing is disabled.

- Select the operating mode (Measurement or Time Delay) with the TGEN bit. The default mode is Time/Capacitance Measurement.

- Discharge the connected circuit by setting the IDISSEN bit (CTMUCONH<1>); after waiting a sufficient time for the circuit to discharge, clear IDISSEN.

- 8. Disable the module by clearing the CTMUEN bit (CTMUCONH<7>).

- 9. Enable the module by setting the CTMUEN bit.

- 10. Clear the Edge Status bits: EDG2STAT and EDG1STAT (CTMUCONL<1:0>).

- 11. Enable both edge inputs by setting the EDGEN bit (CTMUCONH<3>).

Depending on the type of measurement or pulse generation being performed, one or more additional modules may also need to be initialized and configured with the CTMU module:

- Edge Source Generation: In addition to the external edge input pins, both Timer1 and the Output Compare/PWM1 module can be used as edge sources for the CTMU.

- Capacitance or Time Measurement: The CTMU module uses the A/D Converter to measure the voltage across a capacitor that is connected to one of the analog input channels.

- Pulse Generation: When generating system clock independent output pulses, the CTMU module uses Comparator 2 and the associated comparator voltage reference.

## 23.6 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

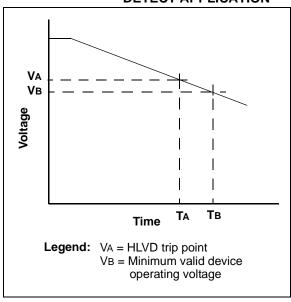

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

FIGURE 23-4: TYPICAL LOW-VOLTAGE DETECT APPLICATION

# 24.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other PIC microcontroller devices.

The user program memory is divided into three or five blocks, depending on the device. One of these is a Boot Block of 0.5K or 2K bytes, depending on the device. The remainder of the memory is divided into individual blocks on binary boundaries.

Each of the blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 24-2 shows the program memory organization for 8, 16 and 32-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 24-5.

FIGURE 24-2: CODE-PROTECTED PROGRAM MEMORY FOR PIC18(L)F2X/4XK22

|                                                     | MEMORY S                                      | IZE/DEVICE                                    |                                                | Block Code Protection           |

|-----------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|---------------------------------|

| 8 Kbytes 16 Kbytes (PIC18(L)FX3K22) (PIC18(L)FX4K22 |                                               | 32 Kbytes<br>(PIC18(L)FX5K22)                 | 64 Kbytes<br>(PIC18(L)FX6K22)                  | Controlled By:                  |

| Boot Block<br>(000h-1FFh)                           | Boot Block<br>(000h-7FFh)                     | Boot Block<br>(000h-7FFh)                     | Boot Block<br>(000h-7FFh)                      | CPB, WRTB, EBTRB                |

| Block 0<br>(200h-FFFh)                              | Block 0<br>(800h-1FFFh)                       | Block 0<br>(800h-1FFFh)                       | Block 0<br>(800h-3FFFh)                        | CP0, WRT0, EBTR0                |

| Block 1<br>(1000h-1FFFh)                            | Block 1<br>(2000h-3FFFh)                      | Block 1<br>(2000h-3FFFh)                      | Block 1<br>(4000h-7FFFh)                       | CP1, WRT1, EBTR1                |

|                                                     |                                               | Block 2<br>(4000h-5FFFh)                      | Block 2<br>(8000h-BFFFh)                       | CP2, WRT2, EBTR2                |

|                                                     |                                               | Block 3<br>(6000h-7FFFh)                      | Block 3<br>(C000h-FFFFh)                       | CP3, WRT3, EBTR3                |

| Unimplemented<br>Read '0's<br>(2000h-1FFFFFh)       | Unimplemented<br>Read '0's<br>(4000h-1FFFFFh) | Unimplemented<br>Read '0's<br>(8000h-1FFFFFh) | Unimplemented<br>Read '0's<br>(10000h-1FFFFFh) | (Unimplemented<br>Memory Space) |

TABLE 24-5: CONFIGURATION REGISTERS ASSOCIATED WITH CODE PROTECTION

| File    | Name     | Bit 7 | Bit 6 | Bit 5               | Bit 4 | Bit 3                | Bit 2                | Bit 1 | Bit 0 |

|---------|----------|-------|-------|---------------------|-------|----------------------|----------------------|-------|-------|

| 300008h | CONFIG5L | -     | _     | _                   | _     | CP3 <sup>(1)</sup>   | CP2 <sup>(1)</sup>   | CP1   | CP0   |

| 300009h | CONFIG5H | CPD   | СРВ   | _                   | _     | _                    | _                    | _     | _     |

| 30000Ah | CONFIG6L | _     | _     | _                   | _     | WRT3 <sup>(1)</sup>  | WRT2 <sup>(1)</sup>  | WRT1  | WRT0  |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC <sup>(2)</sup> | _     | _                    | _                    | _     | _     |

| 30000Ch | CONFIG7L | _     | _     | _                   | _     | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1 | EBTR0 |

| 30000Dh | CONFIG7H | _     | EBTRB | _                   | _     | _                    | _                    | _     | _     |

Legend: Shaded bits are unimplemented.

Note 1: Available on PIC18(L)FX5K22 and PIC18(L)FX6K22 devices only.

2: In user mode, this bit is read-only and cannot be self-programmed.

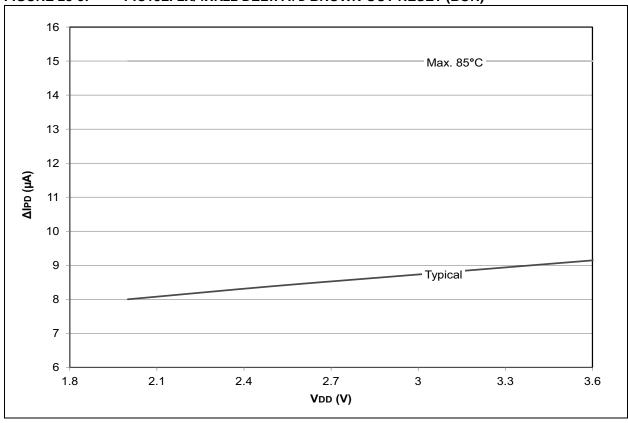

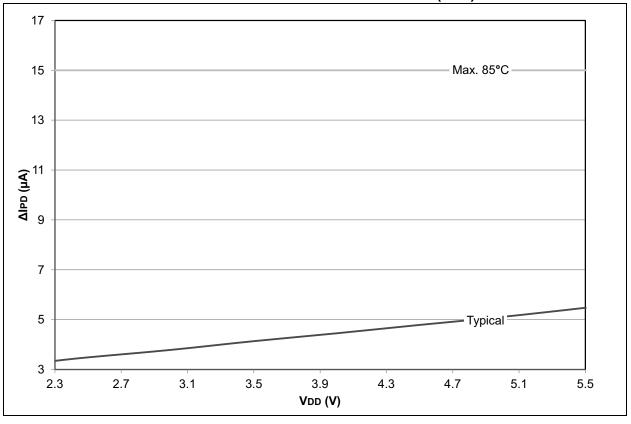

FIGURE 28-5: PIC18LF2X/4XK22 DELTA IPD BROWN-OUT RESET (BOR)

FIGURE 28-6: PIC18F2X/4XK22 DELTA IPD BROWN-OUT RESET (BOR)

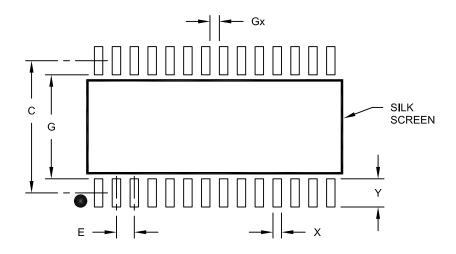

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |      |      |

|--------------------------|----|-------------|------|------|

| Dimension Limits         |    | MIN         | NOM  | MAX  |

| Contact Pitch            | Е  | 1.27 BSC    |      |      |

| Contact Pad Spacing      | С  |             | 9.40 |      |

| Contact Pad Width (X28)  | Х  |             |      | 0.60 |

| Contact Pad Length (X28) | Υ  |             |      | 2.00 |

| Distance Between Pads    | Gx | 0.67        |      |      |

| Distance Between Pads    | G  | 7.40        |      |      |

#### Notes:

Note:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A