Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

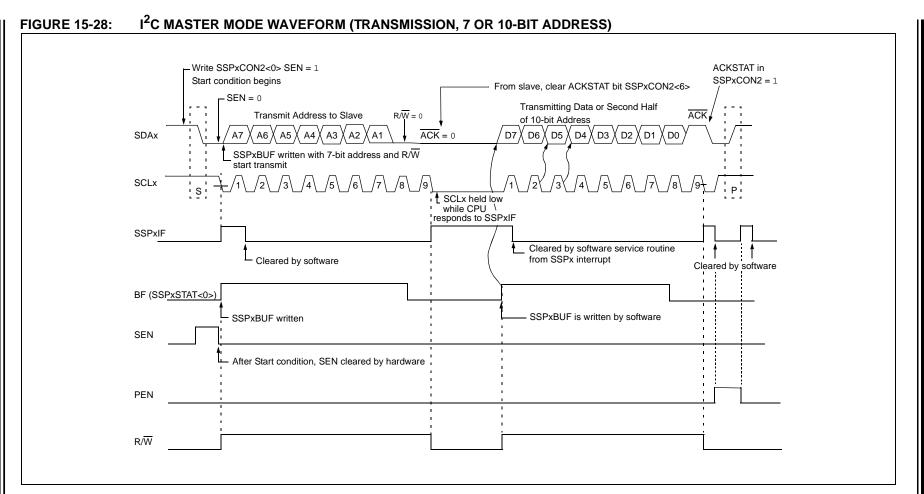

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 × 8                                                                    |

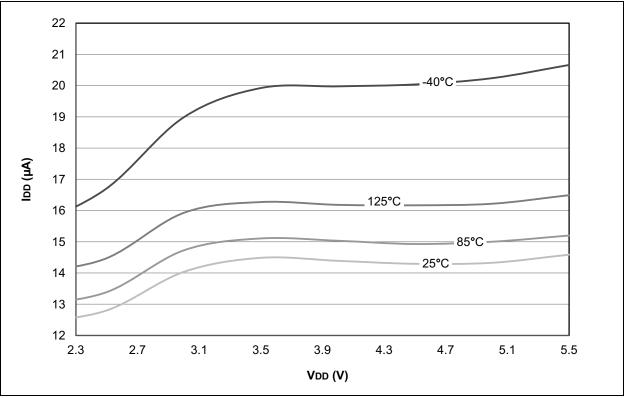

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

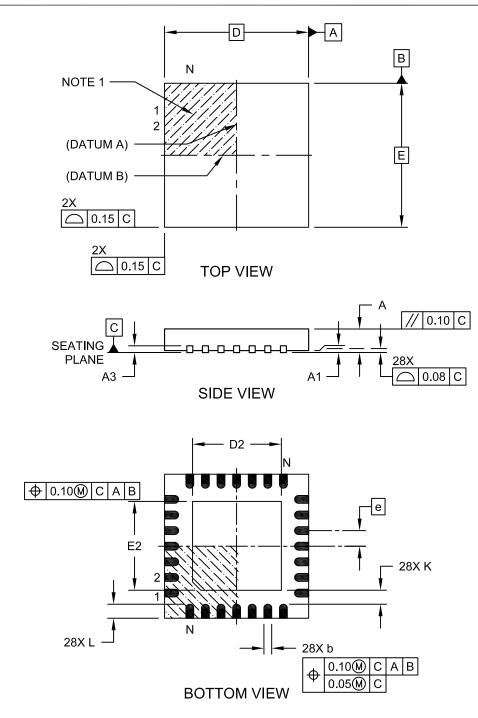

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k22-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABL    | _E 3:   | P       | PIC18( | (L)F4) | (K22 F | PIN SUM    | MARY  |          |                     |                            |            |              |                                               |            |         |              |

|---------|---------|---------|--------|--------|--------|------------|-------|----------|---------------------|----------------------------|------------|--------------|-----------------------------------------------|------------|---------|--------------|

| 40-PDIP | 40-UQFN | 44-TQFP | 44-QFN | 0/     | Analog | Comparator | СТМИ  | SR Latch | Reference           | (E)CCP                     | EUSART     | MSSP         | Timers                                        | Interrupts | Pull-up | Basic        |

| 2       | 17      | 19      | 19     | RA0    | AN0    | C12IN0-    |       |          |                     |                            |            |              |                                               |            |         |              |

| 3       | 18      | 20      | 20     | RA1    | AN1    | C12IN1-    |       |          |                     |                            |            |              |                                               |            |         |              |

| 4       | 19      | 21      | 21     | RA2    | AN2    | C2IN+      |       |          | VREF-<br>DACOU<br>T |                            |            |              |                                               |            |         |              |

| 5       | 20      | 22      | 22     | RA3    | AN3    | C1IN+      |       |          | VREF+               |                            |            |              |                                               |            |         |              |

| 6       | 21      | 23      | 23     | RA4    |        | C10UT      |       | SRQ      |                     |                            |            |              | TOCKI                                         |            |         |              |

| 7       | 22      | 24      | 24     | RA5    | AN4    | C2OUT      |       | SRNQ     | HLVDIN              |                            |            | SS1          |                                               |            |         |              |

| 14      | 29      | 31      | 33     | RA6    |        |            |       |          |                     |                            |            |              |                                               |            |         | OSC2<br>CLKO |

| 13      | 28      | 30      | 32     | RA7    |        |            |       |          |                     |                            |            |              |                                               |            |         | OSC1<br>CLKI |

| 33      | 8       | 8       | 9      | RB0    | AN12   |            |       | SRI      |                     | FLT0                       |            |              |                                               | INT0       | Υ       |              |

| 34      | 9       | 9       | 10     | RB1    | AN10   | C12IN3-    |       |          |                     |                            |            |              |                                               | INT1       | Υ       |              |

| 35      | 10      | 10      | 11     | RB2    | AN8    |            | CTED1 |          |                     |                            |            |              |                                               | INT2       | Υ       |              |

| 36      | 11      | 11      | 12     | RB3    | AN9    | C12IN2-    | CTED2 |          |                     | CCP2<br>P2A <sup>(1)</sup> |            |              |                                               |            | Y       |              |

| 37      | 12      | 14      | 14     | RB4    | AN11   |            |       |          |                     |                            |            |              | T5G                                           | IOC        | Υ       |              |

| 38      | 13      | 15      | 15     | RB5    | AN13   |            |       |          |                     | ССР3<br>РЗА <sup>(3)</sup> |            |              | T1G<br>T3CKI <sup>(2)</sup>                   | IOC        | Y       |              |

| 39      | 14      | 16      | 16     | RB6    |        |            |       |          |                     |                            |            |              |                                               | IOC        | Υ       | PGC          |

| 40      | 15      | 17      | 17     | RB7    |        |            |       |          |                     |                            |            |              |                                               | IOC        | Y       | PGD          |

| 15      | 30      | 32      | 34     | RC0    |        |            |       |          |                     | P2B <sup>(4)</sup>         |            |              | SOSCO<br>T1CKI<br>T3CKI <sup>(2)</sup><br>T3G |            |         |              |

| 16      | 31      | 35      | 35     | RC1    |        |            |       |          |                     | CCP2 <sup>(1)</sup><br>P2A |            |              | SOSCI                                         |            |         |              |

| 17      | 32      | 36      | 36     | RC2    | AN14   |            | CTPLS |          |                     | CCP1<br>P1A                |            |              | T5CKI                                         |            |         |              |

| 18      | 33      | 37      | 37     | RC3    | AN15   |            |       |          |                     |                            |            | SCK1<br>SCL1 |                                               |            |         |              |

| 23      | 38      | 42      | 42     | RC4    | AN16   |            |       |          |                     |                            |            | SDI1<br>SDA1 |                                               |            |         |              |

| 24      | 39      | 43      | 43     | RC5    | AN17   |            |       |          |                     |                            |            | SDO1         |                                               |            |         |              |

| 25      | 40      | 44      | 44     | RC6    | AN18   |            |       |          |                     |                            | TX1<br>CK1 |              |                                               |            |         |              |

| 26      | 1       | 1       | 1      | RC7    | AN19   |            |       |          |                     |                            | RX1<br>DT1 |              |                                               |            |         |              |

| 19      | 34      | 38      | 38     | RD0    | AN20   |            |       |          |                     |                            |            | SCK2<br>SCL2 |                                               |            |         |              |

| 20      | 35      | 39      | 39     | RD1    | AN21   |            |       |          |                     | CCP4                       |            | SDI2<br>SDA2 |                                               |            |         |              |

| 21      | 36      | 40      | 40     | RD2    | AN22   |            |       |          |                     | P2B <sup>(4)</sup>         |            |              |                                               |            |         |              |

| 22      | 37      | 41      | 41     | RD3    | AN23   |            |       |          |                     | P2C                        |            | SS2          |                                               |            |         |              |

| 27      | 2       | 2       | 2      | RD4    | AN24   |            |       |          |                     | P2D                        |            | SD02         |                                               |            |         |              |

| 28      | 3       | 3       | 3      | RD5    | AN25   |            |       |          |                     | P1B                        |            |              |                                               |            |         |              |

| 29      | 4       | 4       | 4      | RD6    | AN26   |            |       |          |                     | P1C                        | TX2<br>CK2 |              |                                               |            |         |              |

| 30      | 5       | 5       | 5      | RD7    | AN27   |            |       |          |                     | P1D                        | RX2<br>DT2 |              |                                               |            |         |              |

| 8       | 23      | 25      | 25     | RE0    | AN5    |            |       |          |                     | ССР3<br>РЗА <sup>(3)</sup> |            |              |                                               |            |         |              |

| TABLE 3: | <b>PIC18(L</b> | .)F4XK22 | PIN | SUMMA | ARY           |

|----------|----------------|----------|-----|-------|---------------|

|          | 1 10 10(L      |          |     |       | <b>\  \  </b> |

Note

1:

CCP2 multiplexed in fuses.

2:

T3CKI multiplexed in fuses.

3:

CCP3/P3A multiplexed in fuses.

4:

P2B multiplexed in fuses.

| OSC Mode               | OSC1 Pin                                              | OSC2 Pin                                              |

|------------------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTOSC with CLKOUT | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RC with IO             | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| INTOSC with IO         | Configured as PORTA, bit 7                            | Configured as PORTA, bit 6                            |

| EC with IO             | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC with CLKOUT         | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT, HS             | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

#### 2.11 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS<1:0>) bits of the OSCCON register.

PIC18(L)F2X/4XK22 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

#### 2.11.1 SYSTEM CLOCK SELECT (SCS<1:0>) BITS

The System Clock Select (SCS<1:0>) bits of the OSCCON register select the system clock source that is used for the CPU and peripherals.

- When SCS<1:0> = 00, the system clock source is determined by configuration of the FOSC<3:0> bits in the CONFIG1H Configuration register.

- When SCS<1:0> = 10, the system clock source is chosen by the internal oscillator frequency selected by the INTSRC bit of the OSCTUNE register, the MFIOSEL bit of the OSCCON2 register and the IRCF<2:0> bits of the OSCCON register.

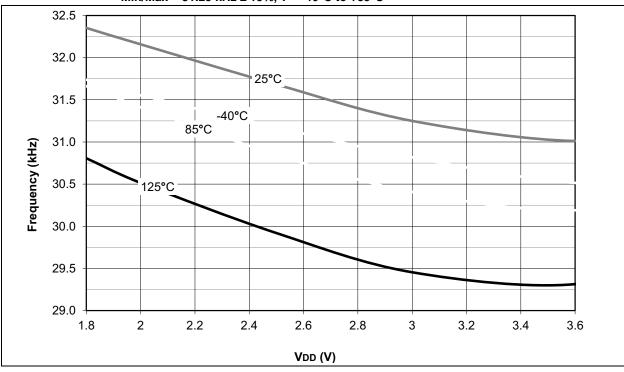

- When SCS<1:0> = 01, the system clock source is the 32.768 kHz secondary oscillator shared with Timer1, Timer3 and Timer5.

After a Reset, the SCS<1:0> bits of the OSCCON register are always cleared.

Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS<1:0> bits of the OSCCON register. The user can monitor the SOSCRUN, MFIOFS and LFIOFS bits of the OSCCON2 register, and the HFIOFS and OSTS bits of the OSCCON register to determine the current system clock source.

#### 2.11.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<3:0> bits in the CONFIG1H Configuration register, or from the internal clock source. In particular, when the primary oscillator is the source of the primary clock, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    |                         |

|                 | ;IN FAST REGISTER STACK |

#### 5.2.2 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.2.2.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | •     |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

#### 5.2.2.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

| Address | Name                  | Bit 7          | Bit 6                                     | Bit 5           | Bit 4            | Bit 3                   | Bit 2         | Bit 1    | Bit 0    | <u>Value on</u><br>POR, BOR |  |

|---------|-----------------------|----------------|-------------------------------------------|-----------------|------------------|-------------------------|---------------|----------|----------|-----------------------------|--|

| F68h    | CCPR2H                |                |                                           | Capture/C       | ompare/PWM       | Register 2, Hig         | gh Byte       |          |          | xxxx xxxx                   |  |

| F67h    | CCPR2L                |                |                                           | Capture/C       | ompare/PWM       | Register 2, Lo          | w Byte        |          |          | xxxx xxxx                   |  |

| F66h    | CCP2CON               | P2M<           | <1:0>                                     | DC2E            | 3<1:0>           |                         | CCP2N         | 1<3:0>   |          | 0000 0000                   |  |

| F65h    | PWM2CON               | P2RSEN         |                                           |                 |                  | P2DC<6:0>               |               |          |          | 0000 0000                   |  |

| F64h    | ECCP2AS               | CCP2ASE        |                                           | CCP2AS<2:0      | >                | PSS2A                   | AC<1:0>       | PSS2B    | D<1:0>   | 0000 0000                   |  |

| F63h    | PSTR2CON              | I              | —                                         | —               | STR2SYNC         | STR2D                   | STR2C         | STR2B    | STR2A    | 0 0001                      |  |

| F62h    | IOCB                  | IOCB7          | IOCB6                                     | IOCB5           | IOCB4            | —                       | -             | —        | _        | 1111                        |  |

| F61h    | WPUB                  | WPUB7          | WPUB6                                     | WPUB5           | WPUB4            | WPUB3                   | WPUB2         | WPUB1    | WPUB0    | 1111 1111                   |  |

| Feah    | SLRCON <sup>(2)</sup> |                | _                                         | -               | _                | —                       | SLRC          | SLRB     | SLRA     | 111                         |  |

| F60h    | SLRCON <sup>(1)</sup> | I              | —                                         | —               | SLRE             | SLRD                    | SLRC          | SLRB     | SLRA     | 1 1111                      |  |

| F5Fh    | CCPR3H                |                |                                           | Capture/        | Compare/PWN      | /I Register 3, H        | ligh Byte     |          |          | xxxx xxxx                   |  |

| F5Eh    | CCPR3L                |                |                                           | Capture/        | Compare/PWN      | /I Register 3, L        | ow Byte       |          |          | xxxx xxxx                   |  |

| F5Dh    | CCP3CON               | P3M<           | P3M<1:0> DC3B<1:0> CCP3M<3:0>             |                 |                  |                         |               |          |          |                             |  |

| F5Ch    | PWM3CON               | P3RSEN         | BRSEN P3DC<6:0>                           |                 |                  |                         |               |          |          |                             |  |

| F5Bh    | ECCP3AS               | <b>CCP3ASE</b> |                                           | CCP3AS<2:0      | >                | PSS3A                   | AC<1:0>       | PSS3B    | D<1:0>   | 0000 0000                   |  |

| F5Ah    | PSTR3CON              | _              | _                                         | _               | STR3SYNC         | STR3D                   | STR3C         | STR3B    | STR3A    | 0 0001                      |  |

| F59h    | CCPR4H                |                | Capture/Compare/PWM Register 4, High Byte |                 |                  |                         |               |          |          | xxxx xxxx                   |  |

| F58h    | CCPR4L                |                |                                           | Capture/        | Compare/PWI      | VI Register 4, L        | _ow Byte      |          |          | xxxx xxxx                   |  |

| F57h    | CCP4CON               |                | DC4B<1:0> CCP4M<3:0>                      |                 |                  |                         |               |          |          |                             |  |

| F56h    | CCPR5H                |                | Capture/Compare/PWM Register 5, High Byte |                 |                  |                         |               |          |          |                             |  |

| F55h    | CCPR5L                |                | Capture/Compare/PWM Register 5, Low Byte  |                 |                  |                         |               |          |          |                             |  |

| F54h    | CCP5CON               |                | — — DC5B<1:0> CCP5M<3:0>                  |                 |                  |                         |               |          |          |                             |  |

| F53h    | TMR4                  |                | Timer4 Register                           |                 |                  |                         |               |          |          |                             |  |

| F52h    | PR4                   |                |                                           |                 | Timer4 Pe        | riod Register           |               |          |          | 1111 1111                   |  |

| F51h    | T4CON                 |                |                                           | T4OUT           | PS<3:0>          |                         | TMR4ON        | T4CKP    | S<1:0>   | -000 0000                   |  |

| F50h    | TMR5H                 |                | Holding R                                 | egister for the | Most Significa   | ant Byte of the         | 16-bit TMR5 R | egister  |          | 0000 0000                   |  |

| F4Fh    | TMR5L                 |                |                                           | Least Signif    | icant Byte of th | ne 16-bit TMR5          | 5 Register    |          |          | 0000 0000                   |  |

| F4Eh    | T5CON                 | TMR5C          | S<1:0>                                    | T5CKF           | PS<1:0>          | T5SOSCEN                | T5SYNC        | T5RD16   | TMR5ON   | 0000 0000                   |  |

| F4Dh    | T5GCON                | TMR5GE         | T5GPOL                                    | T5GTM           | T5GSPM           | T <u>5GGO</u> /<br>DONE | T5GVAL        | T5GSS    | S<1:0>   | 0000 0x00                   |  |

| F4Ch    | TMR6                  |                | •                                         | •               | Timer6 Regist    | er                      | •             | •        |          | 0000 0000                   |  |

| F4Bh    | PR6                   |                |                                           |                 | Timer6 Period    | Register                |               |          |          | 1111 1111                   |  |

| F4Ah    | T6CON                 |                |                                           | T6OUT           | PS<3:0>          |                         | TMR6ON        | T6CKP    | S<1:0>   | -000 0000                   |  |

| F49h    | CCPTMRS0              | C3TSE          | L<1:0>                                    | _               | C2TSE            | L<1:0>                  | _             | C1TSE    | L<1:0>   | 00-0 0-00                   |  |

| F48h    | CCPTMRS1              |                | _                                         | _               | _                | C5TSE                   | EL<1:0>       | C4TSE    | L<1:0>   | 0000                        |  |

| F47h    | SRCON0                | SRLEN          |                                           | SRCLK<2:0>      | •                | SRQEN                   | SRNQEN        | SRPS     | SRPR     | 0000 0000                   |  |

| F46h    | SRCON1                | SRSPE          | SRSCKE                                    | SRSC2E          | SRSC1E           | SRRPE                   | SRRCKE        | SRRC2E   | SRRC1E   | 0000 0000                   |  |

| F45h    | CTMUCONH              | CTMUEN         | _                                         | CTMUSIDL        | TGEN             | EDGEN                   | EDGSEQEN      | IDISSEN  | CTTRIG   | 0000 0000                   |  |

| F44h    | CTMUCONL              | EDG2POL        | EDG2S                                     | EL<1:0>         | EDG1POL          | EDG1S                   | EL<1:0>       | EDG2STAT | EDG1STAT | 0000 0000                   |  |

| F43h    | CTMUICON              |                |                                           | ITRI            | M<5:0>           |                         |               | IRNG     | <1:0>    | 0000 0000                   |  |

| F42h    | VREFCON0              | FVREN          | FVRST                                     | FVRS            | S<1:0>           | _                       | _             | —        | _        | 0001                        |  |

| F41h    | VREFCON1              | DACEN          | DACLPS                                    | DACOE           | _                | DACPS                   | SS<1:0>       | —        | DACNSS   | 000- 00-0                   |  |

| F40h    | VREFCON2              | _              | —                                         | —               |                  |                         | DACR<4:0>     |          |          | 0 0000                      |  |

| F3Fh    | PMD0                  | UART2MD        | UART1MD                                   | TMR6MD          | TMR5MD           | TMR4MD                  | TMR3MD        | TMR2MD   | TMR1MD   | 0000 0000                   |  |

| F3Eh    | PMD1                  | MSSP2MD        | MSSP1MD                                   | _               | CCP5MD           | CCP4MD                  | CCP3MD        | CCP2MD   | CCP1MD   | 00-0 0000                   |  |

| F3Dh    | PMD2                  | _              | _                                         | _               | _                | CTMUMD                  | CMP2MD        | CMP1MD   | ADCMD    | 0000                        |  |

| F3Ch    | ANSELE <sup>(1)</sup> | _              | _                                         | _               | _                | _                       | ANSE2         | ANSE1    | ANSE0    | 111                         |  |

| F3Bh    | ANSELD <sup>(1)</sup> | ANSD7          | ANSD6                                     | ANSD5           | ANSD4            | ANSD3                   | ANSD2         | ANSD1    | ANSD0    | 1111 1111                   |  |

#### TABLE 5-2: REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED)

$\label{eq:Legend: Legend: Legend: Legend: u = unchanged, --= unimplemented, q = value depends on condition$

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

#### 6.4 Reading the Flash Program Memory

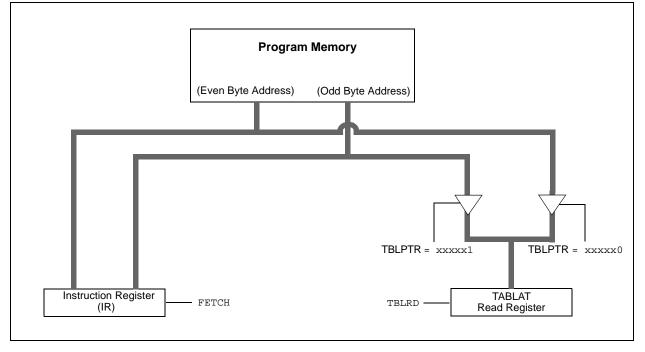

The TBLRD instruction retrieves data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU |   | Load TBLPTR with the base<br>address of the word |

|-----------|----------------|----------------------------|---|--------------------------------------------------|

|           | MOVLW          | CODE_ADDR_HIGH             | ' | address of the word                              |

|           | MOVWF          | TBLPTRH                    |   |                                                  |

|           |                |                            |   |                                                  |

|           | MOVLW          | CODE_ADDR_LOW              |   |                                                  |

|           | MOVWF          | TBLPTRL                    |   |                                                  |

| READ_WORD |                |                            |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVF           | TABLAT, W                  | ; | get data                                         |

|           | MOVWF          | WORD_EVEN                  |   |                                                  |

|           | TBLRD*+        |                            | ; | read into TABLAT and increment                   |

|           | MOVFW          | TABLAT, W                  | ; | get data                                         |

|           | MOVF           | WORD_ODD                   |   |                                                  |

|           |                |                            |   |                                                  |

| IADLE 12 | 0. KEO   |           |               |                 |                       |                |         |         |                            |

|----------|----------|-----------|---------------|-----------------|-----------------------|----------------|---------|---------|----------------------------|

| Name     | Bit 7    | Bit 6     | Bit 5         | Bit 4           | Bit 3                 | Bit 2          | Bit 1   | Bit 0   | Reset<br>Values on<br>Page |

| ANSELB   | _        | —         | ANSB5         | ANSB4           | ANSB3                 | ANSB2          | ANSB1   | ANSB0   | 150                        |

| ANSELC   | ANSC7    | ANSC6     | ANSC5         | ANSC4           | ANSC3                 | ANSC2          | _       | _       | 150                        |

| INTCON   | GIE/GIEH | PEIE/GIEL | TMR0IE        | INTOIE          | RBIE                  | TMR0IF         | INT0IF  | RBIF    | 109                        |

| IPR1     | _        | ADIP      | RC1IP         | TX1IP           | SSP1IP                | CCP1IP         | TMR2IP  | TMR1IP  | 121                        |

| IPR2     | OSCFIP   | C1IP      | C2IP          | EEIP            | BCL1IP                | HLVDIP         | TMR3IP  | CCP2IP  | 122                        |

| IPR3     | SSP2IP   | BCL2IP    | RC2IP         | TX2IP           | CTMUIP                | TMR5GIP        | TMR3GIP | TMR1GIP | 123                        |

| IPR5     | —        | _         | —             |                 | _                     | TMR6IP         | TMR5IP  | TMR4IP  | 124                        |

| PIE1     | _        | ADIE      | RC1IE         | TX1IE           | SSP1IE                | CCP1IE         | TMR2IE  | TMR1IE  | 117                        |

| PIE2     | OSCFIE   | C1IE      | C2IE          | EEIE            | BCL1IE                | HLVDIE         | TMR3IE  | CCP2IE  | 118                        |

| PIE3     | SSP2IE   | BCL2IE    | RC2IE         | TX2IE           | CTMUIE                | TMR5GIE        | TMR3GIE | TMR1GIE | 119                        |

| PIE5     |          | _         |               | _               | —                     | TMR6IE         | TMR5IE  | TMR4IE  | 120                        |

| PIR1     |          | ADIF      | RC1IF         | TX1IF           | SSP1IF                | CCP1IF         | TMR2IF  | TMR1IF  | 112                        |

| PIR2     | OSCFIF   | C1IF      | C2IF          | EEIF            | BCL1IF                | HLVDIF         | TMR3IF  | CCP2IF  | 113                        |

| PIR3     | SSP2IF   | BCL2IF    | RC2IF         | TX2IF           | CTMUIF                | TMR5GIF        | TMR3GIF | TMR1GIF | 114                        |

| PIR5     |          | _         |               | _               | —                     | TMR6IF         | TMR5IF  | TMR4IF  | 116                        |

| PMD0     | UART2MD  | UART1MD   | TMR6MD        | TMR5MD          | TMR4MD                | TMR3MD         | TMR2MD  | TMR1MD  | 52                         |

| T1CON    | TMR1C    | S<1:0>    | T1CK          | PS<1:0>         | T1SOSCEN              | T1SYNC         | T1RD16  | TMR10N  | 166                        |

| T1GCON   | TMR1GE   | T1GPOL    | T1GTM         | T1GSPM          | T1GGO/DONE            | T1GVAL         | T1GSS   | 167     |                            |

| T3CON    | TMR3C    | S<1:0>    | T3CK          | PS<1:0>         | T3SOSCEN              | T3SYNC         | T3RD16  | TMR3ON  | 166                        |

| T3GCON   | TMR3GE   | T3GPOL    | T3GTM         | T3GSPM          | T3GGO/DONE            | T3GVAL         | T3GSS   | S<1:0>  | 167                        |

| T5CON    | TMR5C    | S<1:0>    | T5CKI         | PS<1:0>         | T5SOSCEN              | T5SYNC         | T5RD16  | TMR5ON  | 166                        |

| T5GCON   | TMR5GE   | T5GPOL    | T5GTM         | T5GSPM          | T5GGO/DONE            | T5GVAL         | T5GSS   | S<1:0>  | 167                        |

| TMR1H    |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR1 Reg | gister  |         | _                          |

| TMR1L    |          |           | Least S       | ignificant Byte | of the 16-bit TMR1    | Register       |         |         | _                          |

| TMR3H    |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR3 Reg | gister  |         | _                          |

| TMR3L    |          |           | Least S       | ignificant Byte | of the 16-bit TMR3    | Register       |         |         |                            |

| TMR5H    |          | Holdin    | g Register fo | r the Most Sign | ificant Byte of the 1 | 6-bit TMR5 Reg | gister  |         | _                          |

| TMR5L    |          |           | Least S       | ignificant Byte | of the 16-bit TMR5    | Register       |         |         | _                          |

| TRISB    | TRISB7   | TRISB6    | TRISB5        | TRISB4          | TRISB3                | TRISB2         | TRISB1  | TRISB0  | 151                        |

| TRISC    | TRISC7   | TRISC6    | TRISC5        | TRISC4          | TRISC3                | TRISC2         | TRISC1  | TRISC0  | 151                        |

#### TABLE 12-6: REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

#### TABLE 12-7: CONFIGURATION REGISTERS ASSOCIATED WITH TIMER1/3/5

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|----------------------------|

| CONFIG3H | MCLRE |       | P2BMX | T3CMX | HFOFST | CCP3MX | PBADEN | CCP2MX | 348                        |

#### EXAMPLE 19-3: CAPACITANCE CALIBRATION ROUTINE

```

#include "p18cxxx.h"

#define COUNT 25

//@ 8MHz INTFRC = 62.5 us.

#define ETIME COUNT*2.5

//time in uS

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define ADSCALE 1023

//for unsigned conversion 10 sig

bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

int main(void)

{

int i;

int j = 0;

//index for loop

unsigned int Vread = 0;

float CTMUISrc, CTMUCap, Vavg, VTot, Vcal;

//assume CTMU and A/D have been set up correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

CTMUCONLbits.EDG1STAT = 0;

// Set Edge status bits to zero

CTMUCONLbits.EDG2STAT = 0;

for(j=0;j<10;j++)</pre>

{

CTMUCONHbits.IDISSEN = 1;

//drain charge on the circuit

//wait 125us

DELAY;

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

//wait for 125us

DELAY;

CTMUCONLbits.EDG1STAT = 0;

//Stop charging circuit

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

//CTMUISrc is in 1/100ths of uA

CTMUISrc = Vcal/RCAL;

CTMUCap = (CTMUISrc*ETIME/Vcal)/100;

```

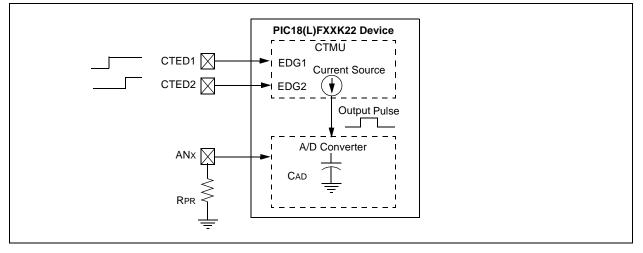

### 19.5 Measuring Time with the CTMU Module

Time can be precisely measured after the ratio (C/I) is measured from the current and capacitance calibration step by following these steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Set EDG2STAT.

- 4. Perform an A/D conversion.

- 5. Calculate the time between edges as T = (C/I) \* V, where *I* is calculated in the current calibration step (Section 19.3.1 "Current Source Calibration"), *C* is calculated in the capacitance calibration step (Section 19.3.2 "Capacitance Calibration") and *V* is measured by performing the A/D conversion.

It is assumed that the time measured is small enough that the capacitance, *C*OFFSET, provides a valid voltage to the A/D Converter. For the smallest time measurement, always set the A/D Channel Select register (AD1CHS) to an unused A/D channel; the corresponding pin for which is not connected to any circuit board trace. This minimizes added stray capacitance, keeping the total circuit capacitance close to that of the A/D Converter itself (4-5 pF). To measure longer time intervals, an external capacitor may be connected to an A/D channel and this channel selected when making a time measurement.

### FIGURE 19-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

#### 24.2 Register Definitions: Configuration Word

REGISTER 24-1: CONFIG1H: CONFIGURATION REGISTER 1 HIGH

| REGISTE    | R 24-1: CONF<br>R/P-0                                                                                                                                                                             | R/P-1                                                                                                                                                                                   | R/P-0                                                                                                                                                                                                |                                                                                                                                               | 1 HIGH<br>R/P-1                                           | R/P-0          |       |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|-------|--|--|--|--|

| IESO       | FCMEN                                                                                                                                                                                             | PRICLKEN                                                                                                                                                                                | R/P-0<br>PLLCFG                                                                                                                                                                                      | R/P-0                                                                                                                                         |                                                           | R/P-0<br><3:0> | R/P-1 |  |  |  |  |

| bit 7      | FOWEIN                                                                                                                                                                                            | FRIGEREN                                                                                                                                                                                | FLLCFG                                                                                                                                                                                               |                                                                                                                                               | FUSC                                                      | <0.0>          | bit C |  |  |  |  |

|            |                                                                                                                                                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                                      |                                                                                                                                               |                                                           |                |       |  |  |  |  |

| Legend:    |                                                                                                                                                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                                      |                                                                                                                                               |                                                           |                |       |  |  |  |  |

| R = Reada  | able bit                                                                                                                                                                                          | P = Programr                                                                                                                                                                            | nable bit                                                                                                                                                                                            | U = Unimple                                                                                                                                   | mented bit, read                                          | d as '0'       |       |  |  |  |  |

| -n = Value | when device is un                                                                                                                                                                                 | programmed                                                                                                                                                                              |                                                                                                                                                                                                      | x = Bit is unk                                                                                                                                | nown                                                      |                |       |  |  |  |  |

| bit 7      | 1 = Oscillator                                                                                                                                                                                    | rnal/External O                                                                                                                                                                         | ode enabled                                                                                                                                                                                          | nover bit                                                                                                                                     |                                                           |                |       |  |  |  |  |

| bit 6      | FCMEN <sup>(1)</sup> : F<br>1 = Fail-Safe                                                                                                                                                         | ail-Safe Clock I<br>Clock Monitor<br>Clock Monitor                                                                                                                                      | Monitor Enable<br>enabled                                                                                                                                                                            | e bit                                                                                                                                         |                                                           |                |       |  |  |  |  |

| bit 5      | 1 = Primary (                                                                                                                                                                                     | PRICLKEN: Primary Clock Enable bit<br>1 = Primary Clock is always enabled<br>0 = Primary Clock can be disabled by software                                                              |                                                                                                                                                                                                      |                                                                                                                                               |                                                           |                |       |  |  |  |  |

| bit 4      | 1 = 4 x PLL a                                                                                                                                                                                     | PLL Enable bi<br>always enabled<br>s under softwar                                                                                                                                      | , Oscillator mu                                                                                                                                                                                      |                                                                                                                                               | E<6>)                                                     |                |       |  |  |  |  |

| bit 3-0    | 1111 = Exte<br>1110 = Exte<br>1101 = EC c<br>1100 = EC c<br>1011 = EC c<br>1010 = EC c<br>1010 = Inter<br>1000 = Inter<br>0111 = Exte<br>0110 = Exte<br>0101 = EC c<br>0100 = EC c<br>0100 = EC c | sscillator (medi<br>oscillator, CLKC<br>nal oscillator bl<br>nal oscillator bl<br>rnal RC oscillator<br>rnal RC oscillator<br>coscillator (high<br>oscillator (medi<br>oscillator (high | tor, CLKOUT f<br>tor, CLKOUT f<br>power, ≤500 k<br>OUT function o<br>um power, 50<br>OUT function o<br>ock, CLKOUT<br>ock<br>tor<br>tor, CLKOUT f<br>power, >16 M<br>OUT function o<br>um power, 4 I | unction on RA<br>Hz)<br>n OSC2 (low j<br>0 kHz-16 MHz<br>n OSC2 (med<br>function on OS<br>unction on OS<br>Hz)<br>n OSC2 (high<br>MHz-16 MHz) | 6<br>power, <b>≤500 kH</b><br>:)<br>ium power, 500<br>SC2 | ) kHz-16 MHz)  |       |  |  |  |  |

| Noto 1     | 0000 = LP o                                                                                                                                                                                       |                                                                                                                                                                                         |                                                                                                                                                                                                      |                                                                                                                                               | nd ECMEN hit :                                            | a cat than the |       |  |  |  |  |

| Note 1:    | When FOSC<3:0>                                                                                                                                                                                    |                                                                                                                                                                                         |                                                                                                                                                                                                      |                                                                                                                                               | NO FOMEN DIT I                                            |                |       |  |  |  |  |

### should also be set to prevent a false failed clock indication and to enable automatic clock switch over from the internal oscillator block to the external oscillator when the OST times out.

#### REGISTER 24-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH

| R/C-1   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-------|-----|-----|-----|-----|-----|-------|

| CPD     | CPB   | —   | —   | —   | _   | _   | —     |

| bit 7   |       |     |     |     |     |     | bit 0 |

|         |       |     |     |     |     |     |       |

| Legend: |       |     |     |     |     |     |       |

| R = Readable bit                       | U = Unimplemented bit, read as '0' |

|----------------------------------------|------------------------------------|

| -n = Value when device is unprogrammed | C = Clearable only bit             |

| bit 7   | CPD: Data EEPROM Code Protection bit |

|---------|--------------------------------------|

|         | 1 = Data EEPROM not code-protected   |

|         | 0 = Data EEPROM code-protected       |

| bit 6   | CPB: Boot Block Code Protection bit  |

|         | 1 = Boot Block not code-protected    |

|         | 0 = Boot Block code-protected        |

| bit 5-0 | Unimplemented: Read as '0'           |

#### REGISTER 24-8: CONFIG6L: CONFIGURATION REGISTER 6 LOW

| U-0   | U-0 | U-0 | U-0 | R/C-1               | R/C-1               | R/C-1 | R/C-1 |

|-------|-----|-----|-----|---------------------|---------------------|-------|-------|

| —     | —   | —   | —   | WRT3 <sup>(1)</sup> | WRT2 <sup>(1)</sup> | WRT1  | WRT0  |

| bit 7 |     |     |     |                     |                     |       | bit 0 |

| Legend:                                |                                    |

|----------------------------------------|------------------------------------|

| R = Readable bit                       | U = Unimplemented bit, read as '0' |

| -n = Value when device is unprogrammed | C = Clearable only bit             |

| bit 7-4     | Unimplemented: Read as '0'                                                               |

|-------------|------------------------------------------------------------------------------------------|

| bit 3       | WRT3: Write Protection bit <sup>(1)</sup>                                                |

|             | 1 = Block 3 not write-protected<br>0 = Block 3 write-protected                           |

| bit 2       | WRT2: Write Protection bit <sup>(1)</sup>                                                |

|             | <ul> <li>1 = Block 2 not write-protected</li> <li>0 = Block 2 write-protected</li> </ul> |

| <b>L</b> :4 |                                                                                          |

| bit 1       | WRT1: Write Protection bit<br>1 = Block 1 not write-protected                            |

|             | 0 = Block 1 write-protected                                                              |

| bit 0       | WRT0: Write Protection bit                                                               |

|             | 1 = Block 0 not write-protected<br>0 = Block 0 write-protected                           |

|             |                                                                                          |

Note 1: Available on PIC18(L)FX5K22 and PIC18(L)FX6K22 devices.

| CPFSGT Compare f with W, skip if f > W |                 |                                      |                  |  |  |  |  |  |  |

|----------------------------------------|-----------------|--------------------------------------|------------------|--|--|--|--|--|--|

| Syntax:                                | CPFSGT          | f {,a}                               |                  |  |  |  |  |  |  |

| Operands:                              | 0 ≤ f ≤ 255     | 0-0                                  |                  |  |  |  |  |  |  |

| opolalido.                             | a ∈ [0,1]       |                                      |                  |  |  |  |  |  |  |

| Operation:                             | (f) - (W),      |                                      |                  |  |  |  |  |  |  |

|                                        | skip if (f) > ( | (W)                                  |                  |  |  |  |  |  |  |

|                                        | (unsigned c     | omparison)                           |                  |  |  |  |  |  |  |

| Status Affected:                       | None            |                                      |                  |  |  |  |  |  |  |

| Encoding:                              | 0110            | 0110 010a ffff ffff                  |                  |  |  |  |  |  |  |

| Description:                           | Compares t      | Compares the contents of data memory |                  |  |  |  |  |  |  |

|                                        |                 | o the contents                       |                  |  |  |  |  |  |  |

|                                        |                 | an unsigned s                        |                  |  |  |  |  |  |  |

|                                        |                 | nts of 'f' are gre                   |                  |  |  |  |  |  |  |

|                                        |                 | WREG, then t<br>s discarded ar       |                  |  |  |  |  |  |  |

|                                        |                 | s discarded ar<br>stead, making      |                  |  |  |  |  |  |  |

|                                        | 2-cycle inst    |                                      | uno u            |  |  |  |  |  |  |

|                                        |                 | he Access Bar                        | nk is selected.  |  |  |  |  |  |  |

|                                        | ,               | ne BSR is used                       | d to select the  |  |  |  |  |  |  |

|                                        | GPR bank.       |                                      | d to star others |  |  |  |  |  |  |

|                                        |                 | nd the extende<br>ed, this instruc   |                  |  |  |  |  |  |  |

|                                        |                 | Literal Offset A                     | •                |  |  |  |  |  |  |

|                                        |                 | ever f ≤ 95 (5F                      | 0                |  |  |  |  |  |  |

|                                        |                 | .2.3 "Byte-Ori                       |                  |  |  |  |  |  |  |

|                                        |                 | d Instruction                        |                  |  |  |  |  |  |  |

|                                        |                 | et Mode" for                         | details.         |  |  |  |  |  |  |

| Words:                                 | 1               |                                      |                  |  |  |  |  |  |  |

| Cycles:                                | 1(2)            |                                      |                  |  |  |  |  |  |  |

|                                        | •               | cles if skip and<br>2-word instrue   |                  |  |  |  |  |  |  |

|                                        | by a            |                                      |                  |  |  |  |  |  |  |

| Q Cycle Activity:                      | 02              | 03                                   | 04               |  |  |  |  |  |  |

| Q1<br>Decode                           | Q2<br>Read      | Q3<br>Process                        | Q4<br>No         |  |  |  |  |  |  |

| Decoue                                 | register 'f'    | Data                                 | operation        |  |  |  |  |  |  |

| If skip:                               | . egietei i     | 2444                                 | oporation        |  |  |  |  |  |  |

| Q1                                     | Q2              | Q3                                   | Q4               |  |  |  |  |  |  |

| No                                     | No              | No                                   | No               |  |  |  |  |  |  |

| operation                              | operation       | operation operation                  |                  |  |  |  |  |  |  |

| If skip and followe                    |                 |                                      |                  |  |  |  |  |  |  |

| Q1                                     | Q2              | Q3                                   | Q4               |  |  |  |  |  |  |

| No                                     | No              | No                                   | No               |  |  |  |  |  |  |

| operation<br>No                        | operation<br>No | operation<br>No                      | operation<br>No  |  |  |  |  |  |  |

| operation                              | operation       | operation                            | operation        |  |  |  |  |  |  |

| oporation                              | oporation       | oporation                            | oporation        |  |  |  |  |  |  |

| Example:                               | HERE            | CPFSGT RE                            | G, 0             |  |  |  |  |  |  |

|                                        | NGREATER        | :                                    |                  |  |  |  |  |  |  |

|                                        | GREATER         | :                                    |                  |  |  |  |  |  |  |

| Before Instruc                         | tion            |                                      |                  |  |  |  |  |  |  |

| PC                                     |                 | dress (HERE)                         | )                |  |  |  |  |  |  |

| W                                      | = ?             |                                      |                  |  |  |  |  |  |  |

| After Instruction                      |                 |                                      |                  |  |  |  |  |  |  |

| If REG                                 | > W;            |                                      | 、                |  |  |  |  |  |  |

| PC<br>If REG                           | = Ad            | dress (GREAT                         | l'ER)            |  |  |  |  |  |  |

|                                                                                | Compare                                                                                                                                                                                                                                                                                                                                                                                                           | f with W,       | skip if $f < W$ |  |  |  |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--|--|--|

| Syntax:                                                                        | CPFSLT f                                                                                                                                                                                                                                                                                                                                                                                                          | {,a}            |                 |  |  |  |

| Operands:                                                                      | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                          |                 |                 |  |  |  |

| Operation:                                                                     | (f) – (W),<br>skip if (f) < (<br>(unsigned o                                                                                                                                                                                                                                                                                                                                                                      | . ,             |                 |  |  |  |

| Status Affected:                                                               | None                                                                                                                                                                                                                                                                                                                                                                                                              | . ,             |                 |  |  |  |

| Encoding:                                                                      | 0110                                                                                                                                                                                                                                                                                                                                                                                                              | 000a f          | fff ffff        |  |  |  |

| Description:                                                                   | Compares the contents of data memory<br>location 'f' to the contents of W by<br>performing an unsigned subtraction.<br>If the contents of 'f' are less than the<br>contents of W, then the fetched<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank. |                 |                 |  |  |  |

| Words:                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                 |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followe<br>by a 2-word instruction. |                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                 |  |  |  |

| Q Cycle Activity:                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                 |  |  |  |

| Q1                                                                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                | Q3              | Q4              |  |  |  |

| Decode                                                                         | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                              | Process<br>Data | No<br>operation |  |  |  |

| If skip:                                                                       | register i                                                                                                                                                                                                                                                                                                                                                                                                        | Dala            | operation       |  |  |  |

| Q1                                                                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                | Q3              | Q4              |  |  |  |

| No                                                                             | No                                                                                                                                                                                                                                                                                                                                                                                                                | No              | No              |  |  |  |

| operation                                                                      | operation                                                                                                                                                                                                                                                                                                                                                                                                         | operation       | operation       |  |  |  |

| If skip and followed                                                           | d by 2-word in                                                                                                                                                                                                                                                                                                                                                                                                    | struction:      |                 |  |  |  |

| Q1                                                                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                | Q3              | Q4              |  |  |  |

| No                                                                             | No                                                                                                                                                                                                                                                                                                                                                                                                                | No              | No              |  |  |  |

| operation                                                                      | operation                                                                                                                                                                                                                                                                                                                                                                                                         | operation       | operation       |  |  |  |

| No                                                                             | No                                                                                                                                                                                                                                                                                                                                                                                                                | No              | No              |  |  |  |

| operation                                                                      | operation                                                                                                                                                                                                                                                                                                                                                                                                         | operation       | operation       |  |  |  |

| Example:                                                                       | HERE (<br>NLESS<br>LESS                                                                                                                                                                                                                                                                                                                                                                                           |                 | G, 1            |  |  |  |