Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

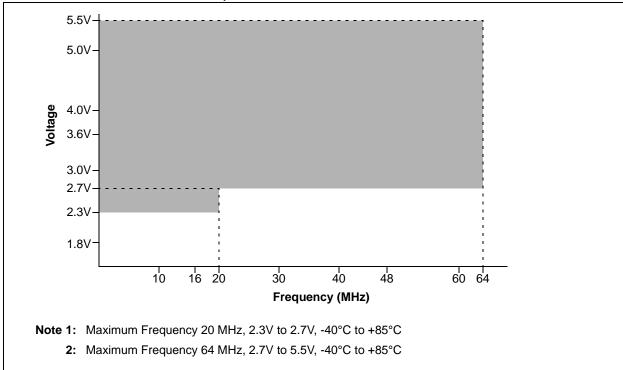

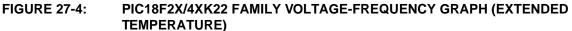

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k22-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

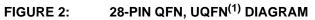

FIGURE 1: 28-PIN PDIP, SOIC, SSOP DIAGRAM

| MCLR/VPP/RE3       °1       28       RB7/PGD         RA0       2       27       RB6/PGC         RA1       3       26       RB5         RA2       4       25       RB4         RA3       5       24       RB3         RA4       6       23       RB2         RA5       7       222       RB1         Vss       8       21       RB0         RA7       9       80       VDD         RA6       10       19       Vss         RC0       11       18       RC7         RC2       13       16       RC5         RC3       14       15       RC4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| U-0          | R/W-0                                                       | R-0                                                | R-0              | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|--------------|-------------------------------------------------------------|----------------------------------------------------|------------------|------------------|------------------|-----------------|--------|--|--|--|

| —            | ADIF                                                        | RC1IF                                              | TX1IF            | SSP1IF           | CCP1IF           | TMR2IF          | TMR1IF |  |  |  |

| bit 7        |                                                             |                                                    |                  |                  |                  |                 | bit (  |  |  |  |

| 1            |                                                             |                                                    |                  |                  |                  |                 |        |  |  |  |

| Legend:      | 1- 1-14                                                     |                                                    | L.14             |                  |                  | 1 (0)           |        |  |  |  |

| R = Readab   |                                                             | W = Writable                                       |                  | -                | mented bit, read |                 |        |  |  |  |

| -n = Value a | IT POR                                                      | '1' = Bit is se                                    | t                | '0' = Bit is cle | ared             | x = Bit is unkr | lown   |  |  |  |

| bit 7        | Unimpleme                                                   | nted: Read as                                      | ʻ0'.             |                  |                  |                 |        |  |  |  |

| bit 6        | ADIF: A/D C                                                 | Converter Interre                                  | upt Flag bit     |                  |                  |                 |        |  |  |  |

|              |                                                             | conversion con                                     |                  |                  |                  |                 |        |  |  |  |

|              |                                                             | Conversion is                                      | -                |                  | n started        |                 |        |  |  |  |

| bit 5        |                                                             | SART1 Receive                                      |                  |                  |                  |                 |        |  |  |  |

|              |                                                             | SART1 receive<br>SART1 receive                     |                  |                  | red when RCR     | EG1 is read)    |        |  |  |  |

| bit 4        |                                                             | ART1 Transmit                                      | -                | -                |                  |                 |        |  |  |  |

|              |                                                             |                                                    |                  |                  | cleared when T   | XREG1 is writte | en)    |  |  |  |

|              |                                                             | SART1 transmi                                      |                  |                  |                  |                 |        |  |  |  |

| bit 3        | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit |                                                    |                  |                  |                  |                 |        |  |  |  |

|              |                                                             | nsmission/receptor to transmit/receptor            | •                | ete (must be cle | eared by softwa  | re)             |        |  |  |  |

| bit 2        | CCP1IF: CC                                                  | P1 Interrupt Fl                                    | ag bit           |                  |                  |                 |        |  |  |  |

|              |                                                             | <u>de:</u><br>register capture<br>R register captu |                  | ist be cleared b | oy software)     |                 |        |  |  |  |

|              | Compare me                                                  |                                                    |                  |                  |                  |                 |        |  |  |  |

|              |                                                             |                                                    |                  |                  | cleared by softw | are)            |        |  |  |  |

|              | <u>PWM mode</u>                                             | R register comp                                    | are match occ    | unea             |                  |                 |        |  |  |  |

|              | Unused in th                                                |                                                    |                  |                  |                  |                 |        |  |  |  |

| bit 1        | TMR2IF: TM                                                  | IR2 to PR2 Mat                                     | tch Interrupt Fl | ag bit           |                  |                 |        |  |  |  |

|              |                                                             | o PR2 match o<br>R2 to PR2 matc                    |                  | be cleared by s  | software)        |                 |        |  |  |  |

| bit 0        | TMR1IF: TM                                                  | IR1 Overflow Ir                                    | terrupt Flag b   | it               |                  |                 |        |  |  |  |

|              |                                                             | egister overflov<br>egister did not (              |                  | leared by softw  | vare)            |                 |        |  |  |  |

|              |                                                             |                                                    |                  |                  |                  |                 |        |  |  |  |

| Note 1:      | Interrupt flag I                                            | oits are set                                       | when an          |                  |                  |                 |        |  |  |  |

|              | interrupt condition                                         |                                                    |                  |                  |                  |                 |        |  |  |  |

|              | the state of its of the Global Ir                           |                                                    |                  |                  |                  |                 |        |  |  |  |

|              | GIEH of the INT                                             |                                                    | bit, Gi∟/        |                  |                  |                 |        |  |  |  |

|              |                                                             | 0                                                  |                  |                  |                  |                 |        |  |  |  |

## REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

Note: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

| R/W-0         | R/W-0                                                                                                                                  | R/W-0                                          | R/W-0           | R/W-0            | R/W-0            | R/W-0            | R/W-0       |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|------------------|------------------|------------------|-------------|--|--|--|--|

| OSCFIF        | C1IF                                                                                                                                   | C2IF                                           | EEIF            | BCL1IF           | HLVDIF           | TMR3IF           | CCP2IF      |  |  |  |  |

| bit 7         |                                                                                                                                        |                                                |                 |                  |                  |                  | bit 0       |  |  |  |  |

|               |                                                                                                                                        |                                                |                 |                  |                  |                  |             |  |  |  |  |

| Legend:       |                                                                                                                                        |                                                |                 |                  |                  |                  |             |  |  |  |  |

| R = Readable  |                                                                                                                                        | W = Writable                                   |                 | -                | mented bit, read |                  |             |  |  |  |  |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                               |                 | '0' = Bit is cle | ared             | x = Bit is unk   | nown        |  |  |  |  |

| bit 7         | OSCFIF: Os                                                                                                                             | cillator Fail Inte                             | rrupt Flag bit  |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        | oscillator failed,                             |                 | as changed to I  | HFINTOSC (mu     | ust be cleared b | y software) |  |  |  |  |

|               |                                                                                                                                        | clock operating                                |                 | 0                | × ×              |                  |             |  |  |  |  |

| bit 6         | C1IF: Compa                                                                                                                            | arator C1 Interr                               | upt Flag bit    |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        | ator C1 output                                 |                 |                  | ed by software)  |                  |             |  |  |  |  |

|               | -                                                                                                                                      | ator C1 output                                 | -               | led              |                  |                  |             |  |  |  |  |

| bit 5         | •                                                                                                                                      | arator C2 Interr                               |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        | ator C2 output                                 |                 |                  | ed by software)  |                  |             |  |  |  |  |

| bit 4         | 0 = Comparator C2 output has not changed                                                                                               |                                                |                 |                  |                  |                  |             |  |  |  |  |

| DIL 4         | <b>EEIF:</b> Data EEPROM/Flash Write Operation Interrupt Flag bit<br>1 = The write operation is complete (must be cleared by software) |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               | 0 = The write operation is not complete or has not been started                                                                        |                                                |                 |                  |                  |                  |             |  |  |  |  |

| bit 3         |                                                                                                                                        | BCL1IF: MSSP1 Bus Collision Interrupt Flag bit |                 |                  |                  |                  |             |  |  |  |  |

|               | 1 = A bus collision occurred (must be cleared by software)                                                                             |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               | 0 = No bus                                                                                                                             | collision occurre                              | ed              |                  |                  |                  |             |  |  |  |  |

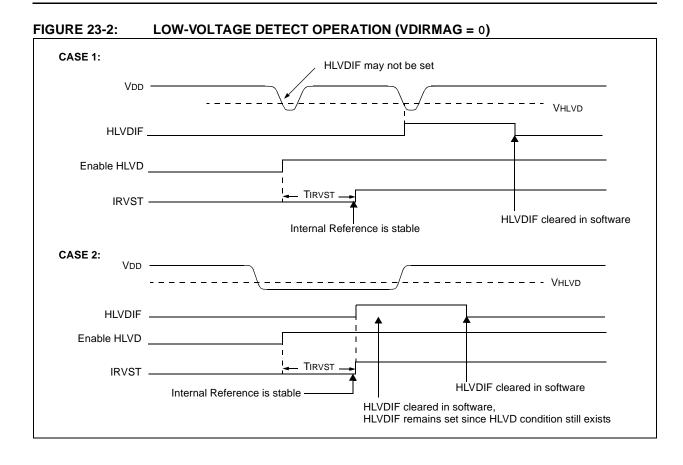

| bit 2         | HLVDIF: Low                                                                                                                            | w-Voltage Deteo                                | t Interrupt Fla | ig bit           |                  |                  |             |  |  |  |  |

|               | 1 = A low-voltage condition occurred (direction determined by the VDIRMAG bit of the                                                   |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               | HLVDCON register)<br>0 = A low-voltage condition has not occurred                                                                      |                                                |                 |                  |                  |                  |             |  |  |  |  |

| bit 1         |                                                                                                                                        | 0                                              |                 |                  |                  |                  |             |  |  |  |  |

|               | <b>TMR3IF:</b> TMR3 Overflow Interrupt Flag bit<br>1 = TMR3 register overflowed (must be cleared by software)                          |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        | egister did not c                              |                 | leared by solu   | vale)            |                  |             |  |  |  |  |

| bit 0         | CCP2IF: CCP2 Interrupt Flag bit                                                                                                        |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               | Capture mode:                                                                                                                          |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               | 1 = A TMR register capture occurred (must be cleared by software)                                                                      |                                                |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        | R register captur                              | e occurred      |                  |                  |                  |             |  |  |  |  |

|               | Compare mo                                                                                                                             |                                                | a matab agai    | mad (must be a   | leared by coffy  | (070)            |             |  |  |  |  |

|               |                                                                                                                                        | register compar<br>R register compa            |                 |                  | leared by solu   | /are)            |             |  |  |  |  |

|               | PWM mode:                                                                                                                              | •                                              |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                        |                                                |                 |                  |                  |                  |             |  |  |  |  |

## REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

## **10.7 Port Analog Control**

Most port pins are multiplexed with analog functions such as the Analog-to-Digital Converter and comparators. When these I/O pins are to be used as analog inputs it is necessary to disable the digital input buffer to avoid excessive current caused by improper biasing of the digital input. Individual control of the digital input buffers on pins which share analog functions is provided by the ANSELA, ANSELB, ANSELC, ANSELD and ANSELE registers. Setting an ANSx bit high will disable the associated digital input buffer and cause all reads of that pin to return '0' while allowing analog functions of that pin to operate correctly.

The state of the ANSx bits has no affect on digital output functions. A pin with the associated TRISx bit clear and ANSx bit set will still operate as a digital output but the input mode will be analog. This can cause unexpected behavior when performing readmodify-write operations on the affected port.

All ANSEL register bits default to '1' upon POR and BOR, disabling digital inputs for their associated port pins. All TRIS register bits default to '1' upon POR or BOR, disabling digital outputs for their associated port pins. As a result, all port pins that have an ANSEL register will default to analog inputs upon POR or BOR.

## 10.8 Port Slew Rate Control

The output slew rate of each port is programmable to select either the standard transition rate or a reduced transition rate of approximately 0.1 times the standard to minimize EMI. The reduced transition time is the default slew rate for all ports.

| 10.9 | Register | <b>Definitions</b> – | Port Control |

|------|----------|----------------------|--------------|

|------|----------|----------------------|--------------|

## REGISTER 10-1: PORTX<sup>(1)</sup>: PORTX REGISTER

| R/W-u/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Rx7     | Rx6     | Rx5     | Rx4     | Rx3     | Rx2     | Rx1     | Rx0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Logona.                    |                             |                                    |

|----------------------------|-----------------------------|------------------------------------|

| R = Readable bit           | W = Writable bit            | U = Unimplemented bit, read as '0' |

| '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown                 |

| -n/n = Value at POR and BO | R/Value at all other Resets |                                    |

bit 7-0 Rx<7:0>: PORTx I/O bit values<sup>(2)</sup>

**Note 1:** Register Description for PORTA, PORTB, PORTC and PORTD.

2: Writes to PORTx are written to corresponding LATx register. Reads from PORTx register is return of I/O pin values.

## 13.6 Register Definitions: Timer2/4/6 Control

REGISTER 13-1: TxCON: TIMER2/TIMER4/TIMER6 CONTROL REGISTER

| U-0            | R/W-0              | R/W-0                                                                       | R/W-0       | R/W-0           | R/W-0            | R/W-0           | R/W-0        |  |

|----------------|--------------------|-----------------------------------------------------------------------------|-------------|-----------------|------------------|-----------------|--------------|--|

| _              |                    | TxOUTF                                                                      | PS<3:0>     |                 | TMRxON           | TxCKP           | S<1:0>       |  |

| bit 7          |                    |                                                                             |             |                 |                  |                 | bit (        |  |

|                |                    |                                                                             |             |                 |                  |                 |              |  |

| Legend:        |                    |                                                                             |             |                 |                  |                 |              |  |

| R = Readal     | ble bit            | W = Writable                                                                | bit         | U = Unimple     | mented bit, read | as '0'          |              |  |

| u = Bit is ur  | nchanged           | x = Bit is unkr                                                             | iown        | -n/n = Value    | at POR and BOR   | /Value at all o | other Resets |  |

| '1' = Bit is s | set                | '0' = Bit is clea                                                           | ared        |                 |                  |                 |              |  |

| bit 7          | Unimplem           | nented: Read as '                                                           | <b>`</b>    |                 |                  |                 |              |  |

| bit 6-3        | -                  |                                                                             |             | ler Select bits |                  |                 |              |  |

|                |                    | TxOUTPS<3:0>: TimerX Output Postscaler Select bits<br>0000 = 1:1 Postscaler |             |                 |                  |                 |              |  |

|                | 0001 = 1:2         | 2 Postscaler                                                                |             |                 |                  |                 |              |  |

|                | 0010 = 1:3         | 3 Postscaler                                                                |             |                 |                  |                 |              |  |

|                |                    | 4 Postscaler                                                                |             |                 |                  |                 |              |  |

|                |                    | 5 Postscaler                                                                |             |                 |                  |                 |              |  |

|                |                    | 6 Postscaler                                                                |             |                 |                  |                 |              |  |

|                |                    | 7 Postscaler<br>3 Postscaler                                                |             |                 |                  |                 |              |  |

|                |                    | 9 Postscaler                                                                |             |                 |                  |                 |              |  |

|                |                    | 10 Postscaler                                                               |             |                 |                  |                 |              |  |

|                |                    | 11 Postscaler                                                               |             |                 |                  |                 |              |  |

|                | 1011 <b>= 1</b> :1 | 12 Postscaler                                                               |             |                 |                  |                 |              |  |

|                | 1100 <b>= 1</b> :  | 13 Postscaler                                                               |             |                 |                  |                 |              |  |

|                |                    | 14 Postscaler                                                               |             |                 |                  |                 |              |  |

|                |                    | 15 Postscaler                                                               |             |                 |                  |                 |              |  |

|                | 1111 <b>= 1</b> :1 | 16 Postscaler                                                               |             |                 |                  |                 |              |  |

| bit 2          | TMRxON:            | TimerX On bit                                                               |             |                 |                  |                 |              |  |

|                | 1 = TimerX is on   |                                                                             |             |                 |                  |                 |              |  |

|                | 0 = Timer          | X is off                                                                    |             |                 |                  |                 |              |  |

| bit 1-0        | TxCKPS<            | 1:0>: Timer2-type                                                           | Clock Presc | ale Select bits |                  |                 |              |  |

|                | 00 = Preso         | caler is 1                                                                  |             |                 |                  |                 |              |  |

|                | 01 = Preso         | caler is 4                                                                  |             |                 |                  |                 |              |  |

|                | 1x = Presc         | polor in 16                                                                 |             |                 |                  |                 |              |  |

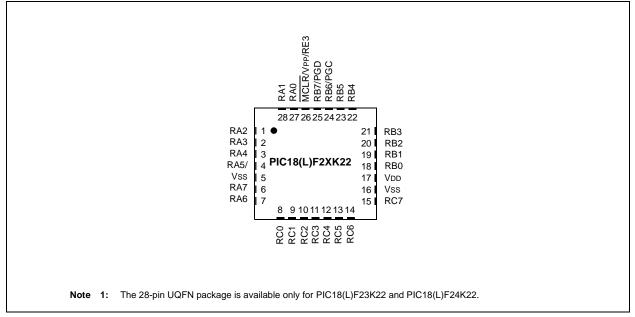

## 14.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 14-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 14-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 14-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

### FIGURE 14-10: EXAMPLE OF FULL-BRIDGE APPLICATION

## 16.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- · Programmable clock and data polarity

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

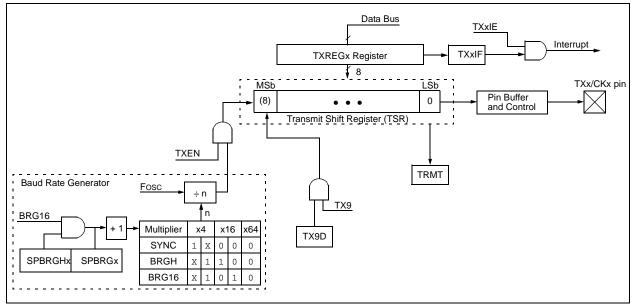

Block diagrams of the EUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

## FIGURE 16-1: EUSART TRANSMIT BLOCK DIAGRAM

- 16.1.2.9 Asynchronous Reception Setup:

- Initialize the SPBRGHx:SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- 3. Enable the serial port by setting the SPEN bit and the RXx/DTx pin TRIS bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCxIE interrupt enable bit and set the GIE/GIEH and PEIE/GIEL bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Set the DTRXP if inverted receive polarity is desired.

- 7. Enable reception by setting the CREN bit.

- 8. The RCxIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCxIE interrupt enable bit was also set.

- 9. Read the RCSTAx register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREGx register.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 16.1.2.10 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGHx, SPBRGx register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 16.4 "EUSART Baud Rate Generator (BRG)").

- 2. Set the RXx/DTx and TXx/CKx TRIS controls to '1'.

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCxIE interrupt enable bit and set the GIE/GIEH and PEIE/GIEL bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Set the DTRXP if inverted receive polarity is desired.

- 8. Enable reception by setting the CREN bit.

- The RCxIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCxIE interrupt enable bit was also set.

- 10. Read the RCSTAx register to get the error flags. The ninth data bit will always be set.

- 11. Get the received eight Least Significant data bits from the receive buffer by reading the RCREGx register. Software determines if this is the device's address.

- 12. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 13. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

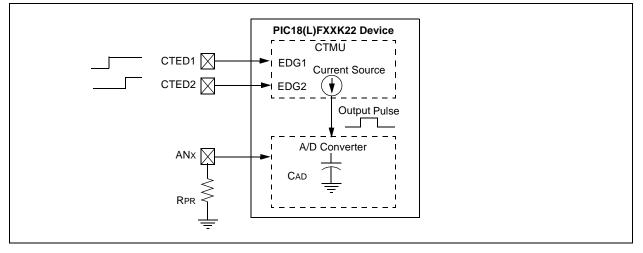

## 19.5 Measuring Time with the CTMU Module

Time can be precisely measured after the ratio (C/I) is measured from the current and capacitance calibration step by following these steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Set EDG2STAT.

- 4. Perform an A/D conversion.

- 5. Calculate the time between edges as T = (C/I) \* V, where *I* is calculated in the current calibration step (Section 19.3.1 "Current Source Calibration"), *C* is calculated in the capacitance calibration step (Section 19.3.2 "Capacitance Calibration") and *V* is measured by performing the A/D conversion.

It is assumed that the time measured is small enough that the capacitance, *C*OFFSET, provides a valid voltage to the A/D Converter. For the smallest time measurement, always set the A/D Channel Select register (AD1CHS) to an unused A/D channel; the corresponding pin for which is not connected to any circuit board trace. This minimizes added stray capacitance, keeping the total circuit capacitance close to that of the A/D Converter itself (4-5 pF). To measure longer time intervals, an external capacitor may be connected to an A/D channel and this channel selected when making a time measurement.

## FIGURE 19-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

| R/W-0        | R/W-0                                               | R/W-0                                                                                                     | R/W-0                                        | R/W-0                             | R/W-0           | R/W-0           | R/W-0  |

|--------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------|-----------------|-----------------|--------|

|              |                                                     | ITRIM                                                                                                     | <5:0>                                        |                                   |                 | IRNG            | i<1:0> |

| bit 7        |                                                     |                                                                                                           |                                              |                                   |                 |                 | bit (  |

| Legend:      |                                                     |                                                                                                           |                                              |                                   |                 |                 |        |

| R = Readal   | ble bit                                             | W = Writable I                                                                                            | bit                                          | U = Unimplen                      | nented bit, rea | d as '0'        |        |

| -n = Value a | at POR                                              | '1' = Bit is set                                                                                          |                                              | '0' = Bit is clea                 | ared            | x = Bit is unkr | nown   |

| bit 7-2      | 011111 = M<br>011110                                | Current Source Maximum positive Minimum positive Nominal current o Minimum negative                       | change from<br>change from<br>utput specifie | nominal current<br>d by IRNG<1:0> |                 |                 |        |

| bit 1-0      | IRNG<1:0><br>11 = 100 ×<br>10 = 10 × E<br>01 = Base | Maximum negative<br>Current Source<br>Base current<br>Base current<br>current level<br>nt source disabled | Range Selec                                  |                                   |                 |                 |        |

### REGISTER 19-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

| Name     | Bit 7      | Bit 6  | Bit 5    | Bit 4   | Bit 3  | Bit 2    | Bit 1    | Bit 0     | Reset<br>Values<br>on Page |

|----------|------------|--------|----------|---------|--------|----------|----------|-----------|----------------------------|

| CTMUCONH | CTMUEN     | _      | CTMUSIDL | TGEN    | EDGEN  | EDGSEQEN | IDISSEN  | CTTRIG    | 323                        |

| CTMUCONL | EDG2POL    | EDG2SE | L<1:0>   | EDG1POL | EDG1S  | EL<1:0>  | EDG2STAT | EDG1STAT  | 324                        |

| CTMUICON | ITRIM<5:0> |        |          |         |        |          |          | IRNG<1:0> |                            |

| IPR3     | SSP2IP     | BCL2IP | RC2IP    | TX2IP   | CTMUIP | TMR5GIP  | TMR3GIP  | TMR1GIP   | 123                        |

| PIE3     | SSP2IE     | BCL2IE | RC2IE    | TX2IE   | CTMUIE | TMR5GIE  | TMR3GIE  | TMR1GIE   | 119                        |

| PIR3     | SSP2IF     | BCL2IF | RC2IF    | TX2IF   | CTMUIF | TMR5GIF  | TMR3GIF  | TMR1GIF   | 114                        |

| PMD2     | —          |        | —        | -       | CTMUMD | CMP2MD   | CMP1MD   | ADCMD     | 54                         |

**Legend:** — = unimplemented, read as '0'. Shaded bits are not used during CTMU operation.

| R/C-1                                                                                           | R/C-1                                                                                                                                                                    | R-1                 | U-0 | U-0           | U-0              | U-0      | U-0   |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------|------------------|----------|-------|--|--|

| WRTD                                                                                            | WRTB                                                                                                                                                                     | WRTC <sup>(1)</sup> | —   | —             | —                | —        | —     |  |  |

| bit 7                                                                                           |                                                                                                                                                                          |                     |     |               |                  |          | bit 0 |  |  |

|                                                                                                 |                                                                                                                                                                          |                     |     |               |                  |          |       |  |  |

| Legend:                                                                                         |                                                                                                                                                                          |                     |     |               |                  |          |       |  |  |

| R = Readable                                                                                    | bit                                                                                                                                                                      |                     |     | U = Unimpler  | mented bit, read | 1 as '0' |       |  |  |

| -n = Value whe                                                                                  | en device is un                                                                                                                                                          | programmed          |     | C = Clearable | e only bit       |          |       |  |  |

| bit 7                                                                                           | bit 7 WRTD: Data EEPROM Write Protection bit<br>1 = Data EEPROM not write-protected<br>0 = Data EEPROM write-protected                                                   |                     |     |               |                  |          |       |  |  |

| bit 6                                                                                           | 6 WRTB: Boot Block Write Protection bit<br>1 = Boot Block not write-protected<br>0 = Boot Block write-protected                                                          |                     |     |               |                  |          |       |  |  |

| bit 5                                                                                           | bit 5 WRTC: Configuration Register Write Protection bit <sup>(1)</sup><br>1 = Configuration registers not write-protected<br>0 = Configuration registers write-protected |                     |     |               |                  |          |       |  |  |

| bit 4-0                                                                                         | Unimplemen                                                                                                                                                               | ted: Read as '      | 0'  |               |                  |          |       |  |  |

| Note 1: This bit is read-only in normal execution mode; it can be written only in Program mode. |                                                                                                                                                                          |                     |     |               |                  |          |       |  |  |

### REGISTER 24-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH

## **REGISTER 24-10: CONFIG7L: CONFIGURATION REGISTER 7 LOW**

|       |     |     |     |                      | -                    |       |       |

|-------|-----|-----|-----|----------------------|----------------------|-------|-------|

| U-0   | U-0 | U-0 | U-0 | R/C-1                | R/C-1                | R/C-1 | R/C-1 |

| —     | —   | —   | —   | EBTR3 <sup>(1)</sup> | EBTR2 <sup>(1)</sup> | EBTR1 | EBTR0 |

| bit 7 |     |     |     |                      |                      |       | bit 0 |

| Legend:                                |                                    |

|----------------------------------------|------------------------------------|

| R = Readable bit                       | U = Unimplemented bit, read as '0' |

| -n = Value when device is unprogrammed | C = Clearable only bit             |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | EBTR3: Table Read Protection bit <sup>(1)</sup>                                                                                                                  |

|         | <ul> <li>1 = Block 3 not protected from table reads executed in other blocks</li> <li>0 = Block 3 protected from table reads executed in other blocks</li> </ul> |

| bit 2   | EBTR2: Table Read Protection bit <sup>(1)</sup>                                                                                                                  |

|         | <ul> <li>1 = Block 2 not protected from table reads executed in other blocks</li> <li>0 = Block 2 protected from table reads executed in other blocks</li> </ul> |

| bit 1   | EBTR1: Table Read Protection bit                                                                                                                                 |

|         | <ul> <li>1 = Block 1 not protected from table reads executed in other blocks</li> <li>0 = Block 1 protected from table reads executed in other blocks</li> </ul> |

| bit 0   | EBTR0: Table Read Protection bit                                                                                                                                 |

|         | <ul> <li>1 = Block 0 not protected from table reads executed in other blocks</li> <li>0 = Block 0 protected from table reads executed in other blocks</li> </ul> |

| Note 1  | Available on PIC18/LIEX5K22 and PIC18/LIEX6K22s devices                                                                                                          |

**Note 1:** Available on PIC18(L)FX5K22 and PIC18(L)FX6K22s devices.

| BTFSC                                                                                      | Bit Test Fil                                                                                                                                                                                                                                    | le, Skip if Cle                                                                                                                                                                                                                                                                                                  | ear                                                                                                                                                                                                                                       | BTFSS                                                                                   | Bit Test File                                                                                                                                                                                                                                         | e, Skip if Se                                                                                                                                                                                                                                                                      | t                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                    | BTFSC f, b                                                                                                                                                                                                                                      | {,a}                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                           | Syntax:                                                                                 | BTFSS f, b {                                                                                                                                                                                                                                          | (,a}                                                                                                                                                                                                                                                                               |                                                                                                                                                                             |

| Operands:                                                                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                           | Operands:                                                                               | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

| Operation:                                                                                 | skip if (f <b>)</b>                                                                                                                                                                                                                             | = 0                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                           | Operation:                                                                              | skip if (f <b>)</b>                                                                                                                                                                                                                                   | = 1                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

| Status Affected:                                                                           | None                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                           | Status Affected:                                                                        | None                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

| Encoding:                                                                                  | 1011                                                                                                                                                                                                                                            | bbba ff                                                                                                                                                                                                                                                                                                          | ff ffff                                                                                                                                                                                                                                   | Encoding:                                                                               | 1010                                                                                                                                                                                                                                                  | bbba fff                                                                                                                                                                                                                                                                           | f ffff                                                                                                                                                                      |

| Description:                                                                               | instruction is<br>the next instru-<br>current instru-<br>and a NOP is<br>this a 2-cycle<br>If 'a' is '0', th<br>'a' is '1', the<br>GPR bank.<br>If 'a' is '0' an<br>set is enable<br>Indexed Liter<br>mode where<br>See Section<br>Bit-Oriented | gister 'f' is '0', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>s executed inst<br>e instruction.<br>e Access Bank<br>BSR is used to<br>d the extended<br>d, this instructi<br>ral Offset Addrever f $\leq$ 95 (5FH<br><b>25.2.3 "Byte-</b><br><b>1 Instructions</b><br><b>et Mode</b> " for do | <ul> <li>'b' is '0', then<br/>during the<br/>n is discarded<br/>ead, making</li> <li>is selected. If</li> <li>select the</li> <li>l instruction<br/>on operates in<br/>essing</li> <li>D.</li> <li>Oriented and<br/>in Indexed</li> </ul> | Description:                                                                            | instruction is<br>the next instru-<br>current instru<br>and a NOP is<br>this a 2-cycle<br>If 'a' is '0', the<br>'a' is '1', the E<br>GPR bank.<br>If 'a' is '0' and<br>set is enabled<br>in Indexed Lit<br>mode wheney<br>See Section<br>Bit-Oriented | ister 'f' is '1', t<br>skipped. If bit<br>uction fetched<br>ction execution<br>executed instr-<br>instruction.<br>Access Bank<br>3SR is used to<br>the extended<br>d, this instructi-<br>eral Offset Ad<br>ver f $\leq$ 95 (5Fh<br>25.2.3 "Byte-<br>Instructions<br>t Mode" for de | b' is '1', then<br>during the<br>is discarded<br>ead, making<br>is selected. If<br>select the<br>instruction<br>on operates<br>dressing<br>).<br>Oriented and<br>in Indexed |

| Words:                                                                                     | 1                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                           | Words:                                                                                  | 1                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

| Cycles:                                                                                    | •                                                                                                                                                                                                                                               | cles if skip and<br>2-word instruc                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                           | Cycles:                                                                                 |                                                                                                                                                                                                                                                       | les if skip and<br>2-word instruc                                                                                                                                                                                                                                                  |                                                                                                                                                                             |

| Q Cycle Activity:                                                                          |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                           | Q Cycle Activity:                                                                       |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

| Q1                                                                                         | Q2                                                                                                                                                                                                                                              | Q3                                                                                                                                                                                                                                                                                                               | Q4                                                                                                                                                                                                                                        | Q1                                                                                      | Q2                                                                                                                                                                                                                                                    | Q3                                                                                                                                                                                                                                                                                 | Q4                                                                                                                                                                          |

| Decode                                                                                     | Read                                                                                                                                                                                                                                            | Process                                                                                                                                                                                                                                                                                                          | No                                                                                                                                                                                                                                        | Decode                                                                                  | Read                                                                                                                                                                                                                                                  | Process                                                                                                                                                                                                                                                                            | No                                                                                                                                                                          |

| lf ckip:                                                                                   | register 'f'                                                                                                                                                                                                                                    | Data                                                                                                                                                                                                                                                                                                             | operation                                                                                                                                                                                                                                 | lf skip:                                                                                | register 'f'                                                                                                                                                                                                                                          | Data                                                                                                                                                                                                                                                                               | operation                                                                                                                                                                   |