Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 19x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f24k22t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 5-2:       REGISTER FILE SUMMARY FOR PIC18(L)F2X/4XK22 DEVICES (CONTINUED) |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | <u>Value on</u><br>POR, BOR |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------|

| F3Ah    | ANSELC | ANSC7 | ANSC6 | ANSC5 | ANSC4 | ANSC3 | ANSC2 | _     |       | 1111 11                     |

| F39h    | ANSELB | _     | _     | ANSB5 | ANSB4 | ANSB3 | ANSB2 | ANSB1 | ANSB0 | 11 1111                     |

| F38h    | ANSELA |       | -     | ANSA5 |       | ANSA3 | ANSA2 | ANSA1 | ANSA0 | 1- 1111                     |

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: PIC18(L)F4XK22 devices only.

2: PIC18(L)F2XK22 devices only.

3: PIC18(L)F23/24K22 and PIC18(L)F43/44K22 devices only.

4: PIC18(L)F26K22 and PIC18(L)F46K22 devices only.

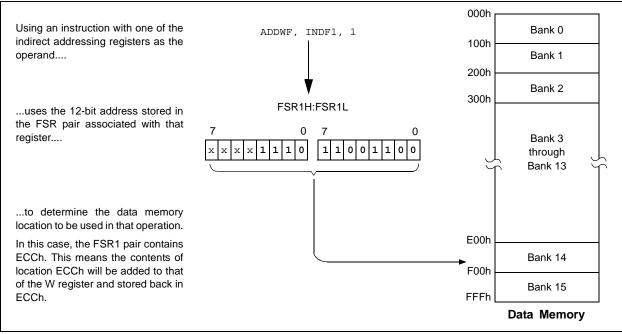

#### 5.6.3.1 FSR Registers and the INDF Operand

At the core of indirect addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. Each FSR pair holds a 12-bit value, therefore, the four upper bits of the FSRnH register are not used. The 12-bit FSR value can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because indirect addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

### 5.6.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by one, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

# FIGURE 5-10: INDIRECT ADDRESSING

#### 6.3.1 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

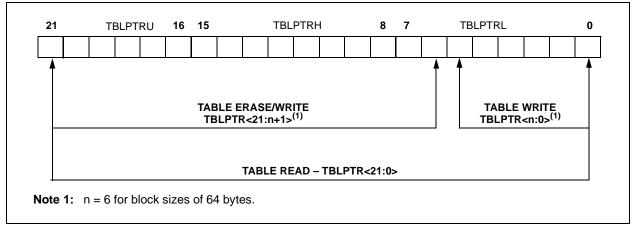

#### 6.3.2 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations on the TBLPTR affect only the low-order 21 bits.

#### 6.3.3 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory directly into the TABLAT register.

When a TBLWT is executed the byte in the TABLAT register is written, not to Flash memory but, to a holding register in preparation for a program memory write. The holding registers constitute a write block which varies depending on the device (see Table 6-1). The 3, 4, or 5 LSbs of the TBLPTRL register determine which specific address within the holding register block is written to. The MSBs of the Table Pointer have no effect during TBLWT operations.

When a program memory write is executed the entire holding register block is written to the Flash memory at the address determined by the MSbs of the TBLPTR. The 3, 4, or 5 LSBs are ignored during Flash memory writes. For more detail, see **Section 6.6** "**Writing to Flash Program Memory**".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer register (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

# TABLE 6-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 6-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

| Name                  | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |                                                         |           |              |              |               |        |        |     |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------|--------------|--------------|---------------|--------|--------|-----|--|--|

| INTCON                | GIE/GIEH                                                                                                | PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF         |           |              |              |               |        |        |     |  |  |

| EEADR                 | EEADR7                                                                                                  | EEADR7 EEADR6 EEADR5 EEADR4 EEADR3 EEADR2 EEADR1 EEADR0 |           |              |              |               |        |        |     |  |  |

| EEADRH <sup>(1)</sup> | — — — — — EEADR9 EEADR8                                                                                 |                                                         |           |              |              |               |        |        |     |  |  |

| EEDATA                | EEPROM Data Register                                                                                    |                                                         |           |              |              |               |        |        |     |  |  |

| EECON2                |                                                                                                         | EEPR                                                    | OM Contro | I Register 2 | 2 (not a phy | sical registe | er)    |        | —   |  |  |

| EECON1                | EEPGD                                                                                                   | CFGS                                                    | —         | FREE         | WRERR        | WREN          | WR     | RD     | 100 |  |  |

| IPR2                  | OSCFIP C1IP C2IP EEIP BCL1IP HLVDIP TMR3IP CCP2IP                                                       |                                                         |           |              |              |               |        |        | 122 |  |  |

| PIR2                  | OSCFIF                                                                                                  | SCFIF C1IF C2IF EEIF BCL1IF HLVDIF TMR3IF CCP2IF        |           |              |              |               |        |        |     |  |  |

| PIE2                  | OSCFIE                                                                                                  | C1IE                                                    | C2IE      | EEIE         | BCL1IE       | HLVDIE        | TMR3IE | CCP2IE | 118 |  |  |

# TABLE 7-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

Note 1: PIC18(L)F26K22 and PIC18(L)F46K22 only.

| R/W-0         | R/W-0                                                                                           | R/W-0                                                                                | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| SSP2IP        | BCL2IP                                                                                          | RC2IP                                                                                | TX2IP           | CTMUIP           | TMR5GIP          | TMR3GIP         | TMR1GIP |  |  |  |  |  |  |

| bit 7         | ·                                                                                               | ·                                                                                    |                 | •                |                  | ·               | bit (   |  |  |  |  |  |  |

|               |                                                                                                 |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

| Legend:       |                                                                                                 |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

| R = Readabl   |                                                                                                 | W = Writable                                                                         |                 | •                | mented bit, read |                 |         |  |  |  |  |  |  |

| -n = Value at | POR                                                                                             | '1' = Bit is set                                                                     |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 7         | SSP2IP: Svn                                                                                     | chronous Seria                                                                       | l Port 2 Interr | upt Priority bit |                  |                 |         |  |  |  |  |  |  |

|               | •                                                                                               | <b>SSP2IP:</b> Synchronous Serial Port 2 Interrupt Priority bit<br>1 = High priority |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | •                                                                                    |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 6         | BCL2IP: Bus                                                                                     | Collision 2 Inte                                                                     | errupt Priority | bit              |                  |                 |         |  |  |  |  |  |  |

|               | 1 = High pric                                                                                   |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | ority                                                                                |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 5         | RC2IP: EUS                                                                                      | ART2 Receive                                                                         | Interrupt Prior | ity bit          |                  |                 |         |  |  |  |  |  |  |

|               | 1 = High price                                                                                  | •                                                                                    |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | -                                                                                    |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 4         |                                                                                                 | ART2 Transmit                                                                        | Interrupt Prior | rity bit         |                  |                 |         |  |  |  |  |  |  |

|               | 1 = High pric                                                                                   | •                                                                                    |                 |                  |                  |                 |         |  |  |  |  |  |  |

| <b>h</b> :4 O | 0 = Low prio                                                                                    | •                                                                                    | -ii4  n i4      |                  |                  |                 |         |  |  |  |  |  |  |

| bit 3         | <b>CTMUIP:</b> CTMU Interrupt Priority bit<br>1 = High priority                                 |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | $1 = -1 \operatorname{Ign} \operatorname{pric}$<br>$0 = \operatorname{Low} \operatorname{pric}$ |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 2         | •                                                                                               | •                                                                                    | rupt Priority b | oit              |                  |                 |         |  |  |  |  |  |  |

|               | <b>TMR5GIP:</b> TMR5 Gate Interrupt Priority bit<br>1 = High priority                           |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | •                                                                                    |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 1         | TMR3GIP: T                                                                                      | MR3 Gate Inter                                                                       | rupt Priority b | oit              |                  |                 |         |  |  |  |  |  |  |

|               |                                                                                                 | <b>TMR3GIP:</b> TMR3 Gate Interrupt Priority bit<br>1 = High priority                |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | ority                                                                                |                 |                  |                  |                 |         |  |  |  |  |  |  |

| bit 0         | TMR1GIP: ⊤                                                                                      | MR1 Gate Inter                                                                       | rupt Priority b | oit              |                  |                 |         |  |  |  |  |  |  |

|               | 1 = High pric                                                                                   |                                                                                      |                 |                  |                  |                 |         |  |  |  |  |  |  |

|               | 0 = Low prio                                                                                    | rity (                                                                               |                 |                  |                  |                 |         |  |  |  |  |  |  |

#### REGISTER 9-16: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. All pins of the I/O ports are multiplexed with one or more alternate functions from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has five registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

- ANSEL register (analog input control)

- SLRCON register (port slew rate control)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

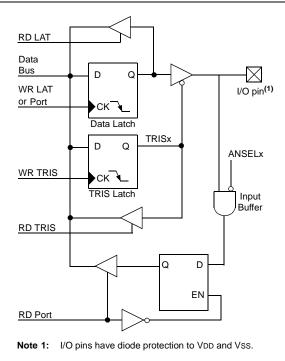

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

#### FIGURE 10-1: GENERIC I/O PORT OPERATION

# 10.1 PORTA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the PORT latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs, and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as analog is selected by setting the ANSELA<5, 3:0> bits in the ANSELA register which is the default setting after a Power-on Reset.

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CM1CON0 and CM2CON0 registers.

Note: On a Power-on Reset, RA5 and RA<3:0> are configured as analog inputs and read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the drivers of the PORTA pins, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| MOVLB | 0xF    | ; | Set BSR for banked SFRs |

|-------|--------|---|-------------------------|

| CLRF  | PORTA  | ; | Initialize PORTA by     |

|       |        | ; | clearing output         |

|       |        | ; | data latches            |

| CLRF  | LATA   | ; | Alternate method        |

|       |        | ; | to clear output         |

|       |        | ; | data latches            |

| MOVLW | E0h    | ; | Configure I/O           |

| MOVWF | ANSELA | ; | for digital inputs      |

| MOVLW | OCFh   | ; | Value used to           |

|       |        | ; | initialize data         |

|       |        | ; | direction               |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs   |

|       |        | ; | RA<5:4> as outputs      |

|       |        |   | _                       |

| TABLE 10-5.  |                         |                 |                  | •••••       | ,              |                                                                    |

|--------------|-------------------------|-----------------|------------------|-------------|----------------|--------------------------------------------------------------------|

| Pin          | Function                | TRIS<br>Setting | ANSEL<br>Setting | Pin<br>Type | Buffer<br>Type | Description                                                        |

| RB6/KBI2/PGC | RB6                     | 0               | —                | 0           | DIG            | LATB<6> data output; not affected by analog input.                 |

|              |                         | 1               | _                | I           | TTL            | PORTB<6> data input; disabled when analog input<br>enabled.        |

|              | IOC2                    | 1               | —                | I           | TTL            | Interrupt-on-change pin.                                           |

|              | TX2 <sup>(3)</sup>      | 1               | —                | 0           | DIG            | EUSART asynchronous transmit data output.                          |

|              | CK2 <sup>(3)</sup>      | 1               | —                | 0           | DIG            | EUSART synchronous serial clock output.                            |

|              |                         | 1               | _                | Ι           | ST             | EUSART synchronous serial clock input.                             |

|              | PGC                     | x               | _                | I           | ST             | In-Circuit Debugger and ICSP <sup>™</sup> programming clock input. |

| RB7/KBI3/PGD | RB7                     | 0               | —                | 0           | DIG            | LATB<7> data output; not affected by analog input.                 |

|              |                         | 1               | _                | Ι           | TTL            | PORTB<7> data input; disabled when analog input<br>enabled.        |

|              | IOC3                    | 1               | —                | I           | TTL            | Interrupt-on-change pin.                                           |

|              | RX2 <sup>(2), (3)</sup> | 1               | —                | I           | ST             | EUSART asynchronous receive data input.                            |

|              | DT2 <sup>(2), (3)</sup> | 1               | —                | 0           | DIG            | EUSART synchronous serial data output.                             |

|              |                         | 1               | —                | Ι           | ST             | EUSART synchronous serial data input.                              |

|              | PGD                     | x               |                  | 0           | DIG            | In-Circuit Debugger and ICSP <sup>™</sup> programming data output. |

|              |                         | x               | —                | Ι           | ST             | In-Circuit Debugger and ICSP <sup>™</sup> programming data input.  |

TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

**Legend:** AN = Analog input or output; TTL = TTL compatible input; HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;  $I^2C$  = Schmitt Trigger input with  $I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

#### TABLE 10-15: REGISTERS ASSOCIATED WITH PORTE

| Name                  | Bit 7 | Bit 6   | Bit 5   | Bit 4               | Bit 3               | Bit 2                 | Bit 1                 | Bit 0                 | Reset<br>Values<br>on page |

|-----------------------|-------|---------|---------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|----------------------------|

| ANSELE <sup>(1)</sup> |       | —       |         | —                   |                     | ANSE2                 | ANSE1                 | ANSE0                 | 151                        |

| INTCON2               | RBPU  | INTEDG0 | INTEDG1 | INTEDG2             |                     | TMR0IP                |                       | RBIP                  | 110                        |

| LATE <sup>(1)</sup>   | _     | —       | _       | —                   | _                   | LATE2                 | LATE1                 | LATE0                 | 152                        |

| PORTE                 | _     | _       | _       | —                   | RE3                 | RE2 <sup>(1)</sup>    | RE1 <sup>(1)</sup>    | RE0 <sup>(1)</sup>    | 149                        |

| SLRCON                | —     | —       | —       | SLRE <sup>(1)</sup> | SLRD <sup>(1)</sup> | SLRC                  | SLRB                  | SLRA                  | 153                        |

| TRISE                 | WPUE3 | _       | _       | _                   | _                   | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 151                        |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for PORTE.

**Note 1:** Available on PIC18(L)F4XK22 devices.

#### TABLE 10-16: CONFIGURATION REGISTERS ASSOCIATED WITH PORTE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2              | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|-------|-------|-------|-------|--------|--------------------|--------|--------|----------------------------|

| CONFIG3H | MCLRE |       | P2BMX | T3CMX | HFOFST | CCP3MX             | PBADEN | CCP2MX | 348                        |

| CONFIG4L | DEBUG | XINST | _     | _     | _      | LVP <sup>(1)</sup> | _      | STRVEN | 349                        |

**Legend:** — = unimplemented locations, read as '0'. Shaded bits are not used for Interrupts.

Note 1: Can only be changed when in high voltage programming mode.

# 12.13 Register Definitions: Timer1/3/5 Control

### REGISTER 12-1: TXCON: TIMER1/3/5 CONTROL REGISTER

| R/W-0/u                           | R/W-0/u                                                                                                                           | R/W-0/u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0/u                                                             | R/W-0/u                                         | R/W-0/u                         | R/W-0/0            | R/W-0/u      |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------|---------------------------------|--------------------|--------------|

| TMRx                              | CS<1:0>                                                                                                                           | TxCKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S<1:0>                                                              | TxSOSCEN                                        | TxSYNC                          | TxRD16             | TMRxON       |

| bit 7                             |                                                                                                                                   | ÷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     | · · · ·                                         |                                 |                    | bit 0        |

|                                   |                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

| Legend:                           | a hit                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - i+                                                                |                                                 | antad hit raad                  |                    |              |

| R = Readabl<br>u = Bit is unc     |                                                                                                                                   | W = Writable<br>x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 | ented bit, read<br>t POR and BO |                    | othar Basata |

| u = Bit is und<br>(1' = Bit is se | -                                                                                                                                 | x = Bit is unknown is clear the second sec | • • • • •                                                           |                                                 | I FOR and bO                    | R/ Value at all    |              |

| 1 - Dit 13 36                     | ι                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

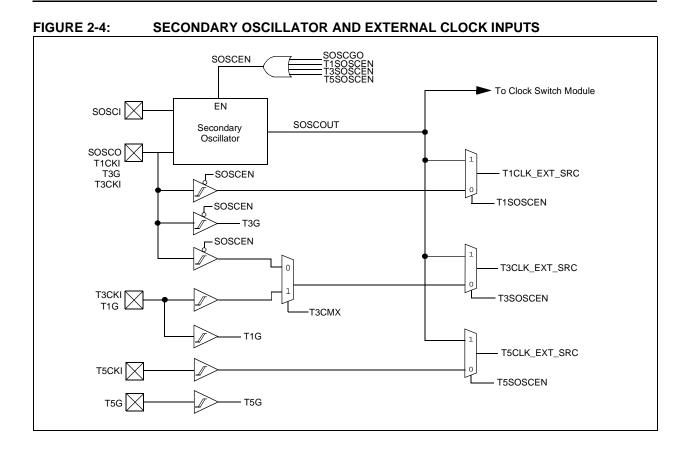

| bit 7-6                           | TMRxCS<1:                                                                                                                         | <b>0&gt;:</b> Timer1/3/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Clock Source                                                        | Select bits                                     |                                 |                    |              |

| bit 5-4                           | 10 = Timer1/2<br><u>If TxSO</u><br>Externa<br><u>If TxSO</u><br>Crystal<br>01 = Timer1/2<br>00 = Timer1/2<br><b>TxCKPS&lt;1:(</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CKI pin (on the<br>SCI/SOSCO<br>e is system clo<br>e is instruction | e rising edge)<br>pins<br>ock (Fosc)            | ts                              |                    |              |

|                                   | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres<br>00 = 1:1 Pres                                                                  | scale value<br>scale value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |                                                 |                                 |                    |              |

| bit 3                             | TxSOSCEN:                                                                                                                         | Secondary Os                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | cillator Enable                                                     | Control bit                                     |                                 |                    |              |

|                                   |                                                                                                                                   | ed Secondary of<br>ed Secondary of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                 |                                 |                    |              |

| bit 2                             | TMRxCS<1:0                                                                                                                        | 0 > = 1X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     | Synchronization                                 | n Control bit                   |                    |              |

|                                   |                                                                                                                                   | synchronize exte<br>nize external clo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     | ut<br>system clock (F                           | OSC)                            |                    |              |

|                                   | <u>TMRxCS&lt;1:(</u><br>This bit is ign                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 uses the int                                                      | ernal clock whe                                 | n TMRxCS<1:(                    | <b>)&gt; =</b> 1X. |              |

| bit 1                             | 1 = Enables                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rite of Timer1/                                                     | bit<br>'3/5 in one 16-bi<br>'3/5 in two 8-bit ( | •                               |                    |              |

| bit 0                             | 1 = Enables<br>0 = Stops Ti                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |                                                 |                                 |                    |              |

| Name                 | Bit 7    | Bit 6       | Bit 5             | Bit 4      | Bit 3             | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|----------|-------------|-------------------|------------|-------------------|-----------------------|-----------------------|-----------------------|---------------------|

| CCP1CON              | P1M-     | P1M<1:0> D0 |                   |            | B<1:0> CCP1M<3:0> |                       |                       |                       | 198                 |

| CCP2CON              | P2M-     | <1:0>       | DC2B<1:0>         |            |                   | 198                   |                       |                       |                     |

| CCP3CON              | P3M-     | <1:0>       | DC3B              | DC3B<1:0>  |                   |                       | 3:0>                  |                       | 198                 |

| CCP4CON              | —        | — DC4B<1:0> |                   |            |                   | 198                   |                       |                       |                     |

| CCP5CON              | —        | —           | DC5B              | <1:0>      |                   | CCP5M<                | 3:0>                  |                       | 198                 |

| CCPTMRS0             | C3TSE    | L<1:0>      | —                 | C2TS       | SEL<1:0>          | —                     | C1TSE                 | L<1:0>                | 201                 |

| CCPTMRS1             | —        | —           | _                 | —          | C5TSEL            | _<1:0>                | C4TSE                 | L<1:0>                | 201                 |

| INTCON               | GIE/GIEH | PEIE/GIEL   | TMR0IE            | INTOIE     | RBIE              | TMR0IF                | INTOIF                | RBIF                  | 109                 |

| IPR1                 | —        | ADIP        | RC1IP             | TX1IP      | SSP1IP            | CCP1IP                | TMR2IP                | TMR1IP                | 121                 |

| IPR2                 | OSCFIP   | C1IP        | C2IP              | EEIP       | BCL1IP            | HLVDIP                | TMR3IP                | CCP2IP                | 122                 |