Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k22-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Nu        | umber        |                                | <b>D</b> '  | Duffer         |                                                     |

|---------------|--------------|--------------------------------|-------------|----------------|-----------------------------------------------------|

| PDIP,<br>SOIC | QFN,<br>UQFN | Pin Name                       | Pin<br>Type | Buffer<br>Type | Description                                         |

| 25            | 22           | RB4/IOC0/P1D/T5G/AN11          |             |                |                                                     |

|               |              | RB4                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC0                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | P1D                            | 0           | CMOS           | Enhanced CCP1 PWM output.                           |

|               |              | T5G                            | I           | ST             | Timer5 external clock gate input.                   |

|               |              | AN11                           | I           | Analog         | Analog input 11.                                    |

| 26            | 23           | RB5/IOC1/P2B/P3A/CCP3/T3CKI/T1 | G/AN13      | 3              |                                                     |

|               |              | RB5                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC1                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | P2B <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP2 PWM output.                           |

|               |              | P3A <sup>(1)</sup>             | 0           | CMOS           | Enhanced CCP3 PWM output.                           |

|               |              | CCP3 <sup>(1)</sup>            | I/O         | ST             | Capture 3 input/Compare 3 output/PWM 3 output.      |

|               |              | ТЗСКІ <sup>(2)</sup>           | I           | ST             | Timer3 clock input.                                 |

|               |              | T1G                            | I           | ST             | Timer1 external clock gate input.                   |

|               |              | AN13                           | I           | Analog         | Analog input 13.                                    |

| 27            | 24           | RB6/IOC2/TX2/CK2/PGC           |             |                |                                                     |

|               |              | RB6                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC2                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | TX2                            | 0           | _              | EUSART asynchronous transmit.                       |

|               |              | CK2                            | I/O         | ST             | EUSART synchronous clock (see related RXx/DTx).     |

|               |              | PGC                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming clock pir |

| 28            | 25           | RB7/IOC3/RX2/DT2/PGD           |             |                |                                                     |

|               |              | RB7                            | I/O         | TTL            | Digital I/O.                                        |

|               |              | IOC3                           | I           | TTL            | Interrupt-on-change pin.                            |

|               |              | RX2                            | I           | ST             | EUSART asynchronous receive.                        |

|               |              | DT2                            | I/O         | ST             | EUSART synchronous data (see related TXx/CKx).      |

|               |              | PGD                            | I/O         | ST             | In-Circuit Debugger and ICSP™ programming data pin  |

| 11            | 8            | RC0/P2B/T3CKI/T3G/T1CKI/SOSCC  | )           |                |                                                     |

|               |              | RC0                            | I/O         | ST             | Digital I/O.                                        |

|               |              | P2B <sup>(2)</sup>             | 0           | CMOS           | Enhanced CCP1 PWM output.                           |

|               |              | ТЗСКІ <sup>(1)</sup>           | I           | ST             | Timer3 clock input.                                 |

|               |              | T3G                            | I           | ST             | Timer3 external clock gate input.                   |

|               |              | T1CKI                          | I           | ST             | Timer1 clock input.                                 |

|               |              | SOSCO                          | 0           | _              | Secondary oscillator output.                        |

| 12            | 9            | RC1/P2A/CCP2/SOSCI             | 1           | 1              |                                                     |

|               |              | RC1                            | I/O         | ST             | Digital I/O.                                        |

|               |              | P2A                            | 0           | CMOS           | Enhanced CCP2 PWM output.                           |

|               |              | CCP2 <sup>(1)</sup>            | I/O         | ST             | Capture 2 input/Compare 2 output/PWM 2 output.      |

|               |              | SOSCI                          | 1           | Analog         | Secondary oscillator input.                         |

#### TABLE 1-2: PIC18(L)F2XK22 PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; I = Input; O = Output; P = Power.

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

## 3.6 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what IDLE mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals. PIC18(L)F2X/4XK22 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with control bits in the Peripheral Module Disable (PMD) registers. These bits generically named XXXMD are located in control registers PMD0, PMD1 or PMD2.

Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, power to the control and status registers associated with the peripheral is removed. Writes to these registers have no effect and read values are invalid. Clearing a set PMD bit restores power to the associated control and status registers, thereby setting those registers to their default values.

## 3.7 Register Definitions: Peripheral Module Disable

### REGISTER 3-1: PMD0: PERIPHERAL MODULE DISABLE REGISTER 0

| R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| UART2MD | UART1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD |

| bit 7   | ·       |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | UART2MD: UART2 Peripheral Module Disable Control bit                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 6 | UART1MD: UART1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 5 | TMR6MD: Timer6 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 4 | TMR5MD: Timer5 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 3 | TMR4MD: Timer4 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 2 | TMR3MD: Timer3 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 1 | TMR2MD: Timer2 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

| bit 0 | TMR1MD: Timer1 Peripheral Module Disable Control bit                                                                                                                                               |

|       | <ul> <li>1 = Module is disabled, Clock Source is disconnected, module does not draw digital power</li> <li>0 = Module is enabled, Clock Source is connected, module draws digital power</li> </ul> |

|       |                                                                                                                                                                                                    |

| R/W-0         | R/W-0                                                                                                                                    | R/W-0                                                                                                                                  | R/W-0           | R/W-0            | R/W-0            | R/W-0            | R/W-0       |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|-------------|--|--|--|--|

| OSCFIF        | C1IF                                                                                                                                     | C2IF                                                                                                                                   | EEIF            | BCL1IF           | HLVDIF           | TMR3IF           | CCP2IF      |  |  |  |  |

| bit 7         |                                                                                                                                          |                                                                                                                                        |                 |                  |                  |                  | bit 0       |  |  |  |  |

|               |                                                                                                                                          |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| Legend:       |                                                                                                                                          |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| R = Readable  |                                                                                                                                          | W = Writable                                                                                                                           |                 | -                | mented bit, read |                  |             |  |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is set                                                                                                                       |                 | '0' = Bit is cle | ared             | x = Bit is unk   | nown        |  |  |  |  |

| bit 7         | OSCFIF: Os                                                                                                                               | cillator Fail Inte                                                                                                                     | rrupt Flag bit  |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                          | oscillator failed,                                                                                                                     |                 | as changed to I  | HFINTOSC (mu     | ust be cleared b | y software) |  |  |  |  |

|               |                                                                                                                                          | clock operating                                                                                                                        |                 | 0                | × ×              |                  |             |  |  |  |  |

| bit 6         | C1IF: Compa                                                                                                                              | arator C1 Interr                                                                                                                       | upt Flag bit    |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                          | ator C1 output                                                                                                                         |                 |                  | ed by software)  |                  |             |  |  |  |  |

|               | -                                                                                                                                        | ator C1 output                                                                                                                         | -               | led              |                  |                  |             |  |  |  |  |

| bit 5         | •                                                                                                                                        | arator C2 Interr                                                                                                                       |                 |                  |                  |                  |             |  |  |  |  |

|               | <ul> <li>1 = Comparator C2 output has changed (must be cleared by software)</li> <li>0 = Comparator C2 output has not changed</li> </ul> |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| bit 4         | -                                                                                                                                        | •                                                                                                                                      |                 |                  | a hit            |                  |             |  |  |  |  |

| DIL 4         |                                                                                                                                          | <b>EEIF:</b> Data EEPROM/Flash Write Operation Interrupt Flag bit<br>1 = The write operation is complete (must be cleared by software) |                 |                  |                  |                  |             |  |  |  |  |

|               | 0 = The write operation is not complete or has not been started                                                                          |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| bit 3         |                                                                                                                                          | SP1 Bus Collis                                                                                                                         | •               |                  |                  |                  |             |  |  |  |  |

|               | 1 = A bus collision occurred (must be cleared by software)                                                                               |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               | 0 = No bus                                                                                                                               | collision occurre                                                                                                                      | ed              |                  |                  |                  |             |  |  |  |  |

| bit 2         | HLVDIF: Low                                                                                                                              | w-Voltage Deteo                                                                                                                        | t Interrupt Fla | ig bit           |                  |                  |             |  |  |  |  |

|               | 1 = A low-voltage condition occurred (direction determined by the VDIRMAG bit of the                                                     |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               | HLVDCON register)<br>0 = A low-voltage condition has not occurred                                                                        |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| bit 1         |                                                                                                                                          | 0                                                                                                                                      |                 |                  |                  |                  |             |  |  |  |  |

|               | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                 |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               | <ul> <li>1 = TMR3 register overflowed (must be cleared by software)</li> <li>0 = TMR3 register did not overflow</li> </ul>               |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

| bit 0         |                                                                                                                                          | P2 Interrupt Fla                                                                                                                       |                 |                  |                  |                  |             |  |  |  |  |

|               | Capture mode:                                                                                                                            |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               | 1 = A TMR register capture occurred (must be cleared by software)                                                                        |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               | 0 = No TMR register capture occurred                                                                                                     |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                          | <u>Compare mode:</u><br>1 = A TMR register compare match occurred (must be cleared by software)                                        |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                          | register compar<br>R register compa                                                                                                    |                 |                  | leared by solu   | /are)            |             |  |  |  |  |

|               | PWM mode:                                                                                                                                | •                                                                                                                                      |                 |                  |                  |                  |             |  |  |  |  |

|               |                                                                                                                                          |                                                                                                                                        |                 |                  |                  |                  |             |  |  |  |  |

## REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

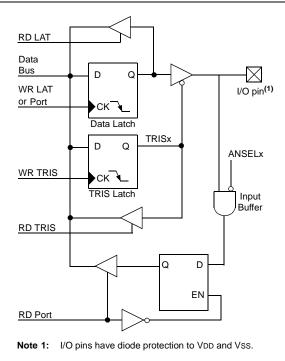

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. All pins of the I/O ports are multiplexed with one or more alternate functions from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has five registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

- ANSEL register (analog input control)

- SLRCON register (port slew rate control)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 10-1.

### FIGURE 10-1: GENERIC I/O PORT OPERATION

## 10.1 PORTA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it, will write to the PORT latch.

The Data Latch (LATA) register is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RA4/T0CKI/C1OUT pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 24.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs, and the comparator voltage reference output. The operation of pins RA<3:0> and RA5 as analog is selected by setting the ANSELA<5, 3:0> bits in the ANSELA register which is the default setting after a Power-on Reset.

Pins RA0 through RA5 may also be used as comparator inputs or outputs by setting the appropriate bits in the CM1CON0 and CM2CON0 registers.

Note: On a Power-on Reset, RA5 and RA<3:0> are configured as analog inputs and read as '0'. RA4 is configured as a digital input.

The RA4/T0CKI/C1OUT pin is a Schmitt Trigger input. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the drivers of the PORTA pins, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| MOVLB | 0xF    | ; | Set BSR for banked SFRs |

|-------|--------|---|-------------------------|

| CLRF  | PORTA  | ; | Initialize PORTA by     |

|       |        | ; | clearing output         |

|       |        | ; | data latches            |

| CLRF  | LATA   | ; | Alternate method        |

|       |        | ; | to clear output         |

|       |        | ; | data latches            |

| MOVLW | E0h    | ; | Configure I/O           |

| MOVWF | ANSELA | ; | for digital inputs      |

| MOVLW | OCFh   | ; | Value used to           |

|       |        | ; | initialize data         |

|       |        | ; | direction               |

| MOVWF | TRISA  | ; | Set RA<3:0> as inputs   |

|       |        | ; | RA<5:4> as outputs      |

|       |        |   | _                       |

### TABLE 10-8: PORTC I/O SUMMARY

| Pin Name                          | Function             | TRIS<br>Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ANSEL setting                                      | Pin<br>Type | Buffer<br>Type   | Description                                                 |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------|------------------|-------------------------------------------------------------|

| RC0/P2B/T3CKI/T3G/                | RC0                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                  | 0           | DIG              | LATC<0> data output; not affected by analog input.          |

| T1CKI/SOSCO                       |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                  | I           | ST               | PORTC<0> data input; disabled when analog input enabled.    |

|                                   | P2B <sup>(2)</sup>   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | 0           | DIG              | Enhanced CCP2 PWM output 2.                                 |

|                                   | T3CKI <sup>(1)</sup> | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                  | I           | ST               | Timer3 clock input.                                         |

|                                   | T3G                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | I           | ST               | Timer3 external clock gate input.                           |

|                                   | T1CKI                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | I           | ST               | Timer1 clock input.                                         |

|                                   | SOSCO                | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | 0           | XTAL             | Secondary oscillator output.                                |

|                                   |                      | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LATC<1> data output; not affected by analog input. |             |                  |                                                             |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                  | I           | ST               | PORTC<1> data input; disabled when analog input enabled.    |

|                                   | P2A                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | 0           | DIG              | Enhanced CCP2 PWM output 1.                                 |

|                                   | CCP2 <sup>(1)</sup>  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | 0           | DIG              | Compare 2 output/PWM 2 output.                              |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | I           | ST               | Capture 2 input.                                            |

|                                   | SOSCI                | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | I           | XTAL             | Secondary oscillator input.                                 |

| RC2/CTPLS/P1A/                    | RC2                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | LATC<2> data output; not affected by analog input.          |

| RC2/CTPLS/P1A/<br>CCP1/T5CKI/AN14 |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | PORTC<2> data input; disabled when analog input<br>enabled. |

|                                   | CTPLS                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | CTMU pulse generator output.                                |

|                                   | P1A                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | Enhanced CCP1 PWM output 1.                                 |

|                                   | CCP1                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | Compare 1 output/PWM 1 output.                              |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | Capture 1 input.                                            |

|                                   | T5CKI                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | Timer5 clock input.                                         |

|                                   | AN14                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                  | I           | AN               | Analog input 14.                                            |

| RC3/SCK1/SCL1/AN15                | RC3                  | Instant<br>RC0SettingSettingTypeTypeDescriptionRC00ODIGLATC<0> data output; not affected by analog inp<br>enabled.28(2)0ODIGEnhanced CCP2 PWM output 2.CKI(1)1ISTTimer3 clock input.T3G1ISTTimer3 clock input.TGKI1ISTTimer3 clock input.DXSCOxOXTALSecondary oscillator output.SRC10ODIGLATC<1> data output; not affected by analog inp<br>enabled.D1ISTPORTC<1> data output; not affected by analog inp<br>enabled.P2A0ODIGEnhanced CCP2 PWM output 1.CSC1xISTCapture 2 input.CSC1xISTCapture 2 input.CSC1xISTPORTC<2> data input; disabled when analog inp<br>enabled.TPLS00ODIGCATC<2> data output; not affected by analog inp<br>enabled.TPLS00ODIGCapture 2 input.CR2100ODIGCapture 1 input.SCH10ISTCapture 1 input.TPLS00DIGCapture 1 input.SCK110ISTPORTC<2> data input; disabled when analog inp<br>enabled.TPLA00 |                                                    |             |                  |                                                             |

| RC2/CTPLS/P1A/<br>CCP1/T5CKI/AN14 |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | PORTC<3> data input; disabled when analog input<br>enabled. |

|                                   | SCK1                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | MSSP1 SPI Clock output.                                     |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | MSSP1 SPI Clock input.                                      |

|                                   | SCL1                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | MSSP1 I <sup>2</sup> C Clock output.                        |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock input.                         |

|                                   | AN15                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                  | I           | AN               | Analog input 15.                                            |

| RC4/SDI1/SDA1/AN16                | RC4                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | LATC<4> data output; not affected by analog input.          |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | I           | ST               | PORTC<4> data input; disabled when analog input<br>enabled. |

|                                   | SDI1                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | Ι           | ST               | MSSP1 SPI data input.                                       |

|                                   | SDA1                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | 0           | DIG              | MSSP1 I <sup>2</sup> C data output.                         |

|                                   |                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                  | Ι           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C data input.                          |

|                                   | AN16                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                  | I           | AN               | Analog input 16.                                            |

**Legend:** AN = Analog input or output; TTL = TTL compatible input;  $HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; <math>I^2C = Schmitt Trigger input with I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

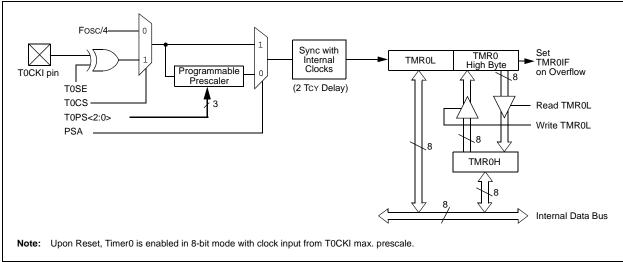

## FIGURE 11-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

## 11.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS<2:0> bits of the T0CON register which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When the prescaler is assigned, prescale values from 1:2 through 1:256 in integer power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

## 11.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

## 11.5 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit of the INTCON register. Before re-enabling the interrupt, the TMR0IF bit must be cleared by software in the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name    | Bit 7                      | Bit 6     | Bit 5   | Bit 4   | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Reset<br>Values<br>on page |

|---------|----------------------------|-----------|---------|---------|--------|--------|---------------|--------|----------------------------|

| INTCON  | GIE/GIEH                   | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 109                        |

| INTCON2 | RBPU                       | INTEDG0   | INTEDG1 | INTEDG2 | —      | TMR0IP |               | RBIP   | 110                        |

| T0CON   | TMR0ON                     | T08BIT    | TOCS    | T0SE    | PSA    |        | 154           |        |                            |

| TMR0H   | Timer0 Register, High Byte |           |         |         |        |        |               |        | —                          |

| TMR0L   | Timer0 Register, Low Byte  |           |         |         |        |        |               | —      |                            |

| TRISA   | TRISA7                     | TRISA6    | TRISA5  | TRISA4  | TRISA3 | TRISA2 | TRISA1        | TRISA0 | 151                        |

## TABLE 11-1: REGISTERS ASSOCIATED WITH TIMER0

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used by Timer0.

| Name                 | Bit 7   | Bit 6   | Bit 5           | Bit 4           | Bit 3              | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|---------|---------|-----------------|-----------------|--------------------|-----------------------|-----------------------|-----------------------|---------------------|

| IPR2                 | OSCFIP  | C1IP    | C2IP            | EEIP            | BCL1IP             | HLVDIP                | TMR3IP                | CCP2IP                | 122                 |

| IPR4                 | —       | —       | —               | —               | _                  | CCP5IP                | CCP4IP                | CCP3IP                | 124                 |

| PIE1                 | —       | ADIE    | RC1IE           | TX1IE           | SSP1IE             | CCP1IE                | TMR2IE                | TMR1IE                | 117                 |

| PIE2                 | OSCFIE  | C1IE    | C2IE            | EEIE            | BCL1IE             | HLVDIE                | TMR3IE                | CCP2IE                | 118                 |

| PIE4                 | —       | —       | —               | —               |                    | CCP5IE                | CCP4IE                | CCP3IE                | 120                 |

| PIR1                 | —       | ADIF    | RC1IF           | TX1IF           | SSP1IF             | CCP1IF                | TMR2IF                | TMR1IF                | 112                 |

| PIR2                 | OSCFIF  | C1IF    | C2IF            | EEIF            | BCL1IF             | HLVDIF                | TMR3IF                | CCP2IF                | 113                 |

| PIR4                 | —       | —       | —               | —               | —                  | CCP5IF                | CCP4IF                | CCP3IF                | 115                 |

| PMD0                 | UART2MD | UART1MD | TMR6MD          | TMR5MD          | TMR4MD             | TMR3MD                | TMR2MD                | TMR1MD                | 52                  |

| PMD1                 | MSSP2MD | MSSP1MD | —               | CCP5MD          | CCP4MD             | CCP3MD                | CCP2MD                | CCP1MD                | 53                  |

| T1CON                | TMR10   | CS<1:0> | T1CKPS<1:0>     |                 | T1SOSCEN           | T1SYNC                | T1RD16                | TMR10N                | 166                 |

| T1GCON               | TMR1GE  | T1GPOL  | T1GTM T1GSPM    |                 | T1GGO/DONE         | T1GVAL                | T1GSS<1:0>            |                       | 167                 |

| T3CON                | TMR30   | CS<1:0> | T3CKP           | T3CKPS<1:0>     |                    | T3SYNC                | T3RD16                | TMR3ON                | 166                 |

| T3GCON               | TMR3GE  | T3GPOL  | T3GTM           | T3GSPM          | T3GGO/DONE         | T3GVAL                | T3GSS                 | S<1:0>                | 167                 |

| T5CON                | TMR50   | CS<1:0> | T5CKP           | S<1:0>          | T5SOSCEN           | T5SYNC                | T5RD16                | TMR5ON                | 166                 |

| T5GCON               | TMR5GE  | T5GPOL  | T5GTM           | T5GSPM          | T5GGO/DONE         | T5GVAL                | T5GSS                 | S<1:0>                | 167                 |

| TMR1H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR1 R          | egister               |                       | _                   |

| TMR1L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR1    | Register              |                       |                       |                     |

| TMR3H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR3 R          | egister               |                       | _                   |

| TMR3L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR3    | Register              |                       |                       | _                   |

| TMR5H                |         | Holding | Register for th | e Most Signifi  | cant Byte of the 1 | 6-bit TMR5 R          | egister               |                       | _                   |

| TMR5L                |         |         | Least Sign      | ificant Byte of | the 16-bit TMR5    | Register              |                       |                       | _                   |

| TRISA                | TRISA7  | TRISA6  | TRISA5          | TRISA4          | TRISA3             | TRISA2                | TRISA1                | TRISA0                | 151                 |

| TRISB                | TRISB7  | TRISB6  | TRISB5          | TRISB4          | TRISB3             | TRISB2                | TRISB1                | TRISB0                | 151                 |

| TRISC                | TRISC7  | TRISC6  | TRISC5          | TRISC4          | TRISC3             | TRISC2                | TRISC1                | TRISC0                | 151                 |