Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 19x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

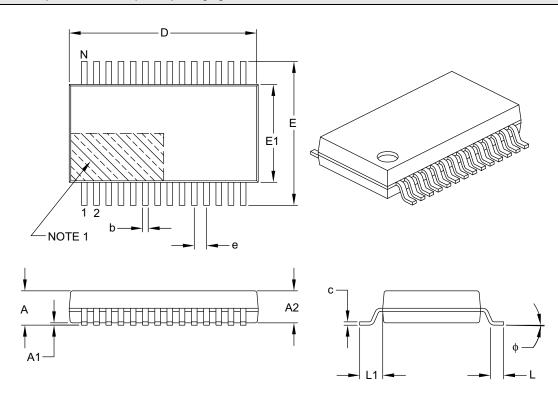

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k22-e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7.1 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a 31.25 kHz internal clock source. The LFINTOSC is not tunable, but is designed to be stable across temperature and voltage. See **Section 27.0 "Electrical Specifications"** for the LFINTOSC accuracy specifications.

The output of the LFINTOSC can be a clock source to the primary clock or the INTOSC clock (see Figure 2-1). The LFINTOSC is also the clock source for the Powerup Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

# 2.7.2 FREQUENCY SELECT BITS (IRCF)

The HFINTOSC (16 MHz) and MFINTOSC (500 MHz) outputs connect to a divide circuit that provides frequencies of 16 MHz to 31.25 kHz. These divide circuit frequencies, along with the 31.25 kHz LFINTOSC output, are multiplexed to provide a single INTOSC clock output (see Figure 2-1). The IRCF<2:0> bits of the OSCCON register, the MFIOSEL bit of the OSCCON2 register and the INTSRC bit of the OSCTUNE register, select the output frequency of the internal oscillators. One of eight frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz (default after Reset)

- 500 kHz (MFINTOSC or HFINTOSC)

- 250 kHz (MFINTOSC or HFINTOSC)

- 31 kHz (LFINTOSC, MFINTOSC or HFINTOSC)

# 2.7.3 INTOSC FREQUENCY DRIFT

The factory calibrates the internal oscillator block outputs (HFINTOSC/MFINTOSC) for 16 MHz/500 kHz. However, this frequency may drift as VDD or temperature changes. It is possible to adjust the HFINTOSC/MFINTOSC frequency by modifying the value of the TUN<5:0> bits in the OSCTUNE register. This has no effect on the LFINTOSC clock source frequency.

Tuning the HFINTOSC/MFINTOSC source requires knowing when to make the adjustment, in which direction it should be made and, in some cases, how large a change is needed. Three possible compensation techniques are discussed in the following sections. However, other techniques may be used.

# 2.7.3.1 Compensating with the EUSART

An adjustment may be required when the EUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

### 2.7.3.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

# 2.7.3.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free running Timer1, Timer3 or Timer5 clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

# 4.7 Reset State of Registers

Some registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. All other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ , are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used by software to determine the nature of the Reset.

Table 5-2 describes the Reset states for all of the Special Function Registers. The table identifies differences between Power-On Reset (POR)/Brown-Out Reset (BOR) and all other Resets, (i.e., Master Clear, WDT Resets, STKFUL, STKUNF, etc.). Additionally, the table identifies register bits that are changed when the device receives a wake-up from WDT or other interrupts.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION |

|------------|------------------------------------------------------------------|

|            | FOR RCON REGISTER                                                |

| Condition                                                   | Program               | RCON Register |    |    |    |     |     | STKPTR Register |        |  |

|-------------------------------------------------------------|-----------------------|---------------|----|----|----|-----|-----|-----------------|--------|--|

| Condition                                                   | Counter               | SBOREN        | RI | то | PD | POR | BOR | STKFUL          | STKUNF |  |

| Power-on Reset                                              | 0000h                 | 1             | 1  | 1  | 1  | 0   | 0   | 0               | 0      |  |

| RESET Instruction                                           | 0000h                 | u <b>(2)</b>  | 0  | u  | u  | u   | u   | u               | u      |  |

| Brown-out Reset                                             | 0000h                 | u <b>(2)</b>  | 1  | 1  | 1  | u   | 0   | u               | u      |  |

| MCLR during Power-Managed<br>Run Modes                      | 0000h                 | ս <b>(2)</b>  | u  | 1  | u  | u   | u   | u               | u      |  |

| MCLR during Power-Managed<br>Idle Modes and Sleep Mode      | 0000h                 | ս <b>(2)</b>  | u  | 1  | 0  | u   | u   | u               | u      |  |

| WDT Time-out during Full Power<br>or Power-Managed Run Mode | 0000h                 | u <b>(2)</b>  | u  | 0  | u  | u   | u   | u               | u      |  |

| MCLR during Full Power<br>Execution                         | 0000h                 | u <b>(2)</b>  | u  | u  | u  | u   | u   | u               | u      |  |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u <b>(2)</b>  | u  | u  | u  | u   | u   | 1               | u      |  |

| Stack Underflow Reset<br>(STVREN = 1)                       | 0000h                 | u <b>(2)</b>  | u  | u  | u  | u   | u   | u               | 1      |  |

| Stack Underflow Error (not an actual Reset, STVREN = 0)     | 0000h                 | u <b>(2)</b>  | u  | u  | u  | u   | u   | u               | 1      |  |

| WDT Time-out during Power-<br>Managed Idle or Sleep Modes   | PC + 2                | u <b>(2)</b>  | u  | 0  | 0  | u   | u   | u               | u      |  |

| Interrupt Exit from Power-<br>Managed Modes                 | PC + 2 <sup>(1)</sup> | u <b>(2)</b>  | u  | u  | 0  | u   | u   | u               | u      |  |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for SBOREN and unchanged for all other Resets when software BOR is enabled (BOREN<1:0> Configuration bits = 01). Otherwise, the Reset state is '0'.

#### TABLE 4-4:REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------------|

| RCON   | IPEN   | SBOREN |       | RI    | TO    | PD    | POR   | BOR   | 56                  |

| STKPTR | STKFUL | STKUNF |       |       | 67    |       |       |       |                     |

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for Resets.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads

The POP instruction discards the current TOS by

decrementing the Stack Pointer. The previous value

pushed onto the stack then becomes the TOS value.

the current PC value onto the stack.

#### 5.1.2.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack without disturbing normal program execution is a desirable feature. The PIC18 instruction set includes two instructions. PUSH and POP. that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

5.2 **Register Definitions: Stack Pointer**

#### **REGISTER 5-1:** STKPTR: STACK POINTER REGISTER

|                       |                       |     | •     |       |             |       |       |

|-----------------------|-----------------------|-----|-------|-------|-------------|-------|-------|

| R/C-0                 | R/C-0                 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —   |       |       | STKPTR<4:0> |       |       |

| bit 7                 |                       |     |       |       |             |       | bit 0 |

| Legend:           |                  |                      |                        |

|-------------------|------------------|----------------------|------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | C = Clearable only bit |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown     |

| bit 7 | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|-------|-------------------------------------------------|

|       | 1 = Stack became full or overflowed             |

|       | 0 = Stack has not become full or overflowed     |

| bit 6 | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|       | 1 = Stack Underflow occurred                    |

|       | 0 = Stack Underflow did not occur               |

| bit 5 | Unimplemented: Read as '0'                      |

|       |                                                 |

bit 4-0 STKPTR<4:0>: Stack Pointer Location bits

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

#### Stack Full and Underflow Resets 5.2.0.1

Device Resets on Stack Overflow and Stack Underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### FAST REGISTER STACK 5.2.1

A fast register stack is provided for the Status, WREG and BSR registers, to provide a "fast return" option for interrupts. The stack for each register is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high priority interrupts are enabled, the stack registers cannot be used reliably to return from low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten. In these cases, users must save the key registers by software during a low priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt. If no interrupts are used, the fast register stack can be used to restore the Status, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL label, FAST instruction must be executed to save the Status, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

© 2010-2016 Microchip Technology Inc.

# 5.3 PIC18 Instruction Cycle

### 5.3.1 CLOCKING SCHEME

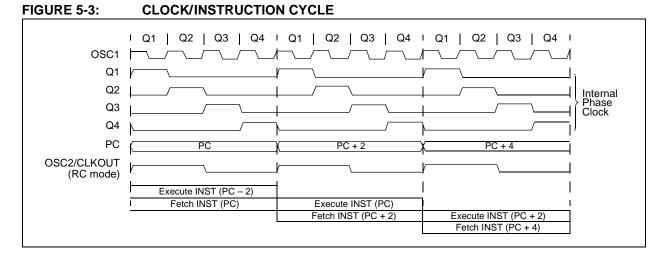

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the instruction register during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-3.

# 5.3.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

|                       | Тсү0       | TCY1      | Tcy2      | Tcy3        | TCY4          | TCY5 |  |  |  |

|-----------------------|------------|-----------|-----------|-------------|---------------|------|--|--|--|

| 1. MOVLW 55h          | Fetch 1    | Execute 1 |           |             | •             |      |  |  |  |

| 2. MOVWF PORTB        |            | Fetch 2   | Execute 2 |             |               |      |  |  |  |

| 3. BRA SUB_1          |            |           | Fetch 3   | Execute 3   |               |      |  |  |  |

| 4. BSF PORTA, BIT3    | (Forced N  |           | Fetch 4   | Flush (NOP) |               |      |  |  |  |

| 5. Instruction @ addr | ress SUB_1 |           |           | Fetch SUB_1 | Execute SUB_1 |      |  |  |  |

|                       |            |           |           |             |               |      |  |  |  |

**Note:** All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

|                   | MOVLW   | D'64′            | ; number of bytes in erase block      |

|-------------------|---------|------------------|---------------------------------------|

|                   | MOVWF   | COUNTER          |                                       |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSR0H            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

|                   | MOVLW   | CODE_ADDR_UPPER  | ; Load TBLPTR with the base           |

|                   | MOVWF   | TBLPTRU          | ; address of the memory block         |

|                   | MOVLW   | CODE_ADDR_HIGH   |                                       |

|                   | MOVWF   | TBLPTRH          |                                       |

|                   | MOVLW   | CODE_ADDR_LOW    |                                       |

|                   | MOVWF   | TBLPTRL          |                                       |

| EAD_BLOCK         |         |                  |                                       |

|                   | TBLRD*+ |                  | ; read into TABLAT, and inc           |

|                   | MOVF    | TABLAT, W        | ; get data                            |

|                   | MOVWF   | POSTINC0         | ; store data                          |

|                   | DECFSZ  | COUNTER          | ; done?                               |

|                   | BRA     | READ_BLOCK       | ; repeat                              |

| ODIFY_WORD        |         |                  |                                       |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSR0H            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

|                   | MOVLW   | NEW_DATA_LOW     | ; update buffer word                  |

|                   | MOVWF   | POSTINC0         |                                       |

|                   | MOVLW   | NEW_DATA_HIGH    |                                       |

|                   | MOVWF   | INDF0            |                                       |

| ERASE_BLOCK       |         |                  |                                       |

|                   | MOVLW   | CODE_ADDR_UPPER  | ; load TBLPTR with the base           |

|                   | MOVWF   | TBLPTRU          | ; address of the memory block         |

|                   | MOVLW   | CODE_ADDR_HIGH   |                                       |

|                   | MOVWF   | TBLPTRH          |                                       |

|                   | MOVLW   | CODE_ADDR_LOW    |                                       |

|                   | MOVWF   | TBLPTRL          |                                       |

|                   | BSF     | EECON1, EEPGD    | ; point to Flash program memory       |

|                   | BCF     | EECON1, CFGS     | ; access Flash program memory         |

|                   | BSF     | EECON1, WREN     | ; enable write to memory              |

|                   | BSF     | EECON1, FREE     | ; enable Erase operation              |

|                   | BCF     | INTCON, GIE      | ; disable interrupts                  |

|                   | MOVLW   | 55h              |                                       |

| Required          | MOVWF   | EECON2           | ; write 55h                           |

| Sequence          | MOVLW   | 0AAh             |                                       |

|                   | MOVWF   | EECON2           | ; write OAAh                          |

|                   | BSF     | EECON1, WR       | ; start erase (CPU stall)             |

|                   | BSF     | INTCON, GIE      | ; re-enable interrupts                |

|                   | TBLRD*- |                  | ; dummy read decrement                |

|                   | MOVLW   | BUFFER_ADDR_HIGH | ; point to buffer                     |

|                   | MOVWF   | FSR0H            |                                       |

|                   | MOVLW   | BUFFER_ADDR_LOW  |                                       |

|                   | MOVWF   | FSROL            |                                       |

| WRITE_BUFFER_BACK |         |                  |                                       |

|                   | MOVLW   | BlockSize        | ; number of bytes in holding register |

|                   | MOVWF   | COUNTER          |                                       |

|                   | MOVLW   | D'64'/BlockSize  | ; number of write blocks in 64 bytes  |

|                   | MOVWF   | COUNTER2         |                                       |

| WRITE_BYTE_TO_HRE | GS      |                  |                                       |

|                   | MOVF    | POSTINCO, W      | ; get low byte of buffer data         |

|                   | MOVWF   | TABLAT           | ; present data to table latch         |

|                   | TBLWT+* |                  | ; write data, perform a short write   |

|                   |         |                  | ; to internal TBLWT holding register. |

# TABLE 10-8: PORTC I/O SUMMARY

| Pin Name           | Function             | TRIS<br>Setting | ANSEL setting | Pin<br>Type | Buffer<br>Type   | Description                                                 |

|--------------------|----------------------|-----------------|---------------|-------------|------------------|-------------------------------------------------------------|

| RC0/P2B/T3CKI/T3G/ | RC0                  | 0               | _             | 0           | DIG              | LATC<0> data output; not affected by analog input.          |

| T1CKI/SOSCO        |                      | 1               | _             | I           | ST               | PORTC<0> data input; disabled when analog input enabled.    |

|                    | P2B <sup>(2)</sup>   | 0               |               | 0           | DIG              | Enhanced CCP2 PWM output 2.                                 |

|                    | T3CKI <sup>(1)</sup> | 1               | _             | I           | ST               | Timer3 clock input.                                         |

|                    | T3G                  | 1               |               | I           | ST               | Timer3 external clock gate input.                           |

|                    | T1CKI                | 1               |               | I           | ST               | Timer1 clock input.                                         |

|                    | SOSCO                | x               |               | 0           | XTAL             | Secondary oscillator output.                                |

| RC1/P2A/CCP2/SOSCI | RC1                  | 0               |               | 0           | DIG              | LATC<1> data output; not affected by analog input.          |

|                    |                      | 1               | _             | I           | ST               | PORTC<1> data input; disabled when analog input enabled.    |

|                    | P2A                  | 0               |               | 0           | DIG              | Enhanced CCP2 PWM output 1.                                 |

|                    | CCP2 <sup>(1)</sup>  | 0               |               | 0           | DIG              | Compare 2 output/PWM 2 output.                              |

|                    |                      | 1               |               | I           | ST               | Capture 2 input.                                            |

|                    | SOSCI                | х               |               | I           | XTAL             | Secondary oscillator input.                                 |

| RC2/CTPLS/P1A/     | RC2                  | 0               | 0             | 0           | DIG              | LATC<2> data output; not affected by analog input.          |

| CCP1/T5CKI/AN14    |                      | 1               | 0             | I           | ST               | PORTC<2> data input; disabled when analog input<br>enabled. |

|                    | CTPLS                | 0               | 0             | 0           | DIG              | CTMU pulse generator output.                                |

|                    | P1A                  | 0               | 0             | 0           | DIG              | Enhanced CCP1 PWM output 1.                                 |

|                    | CCP1                 | 0               | 0             | 0           | DIG              | Compare 1 output/PWM 1 output.                              |

|                    |                      | 1               | 0             | I           | ST               | Capture 1 input.                                            |

|                    | T5CKI                | 1               | 0             | I           | ST               | Timer5 clock input.                                         |

|                    | AN14                 | 1               | 1             | I           | AN               | Analog input 14.                                            |

| RC3/SCK1/SCL1/AN15 | RC3                  | 0               | 0             | 0           | DIG              | LATC<3> data output; not affected by analog input.          |

|                    |                      | 1               | 0             | I           | ST               | PORTC<3> data input; disabled when analog input<br>enabled. |

|                    | SCK1                 | 0               | 0             | 0           | DIG              | MSSP1 SPI Clock output.                                     |

|                    |                      | 1               | 0             | I           | ST               | MSSP1 SPI Clock input.                                      |

|                    | SCL1                 | 0               | 0             | 0           | DIG              | MSSP1 I <sup>2</sup> C Clock output.                        |

|                    |                      | 1               | 0             | I           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C Clock input.                         |

|                    | AN15                 | 1               | 1             | I           | AN               | Analog input 15.                                            |

| RC4/SDI1/SDA1/AN16 | RC4                  | 0               | 0             | 0           | DIG              | LATC<4> data output; not affected by analog input.          |

|                    |                      | 1               | 0             | I           | ST               | PORTC<4> data input; disabled when analog input<br>enabled. |

|                    | SDI1                 | 1               | 0             | I           | ST               | MSSP1 SPI data input.                                       |

|                    | SDA1                 | 0               | 0             | 0           | DIG              | MSSP1 I <sup>2</sup> C data output.                         |

|                    |                      | 1               | 0             | Ι           | l <sup>2</sup> C | MSSP1 I <sup>2</sup> C data input.                          |

|                    | AN16                 | 1               | 1             | I           | AN               | Analog input 16.                                            |

**Legend:** AN = Analog input or output; TTL = TTL compatible input;  $HV = High Voltage; OD = Open Drain; XTAL = Crystal; CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels; <math>I^2C = Schmitt Trigger input with I^2C$ .

Note 1: Default pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are set.

2: Alternate pin assignment for P2B, T3CKI, CCP3 and CCP2 when Configuration bits PB2MX, T3CMX, CCP3MX and CCP2MX are clear.

3: Function on PORTD and PORTE for PIC18(L)F4XK22 devices.

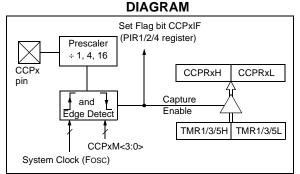

# 14.1 Capture Mode

The Capture mode function described in this section is identical for all CCP and ECCP modules available on this device family.

Capture mode makes use of the 16-bit Timer resources, Timer1, Timer3 and Timer5. The timer resources for each CCP capture function are independent and are selected using the CCPTMRS0 and CCPTMRS1 registers. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the corresponding Interrupt Request Flag bit CCPxIF of the PIR1, PIR2 or PIR4 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

# TABLE 14-2: CCP PIN MULTIPLEXING

Figure 14-1 shows a simplified diagram of the Capture operation.

FIGURE 14-1:

# CAPTURE MODE OPERATION BLOCK

# 14.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Some CCPx outputs are multiplexed on a couple of pins. Table 14-2 shows the CCP output pin multiplexing. Selection of the output pin is determined by the CCPxMX bits in Configuration register 3H (CONFIG3H). Refer to Register 24-4 for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

| CCP OUTPUT | CONFIG 3H Control Bit | Bit Value | PIC18(L)F2XK22 I/O pin | PIC18(L)F4XK22 I/O pin |

|------------|-----------------------|-----------|------------------------|------------------------|

| CCP2       | CCP2MX                | 0         | RB3                    | RB3                    |

| CCP2       | CCPZIVIA              | 1(*)      | RC1                    | RC1                    |

| CCD2       | CODOMY                | 0(*)      | RC6                    | RE0                    |

| CCP3       | CCP3MX                | 1         | RB5                    | RB5                    |

Legend: \* = Default

#### 14.1.2 TIMER1 MODE RESOURCE

The 16-bit Timer resource must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 12.0 "Timer1/3/5 Module with Gate Control" for more information on configuring the 16-bit Timers.

#### 14.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE1, PIE2 or PIE4 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR1, PIR2 or PIR4 register following any change in Operating mode.

Note: Clocking the 16-bit Timer resource from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, the Timer resource must be clocked from the instruction clock (Fosc/4) or from an external clock source.

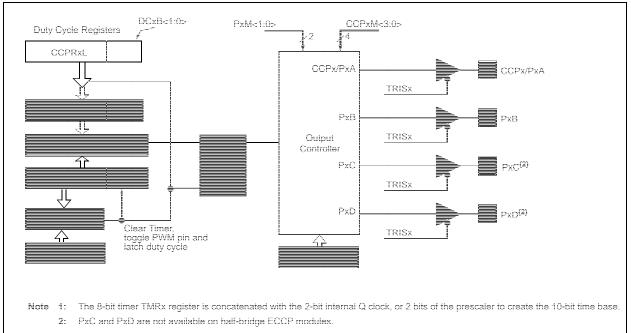

# 14.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- ECCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

- Single PWM with PWM Steering mode

To select an Enhanced PWM Output mode, the PxM<1:0> bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 14-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 14-12 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

# FIGURE 14-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

### 15.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 10-bit Addressing mode (Figure 15-20) and is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

Note: If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a <u>data</u> byte to the slave and clocks out the slaves <u>ACK</u> on the 9th SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 15.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 15-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 15-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

# REGISTER 15-5: SSPxCON3: SSPx CONTROL REGISTER 3 (CONTINUED)

- **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

- 1 = Following the 8th falling edge of SCLx for a received data byte; slave hardware clears the CKP bit of the SSPxCON1 register and SCLx is held low.

- 0 = Data holding is disabled

bit 0

- **Note 1:** For daisy-chained SPI operation; allows the user to ignore all but the last received byte. SSPxOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPxBUF.

- **2:** This bit has no effect in Slave modes for which Start and Stop condition detection is explicitly listed as enabled.

- 3: The ACKTIM Status bit is active only when the AHEN bit or DHEN bit is set.

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### REGISTER 15-6: SSPxMSK: SSPx MASK REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-1 MSK<7:1>: Mask bits

- 1 = The received address bit n is compared to SSPxADD<n> to detect I<sup>2</sup>C address match

- 0 = The received address bit n is not used to detect I<sup>2</sup>C address match

#### bit 0 **MSK<0>:** Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address

$I^2C$  Slave mode, 10-bit address (SSPxM<3:0> = 0111 or 1111):

- 1 = The received address bit 0 is compared to SSPxADD<0> to detect  $I^2C$  address match

- 0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

- I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

| R/W-0         | R/W-0                     | R/W-0                                                     | R/W-0             | R/W-0           | R-0               | R-0               | R-0     |

|---------------|---------------------------|-----------------------------------------------------------|-------------------|-----------------|-------------------|-------------------|---------|

| SPEN          | RX9                       | SREN                                                      | CREN              | ADDEN           | FERR              | OERR              | RX9D    |

| bit 7         |                           |                                                           |                   |                 |                   |                   | bit     |

| Legend:       |                           |                                                           |                   |                 |                   |                   |         |

| R = Readable  | e bit                     | W = Writable                                              | bit               | U = Unimple     | emented bit, rea  | d as '0'          |         |

| -n = Value at | POR                       | '1' = Bit is se                                           | t                 | '0' = Bit is cl | eared             | x = Bit is unkr   | nown    |

| bit 7         |                           | al Port Enable b                                          |                   |                 |                   |                   |         |

|               |                           | port enabled (co<br>port disabled (he                     |                   | DTx and TXx/0   | CKx pins as ser   | ial port pins)    |         |

| bit 6         | RX9: 9-bit F              | Receive Enable                                            | bit               |                 |                   |                   |         |

|               |                           | <ul><li>9-bit reception</li><li>8-bit reception</li></ul> |                   |                 |                   |                   |         |

| bit 5         | SREN: Sing                | gle Receive Ena                                           | ble bit           |                 |                   |                   |         |

|               | Asynchrono                | ous mode:                                                 |                   |                 |                   |                   |         |

|               | Don't care                |                                                           |                   |                 |                   |                   |         |

|               |                           | <u>us mode – Maste</u>                                    |                   |                 |                   |                   |         |

|               |                           | s single receive<br>es single receive                     |                   |                 |                   |                   |         |

|               |                           | leared after rece                                         |                   | ete.            |                   |                   |         |

|               | <u>Synchronou</u>         | <u>us mode – Slave</u>                                    | <u>)</u>          |                 |                   |                   |         |

|               | Don't care                |                                                           |                   |                 |                   |                   |         |

| bit 4         | CREN: Con                 | ntinuous Receive                                          | e Enable bit      |                 |                   |                   |         |

|               | Asynchronc                |                                                           |                   |                 |                   |                   |         |

|               | 1 = Enable                |                                                           |                   |                 |                   |                   |         |

|               | 0 = Disable<br>Synchronou |                                                           |                   |                 |                   |                   |         |

|               |                           | s continuous re                                           | ceive until enal  | ble bit CREN    | is cleared (CRF   | N overrides SR    | EN)     |

|               |                           | es continuous re                                          |                   |                 |                   |                   | ,       |

| bit 3         | ADDEN: Ad                 | dress Detect E                                            | nable bit         |                 |                   |                   |         |

|               | Asynchronc                | ous mode 9-bit (                                          | <u>RX9 = 1)</u> : |                 |                   |                   |         |

|               | 0 = Disable               | s address detec<br>es address detec<br>ous mode 8-bit (   | ction, all bytes  |                 |                   |                   |         |

|               | Don't care                |                                                           |                   |                 |                   |                   |         |

| bit 2         | FERR: Frar                | ning Error bit                                            |                   |                 |                   |                   |         |

|               | 1 = Framin<br>0 = No fran | g error (can be<br>ning error                             | updated by rea    | ading RCREG     | x register and re | eceive next valio | l byte) |

| bit 1         | OERR: Ove                 | errun Error bit                                           |                   |                 |                   |                   |         |

|               | 1 = Overru<br>0 = No ove  | n error (can be o<br>errun error                          | cleared by clea   | aring bit CREN  | 1)                |                   |         |

| <b>h</b> :+ 0 | <b>DYOD</b> . Nint        |                                                           |                   |                 |                   |                   |         |

| bit 0         | TAJD. INITI               | h bit of Receive                                          | d Data            |                 |                   |                   |         |

# REGISTER 16-2: RCSTAX: RECEIVE STATUS AND CONTROL REGISTER

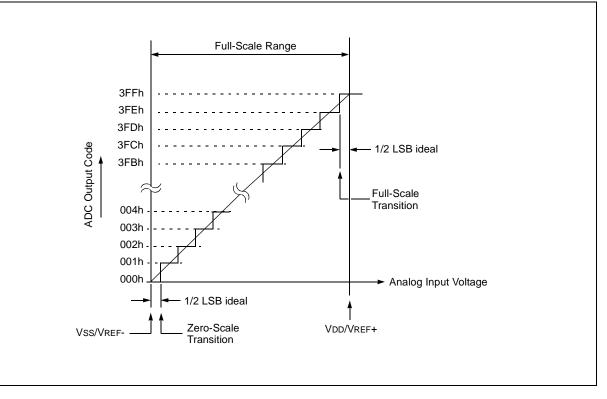

FIGURE 17-6: ADC TRANSFER FUNCTION

| RCALL                        | Relative Call                                                                                                                                                                                                                                                                                                                  |        |  |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|

| Syntax:                      | RCALL n                                                                                                                                                                                                                                                                                                                        |        |  |  |  |  |  |

| Operands:                    | -1024 ≤ n :                                                                                                                                                                                                                                                                                                                    | ≤ 1023 |  |  |  |  |  |

| Operation:                   | $\begin{array}{l} (PC) + 2 \rightarrow TOS, \\ (PC) + 2 + 2n \rightarrow PC \end{array}$                                                                                                                                                                                                                                       |        |  |  |  |  |  |

| Status Affected:             | None                                                                                                                                                                                                                                                                                                                           |        |  |  |  |  |  |

| Encoding:                    | 1101 1nnn nnnn nnnn                                                                                                                                                                                                                                                                                                            |        |  |  |  |  |  |

| Description:                 | Subroutine call with a jump up to 1K from the current location. First, return address (PC + 2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a 2-cycle instruction. |        |  |  |  |  |  |

| Words:                       | 1                                                                                                                                                                                                                                                                                                                              |        |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity: | 2                                                                                                                                                                                                                                                                                                                              |        |  |  |  |  |  |

| Q1              | Q2                                         | Q3              | Q4              |  |

|-----------------|--------------------------------------------|-----------------|-----------------|--|

| Decode          | Read literal<br>'n'<br>PUSH PC to<br>stack | Process<br>Data | Write to PC     |  |

| No<br>operation | No<br>operation                            | No<br>operation | No<br>operation |  |

#### Example: HERE RCALL Jump

Before Instruction

PC = Address (HERE)

After Instruction

PC = Address (Jump) TOS = Address (HERE + 2)

#### RESET Reset Syntax: RESET Operands: None Operation: Reset all registers and flags that are affected by a MCLR Reset. Status Affected: All Encoding: 0000 0000 1111 1111 Description: This instruction provides a way to execute a MCLR Reset by software. Words: 1 Cycles: 1 Q Cycle Activity: Q1 Q2 Q3 Q4 Decode Start No No Reset operation operation

| Example: |

|----------|

|----------|

After Instruction

| Registers = | Reset Value |

|-------------|-------------|

| Flags* =    | Reset Value |

RESET

| TSTFSZ                                           | Test f, skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                 |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|--|--|--|--|

| Syntax:                                          | TSTFSZ f {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,a}                                  |                 |  |  |  |  |

| Operands:                                        | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                      |                 |  |  |  |  |

| Operation:                                       | skip if f = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |                 |  |  |  |  |

| Status Affected:                                 | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                      |                 |  |  |  |  |

| Encoding:                                        | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 011a fff                             | f ffff          |  |  |  |  |

| Description:                                     | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                      |                 |  |  |  |  |

| Words:                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                 |  |  |  |  |

| Cycles:                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vcles if skip and<br>a 2-word instru |                 |  |  |  |  |

| Q Cycle Activity:                                | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      |                 |  |  |  |  |

| Q1                                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                   | Q4              |  |  |  |  |

| Decode                                           | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Process                              | No              |  |  |  |  |

| lf skip:                                         | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Data                                 | operation       |  |  |  |  |

| Q1                                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                   | Q4              |  |  |  |  |

| No                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                   | No              |  |  |  |  |

| operation                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                            | operation       |  |  |  |  |

| If skip and followed                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                    | 0.1             |  |  |  |  |

| Q1                                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                   | Q4              |  |  |  |  |

| No<br>operation                                  | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No<br>operation                      | No<br>operation |  |  |  |  |

| No                                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                   | No              |  |  |  |  |

| operation                                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                            | operation       |  |  |  |  |

| Example: HERE TSTFSZ CNT, 1<br>NZERO :<br>ZERO : |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |                 |  |  |  |  |

| Before Instruc                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |                 |  |  |  |  |

| PC<br>After Instructic                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | dress (HERE)                         | )               |  |  |  |  |

| If CNT<br>PC<br>If CNT<br>PC<br>FC               | = 00<br>= Ad<br>≠ 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dress (ZERO                          |                 |  |  |  |  |

| XORLW             | Exclusiv                           | Exclusive OR literal with W |     |   |           |  |  |

|-------------------|------------------------------------|-----------------------------|-----|---|-----------|--|--|

| Syntax:           | XORLW                              | k                           |     |   |           |  |  |

| Operands:         | $0 \le k \le 25$                   | 5                           |     |   |           |  |  |

| Operation:        | (W) .XOR                           | $. k \rightarrow W$         |     |   |           |  |  |

| Status Affected:  | N, Z                               |                             |     |   |           |  |  |

| Encoding:         | 0000                               | 1010                        | kkk | k | kkkk      |  |  |

| Description:      | The conte<br>the 8-bit li<br>in W. |                             |     |   |           |  |  |

| Words:            | 1                                  |                             |     |   |           |  |  |

| Cycles:           | 1                                  |                             |     |   |           |  |  |

| Q Cycle Activity: |                                    |                             |     |   |           |  |  |

| Q1                | Q2                                 | Q3                          |     |   | Q4        |  |  |

| Decode            | Read<br>literal 'k'                | Proce<br>Data               |     | W | rite to W |  |  |

| Example:          | XORLW                              | 0AFh                        |     |   |           |  |  |

| Before Instruc    | tion                               |                             |     |   |           |  |  |

| W                 | = B5h                              |                             |     |   |           |  |  |

| After Instruction | on                                 |                             |     |   |           |  |  |

| W | = | 1Ah |

|---|---|-----|

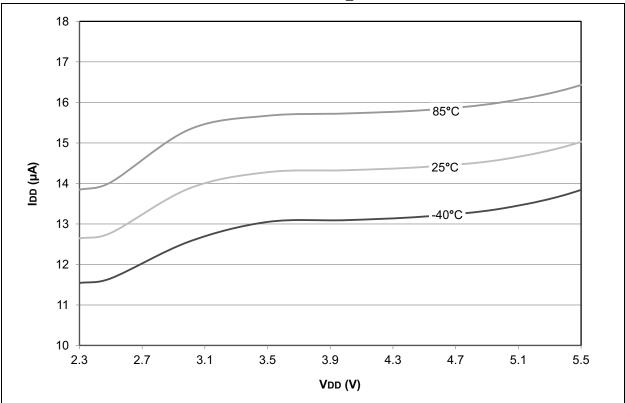

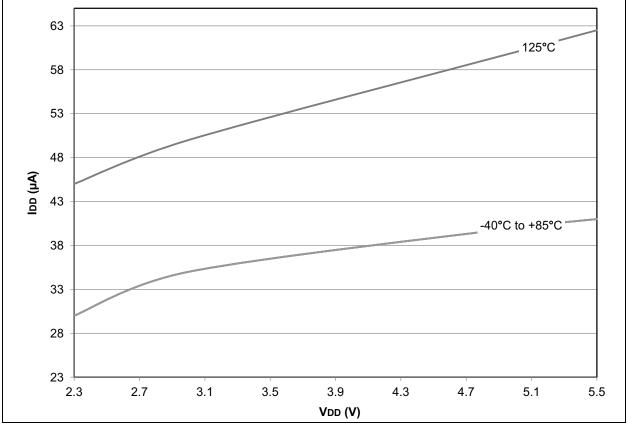

| PIC18LF      | LF2X/4XK22Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le T_A \le +125^{\circ}C$ |       |       |                           |                 |            | tated)                                                                           |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------|---------------------------|-----------------|------------|----------------------------------------------------------------------------------|--|--|

| PIC18F2      | X/4XK22                                                                                                                             |       |       | <b>erating</b><br>nperatu | re -40°C ≤ TA ≤ |            | tated)                                                                           |  |  |

| Param<br>No. | Device Characteristics                                                                                                              | Тур   | Max   | Units                     | Conditions      |            |                                                                                  |  |  |

| D100         | Supply Current (IDD) <sup>(1),(2)</sup>                                                                                             | 0.030 | 0.050 | mA                        | -40°C to +125°C | Vdd = 1.8V | Fosc = 1 MHz                                                                     |  |  |

| D101         |                                                                                                                                     | 0.045 | 0.065 | mA                        | -40°C to +125°C | VDD = 3.0V | ( <b>PRI_IDLE</b> mode,<br>ECM source)                                           |  |  |

| D102         |                                                                                                                                     | 0.06  | 0.12  | mA                        | -40°C to +125°C | VDD = 2.3V | Fosc = 1 MHz                                                                     |  |  |

| D103         |                                                                                                                                     | 0.08  | 0.15  | mA                        | -40°C to +125°C | VDD = 3.0V | ( <b>PRI_IDLE</b> mode,<br>ECM source)                                           |  |  |

| D104         |                                                                                                                                     | 0.13  | 0.20  | mA                        | -40°C to +125°C | VDD = 5.0V |                                                                                  |  |  |

| D105         |                                                                                                                                     | 0.45  | 0.8   | mA                        | -40°C to +125°C | VDD = 1.8V | Fosc = 20 MHz                                                                    |  |  |

| D106         |                                                                                                                                     | 0.70  | 1.0   | mA                        | -40°C to +125°C | VDD = 3.0V | ( <b>PRI_IDLE</b> mode,<br>ECH source)                                           |  |  |

| D107         |                                                                                                                                     | 0.55  | 0.8   | mA                        | -40°C to +125°C | VDD = 2.3V | Fosc = 20 MHz                                                                    |  |  |

| D108         |                                                                                                                                     | 0.75  | 1.0   | mA                        | -40°C to +125°C | VDD = 3.0V | ( <b>PRI_IDLE</b> mode,<br>ECH source)                                           |  |  |

| D109         |                                                                                                                                     | 0.90  | 1.2   | mA                        | -40°C to +125°C | VDD = 5.0V |                                                                                  |  |  |

| D110         |                                                                                                                                     | 2.25  | 3.0   | mA                        | -40°C to +125°C | Vdd = 3.0V | Fosc = 64 MHz<br>( <b>PRI_IDLE</b> mode,<br>ECH source)                          |  |  |

| D111         |                                                                                                                                     | 2.25  | 3.0   | mA                        | -40°C to +125°C | VDD = 3.0V | Fosc = 64 MHz                                                                    |  |  |